# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4F                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | CANbus, HDMI-CEC, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART     |

| Peripherals                | DMA, POR, PWM, WDT                                                    |

| Number of I/O              | 83                                                                    |

| Program Memory Size        | 256КВ (256К х 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 32K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 1.95V                                                         |

| Data Converters            | A/D 16x12b, 21x16b; D/A 3x12b                                         |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 100-LQFP                                                              |

| Supplier Device Package    | 100-LQFP (14x14)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f378vct6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|   |      | 6.3.9    | Memory characteristics                      | 78    |

|---|------|----------|---------------------------------------------|-------|

|   |      | 6.3.10   | EMC characteristics                         | 79    |

|   |      | 6.3.11   | Electrical sensitivity characteristics      | 80    |

|   |      | 6.3.12   | I/O current injection characteristics       | 81    |

|   |      | 6.3.13   | I/O port characteristics                    | 83    |

|   |      | 6.3.14   | NRST and NPOR pins characteristics          | 87    |

|   |      | 6.3.15   | Communications interfaces                   | 89    |

|   |      | 6.3.16   | 12-bit ADC characteristics                  | 96    |

|   |      | 6.3.17   | DAC electrical specifications               | 99    |

|   |      | 6.3.18   | Comparator characteristics                  | . 101 |

|   |      | 6.3.19   | Temperature sensor characteristics          | . 103 |

|   |      | 6.3.20   | V <sub>BAT</sub> monitoring characteristics | . 103 |

|   |      | 6.3.21   | Timer characteristics                       | . 103 |

|   |      | 6.3.22   | CAN (controller area network) interface     | . 105 |

|   |      | 6.3.23   | SDADC characteristics                       | . 105 |

| 7 | Pack | age info | ormation                                    | 111   |

|   | 7.1  | UFBG/    | A100 package information                    | . 111 |

|   | 7.2  | WLCS     | P66 package information                     | .114  |

|   | 7.3  | LQFP1    | 100 package information                     | .116  |

|   | 7.4  | LQFP6    | 64 package information                      | . 119 |

|   | 7.5  | LQFP4    | 18 package information                      | 122   |

|   | 7.6  | Therma   | al characteristics                          | 125   |

|   |      | 7.6.1    | Reference document                          | . 125 |

|   |      | 7.6.2    | Selecting the product temperature range     | . 126 |

| 8 | Part | number   | ring                                        | 128   |

| 9 | Bavi | aian hia | story                                       | 120   |

#### 3.7.2 Power supply supervisor

Device power on reset is controlled through the external NPOR pin. The device remains in reset mode when NPOR is held low. NPOR pin has an internal pull-up resistor so the external driver can be open drain type.

To guarantee a proper power-on reset, the NPOR pin must be held low until  $V_{DD}$  is stable.

When  $V_{DD}$  is stable, the reset state can be exited by:

- either putting the NPOR pin in high impedance. NPOR pin has an internal pull up.

- or forcing the pin to high level by connecting it to V<sub>DDA</sub>.

#### 3.7.3 Low-power modes

The STM32F378xx supports two low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

• Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

Stop mode

Stop mode achieves the lowest power consumption while retaining the content of SRAM and registers. All clocks in the 1.8 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled.

The device can be woken up from Stop mode by any of the EXTI line. The EXTI line source can be one of the 16 external lines, the PVD output, the USARTs, the I2Cs, the CEC the COMPx and the RTC alarm.

# 3.8 Clocks and startup

System clock selection is performed on startup, however the internal RC 8 MHz oscillator is selected as default CPU clock on reset. An external 4-32 MHz clock can be selected, in which case it is monitored for failure. If failure is detected, the system automatically switches back to the internal RC oscillator. A software interrupt is generated if enabled. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example with failure of an indirectly used external oscillator).

Several prescalers allow to configure the AHB frequency, the high speed APB (APB2) and the low speed APB (APB1) domains. The maximum frequency of the AHB and the high speed APB domains is 72 MHz, while the maximum allowed frequency of the low speed APB domain is 36 MHz.

# 3.9 General-purpose input/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions. All GPIOs are high current capable except for analog inputs.

The I/Os alternate function configuration can be locked if needed following a specific sequence in order to avoid spurious writing to the I/Os registers.

| Group | Capacitive sensing signal name | Pin name | Group | Capacitive sensing signal name | Pin<br>name |

|-------|--------------------------------|----------|-------|--------------------------------|-------------|

|       | TSC_G3_IO1                     | PC4      |       | TSC_G7_IO1                     | PE2         |

| 3     | TSC_G3_IO2                     | PC5      | 7     | TSC_G7_IO2                     | PE3         |

| 5     | TSC_G3_IO3                     | PB0      |       | TSC_G7_IO3                     | PE4         |

|       | TSC_G3_IO4                     | PB1      |       | TSC_G7_IO4                     | PE5         |

|       | TSC_G4_IO1                     | PA9      |       | TSC_G8_IO1                     | PD12        |

| 4     | TSC_G4_IO2                     | PA10     | 8     | TSC_G8_IO2                     | PD13        |

| 4     | TSC_G4_IO3                     | PA13     | 0     | TSC_G8_IO3                     | PD14        |

|       | TSC_G4_IO4                     | PA14     |       | TSC_G8_IO4                     | PD15        |

Table 3. Capacitive sensing GPIOs available on STM32F378xx devices (continued)

This GPIO offers a reduced touch sensing sensitivity. It is thus recommended to use it as sampling capacitor I/O.

|                                          | Number      | of capacitive sensing c | hannels     |

|------------------------------------------|-------------|-------------------------|-------------|

| Analog I/O group                         | STM32F378Cx | STM32F378Rx             | STM32F378Vx |

| G1                                       | 3           | 3                       | 3           |

| G2                                       | 2           | 3                       | 3           |

| G3                                       | 1           | 3                       | 3           |

| G4                                       | 3           | 3                       | 3           |

| G5                                       | 3           | 3                       | 3           |

| G6                                       | 2           | 2                       | 3           |

| G7                                       | 0           | 0                       | 3           |

| G8                                       | 0           | 0                       | 3           |

| Number of capacitive<br>sensing channels | 14          | 17                      | 24          |

Table 4. No. of capacitive sensing channels available on STM32F378xx devices

# 6 Electrical characteristics

## 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

#### 6.1.1 Minimum and maximum values

Unless otherwise specified, the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\sigma$ ).

## 6.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = 1.8$  V,  $V_{DDA} = V_{DDSDx} = 3.3$  V. They are given only as design guidelines and are not tested.

Typical ADC and SDADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\sigma$ ).

## 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

## 6.1.4 Loading capacitor

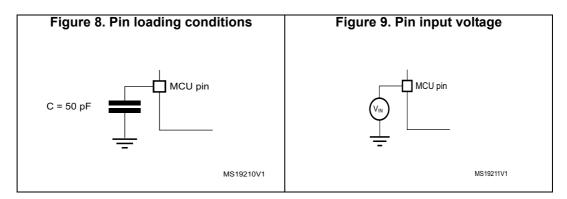

The loading conditions used for pin parameter measurement are shown in *Figure 8*.

#### 6.1.5 Pin input voltage

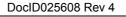

The input voltage measurement on a pin of the device is described in Figure 9.

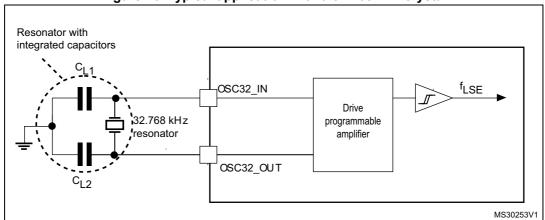

Figure 16. Typical application with a 32.768 kHz crystal

Note:

An external resistor is not required between OSC32\_IN and OSC32\_OUT and it is forbidden to add one.

#### 6.3.7 Internal clock source characteristics

The parameters given in *Table 40* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 22*.

The provided curves are characterization results, not tested in production.

#### High-speed internal (HSI) RC oscillator

| Symbol                | Parameter                           | Conditions                     | Min                 | Тур | Max                 | Unit |  |  |

|-----------------------|-------------------------------------|--------------------------------|---------------------|-----|---------------------|------|--|--|

| f <sub>HSI</sub>      | Frequency                           | -                              | -                   | 8   | -                   | MHz  |  |  |

| TRIM                  | HSI user trimming step              | -                              | -                   | -   | 1 <sup>(2)</sup>    | %    |  |  |

| DuCy <sub>(HSI)</sub> | Duty cycle                          | -                              | 45 <sup>(2)</sup>   | -   | 55 <sup>(2)</sup>   | %    |  |  |

|                       |                                     | T <sub>A</sub> = -40 to 105 °C | -3.8 <sup>(3)</sup> | -   | 4.6 <sup>(3)</sup>  | %    |  |  |

|                       | Accuracy of the HSI                 | T <sub>A</sub> = −10 to 85 °C  | -2.9 <sup>(3)</sup> | -   | 2.9 <sup>(3)</sup>  | %    |  |  |

| ACC <sub>HSI</sub>    | oscillator (factory calibrated)     | T <sub>A</sub> = 0 to 70 °C    | -2.3 <sup>(3)</sup> | -   | -2.2 <sup>(3)</sup> | %    |  |  |

|                       |                                     | T <sub>A</sub> = 25 °C         | -1                  | -   | 1                   | %    |  |  |

| t <sub>su(HSI)</sub>  | HSI oscillator startup<br>time      | -                              | 1 <sup>(3)</sup>    | -   | 2 <sup>(3)</sup>    | μs   |  |  |

| I <sub>DD(HSI)</sub>  | HSI oscillator power<br>consumption | -                              | -                   | 80  | 100 <sup>(3)</sup>  | μA   |  |  |

Table 40. HSI oscillator characteristics<sup>(1)</sup>

1.  $V_{DDA}$  = 3.3 V,  $T_A$  = -40 to 105 °C unless otherwise specified.

2. Guaranteed by design.

3. Guaranteed by characterization results.

#### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latch-up standard.

| Table | 48. | Electrical | sensitivities  |

|-------|-----|------------|----------------|

| Table | τυ. | LICCUICAI  | 30113111411103 |

| Symbol | Parameter             | Conditions                                    | Class      |

|--------|-----------------------|-----------------------------------------------|------------|

| LU     | Static latch-up class | $T_A = +105 \text{ °C conforming to JESD78A}$ | II level A |

### 6.3.12 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard, 3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (higher than 5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of  $-5 \mu$ A/+0  $\mu$ A range), or other functional failure (for example reset occurrence or oscillator frequency deviation).

The test results are given in Table 49.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 6.2*:

- The sum of the currents sourced by all the I/Os on all VDD\_x and VDDSDx, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub> cannot exceed the absolute maximum rating SI<sub>VDD</sub> (see *Table 20*).

- The sum of the currents sunk by all the I/Os on all VSS\_x and VSSSD, plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating SI<sub>VSS</sub> (see *Table 20*).

#### Output voltage levels

Unless otherwise specified, the parameters given in *Table 51* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 22*. All I/Os are CMOS and TTL compliant (FT, TTa or TC unless otherwise specified).

| Symbol                            | Parameter                                                                    | Conditions                                                    | Min            | Max | Unit |

|-----------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------|----------------|-----|------|

| V <sub>OL</sub> <sup>(2)</sup>    | Output low level voltage for an I/O pin                                      | I <sub>IO</sub> = +4 mA<br>1.65 V < V <sub>DD</sub> < 1.95 V  | -              | 0.4 |      |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin                                     | $1.65 \text{ V} < \text{V}_{\text{DD}} < 1.95 \text{ V}$      |                | -   |      |

| V <sub>OL</sub> <sup>(2)(4)</sup> | Output low level voltage for an I/O pin powered by VDDSDx <sup>(1)</sup>     | I <sub>IO</sub> = +8 mA                                       | -              | 0.4 |      |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O<br>pin powered by VDDSDx <sup>(1)</sup> | 2.7 V < VDDSDx < 3.6 V                                        | VDDSDx<br>-0.4 | -   | V    |

| V <sub>OL</sub> <sup>(2)(4)</sup> | Output low level voltage for an I/O pin powered by VDDSDx <sup>(1)</sup>     | I <sub>IO</sub> = +20 mA                                      | -              | 1.3 |      |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O<br>pin powered by VDDSDx <sup>(1)</sup> | 2.7 V < VDDSDx < 3.6 V                                        | VDDSDx<br>-1.3 | -   |      |

| V <sub>OLFM+</sub> <sup>(2)</sup> | Output low level voltage for a FTf I/O pins in FM+ mode                      | I <sub>IO</sub> = +10 mA<br>1.65 V < V <sub>DD</sub> < 1.95 V | -              | 0.4 |      |

| Table 51. | <b>Output voltag</b> | e characteristics <sup>(1)</sup> |

|-----------|----------------------|----------------------------------|

|-----------|----------------------|----------------------------------|

VDDSD12 is the external power supply for the PB10, and PE7 to PE15 I/O pins (the I/O pin ground is internally connected to VSS). VDDSD3 is the external power supply for PB14 to PB15 and PD8 to PD15 I/O pins (the I/O pin ground is internally connected to VSS). For those pins all V<sub>DD</sub> supply references in this table are related to their given VDDSDx power supply.

- 2. The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 20* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS( $\Sigma$ )</sub>.

- 3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in Table 20 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD( $\Sigma$ )</sub>.

- 4. Guaranteed by design.

Note:

- I/O pins are powered from V<sub>DD</sub> voltage except pins which can be used as SDADC inputs:

- The PB10 and PE7 to PE15 I/O pins are powered from  $V_{DDSD12}$ .

- PB14 to PB15 and PD8 to PD15 I/O pins are powered from V\_{DDSD3}. All I/O pin ground is internally connected to V\_{SS}.

$V_{DD}$  mentioned in the Table 51 represents power voltage for a given I/O pin ( $V_{DD}$  or  $V_{DDSD12}$  or  $V_{DDSD3}$ ).

#### Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 20* and *Table 52*, respectively.

Unless otherwise specified, the parameters given are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 22*.

| OSPEEDRy<br>[1:0] value <sup>(1)</sup> | Symbol                                                                                       | Parameter                                                             | Conditions                                                   | Min | Max                | Unit |

|----------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------|-----|--------------------|------|

|                                        | f <sub>max(IO)out</sub>                                                                      | Maximum frequency <sup>(2)</sup>                                      | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 1.95 V                 | -   | 1                  | MHz  |

| x0                                     | t <sub>f(IO)out</sub>                                                                        | Output high to low level<br>fall time                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.65 V to 1.95 V   | -   | 125 <sup>(3)</sup> | ns   |

|                                        | t <sub>r(IO)out</sub>                                                                        | Output low to high level rise time                                    | ομ - 30 μι, ν <sub>DD</sub> - 1.03 ν το 1.33 ν               | -   | 125 <sup>(3)</sup> | 113  |

|                                        | $f_{max(IO)out}$ Maximum frequency <sup>(2)</sup> $C_L = 50$ pF, $V_{DD} = 1.65$ V to 1.95 V |                                                                       | -                                                            | 4   | MHz                |      |

| 01 t <sub>f(IO)ou</sub>                |                                                                                              | Output high to low level<br>fall time                                 |                                                              |     | 62.5               | ns   |

|                                        | t <sub>r(IO)out</sub>                                                                        | Output low to high level rise time                                    | - C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.65 V to 1.95 V |     | 62.5               | 115  |

|                                        | f <sub>max(IO)out</sub>                                                                      | Maximum frequency <sup>(2)(3)</sup>                                   | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.65 V to 1.95 V   | -   | 10                 | MHz  |

| 11                                     | t <sub>f(IO)</sub> out                                                                       | Output high to low level<br>fall time                                 | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 1.95 V                 |     | 25                 | ns   |

|                                        | t <sub>r(IO)out</sub>                                                                        | Output low to high level rise time                                    | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.65 V to 1.95 V   | -   | 25                 | 115  |

|                                        | f <sub>max(IO)out</sub>                                                                      | Maximum frequency <sup>(2)</sup>                                      |                                                              | -   | 0.5                | MHz  |

| FM+<br>configuration                   | t <sub>f(IO)out</sub>                                                                        | Output high to low level fall time                                    | CL = 50 pF, V <sub>DD</sub> = 1.65 V to 1.95 V               | -   | 16                 | ns   |

| (+)                                    | t <sub>r(IO)out</sub>                                                                        | Output low to high level rise time                                    |                                                              | -   | 44                 | 115  |

| -                                      | t <sub>EXTIpw</sub>                                                                          | Pulse width of external<br>signals detected by the<br>EXTI controller | -                                                            | 10  | -                  | ns   |

Table 52. I/O AC characteristics<sup>(1)</sup>

1. The I/O speed is configured using the OSPEEDRx[1:0] bits. Refer to the RM0313 reference manual for a description of GPIO Port configuration register.

2. The maximum frequency is defined in *Figure 20*.

3. Guaranteed by design.

4. The I/O speed configuration is bypassed in FM+ I/O mode. Refer to the STM32F37xx reference manual RM0313 for a description of FM+ I/O mode configuration

1. Measurement points are done at  $0.5V_{DD}$  level and with external C<sub>L</sub> = 30 pF.

| Symbol                                                  | Parameter                                 | Conditions                                            | Min   | Мах    | Unit |

|---------------------------------------------------------|-------------------------------------------|-------------------------------------------------------|-------|--------|------|

| DuCy(SCK) <sup>(1)</sup>                                | I2S slave input clock duty cycle          | Slave mode                                            | 30    | 70     | %    |

| f <sub>CK</sub> <sup>(1)</sup>                          | I <sup>2</sup> S clock frequency          | Master mode (data: 16 bits, Audio frequency = 48 kHz) | 1.528 | 1.539  | MHz  |

| 1/t <sub>c(CK)</sub>                                    |                                           | Slave mode                                            | 0     | 12.288 |      |

| t <sub>r(CK)</sub> <sup>(1)</sup><br>t <sub>f(CK)</sub> | I <sup>2</sup> S clock rise and fall time | Capacitive load C <sub>L</sub> = 30 pF                | -     | 8      |      |

| t <sub>v(WS)</sub> <sup>(1)</sup>                       | WS valid time                             | Master mode                                           | 4     | -      |      |

| t <sub>h(WS)</sub> <sup>(1)</sup>                       | WS hold time                              | Master mode                                           | 4     | -      |      |

| t <sub>su(WS)</sub> <sup>(1)</sup>                      | WS setup time                             | Slave mode                                            | 2     | -      |      |

| t <sub>h(WS)</sub> <sup>(1)</sup>                       | WS hold time                              | Slave mode                                            | -     | -      |      |

| t <sub>w(CKH)</sub> <sup>(1)</sup>                      | I2S clock high time                       | Master f <sub>PCLK</sub> = 16 MHz, audio              | 306   | -      |      |

| t <sub>w(CKL)</sub> <sup>(1)</sup>                      | I2S clock low time                        | frequency = 48 kHz                                    | 312   | -      |      |

| t <sub>su(SD_MR)</sub> <sup>(1)</sup>                   | Deta input actua tima                     | Master receiver                                       | 6     | -      |      |

| t <sub>su(SD_SR)</sub> <sup>(1)</sup>                   | Data input setup time                     | Slave receiver                                        | 3     | -      | ns   |

| $t_{h(SD_MR)}^{(1)}$                                    | Data input hold time                      | Master receiver                                       | 1.5   | -      |      |

| t <sub>h(SD_SR)</sub> <sup>(1)</sup>                    | Data input hold time                      | Slave receiver                                        | 1.5   | -      |      |

| $t_{v(SD\_ST)}$ <sup>(1)</sup>                          | Data output valid time                    | Slave transmitter<br>(after enable edge)              | -     | 16     |      |

| t <sub>h(SD_ST)</sub> <sup>(1)</sup>                    | Data output hold time                     | Slave transmitter<br>(after enable edge)              | 16    | -      |      |

| t <sub>v(SD_MT)</sub> <sup>(1)</sup>                    | Data output valid time                    | Master transmitter<br>(after enable edge)             | -     | 2      |      |

| t <sub>h(SD_MT)</sub> <sup>(1)</sup>                    | Data output hold time                     | Master transmitter<br>(after enable edge)             | 0     | _      |      |

Table 58. I<sup>2</sup>S characteristics

1. Guaranteed by characterization results.

# 6.3.18 Comparator characteristics

| Symbol                   | Parameter                                    | Conditions                           |                                                                                          | Min  | Тур | Max <sup>(1)</sup>  | Unit  |

|--------------------------|----------------------------------------------|--------------------------------------|------------------------------------------------------------------------------------------|------|-----|---------------------|-------|

| M                        |                                              | V <sub>REFINT</sub> scaler           | not in use                                                                               | 1.65 |     | 2.6                 | v     |

| V <sub>DDA</sub>         | Analog supply voltage                        | V <sub>REFINT</sub> scale            | er in use                                                                                | 2    | -   | 3.6                 | v     |

| V <sub>IN</sub>          | Comparator<br>input voltage range            | -                                    |                                                                                          | 0    | -   | V <sub>DDA</sub>    | V     |

| $V_{BG}$                 | V <sub>REFINT</sub> scaler<br>input voltage  | -                                    |                                                                                          | -    | 1.2 | -                   | V     |

| V <sub>SC</sub>          | V <sub>REFINT</sub> scaler<br>offset voltage | -                                    |                                                                                          | -    | ±5  | ±10                 | mV    |

| t <sub>s_sc</sub>        | Scaler startup time<br>from power down       |                                      | First V <sub>REFINT</sub> scaler activation after device<br>power on<br>Next activations |      | -   | 1000 <sup>(2)</sup> | ms    |

| -                        | nom power down                               | Next activa                          |                                                                                          |      |     | 0.2                 |       |

| t <sub>START</sub>       | Comparator startup time                      | Startup time to reach p<br>specifica |                                                                                          | -    | -   | 60                  | μs    |

|                          |                                              | Ultra-low power mode                 |                                                                                          | -    | 2   | 4.5                 |       |

|                          | Propagation delay for                        | Low power mode                       |                                                                                          | -    | 0.7 | 1.5                 | μs    |

|                          | 200 mV step with 100 mV<br>overdrive         | Medium power mode                    |                                                                                          | -    | 0.3 | 0.6                 |       |

|                          |                                              | High speed mode                      | $V_{DDA} \ge 2.7 V$                                                                      | -    | 50  | 100                 | ns    |

| t <sub>D</sub>           |                                              | V <sub>DDA</sub> < 2.7               |                                                                                          | -    | 100 | 240                 | 115   |

| ۲D                       |                                              | Ultra-low pow                        | er mode                                                                                  | -    | 2   | 7                   |       |

|                          | Propagation delay for full                   | Low power mode                       |                                                                                          | -    | 0.7 | 2.1                 | μs    |

|                          | range step with 100 mV                       | Medium power mode                    |                                                                                          | -    | 0.3 | 1.2                 |       |

|                          | overdrive                                    | Link and made                        | $V_{DDA} \ge 2.7 V$                                                                      | -    | 90  | 180                 |       |

|                          |                                              | High speed mode                      | V <sub>DDA</sub> < 2.7 V                                                                 | -    | 110 | 300                 | ns    |

| V <sub>offset</sub>      | Comparator offset error                      | -                                    |                                                                                          | -    | ±4  | ±10                 | mV    |

| dV <sub>offset</sub> /dT | Offset error temperature coefficient         | -                                    |                                                                                          | -    | 18  | -                   | µV/°C |

|                          |                                              | Ultra-low power mode                 |                                                                                          | -    | 1.2 | 1.5                 |       |

|                          | COMP current                                 | Low power                            | mode                                                                                     | -    | 3   | 5                   | μA    |

| I <sub>DD(COMP)</sub>    | consumption                                  | Medium powe                          | er mode                                                                                  | -    | 10  | 15                  |       |

|                          |                                              | High speed                           | mode                                                                                     | -    | 75  | 100                 |       |

|  | Table 63 | . Com | parator | <sup>•</sup> characteristic | cs |

|--|----------|-------|---------|-----------------------------|----|

|--|----------|-------|---------|-----------------------------|----|

## 6.3.19 Temperature sensor characteristics

| Calibration value name | Description                                                                                           | Memory address            |  |  |  |  |

|------------------------|-------------------------------------------------------------------------------------------------------|---------------------------|--|--|--|--|

| TS_CAL1                | TS ADC raw data acquired at temperature of 30 $^{\circ}$ C ± 5 $^{\circ}$ C, V <sub>DDA</sub> = 3.3 V | 0x1FFF F7B8 - 0x1FFF F7B9 |  |  |  |  |

| TS_CAL2                | TS ADC raw data acquired at temperature of 110 $^{\circ}$ C ± 5 $^{\circ}$ C V <sub>DDA</sub> = 3.3 V | 0x1FFF F7C2 - 0x1FFF F7C3 |  |  |  |  |

Table 64. Temperature sensor calibration values

## Table 65. TS characteristics

| Symbol                                | Parameter                                      | Min  | Тур  | Max  | Unit  |

|---------------------------------------|------------------------------------------------|------|------|------|-------|

| TL                                    | V <sub>SENSE</sub> linearity with temperature  | -    | ±1   | ±2   | °C    |

| Avg_Slope <sup>(1)</sup>              | Average slope                                  | 4.0  | 4.3  | 4.6  | mV/°C |

| V <sub>25</sub>                       | Voltage at 25 °C                               | 1.34 | 1.43 | 1.52 | V     |

| t <sub>START</sub> <sup>(1)</sup>     | Startup time                                   | 4    | -    | 10   | μs    |

| T <sub>S_temp</sub> <sup>(2)(1)</sup> | ADC sampling time when reading the temperature | 17.1 | -    | -    | μs    |

1. Guaranteed by design.

2. Shortest sampling time can be determined in the application by multiple iterations.

## 6.3.20 V<sub>BAT</sub> monitoring characteristics

| Symbol                             | Parameter                                                           | Min | Тур | Max | Unit |

|------------------------------------|---------------------------------------------------------------------|-----|-----|-----|------|

| R                                  | Resistor bridge for V <sub>BAT</sub>                                | -   | 50  | -   | KΩ   |

| Q                                  | Ratio on V <sub>BAT</sub> measurement                               | -   | 2   | -   | -    |

| Er <sup>(1)</sup>                  | Error on Q                                                          | -1  | -   | +1  | %    |

| T <sub>S_vbat</sub> <sup>(2)</sup> | ADC sampling time when reading the V <sub>BAT</sub><br>1mV accuracy | 5   | -   | -   | μs   |

#### Table 66. V<sub>BAT</sub> monitoring characteristics

1. Guaranteed by design.

2. Shortest sampling time can be determined in the application by multiple iterations.

## 6.3.21 Timer characteristics

The parameters given in *Table* 67 are guaranteed by design.

Refer to Section 6.3.13: I/O port characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                | Parameter                   | Conditions                    | Min    | Мах                     | Unit                 |  |

|-----------------------|-----------------------------|-------------------------------|--------|-------------------------|----------------------|--|

| t                     | Timer resolution time       | -                             | 1      | -                       | t <sub>TIMxCLK</sub> |  |

| t <sub>res(TIM)</sub> |                             | f <sub>TIMxCLK</sub> = 72 MHz | 13.9   | -                       | ns                   |  |

| f                     | Timer external clock        |                               | 0      | f <sub>TIMxCLK</sub> /2 | MHz                  |  |

| f <sub>EXT</sub>      | frequency on CH1 to CH4     | f <sub>TIMxCLK</sub> = 72 MHz | 0      | 24                      | MHz                  |  |

| Res <sub>TIM</sub>    | Timer resolution            | TIMx (except<br>TIM2)         | -      | 16                      | bit                  |  |

|                       |                             | TIM2                          | -      | 32                      |                      |  |

| +                     | 16 bit counter clock period | -                             | 1      | 65536                   | t <sub>TIMxCLK</sub> |  |

| <sup>t</sup> COUNTER  | 16-bit counter clock period | f <sub>TIMxCLK</sub> = 72 MHz | 0.0139 | 910                     | μs                   |  |

| t <sub>MAX_COUN</sub> | Maximum possible count      | -                             | -      | 65536 × 65536           | t <sub>TIMxCLK</sub> |  |

|                       | with 32-bit counter         | f <sub>TIMxCLK</sub> = 72 MHz | -      | 59.65                   | S                    |  |

Table 67. TIMx<sup>(1) (2)</sup>characteristics

1. TIMx is used as a general term to refer to the TIM2, TIM3, TIM4, TIM5, TIM6, TIM7, TIM12, TIM13, TIM14, TIM15, TIM16, TIM17, TIM18 and TIM19 timers.

2. Guaranteed by characterization results.

| Table 68. IWDG min/max timeout period at 40 kHz (LSI) (14) |              |                                     |                                     |  |  |  |  |

|------------------------------------------------------------|--------------|-------------------------------------|-------------------------------------|--|--|--|--|

| Prescaler divider                                          | PR[2:0] bits | Min timeout (ms) RL[11:0]=<br>0x000 | Max timeout (ms) RL[11:0]=<br>0xFFF |  |  |  |  |

| /4                                                         | 0            | 0.1                                 | 409.6                               |  |  |  |  |

| /8                                                         | 1            | 0.2                                 | 819.2                               |  |  |  |  |

| /16                                                        | 2            | 0.4                                 | 1638.4                              |  |  |  |  |

| /32                                                        | 3            | 0.8                                 | 3276.8                              |  |  |  |  |

| /64                                                        | 4            | 1.6                                 | 6553.6                              |  |  |  |  |

| /128                                                       | 5            | 3.2                                 | 13107.2                             |  |  |  |  |

| /256                                                       | 7            | 6.4                                 | 26214.4                             |  |  |  |  |

| Table 68. IWDG min/max timeout period at 40 k |

|-----------------------------------------------|

|-----------------------------------------------|

1. These timings are given for a 40 kHz clock but the microcontroller's internal RC frequency can vary from 30 to 60 kHz. Moreover, given an exact RC oscillator frequency, the exact timings still depend on the phasing of the APB interface clock versus the LSI clock so that there is always a full RC period of uncertainty.

2. Guaranteed by characterization results.

| Prescaler | WDGTB | Min timeout value | Max timeout value |

|-----------|-------|-------------------|-------------------|

| 1         | 0     | 0.05687           | 3.6409            |

| 2         | 1     | 0.1137            | 7.2817            |

| 4         | 2     | 0.2275            | 14.564            |

| 8         | 3     | 0.4551            | 29.127            |

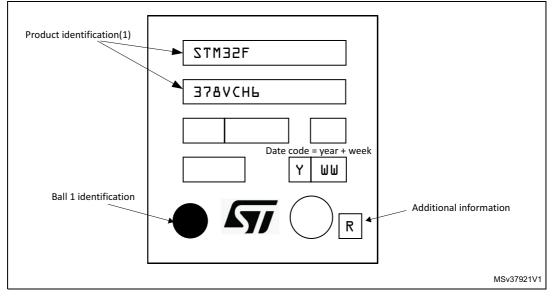

### **Device Marking for UFBGA100**

The following figure gives an example of topside marking orientation versus ball 1 identifier location.

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

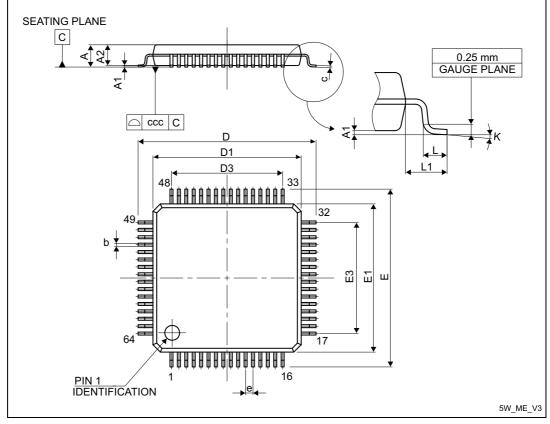

# 7.4 LQFP64 package information

Figure 40. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline

1. Drawing is not to scale.

## 7.6 Thermal characteristics

The maximum chip junction temperature (T<sub>J</sub>max) must never exceed the values given in *Table 22: General operating conditions*.

The maximum chip-junction temperature,  $T_{\rm J}$  max, in degrees Celsius, may be calculated using the following equation:

$T_J max = T_A max + (P_D max x Q_{JA})$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- Q<sub>JA</sub> is the package junction-to-ambient thermal resistance, in °C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

$P_{I/O}$  max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I/O}} \max = \mathsf{S} \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \mathsf{S}((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V\_{OL} / I\_{OL} and V\_{OH} / I\_{OH} of the I/Os at low and high level in the application.

| Symbol        | Parameter                                                                        | Value | Unit |

|---------------|----------------------------------------------------------------------------------|-------|------|

|               | <b>Thermal resistance junction-ambient</b><br>LQFP64 - 10 × 10 mm / 0.5 mm pitch | 45    |      |

|               | <b>Thermal resistance junction-ambient</b><br>LQFP48 - 7 × 7 mm                  | 55    |      |

| $\Theta_{JA}$ | Thermal resistance junction-ambient<br>LQFP100 - 14 × 14 mm / 0.5 mm pitch       | 46    | °C/W |

|               | Thermal resistance junction-ambient<br>BGA100 - 7 x 7 mm                         | 59    |      |

|               | Thermal resistance junction-ambient<br>WLCSP66 - 0.400 mm                        | 53    |      |

#### Table 78. Package thermal characteristics

#### 7.6.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org

#### 7.6.2 Selecting the product temperature range

When ordering the microcontroller, the temperature range is specified in the ordering information scheme shown in Section 8: Part numbering.

Each temperature range suffix corresponds to a specific guaranteed ambient temperature at maximum dissipation and, to a specific maximum junction temperature.

As applications do not commonly use the STM32F378xx at maximum dissipation, it is useful to calculate the exact power consumption and junction temperature to determine which temperature range will be best suited to the application.

The following examples show how to calculate the temperature range needed for a given application.

#### Example 1: High-performance application

Assuming the following application conditions:

Maximum ambient temperature T<sub>Amax</sub> = 82 °C (measured according to JESD51-2),  $I_{DDmax}$  = 50 mA,  $V_{DD}$  = 1.8 V, maximum 3 I/Os used at the same time in output at low level with  $I_{OL}$  = 8 mA,  $V_{OL}$ = 0.4 V and maximum 2 I/Os used at the same time in output at low level with  $I_{OL}$  = 20 mA,  $V_{OL}$  = 1.3 V

P<sub>INTmax</sub> = 50 mA × 1.8 V= 90 mW

P<sub>IOmax</sub> = 3 × 8 mA × 0.4 V + 2 × 20 mA × 1.3 V = 61.6 mW

This gives: P<sub>INTmax</sub> = 90 mW and P<sub>IOmax</sub> = 61.6 mW:

$P_{Dmax} = 90 + 61.6 = 151.6 \text{ mW}$

Thus: P<sub>Dmax</sub> = 151.6 mW

Using the values obtained in *Table 78* T<sub>Jmax</sub> is calculated as follows:

For LQFP64, 45°C/W

T<sub>.lmax</sub> = 82 °C + (45°C/W × 151.6 mW) = 82 °C + 6.8 °C = 88.8 °C

This is within the range of the suffix 6 version parts ( $-40 < T_{.1} < 105$ °C).

In this case, parts must be ordered at least with the temperature range suffix 6 (see Section 8: Part numbering).

#### **Example 2: High-temperature application**

Using the same rules, it is possible to address applications that run at high ambient temperatures with a low dissipation, as long as junction temperature  $T_J$  remains within the specified range.

Assuming the following application conditions:

Maximum ambient temperature T<sub>Amax</sub> = 115 °C (measured according to JESD51-2),  $I_{DDmax}$  = 20 mA,  $V_{DD}$  = 1.8 V, maximum 9 I/Os used at the same time in output at low level with  $I_{OL}$  = 8 mA,  $V_{OL}$ = 0.4 V P<sub>INTmax</sub> = 20 mA × 1.8 V= 36 mW  $P_{IOmax} = 9 \times 8 \text{ mA} \times 0.4 \text{ V} = 28.8 \text{ mW}$ This gives: P<sub>INTmax</sub> = 36 mW and P<sub>IOmax</sub> = 28.8 mW: P<sub>Dmax</sub> = 36+ 28.8 = 64.8 mW

Thus: P<sub>Dmax</sub> = 64.8 mW

# 8 Part numbering

For a list of available options (memory, package, and so on) or for further information on any aspect of this device, please contact your nearest ST sales office.

| Example:                                        | STM32 | F | 378 | R | С | Т | 6 | > |

|-------------------------------------------------|-------|---|-----|---|---|---|---|---|

| Device family                                   |       |   |     |   |   |   |   |   |

| STM32 = ARM-based 32-bit microcontroller        |       |   |     |   |   |   |   |   |

|                                                 |       |   |     |   |   |   |   |   |

| Product type                                    |       |   |     |   |   |   |   |   |

| F = General-purpose                             |       |   |     |   |   |   |   |   |

| Sub-family                                      |       |   |     |   |   |   |   |   |

| 378 = STM32F378xx                               |       |   |     |   |   |   |   |   |

|                                                 |       |   |     |   |   |   |   |   |

| Pin count                                       |       |   |     |   |   |   |   |   |

| C = 48 pins                                     |       |   |     |   |   |   |   |   |

| R = 64/66 pins                                  |       |   |     |   |   |   |   |   |

| V = 100 pins                                    |       |   |     |   |   |   |   |   |

| Code size                                       |       |   |     |   |   |   |   |   |

| C = 256 Kbytes of Flash memory                  |       |   |     |   |   |   |   |   |

| Package                                         |       |   |     |   |   |   |   |   |

| T = LQFP                                        |       |   |     |   |   |   |   |   |

| H = BGA                                         |       |   |     |   |   |   |   |   |

| Y = WLCSP                                       |       |   |     |   |   |   |   |   |

| Temperature range                               |       |   |     |   |   |   |   |   |

| 6 = Industrial temperature range, -40 to 85 °C  |       |   |     |   |   |   | 1 |   |

| 7 = Industrial temperature range, -40 to 105 °C |       |   |     |   |   |   |   |   |

|                                                 |       |   |     |   |   |   |   |   |

| Options                                         |       |   |     |   |   |   |   |   |

#### Options

xxx = programmed parts TR = tape and reel

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 10-Jun-2016 | 4        | <ul> <li>Updated:</li> <li>Table 3: Capacitive sensing GPIOs available on STM32F378xx<br/>devices</li> <li>Table 19: Voltage characteristics</li> <li>Table 25: Embedded internal reference voltage</li> <li>Table 39: LSE oscillator characteristics (fLSE = 32.768 kHz)</li> <li>Table 47: ESD absolute maximum ratings</li> <li>Table 59: ADC characteristics</li> <li>Table 62: DAC characteristics</li> <li>Table 70: SDADC characteristics</li> <li>Table 78: Package thermal characteristics</li> <li>Figure 18: TC and TTa I/O input characteristics</li> <li>Figure 19: Five volt tolerant (FT and FTf) I/O input<br/>characteristics - TTL port</li> </ul> |  |  |

| Table 80. | <b>Document revision</b> | history | (continued) |

|-----------|--------------------------|---------|-------------|

|-----------|--------------------------|---------|-------------|

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved