#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Active                                                        |

|---------------------------------|---------------------------------------------------------------|

| Core Processor                  | PowerPC e300c3                                                |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                |

| Speed                           | 133MHz                                                        |

| Co-Processors/DSP               | Communications; QUICC Engine                                  |

| RAM Controllers                 | DDR2                                                          |

| Graphics Acceleration           | No                                                            |

| Display & Interface Controllers | -                                                             |

| Ethernet                        | 10/100Mbps (3)                                                |

| SATA                            | -                                                             |

| USB                             | USB 2.0 (1)                                                   |

| Voltage - I/O                   | 1.8V, 3.3V                                                    |

| Operating Temperature           | -40°C ~ 105°C (TA)                                            |

| Security Features               | -                                                             |

| Package / Case                  | 369-LFBGA                                                     |

| Supplier Device Package         | 369-PBGA (19x19)                                              |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8306scvmabdca |

|                                 |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Overview

The MPC8306S incorporates the e300c3 (MPC603e-based) core built on Power Architecture® technology, which includes 16 Kbytes of each L1 instruction and data caches, dual integer units, and on-chip memory management units (MMUs). The MPC8306S also includes two DMA engines and a 16-bit DDR2 memory controller.

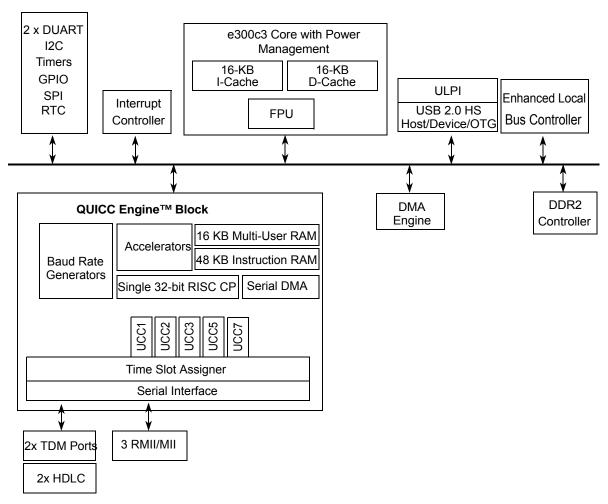

A new communications complex based on QUICC Engine technology forms the heart of the networking capability of the MPC8306S. The QUICC Engine block contains several peripheral controllers and a 32-bit RISC controller. Protocol support is provided by the main workhorses of the device—the unified communication controllers (UCCs). A block diagram of the MPC8306S is shown in the following figure.

Figure 1. MPC8306S Block Diagram

Each of the five UCCs can support a variety of communication protocols such as 10/100 Mbps MII/RMII Ethernet, HDLC and TDM.

Overview

In summary, the MPC8306S provides users with a highly integrated, fully programmable communications processor. This helps to ensure that a low-cost system solution can be quickly developed and offers flexibility to accommodate new standards and evolving system requirements.

## 1.1 Features

The major features of the device are as follows:

- e300c3 Power Architecture processor core

- Enhanced version of the MPC603e core

- High-performance, superscalar processor core with a four-stage pipeline and low interrupt latency times

- Floating-point, dual integer units, load/store, system register, and branch processing units

- 16-Kbyte instruction cache and 16-Kbyte data cache with lockable capabilities

- Dynamic power management

- Enhanced hardware program debug features

- Software-compatible with Freescale processor families implementing Power Architecture technology

- Separate PLL that is clocked by the system bus clock

- Performance monitor

- QUICC Engine block

- 32-bit RISC controller for flexible support of the communications peripherals with the following features:

- One clock per instruction

- Separate PLL for operating frequency that is independent of system's bus and e300 core frequency for power and performance optimization

- 32-bit instruction object code

- Executes code from internal IRAM

- 32-bit arithmetic logic unit (ALU) data path

- Modular architecture allowing for easy functional enhancements

- Slave bus for CPU access of registers and multiuser RAM space

- 48 Kbytes of instruction RAM

- 16 Kbytes of multiuser data RAM

- Serial DMA channel for receive and transmit on all serial channels

- Five unified communication controllers (UCCs) supporting the following protocols and interfaces:

- 10/100 Mbps Ethernet/IEEE Std. 802.3® through MII and RMII interfaces.

- HDLC/Transparent (bit rate up to QUICC Engine operating frequency / 8)

- HDLC Bus (bit rate up to 10 Mbps)

- Asynchronous HDLC (bit rate up to 2 Mbps)

#### Overview

Two TDM interfaces supporting up to 128 QUICC multichannel controller channels, each running at 64 kbps

For more information on QUICC Engine sub-modules, see *QUICC Engine Block Reference Manual with Protocol Interworking*.

- DDR SDRAM memory controller

- Programmable timing supporting DDR2 SDRAM

- Integrated SDRAM clock generation

- 16-bit data interface, up to 266-MHz data rate

- 14 address lines

- The following SDRAM configurations are supported:

- Up to two physical banks (chip selects), 256-Mbyte per chip select for 16 bit data interface.

- 64-Mbit to 2-Gbit devices with x8/x16 data ports (no direct x4 support)

- One 16-bit device or two 8-bit devices on a 16-bit bus,

- Support for up to 16 simultaneous open pages for DDR2

- One clock pair to support up to 4 DRAM devices

- Supports auto refresh

- On-the-fly power management using CKE

- Enhanced local bus controller (eLBC)

- Multiplexed 26-bit address and 8-/16-bit data operating at up to 66 MHz

- Eight chip selects supporting eight external slaves

- Four chip selects dedicated

- Four chip selects offered as multiplexed option

- Supports boot from parallel NOR Flash and parallel NAND Flash

- Supports programmable clock ratio dividers

- Up to eight-beat burst transfers

- 16- and 8-bit ports, separate  $\overline{\text{LWE}}$  for each 8 bit

- Three protocol engines available on a per chip select basis:

- General-purpose chip select machine (GPCM)

- Three user programmable machines (UPMs)

- NAND Flash control machine (FCM)

- Variable memory block sizes for FCM, GPCM, and UPM mode

- Default boot ROM chip select with configurable bus width (8 or 16)

- Provides two Write Enable signals to allow single byte write access to external 16-bit eLBC slave devices

- Integrated programmable interrupt controller (IPIC)

- Functional and programming compatibility with the MPC8260 interrupt controller

- Support for external and internal discrete interrupt sources

- Programmable highest priority request

- Six groups of interrupts with programmable priority

- External and internal interrupts directed to host processor

- Unique vector number for each interrupt source

- Universal serial bus (USB) dual-role controller

- Designed to comply with Universal Serial Bus Revision 2.0 Specification

- Supports operation as a stand-alone USB host controller

- Supports operation as a stand-alone USB device

- Supports high-speed (480-Mbps), full-speed (12-Mbps), and low-speed (1.5-Mbps) operations. Low speed is only supported in host mode.

- Dual I<sup>2</sup>C interfaces

- Two-wire interface

- Multiple-master support

- Master or slave  $I^2C$  mode support

- On-chip digital filtering rejects spikes on the bus

- I<sup>2</sup>C1 can be used as the boot sequencer

- DMA Engine

- Support for the DMA engine with the following features:

- Sixteen DMA channels

- All data movement via dual-address transfers: read from source, write to destination

- Transfer control descriptor (TCD) organized to support two-deep, nested transfer operations

- Channel activation via one of two methods (for both the methods, one activation per execution of the minor loop is required):

- Explicit software initiation

- Initiation via a channel-to-channel linking mechanism for continuous transfers (independent channel linking at end of minor loop and/or major loop)

- Support for fixed-priority and round-robin channel arbitration

- Channel completion reported via optional interrupt requests

- Support for scatter/gather DMA processing

- DUART

- Two 2-wire interfaces (RxD, TxD)

- The same can be configured as one 4-wire interface (RxD, TxD, RTS, CTS)

- Programming model compatible with the original 16450 UART and the PC16550D

- Serial peripheral interface (SPI)

- Master or slave support

- Power managemnt controller (PMC)

- Supports core doze/nap/sleep/ power management

- Exits low power state and returns to full-on mode when

- The core internal time base unit invokes a request to exit low power state

The following table shows the estimated typical I/O power dissipation for the device.

| Table 6. Typical I/O Power Dissipation | Table 6. | . Typical I/O Power Dissipation |

|----------------------------------------|----------|---------------------------------|

|----------------------------------------|----------|---------------------------------|

| Interface                                                                                         | Parameter                                                                                             | GV <sub>DD</sub><br>(1.8 V) | OV <sub>DD</sub><br>(3.3 V) | Unit | Comments |

|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------|------|----------|

| DDR I/O<br>65% utilization<br>1.8 V<br>$R_s = 20 \Omega$<br>$R_t = 50 \Omega$<br>1 pair of clocks | 266 MHz, 1 × 16 bits                                                                                  | 0.141                       | _                           | W    | _        |

| Local bus I/O load = 25 pF<br>1 pair of clocks                                                    | 66 MHz, 26 bits                                                                                       |                             |                             |      |          |

| QUICC Engine block and other I/Os                                                                 | TDM serial, HDLC/TRAN serial,<br>DUART, MII, RMII, Ethernet<br>management, USB, SPI, Timer<br>output, |                             | 0.150                       | W    | 1        |

Note:

1. Typical I/O power is based on a nominal voltage of V<sub>DD</sub> = 3.3V, ambient temperature, and the core running a Dhrystone benchmark application. The measurements were taken on the evaluation board using WC process silicon.

# 4 Clock Input Timing

This section provides the clock input DC and AC electrical characteristics for the MPC8306S.

### NOTE

The rise/fall time on QUICC Engine input pins should not exceed 5 ns. This should be enforced especially on clock signals. Rise time refers to signal transitions from 10% to 90% of  $OV_{DD}$ ; fall time refers to transitions from 90% to 10% of  $OV_{DD}$ .

# 4.1 DC Electrical Characteristics

The following table provides the clock input (SYS\_CLK\_IN) DC specifications for the MPC8306S. These specifications are also applicable for QE\_CLK\_IN.

| Parameter                | Parameter Condition                                                                                              |                 | Min  | Max                    | Unit |

|--------------------------|------------------------------------------------------------------------------------------------------------------|-----------------|------|------------------------|------|

| Input high voltage       | -                                                                                                                | V <sub>IH</sub> | 2.4  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage        | -                                                                                                                | V <sub>IL</sub> | -0.3 | 0.4                    | V    |

| SYS_CLK_IN input current | $0~V \le V_{IN} \le OV_{DD}$                                                                                     | I <sub>IN</sub> | _    | ±5                     | μΑ   |

| SYS_CLK_IN input current | $\begin{array}{c} 0 \ V \leq V_{IN} \leq 0.5 \ V \ or \\ OV_{DD} - 0.5 \ V \leq V_{IN} \leq OV_{DD} \end{array}$ | I <sub>IN</sub> | —    | ±5                     | μΑ   |

| SYS_CLK_IN input current | $0.5~V \leq V_{IN} \leq OV_{DD} - 0.5~V$                                                                         | I <sub>IN</sub> | _    | ±50                    | μΑ   |

Table 7. SYS\_CLK\_IN DC Electrical Characteristics

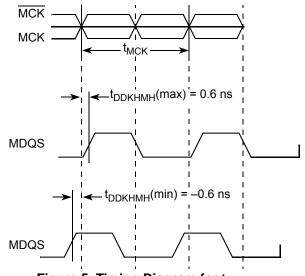

The following figure shows the DDR SDRAM output timing for the MCK to MDQS skew measurement  $(t_{DDKHMH})$ .

Figure 5. Timing Diagram for t<sub>DDKHMH</sub>

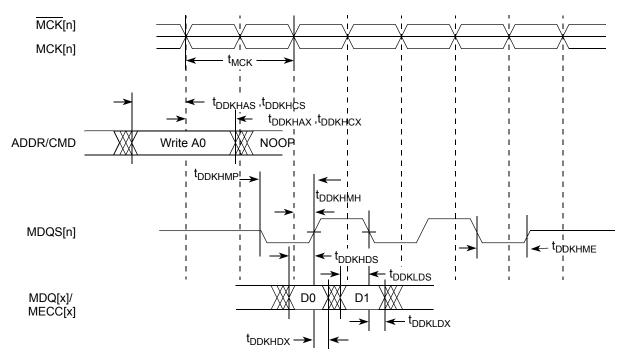

The following figure shows the DDR2 SDRAM output timing diagram.

Figure 6. DDR2 SDRAM Output Timing Diagram

#### **Ethernet and MII Management**

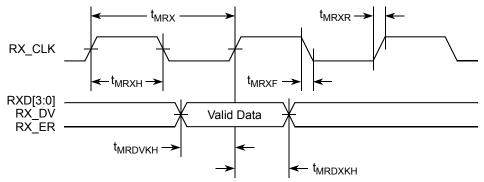

The following figure shows the MII receive AC timing diagram.

Figure 13. MII Receive AC Timing Diagram

## 8.2.2 RMII AC Timing Specifications

This section describes the RMII transmit and receive AC timing specifications.

## 8.2.2.1 RMII Transmit AC Timing Specifications

The following table provides the RMII transmit AC timing specifications.

### Table 22. RMII Transmit AC Timing Specifications

At recommended operating conditions with  $\text{OV}_{\text{DD}}$  of 3.3 V ± 300mV.

| Parameter/Condition                                                    | Symbol <sup>1</sup>                 | Min | Typical | Max | Unit |

|------------------------------------------------------------------------|-------------------------------------|-----|---------|-----|------|

| REF_CLK clock                                                          | t <sub>RMX</sub>                    | _   | 20      |     | ns   |

| REF_CLK duty cycle                                                     | t <sub>RMXH</sub> /t <sub>RMX</sub> | 35  | _       | 65  | %    |

| REF_CLK to RMII data TXD[1:0], TX_EN delay                             | t <sub>RMTKHDX</sub>                | 2   |         | 13  | ns   |

| REF_CLK data clock rise V <sub>IL</sub> (min) to V <sub>IH</sub> (max) | t <sub>RMXR</sub>                   | 1.0 | _       | 4.0 | ns   |

| REF_CLK data clock fall $V_{IH}(max)$ to $V_{IL}(min)$                 | t <sub>RMXF</sub>                   | 1.0 | _       | 4.0 | ns   |

Note:

The symbols used for timing specifications follow the pattern of t<sub>(first three letters of functional block)(signal)(state)(reference)(state)</sub> for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>RMTKHDX</sub> symbolizes RMII transmit timing (RMT) for the time t<sub>RMX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>RMX</sub> represents the RMII(RM) reference (X) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

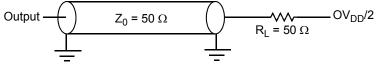

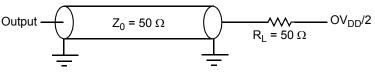

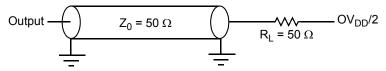

The following figure provides the AC test load.

Figure 14. AC Test Load

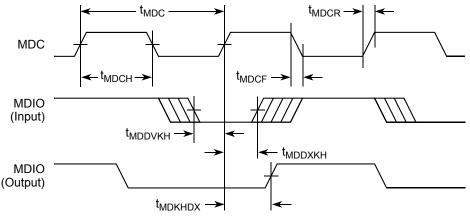

### Table 25. MII Management AC Timing Specifications (continued)

At recommended operating conditions with  $OV_{DD}$  is 3.3 V ± 300mV.

| Parameter/Condition    | Symbol <sup>1</sup> | Min | Typical | Мах | Unit | Note |

|------------------------|---------------------|-----|---------|-----|------|------|

| MDC to MDIO delay      | t <sub>MDKHDX</sub> | 10  |         | 70  | ns   | —    |

| MDIO to MDC setup time | t <sub>MDDVKH</sub> | 8.5 | _       | _   | ns   | _    |

| MDIO to MDC hold time  | t <sub>MDDXKH</sub> | 0   | _       | _   | ns   | —    |

| MDC rise time          | t <sub>MDCR</sub>   | _   | —       | 10  | ns   | —    |

| MDC fall time          | t <sub>MDHF</sub>   | _   | —       | 10  | ns   | —    |

Note:

1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MDKHDX</sub> symbolizes management data timing (MD) for the time t<sub>MDC</sub> from clock reference (K) high (H) until data outputs (D) are invalid (X) or data hold time. Also, t<sub>MDDVKH</sub> symbolizes management data timing (MD) vith respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MDC</sub> clock reference (K) going to the high (H) state or setup time. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

The following figure shows the MII management AC timing diagram.

Figure 17. MII Management Interface Timing Diagram

TDM/SI

# 9 TDM/SI

This section describes the DC and AC electrical specifications for the time-division-multiplexed and serial interface of the MPC8306S.

# 9.1 TDM/SI DC Electrical Characteristics

The following table provides the DC electrical characteristics for the MPC8306S TDM/SI.

| Table 26. TDM/SI DC Electrical Characteristics | ; |

|------------------------------------------------|---|

|------------------------------------------------|---|

| Characteristic      | Symbol          | Condition                      | Min  | Мах                    | Unit |

|---------------------|-----------------|--------------------------------|------|------------------------|------|

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = –2.0 mA      | 2.4  | —                      | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA       | _    | 0.5                    | V    |

| Input high voltage  | V <sub>IH</sub> | —                              | 2.0  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | —                              | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> | $0~V \leq V_{IN} \leq OV_{DD}$ | _    | ±5                     | μA   |

# 9.2 TDM/SI AC Timing Specifications

The following table provides the TDM/SI input and output AC timing specifications.

Table 27. TDM/SI AC Timing Specifications<sup>1</sup>

| Characteristic                                | Symbol <sup>2</sup> | Min | Max | Unit |

|-----------------------------------------------|---------------------|-----|-----|------|

| TDM/SI outputs—External clock delay           | t <sub>SEKHOV</sub> | 2   | 14  | ns   |

| TDM/SI outputs—External clock High Impedance  | t <sub>SEKHOX</sub> | 2   | 10  | ns   |

| TDM/SI inputs—External clock input setup time | t <sub>SEIVKH</sub> | 5   | _   | ns   |

| TDM/SI inputs—External clock input hold time  | t <sub>SEIXKH</sub> | 2   | _   | ns   |

Notes:

1. Output specifications are measured from the 50% level of the rising edge of QE\_CLK\_IN to the 50% level of the signal. Timings are measured at the pin.

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, t<sub>SEKHOX</sub> symbolizes the TDM/SI outputs external timing (SE) for the time t<sub>TDM/SI</sub> memory clock reference (K) goes from the high state (H) until outputs (O) are invalid (X).

</sub></sub>

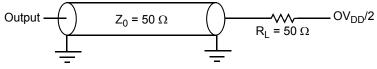

The following figure provides the AC test load for the TDM/SI.

Figure 18. TDM/SI AC Test Load

| USB |

|-----|

|-----|

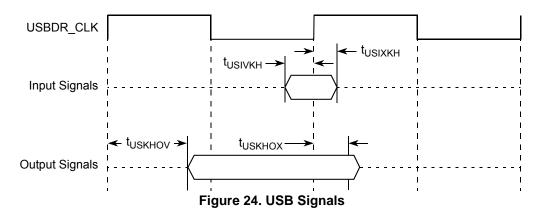

| Parameter                              | Symbol <sup>1</sup> | Min | Max | Unit | Note |

|----------------------------------------|---------------------|-----|-----|------|------|

| USB clock to output valid—USBDR_STP    | t <sub>USKHOV</sub> | _   | 7.5 | ns   | —    |

| Output hold from USB clock—all outputs | t <sub>USKHOX</sub> | 2   |     | ns   | —    |

| Table 31. USE | General | Timing | Parameters | (continued) |

|---------------|---------|--------|------------|-------------|

|---------------|---------|--------|------------|-------------|

Note:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>USIXKH</sub> symbolizes USB timing (USB) for the input (I) to go invalid (X) with respect to the time the USB clock reference (K) goes high (H). Also, t<sub>USKHOX</sub> symbolizes us timing (USB) for the USB clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

</sub>

The following figures provide the AC test load and signals for the USB, respectively.

Figure 23. USB AC Test Load

# 12 DUART

This section describes the DC and AC electrical specifications for the DUART interface of the MPC8306S.

# **12.1 DUART DC Electrical Characteristics**

The following table provides the DC electrical characteristics for the DUART interface of the MPC8306S.

| Parameter                                                                        | Symbol          | Min                    | Мах                    | Unit |

|----------------------------------------------------------------------------------|-----------------|------------------------|------------------------|------|

| High-level input voltage                                                         | V <sub>IH</sub> | 2                      | OV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage OV <sub>DD</sub>                                         | V <sub>IL</sub> | -0.3                   | 0.8                    | V    |

| High-level output voltage, I <sub>OH</sub> = –100 μA                             | V <sub>OH</sub> | OV <sub>DD</sub> – 0.2 | —                      | V    |

| Low-level output voltage, I <sub>OL</sub> = 100 μA                               | V <sub>OL</sub> | —                      | 0.2                    | V    |

| Input current (0 V $\leq$ V <sub>IN</sub> $\leq$ OV <sub>DD</sub> ) <sup>1</sup> | I <sub>IN</sub> | _                      | ±5                     | μA   |

### Table 32. DUART DC Electrical Characteristics

Note:

1. Note that the symbol  $V_{IN}$ , in this case, represents the  $OV_{IN}$  symbol referenced in Table 1 and Table 2.

# 12.2 DUART AC Electrical Specifications

The following table provides the AC timing parameters for the DUART interface of the MPC8306S.

### Table 33. DUART AC Timing Specifications

| Parameter         | Value      | Unit | Note |

|-------------------|------------|------|------|

| Minimum baud rate | 256        | baud | —    |

| Maximum baud rate | >1,000,000 | baud | 1    |

| Oversample rate   | 16         | _    | 2    |

Notes:

1. Actual attainable baud rate is limited by the latency of interrupt processing.

2. The middle of a start bit is detected as the 8<sup>th</sup> sampled 0 after the 1-to-0 transition of the start bit. Subsequent bit values are sampled each 16<sup>th</sup> sample.

| Characteristic      | Symbol          | Condition                    | Min  | Max                    | Unit |

|---------------------|-----------------|------------------------------|------|------------------------|------|

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -6.0 mA    | 2.4  | —                      | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 6.0 mA     | _    | 0.5                    | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA     | _    | 0.4                    | V    |

| Input high voltage  | V <sub>IH</sub> | —                            | 2.0  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | _                            | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> | $0~V \le V_{IN} \le OV_{DD}$ | _    | ±5                     | μA   |

### **Table 42. SPI DC Electrical Characteristics**

# 17.2 SPI AC Timing Specifications

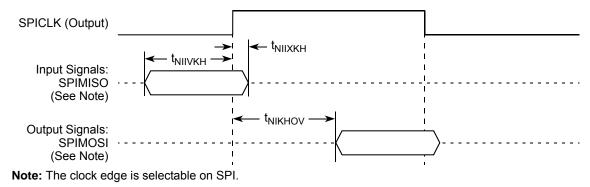

The following table and provide the SPI input and output AC timing specifications.

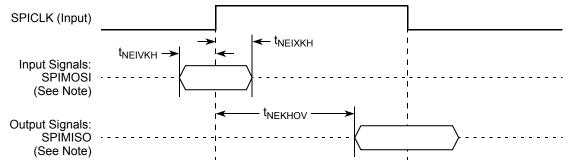

Table 43. SPI AC Timing Specifications<sup>1</sup>

| Characteristic                                           | Symbol <sup>2</sup> | Min | Max | Unit |

|----------------------------------------------------------|---------------------|-----|-----|------|

| SPI outputs—Master mode (internal clock) delay           | t <sub>NIKHOV</sub> | 0.5 | 6   | ns   |

| SPI outputs—Slave mode (external clock) delay            | t <sub>NEKHOV</sub> | 2   | 8   | ns   |

| SPI inputs—Master mode (internal clock) input setup time | t <sub>NIIVKH</sub> | 6   | —   | ns   |

| SPI inputs—Master mode (internal clock) input hold time  | t <sub>NIIXKH</sub> | 0   | —   | ns   |

| SPI inputs—Slave mode (external clock) input setup time  | t <sub>NEIVKH</sub> | 4   | —   | ns   |

| SPI inputs—Slave mode (external clock) input hold time   | t <sub>NEIXKH</sub> | 2   | —   | ns   |

Notes:

1. Output specifications are measured from the 50% level of the rising edge of SPICLK to the 50% level of the signal. Timings are measured at the pin.

2. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, t<sub>NIKHOV</sub> symbolizes the NMSI outputs internal timing (NI) for the time t<sub>SPI</sub> memory clock reference (K) goes from the high state (H) until outputs (O) are valid (V).</sub></sub>

3. All units of output delay must be enabled for 8306S output port spimosi (SPI Master Mode)

4. delay units must not be enabled for Slave Mode.

The following figure provides the AC test load for the SPI.

Figure 29. SPI AC Test Load

Figure 30 and Figure 31 represent the AC timing from Table 43. Note that although the specifications generally reference the rising edge of the clock, these AC timing diagrams also apply when the falling edge is the active edge.

### JTAG

The following figure shows the SPI timing in slave mode (external clock).

Note: The clock edge is selectable on SPI.

The following figure shows the SPI timing in master mode (internal clock).

Figure 31. SPI AC Timing in Master Mode (Internal Clock) Diagram

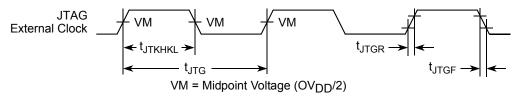

# 18 JTAG

This section describes the DC and AC electrical specifications for the IEEE Std. 1149.1<sup>™</sup> (JTAG) interface of the MPC8306S.

# **18.1 JTAG DC Electrical Characteristics**

The following table provides the DC electrical characteristics for the IEEE Std. 1149.1 (JTAG) interface of the MPC8306S.

| Characteristic      | Symbol          | Condition                 | Min | Мах | Unit |

|---------------------|-----------------|---------------------------|-----|-----|------|

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -6.0 mA | 2.4 | _   | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 6.0 mA  | _   | 0.5 | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA  | _   | 0.4 | V    |

Table 44. JTAG Interface DC Electrical Characteristics

#### JTAG

### Table 45. JTAG AC Timing Specifications (Independent of SYS\_CLK\_IN)<sup>1</sup> (continued)

At recommended operating conditions (see Table 2).

| Parameter                                                                  | Symbol <sup>2</sup>                        | Min    | Max     | Unit | Notes     |

|----------------------------------------------------------------------------|--------------------------------------------|--------|---------|------|-----------|

| Output hold times:<br>Boundary-scan data<br>TDO                            | t <sub>JTKLDX</sub><br>t <sub>JTKLOX</sub> | 2<br>2 |         | ns   | 5         |

| JTAG external clock to output high impedance:<br>Boundary-scan data<br>TDO | t <sub>jtkldz</sub><br>t <sub>jtkloz</sub> | 2<br>2 | 19<br>9 | ns   | 5, 6<br>6 |

#### Notes:

- 1. All outputs are measured from the midpoint voltage of the falling/rising edge of  $t_{TCLK}$  to the midpoint of the signal in question. The output timings are measured at the pins. All output timings assume a purely resistive 50- $\Omega$  load (see Figure 32). Time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

- 2. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>JTDVKH</sub> symbolizes JTAG device timing (JT) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>JTDXKH</sub> symbolizes JTAG timing (JT) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

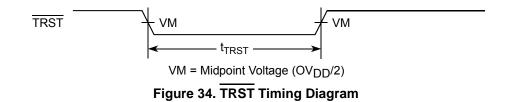

- 3. TRST is an asynchronous level sensitive signal. The setup time is for test purposes only.

- 4. Non-JTAG signal input timing with respect to t<sub>TCLK</sub>.

- 5. Non-JTAG signal output timing with respect to  $t_{TCLK}$ .

- 6. Guaranteed by design and characterization.

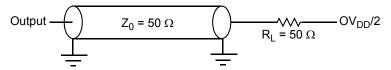

The following figure provides the AC test load for TDO and the boundary-scan outputs of the MPC8306S.

Figure 32. AC Test Load for the JTAG Interface

The following figure provides the JTAG clock input timing diagram.

Figure 33. JTAG Clock Input Timing Diagram

The following figure provides the  $\overline{\text{TRST}}$  timing diagram.

| Table 46. MPC8306S | Pinout Listing (continued) |

|--------------------|----------------------------|

|--------------------|----------------------------|

| Signal                               | Package Pin Number | Pin Type | Power Supply     | Notes |

|--------------------------------------|--------------------|----------|------------------|-------|

| USBDR_TXDRXD[7]/GPIO[37]/QE_BRG[11]  | Y5                 | IO       | OV <sub>DD</sub> |       |

|                                      | DUART              |          |                  | 1     |

| UART1_SOUT[1]/LSRCID4/LCS_B[4]       | C23                | 0        | OV <sub>DD</sub> |       |

| UART1_SIN[1]/LDVAL/LCS_B[5]          | F19                | IO       | OV <sub>DD</sub> |       |

| UART1_SOUT[2]/UART1_RTS_B1/LCS_B[6]  | D23                | 0        | OV <sub>DD</sub> |       |

| UART1_SIN[2]/UART1_CTS_B[1]/LCS_B[7] | D22                | IO       | OV <sub>DD</sub> |       |

|                                      | Interrupts         |          |                  | 1     |

| IRQ_B0_MCP_IN_B/CE_PI_0              | E20                | IO       | OV <sub>DD</sub> |       |

| IRQ_B1/MCP_OUT_B                     | E23                | IO       | OV <sub>DD</sub> |       |

| IRQ_B2/CKSTOP_OUT_B                  | E22                | IO       | OV <sub>DD</sub> |       |

| IRQ_B3/CKSTOP_IN_B                   | F20                | I        | OV <sub>DD</sub> |       |

|                                      | 12C / SPI          |          |                  |       |

| IIC_SDA1                             | G20                | IO       | OV <sub>DD</sub> | 2     |

| IIC_SCL1                             | J20                | IO       | OV <sub>DD</sub> | 2     |

| LCLK1/IIC_SCL2/CKSTOP_IN_B           | H20                | IO       | OV <sub>DD</sub> | 2     |

| SPISEL_BOOT/IIC_SDA2/CKSTOP_OUT_B    | F23                | 0        | OV <sub>DD</sub> | 2     |

| SPIMOSI/LSRCID[2]                    | G22                | IO       | OV <sub>DD</sub> |       |

| SPIMISO/LSRCID[3]                    | K20                | IO       | OV <sub>DD</sub> | —     |

| SPICLK/LSRCID[0]                     | G23                | IO       | OV <sub>DD</sub> |       |

| SPISEL/LSRCID[1]                     | H22                | Ι        | OV <sub>DD</sub> |       |

|                                      | FEC Management     |          |                  |       |

| FEC_MDC                              | H23                | 0        | OV <sub>DD</sub> | _     |

| FEC_MDIO                             | L20                | IO       | OV <sub>DD</sub> |       |

|                                      | FEC1/GTM/GPIO      |          |                  |       |

| FEC1_COL/GTM1_TIN[1]/GPIO[16]        | AB20               | IO       | OV <sub>DD</sub> | _     |

| FEC1_CRS/GTM1_TGATE1_B/GPIO[17]      | AC21               | IO       | OV <sub>DD</sub> |       |

| FEC1_RX_CLK/GPIO[18]                 | Y17                | IO       | OV <sub>DD</sub> |       |

| FEC1_RX_DV/GTM1_TIN[2]/GPIO[19]      | Y18                | IO       | OV <sub>DD</sub> |       |

| FEC1_RX_ER/GTM1_TGATE[2]_B/GPIO[20]  | AB19               | Ю        | OV <sub>DD</sub> |       |

| FEC1_RXD0/GPIO[21]                   | AC20               | 10       | OV <sub>DD</sub> | —     |

| FEC1_RXD1/GTM1_TIN[3]/GPIO[22]       | AC19               | 10       | OV <sub>DD</sub> | —     |

| FEC1_RXD2/GTM1_TGATE[3]_B/GPIO[23]   | AC18               | 10       | OV <sub>DD</sub> | —     |

| FEC1_RXD3/GPIO[24]                   | AB17               | Ю        | OV <sub>DD</sub> |       |

| FEC1_TX_CLK/GTM1_TIN4/GPIO[25]       | Y15                | 10       | OV <sub>DD</sub> |       |

| FEC1_TX_EN/GTM1_TGATE[4]_B/GPIO[26]  | Y16                | IO       | OV <sub>DD</sub> | —     |

| Table 46. MPC8306S | Pinout Listing (continued) |

|--------------------|----------------------------|

|--------------------|----------------------------|

| Signal                               | Package Pin Number | Pin Type | Power Supply     | Notes |

|--------------------------------------|--------------------|----------|------------------|-------|

| FEC1_TX_ER/GTM1_TOUT[4]_B/GPIO[27]   | AC17               | IO       | OV <sub>DD</sub> | _     |

| FEC1_TXD0/GTM1_TOUT[1]_B/GPIO[28]    | AB16               | IO       | OV <sub>DD</sub> | —     |

| FEC1_TXD1/GTM1_TOUT[2]_B/GPIO[29]    | AC16               | IO       | OV <sub>DD</sub> |       |

| FEC1_TXD2/GTM1_TOUT[3]_B/GPIO[30]    | AC15               | IO       | OV <sub>DD</sub> | _     |

| FEC1_TXD3/GPIO[31]                   | AB14               | IO       | OV <sub>DD</sub> |       |

|                                      | FEC2/GPIO          |          |                  |       |

| FEC2_COL/GPIO[32]                    | AC14               | IO       | OV <sub>DD</sub> | _     |

| FEC2_CRS/GPIO[33]                    | AB13               | IO       | OV <sub>DD</sub> |       |

| FEC2_RX_CLK/GPIO[34]                 | Y14                | IO       | OV <sub>DD</sub> |       |

| FEC2_RX_DV/GPIO[35]                  | AC13               | IO       | OV <sub>DD</sub> |       |

| FEC2_RX_ER/GPIO[36]                  | Y13                | IO       | OV <sub>DD</sub> |       |

| FEC2_RXD0/GPIO[37]                   | AC12               | IO       | OV <sub>DD</sub> |       |

| FEC2_RXD1/GPIO[38]                   | AB11               | IO       | OV <sub>DD</sub> |       |

| FEC2_RXD2/GPIO[39]                   | AC11               | IO       | OV <sub>DD</sub> |       |

| FEC2_RXD3/GPIO[40]                   | AB10               | IO       | OV <sub>DD</sub> |       |

| FEC2_TX_CLK/GPIO[41]                 | Y12                | IO       | OV <sub>DD</sub> |       |

| FEC2_TX_EN/GPIO[42]                  | AC10               | IO       | OV <sub>DD</sub> |       |

| FEC2_TX_ER/GPIO[43]                  | AC9                | IO       | OV <sub>DD</sub> |       |

| FEC2_TXD0/GPIO[44]                   | AC8                | IO       | OV <sub>DD</sub> | —     |

| FEC2_TXD1/GPIO[45]                   | Y11                | IO       | OV <sub>DD</sub> | —     |

| FEC2_TXD2/GPIO[46]                   | AC7                | IO       | OV <sub>DD</sub> |       |

| FEC2_TXD3/GPIO[47]                   | Y10                | IO       | OV <sub>DD</sub> |       |

|                                      | FEC3/GPIO          |          | 1                |       |

| FEC3_COL/GPIO[48]                    | J23                | IO       | OV <sub>DD</sub> |       |

| FEC3_CRS/GPIO[49]                    | K23                | IO       | OV <sub>DD</sub> |       |

| FEC3_RX_CLK/GPIO[50]                 | M20                | IO       | OV <sub>DD</sub> |       |

| FEC3_RX_DV/FEC1_TMR_TX_ESFD/GPIO[51] | K22                | IO       | OV <sub>DD</sub> |       |

| FEC3_RX_ER/FEC1_TMR_RX_ESFD/GPIO[52] | L22                | IO       | OV <sub>DD</sub> |       |

| FEC3_RXD0/FEC2_TMR_TX_ESFD/GPIO[53]  | L23                | IO       | OV <sub>DD</sub> | —     |

| FEC3_RXD1/FEC2_TMR_RX_ESFD/GPIO[54]  | M23                | IO       | OV <sub>DD</sub> | —     |

| FEC3_RXD2/TSEC_TMR_TRIG1/GPIO[55]    | N22                | IO       | OV <sub>DD</sub> | —     |

| FEC3_RXD3/TSEC_TMR_TRIG2/GPIO[56]    | N23                | Ю        | OV <sub>DD</sub> | —     |

| FEC3_TX_CLK/TSEC_TMR_CLK/GPIO[57]    | N20                | IO       | OV <sub>DD</sub> | —     |

| FEC3_TX_EN/TSEC_TMR_GCLK/GPIO[58]    | P20                | Ю        | OV <sub>DD</sub> | —     |

| FEC3_TX_ER/TSEC_TMR_PP1/GPIO[59]     | P22                | IO       | OV <sub>DD</sub> | —     |

## Table 46. MPC8306S Pinout Listing (continued)

| Signal                                                     | Package Pin Number                                                                                                                                            | Pin Type | Power Supply     | Notes |

|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|-------|

| FEC3_TXD0/TSEC_TMR_PP2/GPIO[60]                            | R20                                                                                                                                                           | IO       | OV <sub>DD</sub> | _     |

| FEC3_TXD1/TSEC_TMR_PP3/GPIO[61]                            | T22                                                                                                                                                           | IO       | OV <sub>DD</sub> |       |

| FEC3_TXD2/TSEC_TMR_ALARM1/GPIO[62]                         | T23                                                                                                                                                           | IO       | OV <sub>DD</sub> |       |

| FEC3_TXD3/TSEC_TMR_ALARM2/GPIO[63]                         | T20                                                                                                                                                           | IO       | OV <sub>DD</sub> | —     |

|                                                            | HDLC/GPIO/TDM                                                                                                                                                 |          | 1                |       |

| HDLC1_RXCLK/TDM1_RCK/GPIO[1]                               | U23                                                                                                                                                           | IO       | OV <sub>DD</sub> |       |

| HDLC1_RXD/TDM1_RD/GPIO[3]                                  | U22                                                                                                                                                           | IO       | OV <sub>DD</sub> |       |

| HDLC1_TXCLK/GPIO[0]/TDM1_TCK/<br>QE_BRG[5]                 | AC22                                                                                                                                                          | IO       | OV <sub>DD</sub> | -     |

| HDLC1_TXD/GPIO[2]/TDM1_TD/<br>CFG_RESET_SOURCE[0]          | W18                                                                                                                                                           | IO       | OV <sub>DD</sub> | —     |

| HDLC1_CD_B/GPIO[4]/TDM1_TFS                                | W19                                                                                                                                                           | IO       | OV <sub>DD</sub> | —     |

| HDLC1_CTS_B/GPIO[5]/TDM1_RFS                               | Y20                                                                                                                                                           | IO       | OV <sub>DD</sub> | —     |

| HDLC1_RTS_B/GPIO[6]/TDM1_STROBE_B/<br>CFG_RESET_SOURCE[1]  | AB22                                                                                                                                                          | Ю        | OV <sub>DD</sub> | —     |

| HDLC2_TXCLK/GPIO[16]/TDM2_TCK/<br>QE_BRG[7]                | AB23                                                                                                                                                          | IO       | OV <sub>DD</sub> | —     |

| HDLC2_RXCLK/GPIO[17]/TDM2_RCK/<br>QE_BRG[8]                | AA23                                                                                                                                                          | IO       | OV <sub>DD</sub> | —     |

| HDLC2_TXD/GPIO[18]/TDM2_TD/<br>CFG_RESET_SOURCE[2]         | W20                                                                                                                                                           | IO       | OV <sub>DD</sub> | —     |

| HDLC2_RXD/GPIO[19]/TDM2_RD                                 | Y23                                                                                                                                                           | IO       | OV <sub>DD</sub> |       |

| HDLC2_CD_B/GPIO[20]/TDM2_TFS                               | Y22                                                                                                                                                           | IO       | OV <sub>DD</sub> |       |

| HDLC2_CTS_B/GPI0[21]/TDM2_RFS                              | W23                                                                                                                                                           | IO       | OV <sub>DD</sub> | —     |

| HDLC2_RTS_B/GPIO[22]/TDM2_STROBE_B/<br>CFG_RESET_SOURCE[3] | W22                                                                                                                                                           | IO       | OV <sub>DD</sub> | _     |

|                                                            | Power                                                                                                                                                         |          |                  | 1     |

| AV <sub>DD1</sub>                                          | L16                                                                                                                                                           | —        | —                | —     |

| AV <sub>DD2</sub>                                          | M16                                                                                                                                                           | _        | —                | —     |

| AV <sub>DD3</sub>                                          | N8                                                                                                                                                            | —        | —                | —     |

| GV <sub>DD</sub>                                           | G5, H5, J5, K5, L5, M5,<br>N5, P5, R5, T5, U5                                                                                                                 | _        | _                | —     |

| OV <sub>DD</sub>                                           | E7,E8,E9,E10,E11,E12,<br>E13,E14, E15,<br>E16,E17,G19,H19,J19,K<br>19,L19,M19,<br>N19,P19,R19,T19,U19,<br>W7,W8,W9, W10,W11,<br>W12,W13, W14,W15,<br>W16, W17 | _        | _                | _     |

Package and Pin Listings

| Signal                                                                                                                                                                | Package Pin Number                                                                                                                                                                                                                                                                                                                                                                                           | Pin Type | Power Supply | Notes |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------|-------|

| V <sub>DD</sub>                                                                                                                                                       | H8,H9,H10,H11,H12,H1<br>3,H14,H15,H16,J8,J16,K<br>8,K16,M8,N16,P8,P16,R<br>8,R16,T8,T9,T10,T11,T1<br>2,T13,T14,T15,T16                                                                                                                                                                                                                                                                                       | _        | _            | —     |

| VSS                                                                                                                                                                   | A1,B4,B6,B9,B12,B15,B<br>18,B21,C22,D2,D5,D18,<br>D20,F2,F22,J2,J9,J10,J<br>11,J12,J13,J14,J15,J22,<br>K4,K9,K10,K11,K12,K13<br>,K14,K15,L9,L10,L11,L1<br>2,L13,L14,L15,M2,M9,M<br>10,M11,M12,M13,M14,M<br>15,M22,N9,N10,N11,N1<br>2,N13,N14,N15,P9,P10,<br>P11,P12,P13,P14,P15,R<br>2,R9,R10,R11,R12,R13,<br>R14,R15,R22,T4,V2,V19<br>,V22,W4,Y19,AA2,AA22,<br>AB4,AB6,AB9,AB12,AB1<br>5,AB18,AB21,AC1,AC23 | _        |              | _     |

| NC                                                                                                                                                                    | A23                                                                                                                                                                                                                                                                                                                                                                                                          | —        |              | —     |

| <b>Notes</b><br>1. This pin is an open drain signal. A weak pul<br>2. This pin is an open drain signal. A weak pul<br>3. This pin has weak pull-up that is always end | I-up resistor (2-10 k $\Omega$ ) should be                                                                                                                                                                                                                                                                                                                                                                   |          |              |       |

## Table 46. MPC8306S Pinout Listing (continued)

| RCWL[CEPMF] | RCWL[CEPDF] | QUICC Engine PLL Multiplication Factor = RCWL[CEPMF]/<br>(1 + RCWL[CEPDF) |

|-------------|-------------|---------------------------------------------------------------------------|

| 00111       | 0           | × 7                                                                       |

| 01000       | 0           | × 8                                                                       |

| 01001–11111 | 0           | Reserved                                                                  |

The RCWL[CEVCOD] denotes the QUICC Engine PLL VCO internal frequency as shown in the following table.

Table 53. QUICC Engine PLL VCO Divider

| RCWL[CEVCOD] | VCO Divider |

|--------------|-------------|

| 00           | 2           |

| 01           | 4           |

| 10           | 8           |

| 11           | Reserved    |

### NOTE

The VCO divider (RCWL[CEVCOD]) must be set properly so that the QUICC Engine VCO frequency is in the range of 300–600 MHz. The QUICC Engine frequency is not restricted by the CSB and core frequencies. The CSB, core, and QUICC Engine frequencies should be selected according to the performance requirements.

The QUICC Engine VCO frequency is derived from the following equations:

$qe\_clk = (primary clock input \times CEPMF) \div (1 + CEPDF)$

QUICC Engine VCO Frequency =  $qe_{clk} \times VCO$  divider  $\times (1 + CEPDF)$

## 20.5 Suggested PLL Configurations

To simplify the PLL configurations, the MPC8306S might be separated into two clock domains. The first domain contains the CSB PLL and the core PLL. The core PLL is connected serially to the CSB PLL, and has the csb\_clk as its input clock. The second clock domain has the QUICC Engine PLL. The clock domains are independent, and each of their PLLs is configured separately.

The following table shows suggested PLL configurations for 33 and 66 MHz input clocks.

# 24 Document Revision History

The following table provides a revision history for this document.

| Rev.<br>No. | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | 09/2011 | <ul> <li>Added Power numbers for core frequency of 333 MHz in Table 5.</li> <li>Updated QUICC Engine frequency in Table 5.</li> <li>Added SPISEL_BOOT in MPC8306 Pin out Listing Table 46.</li> <li>Corrected SPISEL Pin Type in Table 46</li> <li>Updated QUICC Engine frequency from 200 MHz to 233 MHz in Table 48.</li> <li>Added new PLL configurations as per new core frequency in Table 54.</li> <li>Updated CEPMF and CEDF as per new QE frequency in Table 54.</li> <li>Added AF to indicate 333 MHz in Table 57</li> <li>Updated QE Frequency to 233 MHz in Table 57.</li> </ul> |

| 0           | 03/2011 | Initial Release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

### Table 59. Document Revision History