Welcome to **E-XFL.COM**

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                              |

|---------------------------------|--------------------------------------------------------------|

| Product Status                  | Active                                                       |

| Core Processor                  | PowerPC e300c3                                               |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                               |

| Speed                           | 266MHz                                                       |

| Co-Processors/DSP               | Communications; QUICC Engine                                 |

| RAM Controllers                 | DDR2                                                         |

| Graphics Acceleration           | No                                                           |

| Display & Interface Controllers | -                                                            |

| Ethernet                        | 10/100Mbps (3)                                               |

| SATA                            | -                                                            |

| USB                             | USB 2.0 (1)                                                  |

| Voltage - I/O                   | 1.8V, 3.3V                                                   |

| Operating Temperature           | 0°C ~ 105°C (TA)                                             |

| Security Features               | -                                                            |

| Package / Case                  | 369-LFBGA                                                    |

| Supplier Device Package         | 369-PBGA (19x19)                                             |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8306svmaddca |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 1. Absolute Maximum Ratings<sup>1</sup> (continued)

| Characteristic            |                                                                                                            | Symbol           | Max Value                        | Unit | Notes |

|---------------------------|------------------------------------------------------------------------------------------------------------|------------------|----------------------------------|------|-------|

| Input voltage             | DDR2 DRAM signals                                                                                          | $MV_{IN}$        | -0.3 to (GV <sub>DD</sub> + 0.3) | V    | 3     |

|                           | DDR2 DRAM reference                                                                                        | $MV_REF$         | -0.3 to (GV <sub>DD</sub> + 0.3) | V    | 3     |

|                           | Local bus, DUART, SYS_CLK_IN, system control and power management, I <sup>2</sup> C, SPI, and JTAG signals | OV <sub>IN</sub> | -0.3 to (OV <sub>DD</sub> + 0.3) | V    | 4     |

| Storage temperature range | ge                                                                                                         | T <sub>STG</sub> | -55 to 150                       | °C   | _     |

#### Notes:

- 1. Functional and tested operating conditions are given in Table 2. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

- 2. OVDD here refers to NVDDA, NVDDB, NVDDC, NVDDF, NVDDG, and NVDDH from the ball map.

- 3. Caution:  $MV_{IN}$  must not exceed  $GV_{DD}$  by more than 0.3 V. This limit may be exceeded for a maximum of 100 ms during power-on reset and power-down sequences.

- 4. Caution:  $OV_{IN}$  must not exceed  $OV_{DD}$  by more than 0.3 V. This limit may be exceeded for a maximum of 100 ms during power-on reset and power-down sequences.

### 2.1.3 Output Driver Characteristics

The following table provides information on the characteristics of the output driver strengths.

**Table 3. Output Drive Capability**

| Driver Type                           | Output Impedance (Ω) | Supply Voltage (V)     |

|---------------------------------------|----------------------|------------------------|

| Local bus interface utilities signals | 42                   | OV <sub>DD</sub> = 3.3 |

| DDR2 signal                           | 18                   | GV <sub>DD</sub> = 1.8 |

| DUART, system control, I2C, SPI, JTAG | 42                   | OV <sub>DD</sub> = 3.3 |

| GPIO signals                          | 42                   | OV <sub>DD</sub> = 3.3 |

### 2.1.4 Input Capacitance Specification

The following table describes the input capacitance for the SYS\_CLK\_IN pin in the MPC8306S.

**Table 4. Input Capacitance Specification**

| Parameter/Condition                                            | Symbol               | Min | Max | Unit | Note |

|----------------------------------------------------------------|----------------------|-----|-----|------|------|

| Input capacitance for all pins except SYS_CLK_IN and QE_CLK_IN | C <sub>I</sub>       | 6   | 8   | pF   | _    |

| Input capacitance for SYS_CLK_IN and QE_CLK_IN                 | C <sub>ICLK_IN</sub> | 10  | _   | pF   | 1    |

#### Note:

### 2.2 Power Sequencing

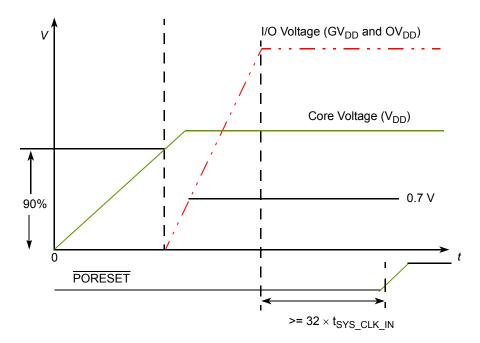

The device does not require the core supply voltage ( $V_{DD}$ ) and I/O supply voltages ( $GV_{DD}$  and  $OV_{DD}$ ) to be applied in any particular order. Note that during power ramp-up, before the power supplies are stable and if the I/O voltages are supplied before the core voltage, there might be a period of time that all input and output pins are actively driven and cause contention and excessive current. In order to avoid actively driving the I/O pins and to eliminate excessive current draw, apply the core voltage ( $V_{DD}$ ) before the I/O voltage ( $V_{DD}$ ) and assert  $\overline{V_{DD}}$  and  $\overline{V_{DD}}$  and assert  $\overline{V_{DD}}$  before the power supplies fully ramp up. In the case where the core voltage is applied first, the core voltage supply must rise to 90% of its nominal value before the I/O supplies reach 0.7 V; see Figure 3. Once both the power supplies (I/O voltage and core voltage) are stable, wait for a minimum of 32 clock cycles before negating  $\overline{V_{DD}}$

### NOTE

There is no specific power down sequence requirement for the device. I/O voltage supplies ( $GV_{DD}$  and  $OV_{DD}$ ) do not have any ordering requirements with respect to one another.

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

<sup>1.</sup> The external clock generator should be able to drive 10 pF.

#### **Power Characteristics**

Figure 3. MPC8306S Power-Up Sequencing Example

## 3 Power Characteristics

The typical power dissipation for this family of MPC8306S devices is shown in the following table.

| Core<br>Frequency (MHz) | QUICC Engine<br>Frequency (MHz) | CSB<br>Frequency (MHz) | Typical | Maximum | Unit | Note    |

|-------------------------|---------------------------------|------------------------|---------|---------|------|---------|

| 133                     | 133                             | 133                    | 0.272   | 0.618   | W    | 1, 2, 3 |

| 200                     | 233                             | 133                    | 0.291   | 0.631   | W    | 1, 2, 3 |

| 266                     | 233                             | 133                    | 0.451   | 0.925   | W    | 1, 2, 3 |

| 333                     | 233                             | 133                    | 0.471   | 0.950   | W    | 1, 2, 3 |

Table 5. MPC8306S Power Dissipation

#### Notes:

- 1. The values do not include I/O supply power (OV<sub>DD</sub> and GV<sub>DD</sub>), but it does include V<sub>DD</sub> and AV<sub>DD</sub> power. For I/O power values, see Table 6.

- 2. Typical power is based on a nominal voltage of  $V_{DD}$  = 1.0 V, ambient temperature, and the core running a Dhrystone benchmark application. The measurements were taken on the evaluation board using WC process silicon.

- 3. Maximum power is based on a voltage of  $V_{DD}$  = 1.05 V, WC process, a junction  $T_J$  = 105°C, and a smoke test code.

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

The following table shows the estimated typical I/O power dissipation for the device.

Table 6. Typical I/O Power Dissipation

| Interface                                                                          | Parameter                                                                                             | GV <sub>DD</sub><br>(1.8 V) | OV <sub>DD</sub><br>(3.3 V) | Unit | Comments |

|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------|------|----------|

| DDR I/O 65% utilization 1.8 V $R_s = 20 \Omega$ $R_t = 50 \Omega$ 1 pair of clocks | 266 MHz, 1 × 16 bits                                                                                  | 0.141                       | _                           | W    | _        |

| Local bus I/O load = 25 pF<br>1 pair of clocks                                     | 66 MHz, 26 bits                                                                                       |                             |                             |      |          |

| QUICC Engine block and other I/Os                                                  | TDM serial, HDLC/TRAN serial,<br>DUART, MII, RMII, Ethernet<br>management, USB, SPI, Timer<br>output, | ı                           | 0.150                       | W    | 1        |

#### Note:

# 4 Clock Input Timing

This section provides the clock input DC and AC electrical characteristics for the MPC8306S.

#### NOTE

The rise/fall time on QUICC Engine input pins should not exceed 5 ns. This should be enforced especially on clock signals. Rise time refers to signal transitions from 10% to 90% of  $OV_{DD}$ ; fall time refers to transitions from 90% to 10% of  $OV_{DD}$ .

### 4.1 DC Electrical Characteristics

The following table provides the clock input (SYS\_CLK\_IN) DC specifications for the MPC8306S. These specifications are also applicable for QE\_CLK\_IN.

Table 7. SYS\_CLK\_IN DC Electrical Characteristics

| Parameter                | Condition                                                                                                                                                    | Symbol          | Min  | Max                    | Unit |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|------------------------|------|

| Input high voltage       | _                                                                                                                                                            | V <sub>IH</sub> | 2.4  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage        | _                                                                                                                                                            | V <sub>IL</sub> | -0.3 | 0.4                    | V    |

| SYS_CLK_IN input current | $0 \text{ V} \leq V_{IN} \leq OV_{DD}$                                                                                                                       | I <sub>IN</sub> | _    | ±5                     | μΑ   |

| SYS_CLK_IN input current | $\begin{array}{c} 0 \text{ V} \leq \text{V}_{IN} \leq 0.5 \text{ V or} \\ \text{OV}_{DD} - 0.5 \text{ V} \leq \text{V}_{IN} \leq \text{OV}_{DD} \end{array}$ | I <sub>IN</sub> | _    | ±5                     | μΑ   |

| SYS_CLK_IN input current | $0.5 \text{ V} \le V_{IN} \le OV_{DD} - 0.5 \text{ V}$                                                                                                       | I <sub>IN</sub> | _    | ±50                    | μΑ   |

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

<sup>1.</sup> Typical I/O power is based on a nominal voltage of V<sub>DD</sub> = 3.3V, ambient temperature, and the core running a Dhrystone benchmark application. The measurements were taken on the evaluation board using WC process silicon.

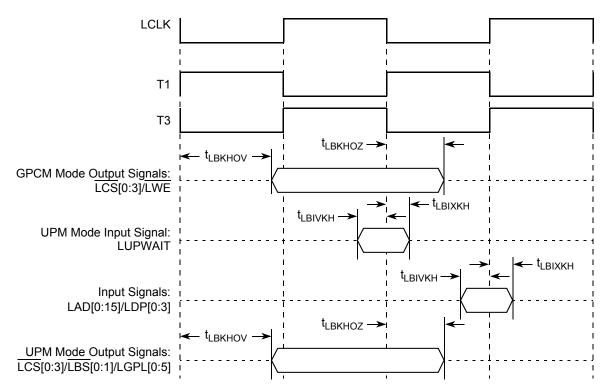

Figure 9. Local Bus Signals, GPCM/UPM Signals for LCRR[CLKDIV] = 2

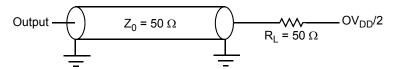

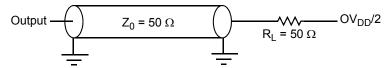

The following figure provides the AC test load.

Figure 11. AC Test Load

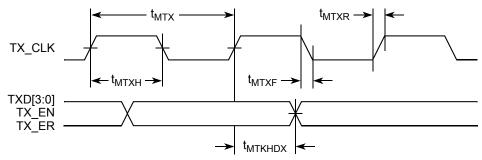

The following figure shows the MII transmit AC timing diagram.

Figure 12. MII Transmit AC Timing Diagram

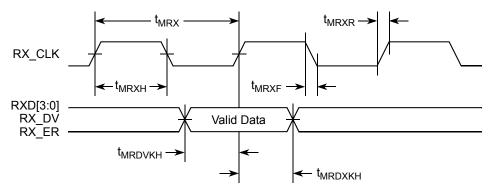

### 8.2.1.2 MII Receive AC Timing Specifications

The following table provides the MII receive AC timing specifications.

### **Table 21. MII Receive AC Timing Specifications**

At recommended operating conditions with OV<sub>DD</sub> of 3.3 V ± 300mV.

| Parameter/Condition                                                   | Symbol <sup>1</sup>                 | Min  | Typical | Max | Unit |

|-----------------------------------------------------------------------|-------------------------------------|------|---------|-----|------|

| RX_CLK clock period 10 Mbps                                           | t <sub>MRX</sub>                    | _    | 400     | _   | ns   |

| RX_CLK clock period 100 Mbps                                          | t <sub>MRX</sub>                    | _    | 40      | _   | ns   |

| RX_CLK duty cycle                                                     | t <sub>MRXH</sub> /t <sub>MRX</sub> | 35   | _       | 65  | %    |

| RXD[3:0], RX_DV, RX_ER setup time to RX_CLK                           | t <sub>MRDVKH</sub>                 | 10.0 | _       | _   | ns   |

| RXD[3:0], RX_DV, RX_ER hold time to RX_CLK                            | t <sub>MRDXKH</sub>                 | 10.0 | _       | _   | ns   |

| RX_CLK clock rise V <sub>IL</sub> (min) to V <sub>IH</sub> (max)      | t <sub>MRXR</sub>                   | 1.0  | _       | 4.0 | ns   |

| RX_CLK clock fall time V <sub>IH</sub> (max) to V <sub>IL</sub> (min) | t <sub>MRXF</sub>                   | 1.0  | _       | 4.0 | ns   |

#### Note:

1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MRDVKH</sub> symbolizes MII receive timing (MR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>MRDXKL</sub> symbolizes MII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>MRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>MRX</sub> represents the MII (M) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

#### **Ethernet and MII Management**

The following figure shows the MII receive AC timing diagram.

Figure 13. MII Receive AC Timing Diagram

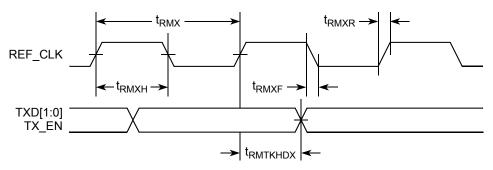

### 8.2.2 RMII AC Timing Specifications

This section describes the RMII transmit and receive AC timing specifications.

### 8.2.2.1 RMII Transmit AC Timing Specifications

The following table provides the RMII transmit AC timing specifications.

#### **Table 22. RMII Transmit AC Timing Specifications**

At recommended operating conditions with  $OV_{DD}$  of 3.3 V  $\pm$  300mV.

| Parameter/Condition                                                    | Symbol <sup>1</sup>                 | Min | Typical | Max | Unit |

|------------------------------------------------------------------------|-------------------------------------|-----|---------|-----|------|

| REF_CLK clock                                                          | t <sub>RMX</sub>                    | _   | 20      | _   | ns   |

| REF_CLK duty cycle                                                     | t <sub>RMXH</sub> /t <sub>RMX</sub> | 35  | _       | 65  | %    |

| REF_CLK to RMII data TXD[1:0], TX_EN delay                             | t <sub>RMTKHDX</sub>                | 2   | _       | 13  | ns   |

| REF_CLK data clock rise V <sub>IL</sub> (min) to V <sub>IH</sub> (max) | t <sub>RMXR</sub>                   | 1.0 | _       | 4.0 | ns   |

| REF_CLK data clock fall V <sub>IH</sub> (max) to V <sub>IL</sub> (min) | t <sub>RMXF</sub>                   | 1.0 | _       | 4.0 | ns   |

#### Note:

1. The symbols used for timing specifications follow the pattern of t<sub>(first three letters of functional block)</sub>(signal)(state)(reference)(state)</sub> for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>RMTKHDX</sub> symbolizes RMII transmit timing (RMT) for the time t<sub>RMX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>RMX</sub> represents the RMII(RM) reference (X) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

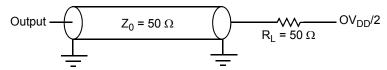

The following figure provides the AC test load.

Figure 14. AC Test Load

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

The following figure shows the RMII transmit AC timing diagram.

Figure 15. RMII Transmit AC Timing Diagram

### 8.2.2.2 RMII Receive AC Timing Specifications

The following table provides the RMII receive AC timing specifications.

#### **Table 23. RMII Receive AC Timing Specifications**

At recommended operating conditions with  $OV_{DD}$  of 3.3 V  $\pm$  300mV.

| Parameter/Condition                                                    | Symbol <sup>1</sup>                 | Min | Typical | Max | Unit |

|------------------------------------------------------------------------|-------------------------------------|-----|---------|-----|------|

| REF_CLK clock period                                                   | t <sub>RMX</sub>                    | _   | 20      | _   | ns   |

| REF_CLK duty cycle                                                     | t <sub>RMXH</sub> /t <sub>RMX</sub> | 35  | _       | 65  | %    |

| RXD[1:0], CRS_DV, RX_ER setup time to REF_CLK                          | t <sub>RMRDVKH</sub>                | 4.0 | _       | _   | ns   |

| RXD[1:0], CRS_DV, RX_ER hold time to REF_CLK                           | t <sub>RMRDXKH</sub>                | 2.0 | _       | _   | ns   |

| REF_CLK clock rise V <sub>IL</sub> (min) to V <sub>IH</sub> (max)      | t <sub>RMXR</sub>                   | 1.0 | _       | 4.0 | ns   |

| REF_CLK clock fall time V <sub>IH</sub> (max) to V <sub>IL</sub> (min) | t <sub>RMXF</sub>                   | 1.0 | _       | 4.0 | ns   |

#### Note:

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

<sup>1.</sup> The symbols used for timing specifications follow the pattern of t<sub>(first three letters of functional block)(signal)(state)</sub> for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>RMRDVKH</sub> symbolizes RMII receive timing (RMR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>RMX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>RMRDXKL</sub> symbolizes RMII receive timing (RMR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>RMX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>RMX</sub> represents the RMII (RM) reference (X) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

### 9 TDM/SI

This section describes the DC and AC electrical specifications for the time-division-multiplexed and serial interface of the MPC8306S.

### 9.1 TDM/SI DC Electrical Characteristics

The following table provides the DC electrical characteristics for the MPC8306S TDM/SI.

Condition Characteristic Symbol Min Max Unit  $I_{OH} = -2.0 \text{ mA}$ Output high voltage  $V_{OH}$ 2.4 V  $I_{OL} = 3.2 \text{ mA}$ Output low voltage  $V_{OL}$ 0.5 V ٧ Input high voltage  $V_{IH}$ 2.0  $OV_{DD} + 0.3$ Input low voltage  $V_{IL}$ -0.3 8.0 V Input current  $I_{IN}$  $0 \text{ V} \leq V_{IN} \leq OV_{DD}$ ±5 μΑ

Table 26. TDM/SI DC Electrical Characteristics

### 9.2 TDM/SI AC Timing Specifications

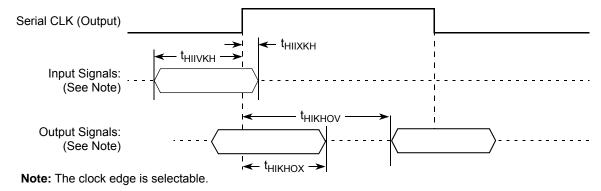

The following table provides the TDM/SI input and output AC timing specifications.

| Characteristic                                | Symbol <sup>2</sup> | Min | Max | Unit |

|-----------------------------------------------|---------------------|-----|-----|------|

| TDM/SI outputs—External clock delay           | t <sub>SEKHOV</sub> | 2   | 14  | ns   |

| TDM/SI outputs—External clock High Impedance  | t <sub>SEKHOX</sub> | 2   | 10  | ns   |

| TDM/SI inputs—External clock input setup time | t <sub>SEIVKH</sub> | 5   | _   | ns   |

| TDM/SI inputs—External clock input hold time  | t <sub>SEIXKH</sub> | 2   | _   | ns   |

Table 27. TDM/SI AC Timing Specifications<sup>1</sup>

#### Notes:

- 1. Output specifications are measured from the 50% level of the rising edge of QE\_CLK\_IN to the 50% level of the signal. Timings are measured at the pin.

- 2. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state)</sub> for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>SEKHOX</sub> symbolizes the TDM/SI outputs external timing (SE) for the time t<sub>TDM/SI</sub> memory clock reference (K) goes from the high state (H) until outputs (O) are invalid (X).

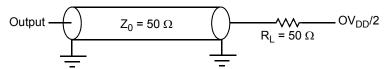

The following figure provides the AC test load for the TDM/SI.

Figure 18. TDM/SI AC Test Load

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

The following figure shows the timing with internal clock.

Figure 22. AC Timing (Internal Clock) Diagram

### **11 USB**

### 11.1 USB Controller

This section provides the AC and DC electrical specifications for the USB (ULPI) interface.

### 11.1.1 USB DC Electrical Characteristics

The following table provides the DC electrical characteristics for the USB interface.

**Parameter Symbol** Min Unit Max High-level input voltage  $V_{\text{IH}}$ 2.0  $OV_{DD} + 0.3$ ٧ Low-level input voltage -0.38.0 ٧  $V_{IL}$ Input current ±5  $I_{IN}$ μΑ High-level output voltage,  $I_{OH}$  = -100  $\mu A$  $V_{OH}$ ٧  $OV_{DD} - 0.2$ Low-level output voltage,  $I_{OL}$  = 100  $\mu$ A 0.2 V  $V_{OL}$

**Table 30. USB DC Electrical Characteristics**

### 11.1.2 USB AC Electrical Specifications

The following table describes the general timing parameters of the USB interface.

Table 31. USB General Timing Parameters

| Parameter                                                          | Symbol <sup>1</sup> | Min | Max | Unit | Note |

|--------------------------------------------------------------------|---------------------|-----|-----|------|------|

| USB clock cycle time                                               | t <sub>usck</sub>   | 15  | _   | ns   | _    |

| Input setup to USB clock—all inputs                                | t <sub>USIVKH</sub> | 4   | _   | ns   | _    |

| input hold to USB clock—all inputs                                 | t <sub>USIXKH</sub> | 1   | _   | ns   | _    |

| USB clock to output valid—all outputs (except USBDR_STP_USBDR_STP) | t <sub>uskhov</sub> | _   | 7   | ns   | _    |

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

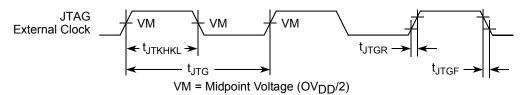

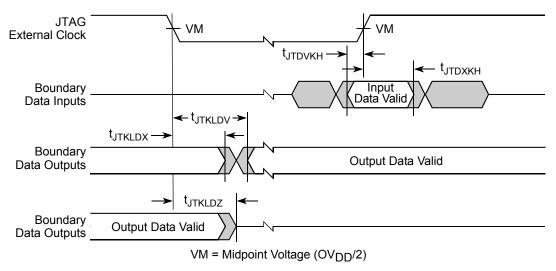

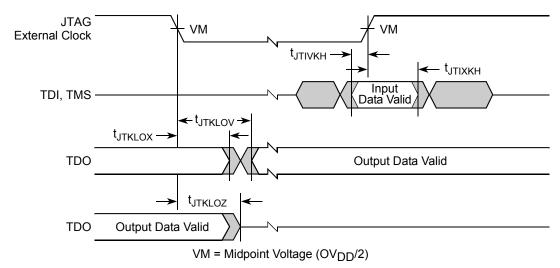

### Table 45. JTAG AC Timing Specifications (Independent of SYS\_CLK\_IN)<sup>1</sup> (continued)

At recommended operating conditions (see Table 2).

| Parameter                                                             | Symbol <sup>2</sup>                        | Min    | Max     | Unit | Notes     |

|-----------------------------------------------------------------------|--------------------------------------------|--------|---------|------|-----------|

| Output hold times:  Boundary-scan data TDO                            | t <sub>JTKLDX</sub><br>t <sub>JTKLOX</sub> | 2<br>2 | _<br>_  | ns   | 5         |

| JTAG external clock to output high impedance:  Boundary-scan data TDO | t <sub>JTKLDZ</sub><br>t <sub>JTKLOZ</sub> | 2<br>2 | 19<br>9 | ns   | 5, 6<br>6 |

#### Notes:

- 1. All outputs are measured from the midpoint voltage of the falling/rising edge of  $t_{TCLK}$  to the midpoint of the signal in question. The output timings are measured at the pins. All output timings assume a purely resistive 50- $\Omega$  load (see Figure 32). Time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

- 2. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>JTDVKH</sub> symbolizes JTAG device timing (JT) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>JTDXKH</sub> symbolizes JTAG timing (JT) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

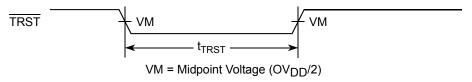

- 3. TRST is an asynchronous level sensitive signal. The setup time is for test purposes only.

- 4. Non-JTAG signal input timing with respect to t<sub>TCLK</sub>.

- 5. Non-JTAG signal output timing with respect to t<sub>TCLK</sub>.

- 6. Guaranteed by design and characterization.

The following figure provides the AC test load for TDO and the boundary-scan outputs of the MPC8306S.

Figure 32. AC Test Load for the JTAG Interface

The following figure provides the JTAG clock input timing diagram.

Figure 33. JTAG Clock Input Timing Diagram

The following figure provides the TRST timing diagram.

Figure 34. TRST Timing Diagram

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

The following figure provides the boundary-scan timing diagram.

Figure 35. Boundary-Scan Timing Diagram

The following figure provides the test access port timing diagram.

Figure 36. Test Access Port Timing Diagram

# 19 Package and Pin Listings

This section details package parameters, pin assignments, and dimensions. The MPC8306S is available in a thermally enhanced MAPBGA (mold array process-ball grid array); see Section 19.1, "Package Parameters for the MPC8306S," and Section 19.2, "Mechanical Dimensions of the MPC8306S MAPBGA," for information on the MAPBGA.

### 19.1 Package Parameters for the MPC8306S

The package parameters are as provided in the following list.

Package outline  $19 \text{ mm} \times 19 \text{ mm}$

Package Type MAPBGA

Interconnects 369

Pitch 0.80 mm

Module height (typical) 1.48 mm; Min = 1.31mm and Max 1.61mm

Solder Balls 96 Sn / 3.5 Ag / 0.5 Cu (VM package)

Ball diameter (typical) 0.40 mm

### 19.2 Mechanical Dimensions of the MPC8306S MAPBGA

The following figure shows the mechanical dimensions and bottom surface nomenclature of the MPC8306S, 369-MAPBGA package.

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

# 19.3 Pinout Listings

Following table shows the pin list of the MPC8306S.

Table 46. MPC8306S Pinout Listing

| Signal       | Package Pin Number              | Pin Type | Power Supply     | Notes |  |  |

|--------------|---------------------------------|----------|------------------|-------|--|--|

|              | DDR Memory Controller Interface |          |                  |       |  |  |

| MEMC_MDQ[0]  | W5                              | Ю        | GV <sub>DD</sub> | _     |  |  |

| MEMC_MDQ[1]  | V4                              | Ю        | GV <sub>DD</sub> | _     |  |  |

| MEMC_MDQ[2]  | Y4                              | Ю        | GV <sub>DD</sub> | _     |  |  |

| MEMC_MDQ[3]  | AB1                             | Ю        | GV <sub>DD</sub> | _     |  |  |

| MEMC_MDQ[4]  | AA1                             | Ю        | GV <sub>DD</sub> | _     |  |  |

| MEMC_MDQ[5]  | Y2                              | Ю        | GV <sub>DD</sub> | _     |  |  |

| MEMC_MDQ[6]  | Y1                              | Ю        | GV <sub>DD</sub> | _     |  |  |

| MEMC_MDQ[7]  | W2                              | Ю        | GV <sub>DD</sub> | _     |  |  |

| MEMC_MDQ[8]  | G2                              | Ю        | GV <sub>DD</sub> | _     |  |  |

| MEMC_MDQ[9]  | G1                              | Ю        | GV <sub>DD</sub> | _     |  |  |

| MEMC_MDQ[10] | F1                              | Ю        | GV <sub>DD</sub> | _     |  |  |

| MEMC_MDQ[11] | E2                              | Ю        | GV <sub>DD</sub> | _     |  |  |

| MEMC_MDQ[12] | E1                              | Ю        | GV <sub>DD</sub> | _     |  |  |

| MEMC_MDQ[13] | E4                              | Ю        | GV <sub>DD</sub> | _     |  |  |

| MEMC_MDQ[14] | F4                              | Ю        | GV <sub>DD</sub> | _     |  |  |

| MEMC_MDQ[15] | D1                              | Ю        | GV <sub>DD</sub> | _     |  |  |

| MEMC_MDM[0]  | AB2                             | 0        | GV <sub>DD</sub> | _     |  |  |

| MEMC_MDM[1]  | G4                              | 0        | GV <sub>DD</sub> | _     |  |  |

| MEMC_MDQS[0] | V5                              | Ю        | GV <sub>DD</sub> | _     |  |  |

| MEMC_MDQS[1] | F5                              | Ю        | GV <sub>DD</sub> | _     |  |  |

| MEMC_MBA[0]  | L2                              | 0        | GV <sub>DD</sub> | _     |  |  |

| MEMC_MBA[1]  | L1                              | 0        | GV <sub>DD</sub> | _     |  |  |

| MEMC_MBA[2]  | R4                              | 0        | GV <sub>DD</sub> | _     |  |  |

| MEMC_MA[0]   | M1                              | 0        | GV <sub>DD</sub> | _     |  |  |

| MEMC_MA[1]   | M4                              | 0        | GV <sub>DD</sub> | _     |  |  |

| MEMC_MA[2]   | N1                              | 0        | GV <sub>DD</sub> | _     |  |  |

| MEMC_MA[3]   | N2                              | 0        | GV <sub>DD</sub> | _     |  |  |

| MEMC_MA[4]   | P1                              | 0        | GV <sub>DD</sub> | _     |  |  |

| MEMC_MA[5]   | N4                              | 0        | GV <sub>DD</sub> | _     |  |  |

| MEMC_MA[6]   | P2                              | 0        | GV <sub>DD</sub> | _     |  |  |

| MEMC_MA[7]   | R1                              | 0        | GV <sub>DD</sub> | _     |  |  |

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

Table 46. MPC8306S Pinout Listing (continued)

| Signal        | Package Pin Number           | Pin Type | Power Supply     | Notes |

|---------------|------------------------------|----------|------------------|-------|

| MEMC_MA[8]    | T1                           | 0        | GV <sub>DD</sub> | _     |

| MEMC_MA[9]    | P4                           | 0        | GV <sub>DD</sub> | _     |

| MEMC_MA[10]   | L4                           | 0        | GV <sub>DD</sub> | _     |

| MEMC_MA[11]   | T2                           | 0        | GV <sub>DD</sub> | _     |

| MEMC_MA[12]   | U1                           | 0        | GV <sub>DD</sub> | _     |

| MEMC_MA[13]   | U2                           | 0        | GV <sub>DD</sub> | _     |

| MEMC_MWE_B    | K1                           | 0        | GV <sub>DD</sub> | _     |

| MEMC_MRAS_B   | K2                           | 0        | GV <sub>DD</sub> | _     |

| MEMC_MCAS_B   | J1                           | 0        | GV <sub>DD</sub> | _     |

| MEMC_MCS_B[0] | J4                           | 0        | GV <sub>DD</sub> | _     |

| MEMC_MCS_B[1] | H1                           | 0        | GV <sub>DD</sub> | _     |

| MEMC_MCKE[0]  | U4                           | 0        | GV <sub>DD</sub> | _     |

| MEMC_MCK[0]   | V1                           | 0        | GV <sub>DD</sub> | _     |

| MEMC_MCK_B[0] | W1                           | 0        | GV <sub>DD</sub> | _     |

| MEMC_MODT[0]  | H2                           | 0        | GV <sub>DD</sub> | _     |

| MEMC_MODT[1]  | H4                           | 0        | GV <sub>DD</sub> | _     |

| MEMC_MVREF    | L8                           |          | GV <sub>DD</sub> | _     |

| L             | ocal Bus Controller Interfac | е        |                  |       |

| LAD[0]        | В7                           | Ю        | OV <sub>DD</sub> | _     |

| LAD[1]        | D9                           | Ю        | OV <sub>DD</sub> | _     |

| LAD[2]        | A6                           | Ю        | OV <sub>DD</sub> | _     |

| LAD[3]        | B8                           | Ю        | OV <sub>DD</sub> | _     |

| LAD[4]        | A7                           | Ю        | OV <sub>DD</sub> | _     |

| LAD[5]        | A8                           | Ю        | OV <sub>DD</sub> | _     |

| LAD[6]        | A9                           | 10       | OV <sub>DD</sub> | _     |

| LAD[7]        | D10                          | 10       | OV <sub>DD</sub> | _     |

| LAD[8]        | B10                          | Ю        | OV <sub>DD</sub> | _     |

| LAD[9]        | A10                          | Ю        | OV <sub>DD</sub> | _     |

| LAD[10]       | B11                          | Ю        | OV <sub>DD</sub> | _     |

| LAD[11]       | D12                          | Ю        | OV <sub>DD</sub> | _     |

| LAD[12]       | D11                          | Ю        | OV <sub>DD</sub> | _     |

| LAD[13]       | A11                          | Ю        | OV <sub>DD</sub> | _     |

| LAD[14]       | A12                          | Ю        | OV <sub>DD</sub> | _     |

| LAD[15]       | B13                          | Ю        | OV <sub>DD</sub> | _     |

| LA[16]        | A13                          | Ю        | OV <sub>DD</sub> | _     |

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

### Package and Pin Listings

Table 46. MPC8306S Pinout Listing (continued)

| Signal                 | Package Pin Number | Pin Type | Power Supply     | Notes |  |

|------------------------|--------------------|----------|------------------|-------|--|

| LA[17]                 | B14                | 0        | OV <sub>DD</sub> | _     |  |

| LA[18]                 | A14                | 0        | OV <sub>DD</sub> | _     |  |

| LA[19]                 | A15                | 0        | OV <sub>DD</sub> | _     |  |

| LA[20]                 | A16                | 0        | OV <sub>DD</sub> | _     |  |

| LA[21]                 | B16                | 0        | OV <sub>DD</sub> | _     |  |

| LA[22]                 | A17                | 0        | OV <sub>DD</sub> | _     |  |

| LA[23]                 | B17                | 0        | OV <sub>DD</sub> | _     |  |

| LA[24]                 | A18                | 0        | OV <sub>DD</sub> | _     |  |

| LA[25]                 | B19                | 0        | OV <sub>DD</sub> | _     |  |

| LCS_B[0]               | A19                | 0        | OV <sub>DD</sub> | 3     |  |

| LCS_B[1]               | B20                | 0        | OV <sub>DD</sub> | 3     |  |

| LCS_B[2]               | A20                | 0        | OV <sub>DD</sub> | 3     |  |

| LCS_B[3]               | A21                | 0        | OV <sub>DD</sub> | 3     |  |

| LCLK[0]                | D13                | 0        | OV <sub>DD</sub> | _     |  |

| LGPL[0]                | B22                | 0        | OV <sub>DD</sub> | _     |  |

| LGPL[1]                | D16                | 0        | OV <sub>DD</sub> | _     |  |

| LGPL[2]                | D19                | 0        | OV <sub>DD</sub> | _     |  |

| LGPL[3]                | D17                | 0        | OV <sub>DD</sub> | _     |  |

| LGPL[4]                | E18                | Ю        | OV <sub>DD</sub> | _     |  |

| LGPL[5]                | E19                | 0        | OV <sub>DD</sub> | _     |  |

| LWE_B[0]               | D15                | 0        | OV <sub>DD</sub> | _     |  |

| LWE_B[1]               | D14                | 0        | OV <sub>DD</sub> | _     |  |

| LBCTL                  | A22                | 0        | OV <sub>DD</sub> | _     |  |

| LALE                   | B23                | 0        | OV <sub>DD</sub> | _     |  |

|                        | JTAG               |          |                  |       |  |

| TCK                    | A3                 | I        | OV <sub>DD</sub> | _     |  |

| TDI                    | B5                 | I        | OV <sub>DD</sub> | 3     |  |

| TDO                    | D7                 | 0        | OV <sub>DD</sub> | _     |  |

| TMS                    | A4                 | I        | OV <sub>DD</sub> | 3     |  |

| TRST_B                 | D8                 | I        | OV <sub>DD</sub> | 3     |  |

|                        | Test Interface     |          |                  |       |  |

| TEST_MODE              | A5                 | I        | OV <sub>DD</sub> | _     |  |

| System Control Signals |                    |          |                  |       |  |

| HRESET_B               | U20                | Ю        | OV <sub>DD</sub> | 1     |  |

| PORESET_B              | V20                | I        | OV <sub>DD</sub> | _     |  |

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

### 20.1 System Clock Domains

As shown in Figure 38, the primary clock input (frequency) is multiplied up by the system phase-locked loop (PLL) and the clock unit to create four major clock domains:

- The coherent system bus clock (*csb\_clk*)

- The QUICC Engine clock (*qe\_clk*)

- The internal clock for the DDR controller (ddr clk)

- The internal clock for the local bus controller (*lbc clk*)

The *csb\_clk* frequency is derived from the following equation:

Eqn. 1

The *csb\_clk* serves as the clock input to the e300 core. A second PLL inside the core multiplies up the *csb\_clk* frequency to create the internal clock for the core (*core\_clk*). The system and core PLL multipliers are selected by the SPMF and COREPLL fields in the reset configuration word low (RCWL) which is loaded at power-on reset or by one of the hard-coded reset options. For more information, see the Reset Configuration chapter in the *MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Reference Manual*.

The *qe\_clk* frequency is determined by the QUICC Engine PLL multiplication factor (RCWL[CEPMF]) and the QUICC Engine PLL division factor (RCWL[CEPDF]) as the following equation:

qe clk = (QE CLK

$$IN \times CEPMF$$

)  $\div$  (1 + CEPDF) **Eqn. 2**

$$qe\_clk = (QE\_CLK\_IN \times CEPMF) \div (1 + CEPDF)$$

Eqn. 3

For more information, see the QUICC Engine PLL Multiplication Factor section and the "QUICC Engine PLL Division Factor" section in the *MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Reference Manual* for more information.

The DDR SDRAM memory controller operates with a frequency equal to twice the frequency of  $csb\_clk$ . Note that  $ddr\_clk$  is not the external memory bus frequency;  $ddr\_clk$  passes through the DDR clock divider (÷2) to create the differential DDR memory bus clock outputs (MCK and  $\overline{\text{MCK}}$ ). However, the data rate is the same frequency as  $ddr\_clk$ .

The local bus memory controller operates with a frequency equal to the frequency of  $csb\_clk$ . Note that  $lbc\_clk$  is not the external local bus frequency;  $lbc\_clk$  passes through the LBC clock divider to create the external local bus clock outputs (LCLK). The LBC clock divider ratio is controlled by LCRR[CLKDIV]. For more information, see the LBC Bus Clock and Clock Ratios section in the MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Reference Manual.

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

**Table 49. System PLL Multiplication Factors**

| RCWL[SPMF] | System PLL Multiplication Factor |  |  |

|------------|----------------------------------|--|--|

| 0000       | Reserved                         |  |  |

| 0001       | Reserved                         |  |  |

| 0010       | × 2                              |  |  |

| 0011       | × 3                              |  |  |

| 0100       | × 4                              |  |  |

| 0101       | × 5                              |  |  |

| 0110       | × 6                              |  |  |

| 0111–1111  | Reserved                         |  |  |

coherent system bus clock (*csb\_clk*). The following table shows the expected frequency values for the CSB frequency for selected *csb\_clk* to *SYS\_CLK\_IN* ratios.

**Table 50. CSB Frequency Options**

|      |                            | SYS_CLK_IN(MHz) |                   |       |  |

|------|----------------------------|-----------------|-------------------|-------|--|

| SPMF | csb_clk : sys_clk_in Ratio | 25              | 33.33             | 66.67 |  |

|      |                            | csb_c           | clk Frequency (Mi | Hz)   |  |

| 0010 | 2:1                        |                 |                   | 133   |  |

| 0011 | 3:1                        |                 |                   |       |  |

| 0100 | 4:1                        |                 | 133               |       |  |

| 0101 | 5:1                        | 125             | 167               |       |  |

| 0110 | 6:1                        |                 |                   |       |  |

# 20.3 Core PLL Configuration

RCWL[COREPLL] selects the ratio between the internal coherent system bus clock (*csb\_clk*) and the e300 core clock (*core\_clk*). The following table shows the encodings for RCWL[COREPLL]. COREPLL values not listed, and should be considered reserved.

Table 51. e300 Core PLL Configuration

| RCWL[COREPLL] |      | core clk: csb clk Ratio | VCO Divider                                          |                                                      |  |

|---------------|------|-------------------------|------------------------------------------------------|------------------------------------------------------|--|

| 0-1           | 2-5  | 6                       | - COIE_CIK . CSD_CIK RAUO                            | VGO DIVIGEI                                          |  |

| nn            | 0000 | n                       | PLL bypassed (PLL off, csb_clk clocks core directly) | PLL bypassed (PLL off, csb_clk clocks core directly) |  |

| 00            | 0001 | 0                       | 1:1                                                  | ÷2                                                   |  |

| 01            | 0001 | 0                       | 1:1                                                  | ÷4                                                   |  |

| 10            | 0001 | 0                       | 1:1                                                  | ÷8                                                   |  |

| 11            | 0001 | 0                       | 1:1                                                  | ÷8                                                   |  |

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

Clocking

Table 51. e300 Core PLL Configuration (continued)

| RCWL[COREPLL] |      | L] |                         | V00 PL I I  |

|---------------|------|----|-------------------------|-------------|

| 0-1           | 2-5  | 6  | core_clk: csb_clk Ratio | VCO Divider |

| 00            | 0001 | 1  | 1.5:1                   | ÷ 2         |

| 01            | 0001 | 1  | 1.5:1                   | ÷ 4         |

| 10            | 0001 | 1  | 1.5:1                   | ÷ 8         |

| 11            | 0001 | 1  | 1.5:1                   | ÷ 8         |

| 00            | 0010 | 0  | 2:1                     | ÷ 2         |

| 01            | 0010 | 0  | 2:1                     | ÷ 4         |

| 10            | 0010 | 0  | 2:1                     | ÷ 8         |

| 11            | 0010 | 0  | 2:1                     | ÷ 8         |

| 00            | 0010 | 1  | 2.5:1                   | ÷ 2         |

| 01            | 0010 | 1  | 2.5:1                   | ÷ 4         |

| 10            | 0010 | 1  | 2.5:1                   | ÷ 8         |

| 11            | 0010 | 1  | 2.5:1                   | ÷ 8         |

| 00            | 0011 | 0  | 3:1                     | ÷ 2         |

| 01            | 0011 | 0  | 3:1                     | ÷ 4         |

| 10            | 0011 | 0  | 3:1                     | ÷ 8         |

| 11            | 0011 | 0  | 3:1                     | ÷ 8         |

#### **NOTE**

Core VCO frequency = core frequency  $\times$  VCO divider. The VCO divider (RCWL[COREPLL[0:1]]), must be set properly so that the core VCO frequency is in the range of 400–800 MHz.

### 20.4 QUICC Engine PLL Configuration

The QUICC Engine PLL is controlled by the RCWL[CEPMF] and RCWL[CEPDF] parameters. The following table shows the multiplication factor encodings for the QUICC Engine PLL.

**Table 52. QUICC Engine PLL Multiplication Factors**

| RCWL[CEPMF] | RCWL[CEPDF] | QUICC Engine PLL Multiplication Factor = RCWL[CEPMF]/ (1 + RCWL[CEPDF) |

|-------------|-------------|------------------------------------------------------------------------|

| 00000–00001 | 0           | Reserved                                                               |

| 00010       | 0           | × 2                                                                    |

| 00011       | 0           | × 3                                                                    |

| 00100       | 0           | × 4                                                                    |

| 00101       | 0           | × 5                                                                    |

| 00110       | 0           | × 6                                                                    |

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

#### **System Design Information**

lifetime of the package. Recommended maximum force on the top of the package is 10 lb (4.5 kg) force. If an adhesive attachment is planned, the adhesive should be intended for attachment to painted or plastic surfaces and its performance verified under the application requirements.

# 21.2.1 Experimental Determination of the Junction Temperature with a Heat Sink

When heat sink is used, the junction temperature is determined from a thermocouple inserted at the interface between the case of the package and the interface material. A clearance slot or hole is normally required in the heat sink. Minimizing the size of the clearance is important to minimize the change in thermal performance caused by removing part of the thermal interface to the heat sink. Because of the experimental difficulties with this technique, many engineers measure the heat sink temperature and then back calculate the case temperature using a separate measurement of the thermal resistance of the interface.

From this case temperature, the junction temperature is determined from the junction-to-case thermal resistance using the following equation:

$$T_I = T_C + (R_{\theta IC} \times P_D)$$

Eqn. 5

where:

$T_C$  = case temperature of the package (°C)  $R_{\theta IC}$  = junction-to-case thermal resistance (°C/W)

$P_D$  = power dissipation (W)

# 22 System Design Information

This section provides electrical and thermal design recommendations for successful application of the MPC8306S.

### 22.1 System Clocking

The MPC8306S includes three PLLs.

- The system PLL (AV<sub>DD2</sub>) generates the system clock from the externally supplied SYS\_CLK\_IN input. The frequency ratio between the system and SYS\_CLK\_IN is selected using the system PLL ratio configuration bits as described in Section 20.2, "System PLL Configuration."

- The e300 core PLL (AV<sub>DD3</sub>) generates the core clock as a slave to the system clock. The frequency ratio between the e300 core clock and the system clock is selected using the e300 PLL ratio configuration bits as described in Section 20.3, "Core PLL Configuration."

- The QUICC Engine PLL (AV<sub>DD1</sub>) which uses the same reference as the system PLL. The QUICC Engine block generates or uses external sources for all required serial interface clocks.

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1