# E·XFL

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Active                                                                  |

|---------------------------------|-------------------------------------------------------------------------|

| Core Processor                  | PowerPC e300c3                                                          |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                          |

| Speed                           | 333MHz                                                                  |

| Co-Processors/DSP               | Communications; QUICC Engine                                            |

| RAM Controllers                 | DDR2                                                                    |

| Graphics Acceleration           | No                                                                      |

| Display & Interface Controllers | -                                                                       |

| Ethernet                        | 10/100Mbps (3)                                                          |

| SATA                            | -                                                                       |

| USB                             | USB 2.0 (1)                                                             |

| Voltage - I/O                   | 1.8V, 3.3V                                                              |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                        |

| Security Features               | -                                                                       |

| Package / Case                  | 369-LFBGA                                                               |

| Supplier Device Package         | 369-PBGA (19x19)                                                        |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8306svmafdca |

|                                 |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Overview

In summary, the MPC8306S provides users with a highly integrated, fully programmable communications processor. This helps to ensure that a low-cost system solution can be quickly developed and offers flexibility to accommodate new standards and evolving system requirements.

## 1.1 Features

The major features of the device are as follows:

- e300c3 Power Architecture processor core

- Enhanced version of the MPC603e core

- High-performance, superscalar processor core with a four-stage pipeline and low interrupt latency times

- Floating-point, dual integer units, load/store, system register, and branch processing units

- 16-Kbyte instruction cache and 16-Kbyte data cache with lockable capabilities

- Dynamic power management

- Enhanced hardware program debug features

- Software-compatible with Freescale processor families implementing Power Architecture technology

- Separate PLL that is clocked by the system bus clock

- Performance monitor

- QUICC Engine block

- 32-bit RISC controller for flexible support of the communications peripherals with the following features:

- One clock per instruction

- Separate PLL for operating frequency that is independent of system's bus and e300 core frequency for power and performance optimization

- 32-bit instruction object code

- Executes code from internal IRAM

- 32-bit arithmetic logic unit (ALU) data path

- Modular architecture allowing for easy functional enhancements

- Slave bus for CPU access of registers and multiuser RAM space

- 48 Kbytes of instruction RAM

- 16 Kbytes of multiuser data RAM

- Serial DMA channel for receive and transmit on all serial channels

- Five unified communication controllers (UCCs) supporting the following protocols and interfaces:

- 10/100 Mbps Ethernet/IEEE Std. 802.3® through MII and RMII interfaces.

- HDLC/Transparent (bit rate up to QUICC Engine operating frequency / 8)

- HDLC Bus (bit rate up to 10 Mbps)

- Asynchronous HDLC (bit rate up to 2 Mbps)

The following table shows the estimated typical I/O power dissipation for the device.

| Table 6. Typical I/O Power Dissipation | Table 6. | . Typical I/O Power Dissipation |

|----------------------------------------|----------|---------------------------------|

|----------------------------------------|----------|---------------------------------|

| Interface                                                                                         | Parameter                                                                                             | GV <sub>DD</sub><br>(1.8 V) | OV <sub>DD</sub><br>(3.3 V) | Unit | Comments |

|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------|------|----------|

| DDR I/O<br>65% utilization<br>1.8 V<br>$R_s = 20 \Omega$<br>$R_t = 50 \Omega$<br>1 pair of clocks | 266 MHz, 1 × 16 bits                                                                                  | 0.141                       | _                           | W    | _        |

| Local bus I/O load = 25 pF<br>1 pair of clocks                                                    | 66 MHz, 26 bits                                                                                       |                             |                             |      |          |

| QUICC Engine block and other I/Os                                                                 | TDM serial, HDLC/TRAN serial,<br>DUART, MII, RMII, Ethernet<br>management, USB, SPI, Timer<br>output, |                             | 0.150                       | W    | 1        |

Note:

1. Typical I/O power is based on a nominal voltage of V<sub>DD</sub> = 3.3V, ambient temperature, and the core running a Dhrystone benchmark application. The measurements were taken on the evaluation board using WC process silicon.

# 4 Clock Input Timing

This section provides the clock input DC and AC electrical characteristics for the MPC8306S.

## NOTE

The rise/fall time on QUICC Engine input pins should not exceed 5 ns. This should be enforced especially on clock signals. Rise time refers to signal transitions from 10% to 90% of  $OV_{DD}$ ; fall time refers to transitions from 90% to 10% of  $OV_{DD}$ .

## 4.1 DC Electrical Characteristics

The following table provides the clock input (SYS\_CLK\_IN) DC specifications for the MPC8306S. These specifications are also applicable for QE\_CLK\_IN.

| Parameter                | Condition                                                                                                        | Symbol          | Min  | Max                    | Unit |

|--------------------------|------------------------------------------------------------------------------------------------------------------|-----------------|------|------------------------|------|

| Input high voltage       | -                                                                                                                | V <sub>IH</sub> | 2.4  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage        | -                                                                                                                | V <sub>IL</sub> | -0.3 | 0.4                    | V    |

| SYS_CLK_IN input current | $0~V \le V_{IN} \le OV_{DD}$                                                                                     | I <sub>IN</sub> | _    | ±5                     | μΑ   |

| SYS_CLK_IN input current | $\begin{array}{c} 0 \ V \leq V_{IN} \leq 0.5 \ V \ or \\ OV_{DD} - 0.5 \ V \leq V_{IN} \leq OV_{DD} \end{array}$ | I <sub>IN</sub> | —    | ±5                     | μΑ   |

| SYS_CLK_IN input current | $0.5~V \leq V_{IN} \leq OV_{DD} - 0.5~V$                                                                         | I <sub>IN</sub> | _    | ±50                    | μΑ   |

Table 7. SYS\_CLK\_IN DC Electrical Characteristics

1

1

1

1

\_\_\_\_

\_

The following table provides the PLL lock times.

Table 10. PLL Lock Times

| Parameter/Condition | Min | Мах | Unit | Note |

|---------------------|-----|-----|------|------|

| PLL lock times      | —   | 100 | μS   | —    |

#### 5.1 **Reset Signals DC Electrical Characteristics**

The following table provides the DC electrical characteristics for the MPC8306S reset signals mentioned in Table 9.

Characteristic Symbol Condition Max Unit Min Note Output high voltage VOH  $I_{OH} = -6.0 \text{ mA}$ 2.4 V Output low voltage VOL I<sub>OL</sub> = 6.0 mA 0.5 V \_\_\_\_  $V_{OL}$ V Output low voltage I<sub>OL</sub> = 3.2 mA 0.4 Input high voltage V  $V_{IH}$ 2.0 OV<sub>DD</sub> + 0.3 -0.3 0.8 V Input low voltage VII Input current  $0 V \leq V_{IN} \leq OV_{DD}$ — ±5 μΑ IIN

Table 11. Reset Signals DC Electrical Characteristics

Note:

1. This specification applies when operating from 3.3 V supply.

#### **DDR2 SDRAM** 6

This section describes the DC and AC electrical specifications for the DDR2 SDRAM interface of the MPC8306S. Note that DDR2 SDRAM is  $GV_{DD}(typ) = 1.8 V.$

#### **DDR2 SDRAM DC Electrical Characteristics** 6.1

The following table provides the recommended operating conditions for the DDR2 SDRAM component(s) of the MPC8306S when  $GV_{DD}(typ) = 1.8 V$ .

| Parameter/Condition     | Symbol           | Min                  | Max                    | Unit | Note |

|-------------------------|------------------|----------------------|------------------------|------|------|

| I/O supply voltage      | GV <sub>DD</sub> | 1.7                  | 1.9                    | V    | 1    |

| I/O reference voltage   | MVREF            | $0.49 	imes GV_{DD}$ | $0.51 \times GV_{DD}$  | V    | 2    |

| I/O termination voltage | V <sub>TT</sub>  | MVREF – 0.04         | MVREF + 0.04           | V    | 3    |

| Input high voltage      | V <sub>IH</sub>  | MVREF+ 0.125         | GV <sub>DD</sub> + 0.3 | V    | —    |

| Input low voltage       | V <sub>IL</sub>  | -0.3                 | MVREF – 0.125          | V    | —    |

| Output leakage current  | I <sub>OZ</sub>  | -9.9                 | 9.9                    | μΑ   | 4    |

Table 12. DDR2 SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 1.8 V

### Table 15. DDR2 SDRAM Input AC Timing Specifications (continued)

At recommended operating conditions with  $GV_{DD}$  of 1.8V ± 100mV.

| Parameter | Symbol | Min  | Мах | Unit | Note |

|-----------|--------|------|-----|------|------|

| 266 MHz   |        | -750 | 750 |      |      |

#### Notes:

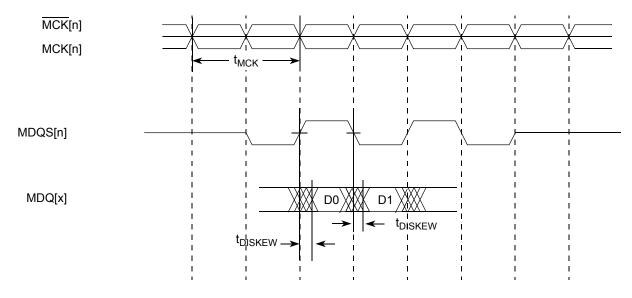

1. t<sub>CISKEW</sub> represents the total amount of skew consumed by the controller between MDQS[n] and any corresponding bit that is captured with MDQS[n]. This should be subtracted from the total timing budget.

The amount of skew that can be tolerated from MDQS to a corresponding MDQ signal is called t<sub>DISKEW</sub>. This can be determined by the equation: t<sub>DISKEW</sub> = ±(T/4 – abs(t<sub>CISKEW</sub>)) where T is the clock period and abs(t<sub>CISKEW</sub>) is the absolute value of t<sub>CISKEW</sub>.

The following figure shows the input timing diagram for the DDR controller.

Figure 4. DDR Input Timing Diagram

## 6.2.2 DDR2 SDRAM Output AC Timing Specifications

The following table provides the output AC timing specifications for the DDR2 SDRAM interfaces.

## Table 16. DDR2 SDRAM Output AC Timing Specifications

At recommended operating conditions with GV\_{DD} of 1.8V  $\pm$  100mV.

| Parameter                                 | Symbol <sup>1</sup> | Min   | Мах | Unit | Note |

|-------------------------------------------|---------------------|-------|-----|------|------|

| MCK cycle time, (MCK/MCK crossing)        | t <sub>MCK</sub>    | 5.988 | 8   | ns   | 2    |

| ADDR/CMD output setup with respect to MCK | t <sub>DDKHAS</sub> |       |     | ns   | 3    |

| 266 MHz                                   |                     | 2.5   | —   |      |      |

| ADDR/CMD output hold with respect to MCK  | t <sub>DDKHAX</sub> |       |     | ns   | 3    |

| 266 MHz                                   |                     | 2.5   | —   |      |      |

| MCS output setup with respect to MCK      | t <sub>DDKHCS</sub> |       |     | ns   | 3    |

| 266 MHz                                   |                     | 2.5   | —   |      |      |

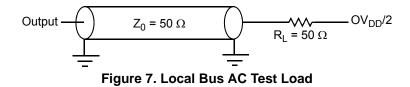

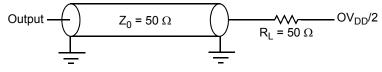

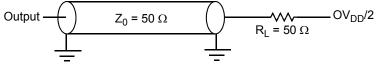

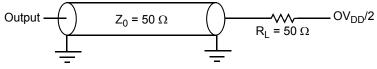

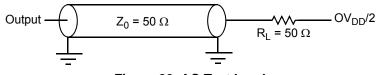

The following figure provides the AC test load for the local bus.

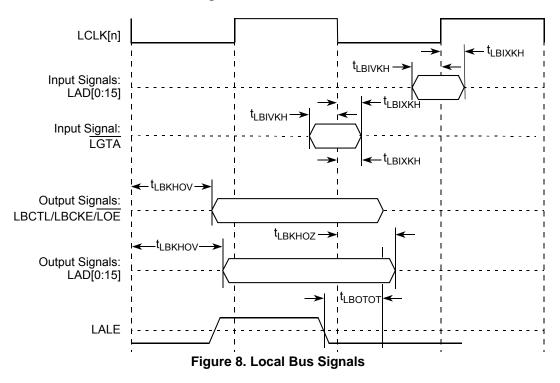

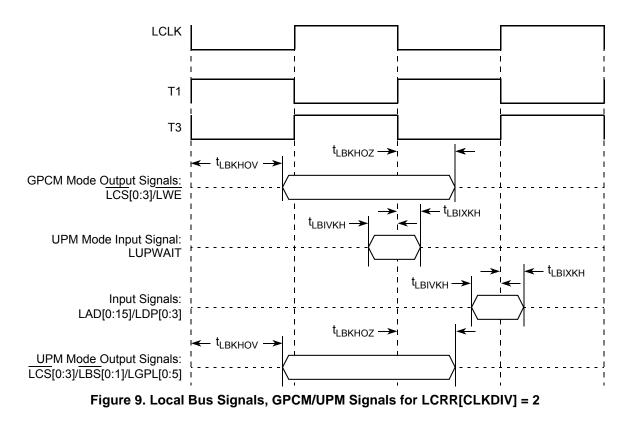

The following figures show the local bus signals. These figures has been given indicate timing parameters only and do not reflect actual functional operation of interface.

Local Bus

The following figure provides the AC test load.

Figure 11. AC Test Load

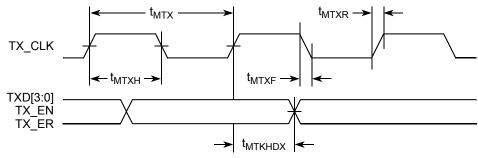

The following figure shows the MII transmit AC timing diagram.

Figure 12. MII Transmit AC Timing Diagram

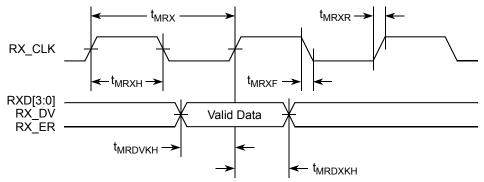

## 8.2.1.2 MII Receive AC Timing Specifications

The following table provides the MII receive AC timing specifications.

| Table 21. MII Receive AC Timing Specifications | Table 2 | 21. MII | Receive | AC | Timing | Specifications |

|------------------------------------------------|---------|---------|---------|----|--------|----------------|

|------------------------------------------------|---------|---------|---------|----|--------|----------------|

At recommended operating conditions with  $OV_{DD}$  of 3.3 V ± 300mV.

| Parameter/Condition                                              | Symbol <sup>1</sup>                 | Min  | Typical | Max | Unit |

|------------------------------------------------------------------|-------------------------------------|------|---------|-----|------|

| RX_CLK clock period 10 Mbps                                      | t <sub>MRX</sub>                    |      | 400     | —   | ns   |

| RX_CLK clock period 100 Mbps                                     | t <sub>MRX</sub>                    | _    | 40      | —   | ns   |

| RX_CLK duty cycle                                                | t <sub>MRXH</sub> /t <sub>MRX</sub> | 35   | _       | 65  | %    |

| RXD[3:0], RX_DV, RX_ER setup time to RX_CLK                      | t <sub>MRDVKH</sub>                 | 10.0 | —       | —   | ns   |

| RXD[3:0], RX_DV, RX_ER hold time to RX_CLK                       | t <sub>MRDXKH</sub>                 | 10.0 | —       | _   | ns   |

| RX_CLK clock rise V <sub>IL</sub> (min) to V <sub>IH</sub> (max) | t <sub>MRXR</sub>                   | 1.0  | —       | 4.0 | ns   |

| RX_CLK clock fall time $V_{IH}(max)$ to $V_{IL}(min)$            | t <sub>MRXF</sub>                   | 1.0  | —       | 4.0 | ns   |

Note:

1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MRDVKH</sub> symbolizes MII receive timing (MR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>MRDXKL</sub> symbolizes MII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>MRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>MRX</sub> represents the MII (M) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

#### **Ethernet and MII Management**

The following figure shows the MII receive AC timing diagram.

Figure 13. MII Receive AC Timing Diagram

## 8.2.2 RMII AC Timing Specifications

This section describes the RMII transmit and receive AC timing specifications.

## 8.2.2.1 RMII Transmit AC Timing Specifications

The following table provides the RMII transmit AC timing specifications.

### Table 22. RMII Transmit AC Timing Specifications

At recommended operating conditions with  $\text{OV}_{\text{DD}}$  of 3.3 V ± 300mV.

| Parameter/Condition                                                    | Symbol <sup>1</sup>                 | Min | Typical | Max | Unit |

|------------------------------------------------------------------------|-------------------------------------|-----|---------|-----|------|

| REF_CLK clock                                                          | t <sub>RMX</sub>                    | _   | 20      |     | ns   |

| REF_CLK duty cycle                                                     | t <sub>RMXH</sub> /t <sub>RMX</sub> | 35  | _       | 65  | %    |

| REF_CLK to RMII data TXD[1:0], TX_EN delay                             | t <sub>RMTKHDX</sub>                | 2   |         | 13  | ns   |

| REF_CLK data clock rise V <sub>IL</sub> (min) to V <sub>IH</sub> (max) | t <sub>RMXR</sub>                   | 1.0 | _       | 4.0 | ns   |

| REF_CLK data clock fall $V_{IH}(max)$ to $V_{IL}(min)$                 | t <sub>RMXF</sub>                   | 1.0 | _       | 4.0 | ns   |

Note:

The symbols used for timing specifications follow the pattern of t<sub>(first three letters of functional block)(signal)(state)(reference)(state)</sub> for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>RMTKHDX</sub> symbolizes RMII transmit timing (RMT) for the time t<sub>RMX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>RMX</sub> represents the RMII(RM) reference (X) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

The following figure provides the AC test load.

Figure 14. AC Test Load

TDM/SI

# 9 TDM/SI

This section describes the DC and AC electrical specifications for the time-division-multiplexed and serial interface of the MPC8306S.

# 9.1 TDM/SI DC Electrical Characteristics

The following table provides the DC electrical characteristics for the MPC8306S TDM/SI.

| Table 26. TDM/SI DC Electrical Characteristics | ; |

|------------------------------------------------|---|

|------------------------------------------------|---|

| Characteristic      | Symbol          | Condition                      | Min  | Мах                    | Unit |

|---------------------|-----------------|--------------------------------|------|------------------------|------|

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = –2.0 mA      | 2.4  | —                      | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA       | _    | 0.5                    | V    |

| Input high voltage  | V <sub>IH</sub> | —                              | 2.0  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | —                              | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> | $0~V \leq V_{IN} \leq OV_{DD}$ | _    | ±5                     | μA   |

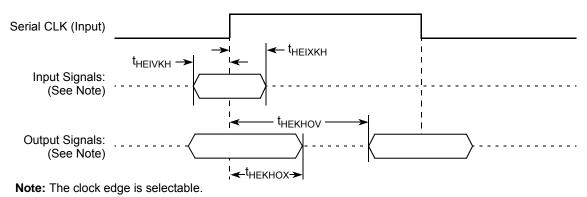

# 9.2 TDM/SI AC Timing Specifications

The following table provides the TDM/SI input and output AC timing specifications.

Table 27. TDM/SI AC Timing Specifications<sup>1</sup>

| Characteristic                                | Symbol <sup>2</sup> | Min | Max | Unit |

|-----------------------------------------------|---------------------|-----|-----|------|

| TDM/SI outputs—External clock delay           | t <sub>SEKHOV</sub> | 2   | 14  | ns   |

| TDM/SI outputs—External clock High Impedance  | t <sub>SEKHOX</sub> | 2   | 10  | ns   |

| TDM/SI inputs—External clock input setup time | t <sub>SEIVKH</sub> | 5   | _   | ns   |

| TDM/SI inputs—External clock input hold time  | t <sub>SEIXKH</sub> | 2   | _   | ns   |

Notes:

1. Output specifications are measured from the 50% level of the rising edge of QE\_CLK\_IN to the 50% level of the signal. Timings are measured at the pin.

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, t<sub>SEKHOX</sub> symbolizes the TDM/SI outputs external timing (SE) for the time t<sub>TDM/SI</sub> memory clock reference (K) goes from the high state (H) until outputs (O) are invalid (X).

</sub></sub>

The following figure provides the AC test load for the TDM/SI.

Figure 18. TDM/SI AC Test Load

| Characteristic                         | Symbol <sup>2</sup> | Min | Мах | Unit |

|----------------------------------------|---------------------|-----|-----|------|

| Outputs—External clock high impedance  | t <sub>HEKHOX</sub> | 1   | 8   | ns   |

| Inputs—Internal clock input setup time | t <sub>HII∨KH</sub> | 9   | _   | ns   |

| Inputs—External clock input setup time | t <sub>HEIVKH</sub> | 4   | —   | ns   |

| Inputs—Internal clock input hold time  | t <sub>HIIXKH</sub> | 0   | —   | ns   |

| Inputs—External clock input hold time  | t <sub>HEIXKH</sub> | 1   | —   | ns   |

Table 29. HDLC AC Timing Specifications<sup>1</sup> (continued)

#### Notes:

1. Output specifications are measured from the 50% level of the rising edge of QE\_CLK\_IN to the 50% level of the signal. Timings are measured at the pin.

2. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>HIKHOX</sub> symbolizes the outputs internal timing (HI) for the time t<sub>serial</sub> memory clock reference (K) goes from the high state (H) until outputs (O) are invalid (X).</sub>

The following figure provides the AC test load.

Figure 20. AC Test Load

Figure 21 and Figure 22 represent the AC timing from Table 29. Note that although the specifications generally reference the rising edge of the clock, these AC timing diagrams also apply when the falling edge is the active edge.

The following figure shows the timing with external clock.

Figure 21. AC Timing (External Clock) Diagram

# 13 I<sup>2</sup>C

I<sup>2</sup>C

This section describes the DC and AC electrical characteristics for the I<sup>2</sup>C interface of the MPC8306S.

# **13.1** I<sup>2</sup>C DC Electrical Characteristics

The following table provides the DC electrical characteristics for the I<sup>2</sup>C interface of the MPC8306S.

Table 34. I<sup>2</sup>C DC Electrical Characteristics

At recommended operating conditions with  $\text{OV}_{\text{DD}}$  of 3.3 V ± 300mV.

| Parameter                                                                                     | Symbol              | Min                   | Max                       | Unit | Notes |

|-----------------------------------------------------------------------------------------------|---------------------|-----------------------|---------------------------|------|-------|

| Input high voltage level                                                                      | V <sub>IH</sub>     | $0.7 \times OV_{DD}$  | OV <sub>DD</sub> + 0.3    | V    | _     |

| Input low voltage level                                                                       | V <sub>IL</sub>     | -0.3                  | $0.3\times\text{OV}_{DD}$ | V    |       |

| Low level output voltage                                                                      | V <sub>OL</sub>     | 0                     | 0.4                       | V    | 1     |

| Output fall time from $V_{IH}(min)$ to $V_{IL}(max)$ with a bus capacitance from 10 to 400 pF | t <sub>I2KLKV</sub> | $20 + 0.1 \times C_B$ | 250                       | ns   | 2     |

| Pulse width of spikes which must be suppressed by the input filter                            | t <sub>i2KHKL</sub> | 0                     | 50                        | ns   | 3     |

| Capacitance for each I/O pin                                                                  | Cl                  | —                     | 10                        | pF   |       |

| Input current (0 V $\leq$ V <sub>IN</sub> $\leq$ OV <sub>DD</sub> )                           | I <sub>IN</sub>     | _                     | ±5                        | μA   | 4     |

Notes:

1. Output voltage (open drain or open collector) condition = 3 mA sink current.

2.  $C_B$  = capacitance of one bus line in pF.

3. Refer to the MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Reference Manual for information on the digital filter used.

4. I/O pins obstructs the SDA and SCL lines if  $\mathsf{OV}_\mathsf{DD}$  is switched off.

# 13.2 I<sup>2</sup>C AC Electrical Specifications

The following table provides the AC timing parameters for the I<sup>2</sup>C interface of the MPC8306S.

## Table 35. I<sup>2</sup>C AC Electrical Specifications

All values refer to  $V_{IH}$  (min) and  $V_{IL}$  (max) levels (see Table 34).

| Parameter                                                                                    | Symbol <sup>1</sup> | Min                                  | Мах              | Unit |

|----------------------------------------------------------------------------------------------|---------------------|--------------------------------------|------------------|------|

| SCL clock frequency                                                                          | f <sub>I2C</sub>    | 0                                    | 400              | kHz  |

| Low period of the SCL clock                                                                  | t <sub>I2CL</sub>   | 1.3                                  | _                | μs   |

| High period of the SCL clock                                                                 | t <sub>I2CH</sub>   | 0.6                                  | _                | μS   |

| Setup time for a repeated START condition                                                    | t <sub>I2SVKH</sub> | 0.6                                  | _                | μs   |

| Hold time (repeated) START condition (after this period, the first clock pulse is generated) | t <sub>I2SXKL</sub> | 0.6                                  |                  | μs   |

| Data setup time                                                                              | t <sub>I2DVKH</sub> | 100                                  | _                | ns   |

| Data hold time: I <sup>2</sup> C bus devices                                                 | t <sub>I2DXKL</sub> | 300                                  | 0.9 <sup>3</sup> | μS   |

| Rise time of both SDA and SCL signals                                                        | t <sub>I2CR</sub>   | 20 + 0.1 C <sub>B</sub> <sup>4</sup> | 300              | ns   |

| Characteristic     | Symbol          | Condition                      | Min  | Мах                    | Unit |

|--------------------|-----------------|--------------------------------|------|------------------------|------|

| Input high voltage | V <sub>IH</sub> | _                              | 2.0  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage  | V <sub>IL</sub> | _                              | -0.3 | 0.8                    | V    |

| Input current      | I <sub>IN</sub> | $0~V \leq V_{IN} \leq OV_{DD}$ | _    | ±5                     | μA   |

## Table 44. JTAG Interface DC Electrical Characteristics (continued)

## **18.2 JTAG AC Electrical Characteristics**

This section describes the AC electrical specifications for the IEEE Std. 1149.1 (JTAG) interface of the MPC8306S. The following table provides the JTAG AC timing specifications as defined in Figure 33 through Figure 36.

## Table 45. JTAG AC Timing Specifications (Independent of SYS\_CLK\_IN)<sup>1</sup>

At recommended operating conditions (see Table 2).

| Parameter                                            | Symbol <sup>2</sup>                        | Min      | Мах      | Unit | Notes |

|------------------------------------------------------|--------------------------------------------|----------|----------|------|-------|

| JTAG external clock frequency of operation           | f <sub>JTG</sub>                           | 0        | 33.3     | MHz  |       |

| JTAG external clock cycle time                       | t <sub>JTG</sub>                           | 30       | _        | ns   | _     |

| JTAG external clock pulse width measured at 1.4 V    | t <sub>JTKHKL</sub>                        | 11       | _        | ns   | _     |

| JTAG external clock rise and fall times              | t <sub>JTGR</sub> , t <sub>JTGF</sub>      | 0        | 2        | ns   | _     |

| TRST assert time                                     | t <sub>TRST</sub>                          | 25       | _        | ns   | 3     |

| Input setup times:<br>Boundary-scan data<br>TMS, TDI | t <sub>JTDVKH</sub><br>t <sub>JTIVKH</sub> | 4<br>4   |          | ns   | 4     |

| Input hold times:<br>Boundary-scan data<br>TMS, TDI  | t <sub>JTDXKH</sub><br>t <sub>JTIXKH</sub> | 10<br>10 |          | ns   | 4     |

| Valid times:<br>Boundary-scan data<br>TDO            | t <sub>jtkldv</sub><br>t <sub>jtklov</sub> | 2<br>2   | 15<br>15 | ns   | 5     |

MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Hardware Specifications, Rev. 1

JTAG

# 19 Package and Pin Listings

This section details package parameters, pin assignments, and dimensions. The MPC8306S is available in a thermally enhanced MAPBGA (mold array process-ball grid array); see Section 19.1, "Package Parameters for the MPC8306S," and Section 19.2, "Mechanical Dimensions of the MPC8306S MAPBGA," for information on the MAPBGA.

# **19.1 Package Parameters for the MPC8306S**

The package parameters are as provided in the following list.

| Package outline         | 19 mm × 19 mm                        |

|-------------------------|--------------------------------------|

| Package Type            | MAPBGA                               |

| Interconnects           | 369                                  |

| Pitch                   | 0.80 mm                              |

| Module height (typical) | 1.48 mm; Min = 1.31mm and Max 1.61mm |

| Solder Balls            | 96 Sn / 3.5 Ag / 0.5 Cu (VM package) |

| Ball diameter (typical) | 0.40 mm                              |

# 19.2 Mechanical Dimensions of the MPC8306S MAPBGA

The following figure shows the mechanical dimensions and bottom surface nomenclature of the MPC8306S, 369-MAPBGA package.

#### Package and Pin Listings

| Signal    | Package Pin Number     | Pin Type | Power Supply     | Notes |

|-----------|------------------------|----------|------------------|-------|

| LA[17]    | B14                    | 0        | OV <sub>DD</sub> | —     |

| LA[18]    | A14                    | 0        | OV <sub>DD</sub> | —     |

| LA[19]    | A15                    | 0        | OV <sub>DD</sub> | —     |

| LA[20]    | A16                    | 0        | OV <sub>DD</sub> | —     |

| LA[21]    | B16                    | 0        | OV <sub>DD</sub> | —     |

| LA[22]    | A17                    | 0        | OV <sub>DD</sub> | —     |

| LA[23]    | B17                    | 0        | OV <sub>DD</sub> | —     |

| LA[24]    | A18                    | 0        | OV <sub>DD</sub> | —     |

| LA[25]    | B19                    | 0        | OV <sub>DD</sub> | —     |

| LCS_B[0]  | A19                    | 0        | OV <sub>DD</sub> | 3     |

| LCS_B[1]  | B20                    | 0        | OV <sub>DD</sub> | 3     |

| LCS_B[2]  | A20                    | 0        | OV <sub>DD</sub> | 3     |

| LCS_B[3]  | A21                    | 0        | OV <sub>DD</sub> | 3     |

| LCLK[0]   | D13                    | 0        | OV <sub>DD</sub> | —     |

| LGPL[0]   | B22                    | 0        | OV <sub>DD</sub> |       |

| LGPL[1]   | D16                    | 0        | OV <sub>DD</sub> | —     |

| LGPL[2]   | D19                    | 0        | OV <sub>DD</sub> | —     |

| LGPL[3]   | D17                    | 0        | OV <sub>DD</sub> | —     |

| LGPL[4]   | E18                    | IO       | OV <sub>DD</sub> | —     |

| LGPL[5]   | E19                    | 0        | OV <sub>DD</sub> | —     |

| LWE_B[0]  | D15                    | 0        | OV <sub>DD</sub> | —     |

| LWE_B[1]  | D14                    | 0        | OV <sub>DD</sub> | —     |

| LBCTL     | A22                    | 0        | OV <sub>DD</sub> | —     |

| LALE      | B23                    | 0        | OV <sub>DD</sub> | —     |

|           | JTAG                   |          |                  | 1     |

| тск       | A3                     | I        | OV <sub>DD</sub> | _     |

| TDI       | B5                     | I        | OV <sub>DD</sub> | 3     |

| TDO       | D7                     | 0        | OV <sub>DD</sub> |       |

| TMS       | A4                     | I        | OV <sub>DD</sub> | 3     |

| TRST_B    | D8                     | I        | OV <sub>DD</sub> | 3     |

|           | Test Interface         |          | 1                | ı     |

| TEST_MODE | A5                     | I        | OV <sub>DD</sub> | —     |

|           | System Control Signals |          |                  |       |

| HRESET_B  | U20                    | Ю        | OV <sub>DD</sub> | 1     |

| PORESET_B | V20                    | I        | OV <sub>DD</sub> | —     |

## Table 46. MPC8306S Pinout Listing (continued)

| Table 46. MPC8306S | <b>Pinout Listing (continued)</b> |

|--------------------|-----------------------------------|

|--------------------|-----------------------------------|

| Signal                                                       | Package Pin Number    | Pin Type | Power Supply     | Notes |

|--------------------------------------------------------------|-----------------------|----------|------------------|-------|

|                                                              | Clock Interface       |          |                  |       |

| QE_CLK_IN                                                    | P23                   | I        | OV <sub>DD</sub> | _     |

| SYS_CLK_IN                                                   | R23                   | I        | OV <sub>DD</sub> | —     |

| RTC_PIT_CLOCK                                                | V23                   | I        | OV <sub>DD</sub> | —     |

|                                                              | Miscellaneous Signals |          | •                | Į     |

| QUIESCE_B                                                    | A2                    | 0        | OV <sub>DD</sub> | —     |

| THERM0                                                       | D6                    | Ι        | OV <sub>DD</sub> | _     |

|                                                              | GPIO                  |          | •                |       |

| GPIO[0]/MSRCID0 (DDR ID)                                     | E5                    | IO       | OV <sub>DD</sub> | _     |

| GPIO[1]/MSRCID1 (DDR ID)                                     | E6                    | IO       | OV <sub>DD</sub> | _     |

| GPIO[2]/MSRCID2 (DDR ID)                                     | D4                    | IO       | OV <sub>DD</sub> |       |

| GPIO[3]/MSRCID3 (DDR ID)                                     | C2                    | IO       | OV <sub>DD</sub> | —     |

| GPIO[4]/MSRCID4 (DDR ID)                                     | C1                    | IO       | OV <sub>DD</sub> | _     |

| GPIO[5]/MDVAL (DDR ID)                                       | B1                    | IO       | OV <sub>DD</sub> | _     |

| GPIO[6]/QE_EXT_REQ_3                                         | B3                    | IO       | OV <sub>DD</sub> | —     |

| GPIO[7]/QE_EXT_REQ_1                                         | B2                    | IO       | OV <sub>DD</sub> | —     |

|                                                              | USB                   |          |                  |       |

| USBDR_PWRFAULT/IIC_SDA2/CE_PIO_1                             | AC4                   | IO       | OV <sub>DD</sub> | 2     |

| USBDR_CLK/UART2_SIN[2]/UART2_CTS_B[1]                        | Y9                    | Ι        | OV <sub>DD</sub> |       |

| USBDR_DIR/IIC_SCL2                                           | AC3                   | IO       | OV <sub>DD</sub> | 2     |

| USBDR_NXT/UART2_SIN[1]/QE_EXT_REQ_4                          | AC2                   | IO       | OV <sub>DD</sub> | —     |

| USBDR_PCTL[0]/UART2_SOUT[1]/<br>LB_POR_CFG_BOOT_ECC          | AB3                   | Ю        | OV <sub>DD</sub> | —     |

| USBDR_PCTL[1]/UART2_SOUT[2]/<br>UART2_RTS_B1/LB_POR_BOOT_ERR | Y8                    | 0        | OV <sub>DD</sub> | —     |

| USBDR_STP/QE_EXT_REQ_2                                       | W6                    | IO       | OV <sub>DD</sub> | —     |

| USBDR_TXDRXD[0]/UART1_SOUT[1]/<br>GPI0[32]/QE_TRB_O          | AB7                   | Ю        | OV <sub>DD</sub> | —     |

| USBDR_TXDRXD[1]/UART1_SIN[1]/GPIO[33]/<br>QE_TRB_I           | AB8                   | Ю        | OV <sub>DD</sub> | —     |

| USBDR_TXDRXD[2]/UART1_SOUT[2]/<br>UART1_RTS_B1/QE_BRG[1]     | AC6                   | IO       | OV <sub>DD</sub> | —     |

| USBDR_TXDRXD[3]/UART1_SIN[2]/<br>UART1_CTS_B1/QE_BRG[2]      | AC5                   | IO       | OV <sub>DD</sub> | —     |

| USBDR_TXDRXD[4]/GPIO[34]/QE_BRG[3]                           | AB5                   | Ю        | OV <sub>DD</sub> |       |

| USBDR_TXDRXD[5]/GPIO[35]/QE_BRG[4]                           | Y7                    | Ю        | OV <sub>DD</sub> |       |

| USBDR_TXDRXD[6]/GPIO[36]/QE_BRG[9]                           | Y6                    | IO       | OV <sub>DD</sub> |       |

## Table 46. MPC8306S Pinout Listing (continued)

| Signal                                                     | Package Pin Number                                                                                                                                            | Pin Type | Power Supply     | Notes |

|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|-------|

| FEC3_TXD0/TSEC_TMR_PP2/GPIO[60]                            | R20                                                                                                                                                           | IO       | OV <sub>DD</sub> | _     |

| FEC3_TXD1/TSEC_TMR_PP3/GPIO[61]                            | T22                                                                                                                                                           | IO       | OV <sub>DD</sub> |       |

| FEC3_TXD2/TSEC_TMR_ALARM1/GPIO[62]                         | T23                                                                                                                                                           | IO       | OV <sub>DD</sub> |       |

| FEC3_TXD3/TSEC_TMR_ALARM2/GPIO[63]                         | T20                                                                                                                                                           | IO       | OV <sub>DD</sub> | —     |

|                                                            | HDLC/GPIO/TDM                                                                                                                                                 |          | 1                |       |

| HDLC1_RXCLK/TDM1_RCK/GPI0[1]                               | U23                                                                                                                                                           | IO       | OV <sub>DD</sub> |       |

| HDLC1_RXD/TDM1_RD/GPIO[3]                                  | U22                                                                                                                                                           | IO       | OV <sub>DD</sub> |       |

| HDLC1_TXCLK/GPIO[0]/TDM1_TCK/<br>QE_BRG[5]                 | AC22                                                                                                                                                          | IO       | OV <sub>DD</sub> | -     |

| HDLC1_TXD/GPIO[2]/TDM1_TD/<br>CFG_RESET_SOURCE[0]          | W18                                                                                                                                                           | IO       | OV <sub>DD</sub> | —     |

| HDLC1_CD_B/GPIO[4]/TDM1_TFS                                | W19                                                                                                                                                           | IO       | OV <sub>DD</sub> | —     |

| HDLC1_CTS_B/GPIO[5]/TDM1_RFS                               | Y20                                                                                                                                                           | IO       | OV <sub>DD</sub> | —     |

| HDLC1_RTS_B/GPIO[6]/TDM1_STROBE_B/<br>CFG_RESET_SOURCE[1]  | AB22                                                                                                                                                          | Ю        | OV <sub>DD</sub> | —     |

| HDLC2_TXCLK/GPIO[16]/TDM2_TCK/<br>QE_BRG[7]                | AB23                                                                                                                                                          | IO       | OV <sub>DD</sub> | —     |

| HDLC2_RXCLK/GPIO[17]/TDM2_RCK/<br>QE_BRG[8]                | AA23                                                                                                                                                          | IO       | OV <sub>DD</sub> | —     |

| HDLC2_TXD/GPIO[18]/TDM2_TD/<br>CFG_RESET_SOURCE[2]         | W20                                                                                                                                                           | IO       | OV <sub>DD</sub> | —     |

| HDLC2_RXD/GPIO[19]/TDM2_RD                                 | Y23                                                                                                                                                           | IO       | OV <sub>DD</sub> |       |

| HDLC2_CD_B/GPIO[20]/TDM2_TFS                               | Y22                                                                                                                                                           | IO       | OV <sub>DD</sub> |       |

| HDLC2_CTS_B/GPI0[21]/TDM2_RFS                              | W23                                                                                                                                                           | IO       | OV <sub>DD</sub> | —     |

| HDLC2_RTS_B/GPIO[22]/TDM2_STROBE_B/<br>CFG_RESET_SOURCE[3] | W22                                                                                                                                                           | IO       | OV <sub>DD</sub> | _     |

|                                                            | Power                                                                                                                                                         |          |                  | 1     |

| AV <sub>DD1</sub>                                          | L16                                                                                                                                                           | —        | —                | —     |

| AV <sub>DD2</sub>                                          | M16                                                                                                                                                           | _        | —                | —     |

| AV <sub>DD3</sub>                                          | N8                                                                                                                                                            | —        | —                | —     |

| GV <sub>DD</sub>                                           | G5, H5, J5, K5, L5, M5,<br>N5, P5, R5, T5, U5                                                                                                                 | _        | _                | —     |

| OV <sub>DD</sub>                                           | E7,E8,E9,E10,E11,E12,<br>E13,E14, E15,<br>E16,E17,G19,H19,J19,K<br>19,L19,M19,<br>N19,P19,R19,T19,U19,<br>W7,W8,W9, W10,W11,<br>W12,W13, W14,W15,<br>W16, W17 | _        | _                | _     |

| RCWL[COREPLL] |      |   |                                        |             |  |  |

|---------------|------|---|----------------------------------------|-------------|--|--|

| 0-1           | 2-5  | 6 | <i>core_clk</i> : <i>csb_clk</i> Ratio | VCO Divider |  |  |

| 00            | 0001 | 1 | 1.5:1                                  | ÷ 2         |  |  |

| 01            | 0001 | 1 | 1.5:1                                  | ÷ 4         |  |  |

| 10            | 0001 | 1 | 1.5:1                                  | ÷8          |  |  |

| 11            | 0001 | 1 | 1.5:1                                  | ÷8          |  |  |

| 00            | 0010 | 0 | 2:1                                    | ÷ 2         |  |  |

| 01            | 0010 | 0 | 2:1                                    | ÷ 4         |  |  |

| 10            | 0010 | 0 | 2:1                                    | ÷8          |  |  |

| 11            | 0010 | 0 | 2:1                                    | ÷8          |  |  |

| 00            | 0010 | 1 | 2.5:1                                  | ÷2          |  |  |

| 01            | 0010 | 1 | 2.5:1                                  | ÷ 4         |  |  |

| 10            | 0010 | 1 | 2.5:1                                  | ÷8          |  |  |

| 11            | 0010 | 1 | 2.5:1                                  | ÷8          |  |  |

| 00            | 0011 | 0 | 3:1                                    | ÷ 2         |  |  |

| 01            | 0011 | 0 | 3:1                                    | ÷ 4         |  |  |

| 10            | 0011 | 0 | 3:1                                    | ÷8          |  |  |

| 11            | 0011 | 0 | 3:1                                    | ÷8          |  |  |

### Table 51. e300 Core PLL Configuration (continued)

## NOTE

Core VCO frequency = core frequency  $\times$  VCO divider. The VCO divider (RCWL[COREPLL[0:1]]), must be set properly so that the core VCO frequency is in the range of 400–800 MHz.

# 20.4 QUICC Engine PLL Configuration

The QUICC Engine PLL is controlled by the RCWL[CEPMF] and RCWL[CEPDF] parameters. The following table shows the multiplication factor encodings for the QUICC Engine PLL.

| RCWL[CEPMF] | RCWL[CEPDF] | QUICC Engine PLL Multiplication Factor = RCWL[CEPMF]/<br>(1 + RCWL[CEPDF) |

|-------------|-------------|---------------------------------------------------------------------------|

| 00000–00001 | 0           | Reserved                                                                  |

| 00010       | 0           | × 2                                                                       |

| 00011       | 0           | × 3                                                                       |

| 00100       | 0           | × <b>4</b>                                                                |

| 00101       | 0           | × 5                                                                       |

| 00110       | 0           | × 6                                                                       |

## Table 52. QUICC Engine PLL Multiplication Factors

#### Clocking

| Conf No. | SPMF | Core<br>PLL | CEPMF | CEDF | Input Clock<br>Frequency<br>(MHz) | CSB<br>Frequency<br>(MHz) | Core<br>Frequency<br>(MHz) | QUICC<br>Engine<br>Frequency<br>(MHz) |

|----------|------|-------------|-------|------|-----------------------------------|---------------------------|----------------------------|---------------------------------------|

| 1        | 0100 | 0000100     | 0111  | 0    | 33.33                             | 133.33                    | 266.66                     | 233                                   |

| 2        | 0010 | 0000100     | 0111  | 1    | 66.67                             | 133.33                    | 266.66                     | 233                                   |

| 3        | 0100 | 0000101     | 0111  | 0    | 33.33                             | 133.33                    | 333.33                     | 233                                   |

| 4        | 0101 | 0000101     | 1001  | 0    | 25                                | 125                       | 312.5                      | 225                                   |

| 5        | 0010 | 0000101     | 0111  | 1    | 66.67                             | 133.33                    | 333.33                     | 233                                   |

## Table 54. Suggested PLL Configurations

# 21 Thermal

This section describes the thermal specifications of the MPC8306S.

# 21.1 Thermal Characteristics

The following table provides the package thermal characteristics for the 369,  $19 \times 19$  mm MAPBGA of the MPC8306S.

| Characteristic                         | Board type              | Symbol              | Value | Unit | Notes   |

|----------------------------------------|-------------------------|---------------------|-------|------|---------|

| Junction-to-ambient natural convection | Single-layer board (1s) | $R_{	hetaJA}$       | 39    | °C/W | 1, 2    |

| Junction-to-ambient natural convection | Four-layer board (2s2p) | $R_{	ext{	heta}JA}$ | 24    | °C/W | 1, 2, 3 |

| Junction-to-ambient (@200 ft/min)      | Single-layer board (1s) | R <sub>0JMA</sub>   | 32    | °C/W | 1, 3    |

| Junction-to-ambient (@200 ft/min)      | Four-layer board (2s2p) | R <sub>0JMA</sub>   | 21    | °C/W | 1, 3    |

| Junction-to-board                      | -                       | $R_{\thetaJB}$      | 14    | °C/W | 4       |

| Junction-to-case                       | —                       | $R_{	ext{	heta}JC}$ | 9     | °C/W | 5       |

| Junction-to-package top                | Natural convection      | Ψ <sub>JT</sub>     | 2     | °C/W | 6       |

Table 55. Package Thermal Characteristics for MAPBGA

Notes:

1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per JEDEC JESD51-2 with the single layer board horizontal. Board meets JESD51-9 specification.

- 3. Per JEDEC JESD51-6 with the board horizontal.

- 4. Thermal resistance between the die and the printed-circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- 6. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

## 21.1.1 Thermal Management Information

For the following sections,  $P_D = (V_{DD} \times I_{DD}) + P_{I/O}$ , where  $P_{I/O}$  is the power dissipation of the I/O drivers.

## 21.1.2 Estimation of Junction Temperature with Junction-to-Ambient Thermal Resistance

An estimation of the chip junction temperature, T<sub>J</sub>, can be obtained from the equation:

$$T_J = T_A + (R_{\theta} J_A \times P_D)$$

Eqn. 1

where:

$T_I$  = junction temperature (°C)

The following table summarizes the signal impedance targets. The driver impedance is targeted at minimum  $V_{DD}$ , nominal  $OV_{DD}$ , 105°C.

| Impedance      | Local Bus, Ethernet, DUART, Control,<br>Configuration and Power Management | DDR DRAM  | Symbol            | Unit |

|----------------|----------------------------------------------------------------------------|-----------|-------------------|------|

| R <sub>N</sub> | 42 Target                                                                  | 20 Target | Z <sub>0</sub>    | Ω    |

| R <sub>P</sub> | 42 Target                                                                  | 20 Target | Z <sub>0</sub>    | Ω    |

| Differential   | NA                                                                         | NA        | Z <sub>DIFF</sub> | Ω    |

**Table 56. Impedance Characteristics**

**Note:** Nominal supply voltages. See Table 1,  $T_j = 105^{\circ}C$ .

# 22.5 Configuration Pin Multiplexing

The MPC8306S provides the user with power-on configuration options which can be set through the use of external pull-up or pull-down resistors of 4.7 k $\Omega$  on certain output pins (Refer to the "Reset, Clocking and Initialization" of *MPC8306S PowerQUICC II Pro Integrated Communications Processor Family Reference Manual*). These pins are generally used as output only pins in normal operation.

While HRESET is asserted however, these pins are treated as inputs. The value presented on these pins while HRESET is asserted, is latched when HRESET deasserts, at which time the input receiver is disabled and the I/O circuit takes on its normal function. Careful board layout with stubless connections to these pull-up/pull-down resistors coupled with the large value of the pull-up/pull-down resistor should minimize the disruption of signal quality or speed for output pins thus configured.

# 23 Ordering Information

This section presents ordering information for the devices discussed in this document, and it shows an example of how the parts are marked. Ordering information for the devices fully covered by this document is provided in Section 23.1, "Part Numbers Fully Addressed by This Document."

# 23.1 Part Numbers Fully Addressed by This Document

The following table provides the Freescale part numbering nomenclature for the MPC8306S family. Note that the individual part numbers correspond to a maximum processor core frequency. For available frequencies, contact your local Freescale sales office. In addition to the maximum processor core frequency, the part numbering scheme also includes the maximum effective DDR memory speed and QUICC Engine bus frequency. Each part number also contains a revision code which refers to the die mask revision number.