#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | H8/300H                                                                     |

| Core Size                  | 16-Bit                                                                      |

| Speed                      | 20MHz                                                                       |

| Connectivity               | I²C, SCI                                                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                          |

| Number of I/O              | 59                                                                          |

| Program Memory Size        | 96KB (96K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 4K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                   |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 80-BQFP                                                                     |

| Supplier Device Package    | 80-QFP (14x14)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df36049ghv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| Sect       | ion 1 O  | verview                                      | 1  |  |  |  |  |  |  |  |

|------------|----------|----------------------------------------------|----|--|--|--|--|--|--|--|

| 1.1        | Features | S                                            | 1  |  |  |  |  |  |  |  |

| 1.2        | Internal | Internal Block Diagram                       |    |  |  |  |  |  |  |  |

| 1.3        | Pin Arra | Pin Arrangement                              |    |  |  |  |  |  |  |  |

| 1.4        | Pin Fun  | ctions                                       | 5  |  |  |  |  |  |  |  |

| a .        | · • •    |                                              | 0  |  |  |  |  |  |  |  |

|            |          | PU                                           |    |  |  |  |  |  |  |  |

| 2.1        |          | Space and Memory Map                         |    |  |  |  |  |  |  |  |

| 2.2        | -        | r Configuration                              |    |  |  |  |  |  |  |  |

|            | 2.2.1    | General Registers                            |    |  |  |  |  |  |  |  |

|            | 2.2.2    | Program Counter (PC)                         |    |  |  |  |  |  |  |  |

|            | 2.2.3    | Condition-Code Register (CCR)                |    |  |  |  |  |  |  |  |

| 2.3        | Data Fo  | rmats                                        |    |  |  |  |  |  |  |  |

|            | 2.3.1    | General Register Data Formats                |    |  |  |  |  |  |  |  |

|            | 2.3.2    | Memory Data Formats                          |    |  |  |  |  |  |  |  |

| 2.4        | Instruct | ion Set                                      |    |  |  |  |  |  |  |  |

|            | 2.4.1    | List of Instructions Classified by Function  |    |  |  |  |  |  |  |  |

|            | 2.4.2    | Basic Instruction Formats                    |    |  |  |  |  |  |  |  |

| 2.5        | Address  | sing Modes and Effective Address Calculation |    |  |  |  |  |  |  |  |

|            | 2.5.1    | Addressing Modes                             |    |  |  |  |  |  |  |  |

|            | 2.5.2    | Effective Address Calculation                |    |  |  |  |  |  |  |  |

| 2.6        | Basic B  | us Cycle                                     |    |  |  |  |  |  |  |  |

|            | 2.6.1    | Access to On-Chip Memory (RAM, ROM)          |    |  |  |  |  |  |  |  |

|            | 2.6.2    | On-Chip Peripheral Modules                   |    |  |  |  |  |  |  |  |

| 2.7        | CPU Sta  | ates                                         |    |  |  |  |  |  |  |  |

| 2.8        | Usage N  | Notes                                        |    |  |  |  |  |  |  |  |

|            | 2.8.1    | Notes on Data Access to Empty Areas          |    |  |  |  |  |  |  |  |

|            | 2.8.2    | EEPMOV Instruction                           |    |  |  |  |  |  |  |  |

|            | 2.8.3    | Bit Manipulation Instruction                 |    |  |  |  |  |  |  |  |

| <b>G</b> ( | · • • •  | .' 11 11'                                    | 12 |  |  |  |  |  |  |  |

|            |          | xception Handling                            |    |  |  |  |  |  |  |  |

| 3.1        | -        | on Sources and Vector Address                |    |  |  |  |  |  |  |  |

| 3.2        | -        | r Descriptions                               |    |  |  |  |  |  |  |  |

|            | 3.2.1    | Interrupt Edge Select Register 1 (IEGR1)     |    |  |  |  |  |  |  |  |

|            | 3.2.2    | Interrupt Edge Select Register 2 (IEGR2)     |    |  |  |  |  |  |  |  |

|            | 3.2.3    | Interrupt Enable Register 1 (IENR1)          |    |  |  |  |  |  |  |  |

# RENESAS

#### 2.3.2 Memory Data Formats

Figure 2.6 shows the data formats in memory. The H8/300H CPU can access word data and longword data in memory, however word or longword data must begin at an even address. If an attempt is made to access word or longword data at an odd address, an address error does not occur, however the least significant bit of the address is regarded as 0, so access begins the preceding address. This also applies to instruction fetches.

When ER7 (SP) is used as an address register to access the stack area, the operand size should be word or longword.

| Data Type     | Address                                                    | Data Format     |

|---------------|------------------------------------------------------------|-----------------|

|               | ſ                                                          | 7 0             |

| 1-bit data    | Address L                                                  | 7 6 5 4 3 2 1 0 |

| Byte data     | Address L                                                  | MSB LSB         |

| Word data     | Address 2M<br>Address 2M+1                                 | NSB LSB         |

| Longword data | Address 2N<br>Address 2N+1<br>Address 2N+2<br>Address 2N+3 | NSB LSB         |

|               |                                                            |                 |

Figure 2.6 Memory Data Formats

- Description on operation

- 1. When the BSET instruction is executed, first the CPU reads port 5.

Since P57 and P56 are input pins, the CPU reads the pin states (low-level and high-level input).

P55 to P50 are output pins, so the CPU reads the value in PDR5. In this example PDR5 has a value of H'80, but the value read by the CPU is H'40.

- 2. Next, the CPU sets bit 0 of the read data to 1, changing the PDR5 data to H'41.

- 3. Finally, the CPU writes H'41 to PDR5, completing execution of BSET instruction. As a result of the BSET instruction, bit 0 in PDR5 becomes 1, and P50 outputs a high-level signal. However, bits 7 and 6 of PDR5 end up with different values. To prevent this problem, store a copy of the PDR5 data in a work area in memory. Perform the bit manipulation on the data in the work area, then write this data to PDR5.

#### • Prior to executing BSET instruction

| MOV.B | #80, | ROL   |

|-------|------|-------|

| MOV.B | ROL, | @RAM0 |

| MOV.B | ROL, | @PDR5 |

The PDR5 value (H'80) is written to a work area in memory (RAM0) as well as to PDR5.

|              | P57          | P56           | P55          | P54          | P53          | P52          | P51          | P50          |

|--------------|--------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Input/output | Input        | Input         | Output       | Output       | Output       | Output       | Output       | Output       |

| Pin state    | Low<br>level | High<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level |

| PCR5         | 0            | 0             | 1            | 1            | 1            | 1            | 1            | 1            |

| PDR5         | 1            | 0             | 0            | 0            | 0            | 0            | 0            | 0            |

| RAM0         | 1            | 0             | 0            | 0            | 0            | 0            | 0            | 0            |

• BSET instruction executed

BSET #0, @RAMO

The BSET instruction is executed designating the PDR5 work area (RAM0).

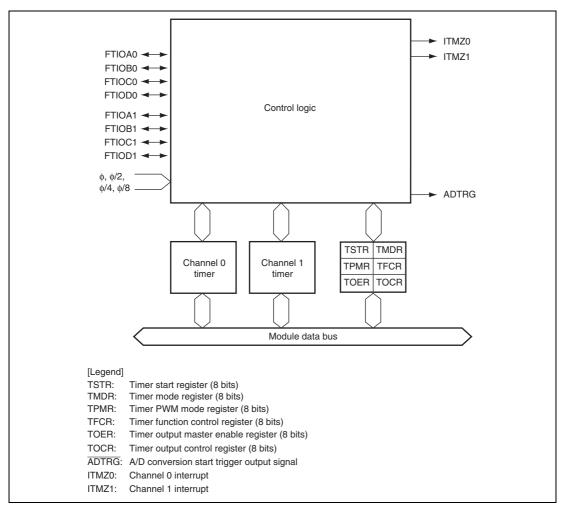

#### 5.2.2 Pin Connection when not Using Subclock

When the subclock is not used, connect pin  $X_1$  to  $V_{cL}$  or  $V_{ss}$  and leave pin  $X_2$  open, as shown in figure 5.10.

### 5.3 Prescalers

#### 5.3.1 Prescaler S

Prescaler S is a 13-bit counter using the system clock ( $\phi$ ) as its input clock. It is incremented once per clock period. Prescaler S is initialized to H'0000 by a reset, and starts counting on exit from the reset state. In standby mode, subactive mode, and subsleep mode, the system clock pulse generator stops. Prescaler S also stops and is initialized to H'0000. The CPU cannot read or write prescaler S. The output from prescaler S is shared by the on-chip peripheral modules. The divider ratio can be set separately for each on-chip peripheral function. In active mode and sleep mode, the clock input to prescaler S is determined by the division factor designated by the MA2 to MA0 bits in SYSCR2.

#### 5.3.2 Prescaler W

Prescaler W is a 5-bit counter using a 32.768 kHz signal divided by 4 ( $\phi_w/4$ ) as its input clock. The divided output is used for clock time base operation of timer A. Prescaler W is initialized to H'00 by a reset, and starts counting on exit from the reset state. Even in standby mode, subactive mode, or subsleep mode, prescaler W continues functioning so long as clock signals are supplied to pins  $X_1$  and  $X_2$ .

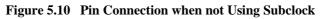

#### Table 7.2 Boot Mode Operation

### • P22/TXD pin

| Register      | PMR1 | PCR2  |                |

|---------------|------|-------|----------------|

| Bit Name      | TXD  | PCR22 | Pin Function   |

| Setting Value | 0    | 0     | P22 input pin  |

|               |      | 1     | P22 output pin |

|               | 1    | Х     | TXD output pin |

[Legend] X: Don't care.

#### • P21/RXD pin

| Register      | SCR3 | PCR2  |                |

|---------------|------|-------|----------------|

| Bit Name      | RE   | PCR21 | Pin Function   |

| Setting Value | 0    | 0     | P21 input pin  |

|               |      | 1     | P21 output pin |

|               | 1    | Х     | RXD input pin  |

[Legend] X: Don't care.

### • P20/SCK3 pin

| Register      | SCR3 |      | SMR | PCR2  |                 |

|---------------|------|------|-----|-------|-----------------|

| Bit Name      | CKE1 | CKE0 | СОМ | PCR20 | Pin Function    |

| Setting Value | 0    | 0    | 0   | 0     | P20 input pin   |

|               |      |      |     | 1     | P20 output pin  |

|               | 0    | 0    | 1   | Х     | SCK3 output pin |

|               | 0    | 1    | Х   | Х     | SCK3 output pin |

|               | 1    | Х    | Х   | Х     | SCK3 input pin  |

[Legend] X: Don't care.

| PCR3  |                |

|-------|----------------|

| PCR30 | Pin Function   |

| 0     | P30 input pin  |

| 1     | P30 output pin |

| -     | PCR30          |

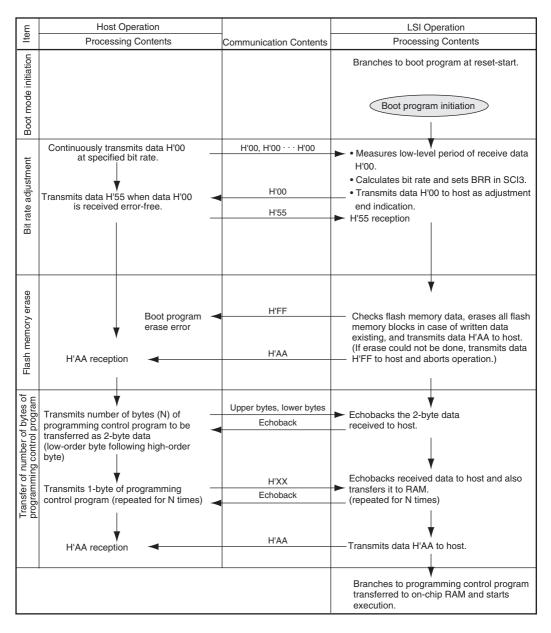

### 9.4 Port 5

Port 5 is a general I/O port also functioning as an I<sup>2</sup>C bus interface I/O pin, an A/D trigger input pin, and a wakeup interrupt input pin. Each pin of the port 5 is shown in figure 9.4. The register setting of the I<sup>2</sup>C bus interface has priority for functions of the pins P57/SCL and P56/SDA. Since the output buffer for pins P56 and P57 has the NMOS push-pull structure, it differs from an output buffer with the CMOS structure in the high-level output characteristics (see section 23, Electrical Characteristics).

#### Figure 9.4 Port 5 Pin Configuration

Port 5 has the following registers.

- Port mode register 5 (PMR5)

- Port control register 5 (PCR5)

- Port data register 5 (PDR5)

- Port pull-up control register 5 (PUCR5)

### 9.8.3 Pin Functions

The correspondence between the register specification and the port functions is shown below.

| • | P97 | pin |

|---|-----|-----|

|---|-----|-----|

| Register      | PCR9  |                |

|---------------|-------|----------------|

| Bit Name      | PCR97 | Pin Function   |

| Setting Value | 0     | P97 input pin  |

|               | 1     | P97 output pin |

• P96 pin

| Register      | PCR9  |                |

|---------------|-------|----------------|

| Bit Name      | PCR96 | Pin Function   |

| Setting Value | 0     | P96 input pin  |

|               | 1     | P96 output pin |

• P95 pin

| Register      | PCR9  |                |

|---------------|-------|----------------|

| Bit Name      | PCR95 | Pin Function   |

| Setting Value | 0     | P95 input pin  |

|               | 1     | P95 output pin |

• P94 pin

| Register      | PCR9  |                |

|---------------|-------|----------------|

| Bit Name      | PCR94 | Pin Function   |

| Setting Value | 0     | P94 input pin  |

|               | 1     | P94 output pin |

• P93 pin

| Register      | PCR9  |                |

|---------------|-------|----------------|

| Bit Name      | PCR93 | Pin Function   |

| Setting Value | 0     | P93 input pin  |

|               | 1     | P93 output pin |

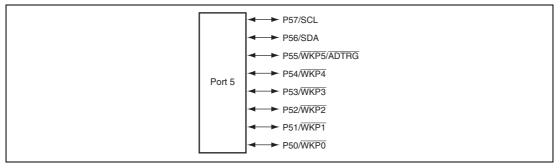

Figure 14.1 Timer Z Block Diagram

# 14.4 Operation

### 14.4.1 Counter Operation

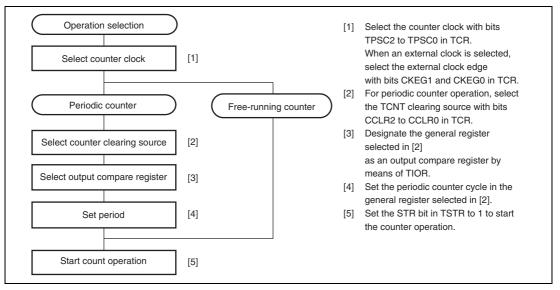

When one of bits STR0 and STR1 in TSTR is set to 1, the TCNT counter for the corresponding channel begins counting. TCNT can operate as a free-running counter, periodic counter, for example. Figure 14.7 shows an example of the counter operation setting procedure.

Figure 14.7 Example of Counter Operation Setting Procedure

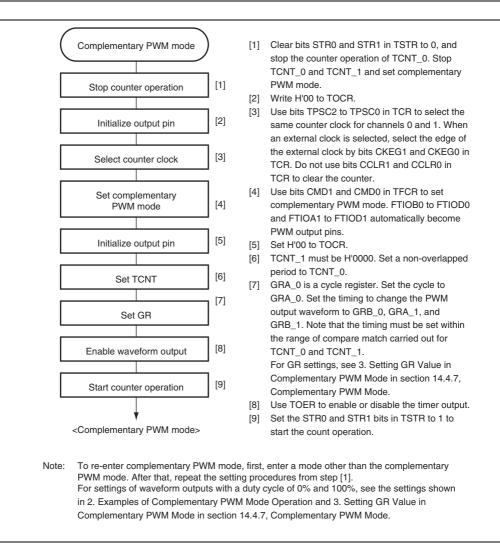

### 14.4.7 Complementary PWM Mode

Three PWM waveforms for non-overlapped normal and counter phases are output by combining channels 0 and 1.

In complementary PWM mode, the FTIOB0 to FTIOD0 and FTIOA1 to FTIOD1 pins become PWM-output pins automatically. TCNT\_0 and TCNT\_1 perform an increment or decrement operation. Tables 14.6 and 14.7 show the output pins and register settings in complementary PWM mode, respectively.

Figure 14.29 shows the example of complementary PWM mode setting procedure.

| Channel | Pin Name | Input/Output | Pin Function                                                               |

|---------|----------|--------------|----------------------------------------------------------------------------|

| 0       | FTIOC0   | Output       | Toggle output in synchronous with PWM cycle                                |

| 0       | FTIOB0   | Output       | PWM output 1                                                               |

| 0       | FTIOD0   | Output       | PWM output 1 (counter-phase waveform non-<br>overlapped with PWM output 1) |

| 1       | FTIOA1   | Output       | PWM output 2                                                               |

| 1       | FTIOC1   | Output       | PWM output 2 (counter-phase waveform non-<br>overlapped with PWM output 2) |

| 1       | FTIOB1   | Output       | PWM output 3                                                               |

| 1       | FTIOD1   | Output       | PWM output 3 (counter-phase waveform non-<br>overlapped with PWM output 3) |

Table 14.6

Output Pins in Complementary PWM Mode

#### Table 14.7 Register Settings in Complementary PWM Mode

| Register | Description                                                                                    |

|----------|------------------------------------------------------------------------------------------------|

| TCNT_0   | Initial setting of non-overlapped periods (non-overlapped periods are differences with TCNT_1) |

| TCNT_1   | Initial setting of H'0000                                                                      |

| GRA_0    | Sets (upper limit value – 1) of TCNT_0                                                         |

| GRB_0    | Set a changing point of the PWM waveform output from pins FTIOB0 and FTIOD0.                   |

| GRA_1    | Set a changing point of the PWM waveform output from pins FTIOA1 and FTIOC1.                   |

| GRB_1    | Set a changing point of the PWM waveform output from pins FTIOB1 and FTIOD1.                   |

Figure 14.29 Example of Complementary PWM Mode Setting Procedure

# 15.3 Operation

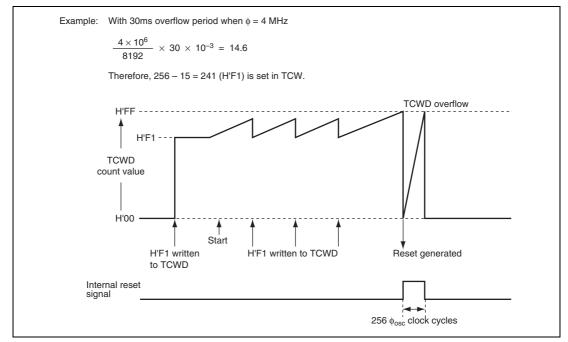

The watchdog timer is provided with an 8-bit counter. If 1 is written to WDON while writing 0 to B2WI when the TCSRWE bit in TCSRWD is set to 1, TCWD begins counting up. (To operate the watchdog timer, two write accesses to TCSRWD are required.) When a clock pulse is input after the TCWD count value has reached H'FF, the watchdog timer overflows and an internal reset signal is generated. The internal reset signal is output for a period of 256  $\phi_{osc}$  clock cycles. TCWD is a writable counter, and when a value is set in TCWD, the count-up starts from that value. An overflow period in the range of 1 to 256 input clock cycles can therefore be set, according to the TCWD set value.

Figure 15.2 shows an example of watchdog timer operation.

Figure 15.2 Watchdog Timer Operation Example

# Section 17 Serial Communication Interface 3 (SCI3)

This LSI includes a serial communication interface 3 (SCI3), which has independent three channels. The SCI3 can handle both asynchronous and clocked synchronous serial communication. In asynchronous mode, serial data communication can be carried out using standard asynchronous communication chips such as a Universal Asynchronous Receiver/Transmitter (UART) or an Asynchronous Communication Interface Adapter (ACIA). A function is also provided for serial communication between processors (multiprocessor communication function).

Table 17.1 shows the SCI3 channel configuration and figure 17.1 shows a block diagram of the SCI3. Since basic pin functions are identical for each of the three channels (SCI3, SCI3\_2, and SCI3\_3), separate explanations are not given in this section.

## 17.1 Features

- Choice of asynchronous or clocked synchronous serial communication mode

- Full-duplex communication capability

The transmitter and receiver are mutually independent, enabling transmission and reception to be executed simultaneously.

Double-buffering is used in both the transmitter and the receiver, enabling continuous transmission and continuous reception of serial data.

- On-chip baud rate generator allows any bit rate to be selected

- External clock or on-chip baud rate generator can be selected as a transfer clock source.

- Six interrupt sources

Transmit-end, transmit-data-empty, receive-data-full, overrun error, framing error, and parity error.

• Noise canceller (only for SCI3\_3)

### Asynchronous mode

- Data length: 7 or 8 bits

- Stop bit length: 1 or 2 bits

- Parity: Even, odd, or none

- Receive error detection: Parity, overrun, and framing errors

- Break detection: Break can be detected by reading the RxD pin level directly in the case of a framing error

# 17.6 Multiprocessor Communication Function

Use of the multiprocessor communication function enables data transfer between a number of processors sharing communication lines by asynchronous serial communication using the multiprocessor format, in which a multiprocessor bit is added to the transfer data. When multiprocessor communication is performed, each receiving station is addressed by a unique ID code. The serial communication cycle consists of two component cycles; an ID transmission cycle that specifies the receiving station, and a data transmission cycle. The multiprocessor bit is used to differentiate between the ID transmission cycle and the data transmission cycle. If the multiprocessor bit is 1, the cycle is an ID transmission cycle; if the multiprocessor bit is 0, the cycle is a data transmission cycle. Figure 17.15 shows an example of inter-processor communication using the multiprocessor format. The transmitting station first sends the ID code of the receiving station with which it wants to perform serial communication as data with a 1 multiprocessor bit added. When data with a 1 multiprocessor bit is received, the receiving station compares that data with its own ID. The station whose ID matches then receives the data sent next. Stations whose IDs do not match continue to skip data until data with a 1 multiprocessor bit is again received.

The SCI3 uses the MPIE bit in SCR3 to implement this function. When the MPIE bit is set to 1, transfer of receive data from RSR to RDR, error flag detection, and setting the SSR status flags, RDRF, FER, and OER, to 1, are inhibited until data with a 1 multiprocessor bit is received. On reception of a receive character with a 1 multiprocessor bit, the MPBR bit in SSR is set to 1 and the MPIE bit is automatically cleared, thus normal reception is resumed. If the RIE bit in SCR3 is set to 1 at this time, an RXI interrupt is generated.

When the multiprocessor format is selected, the parity bit setting is rendered invalid. All other bit settings are the same as those in normal asynchronous mode. The clock used for multiprocessor communication is the same as that in normal asynchronous mode.

### 18.3.7 I<sup>2</sup>C Bus Transmit Data Register (ICDRT)

ICDRT is an 8-bit readable/writable register that stores the transmit data. When ICDRT detects the space in the shift register (ICDRS), it transfers the transmit data which is written in ICDRT to ICDRS and starts transferring data. If the next transfer data is written to ICDRT during transferring data of ICDRS, continuous transfer is possible. If the MLS bit of ICMR is set to 1 and when the data is written to ICDRT, the MSB/LSB inverted data is read. The initial value of ICDRT is H'FF.

### 18.3.8 I<sup>2</sup>C Bus Receive Data Register (ICDRR)

ICDRR is an 8-bit register that stores the receive data. When data of one byte is received, ICDRR transfers the receive data from ICDRS to ICDRR and the next data can be received. ICDRR is a receive-only register, therefore the CPU cannot write to this register. The initial value of ICDRR is H'FF.

### 18.3.9 I<sup>2</sup>C Bus Shift Register (ICDRS)

ICDRS is a register that is used to transfer/receive data. In transmission, data is transferred from ICDRT to ICDRS and the data is sent from the SDA pin. In reception, data is transferred from ICDRS to ICDRR after data of one byte is received. This register cannot be read directly from the CPU.

| Register<br>Name | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Module<br>Name    |

|------------------|--------|--------|--------|--------|--------|--------|--------|--------|-------------------|

| PWDRL            | PWDRL7 | PWDRL6 | PWDRL5 | PWDRL4 | PWDRL3 | PWDRL2 | PWDRL1 | PWDRL0 | 14-bit PWM        |

| PWDRU            | _      | _      | PWDRU5 | PWDRU4 | PWDRU3 | PWDRU2 | PWDRU1 | PWDRU0 | -                 |

| PWCR             | _      | _      | _      | _      | _      | _      | _      | PWCR0  | -                 |

| TCSRWD           | B6WI   | TCWE   | B4WI   | TCSRWE | B2WI   | WDON   | BOWI   | WRST   | WDT* <sup>2</sup> |

| TCWD             | TCWD7  | TCWD6  | TCWD5  | TCWD4  | TCWD3  | TCWD2  | TCWD1  | TCWD0  | -                 |

| TMWD             | _      | _      | _      | _      | CKS3   | CKS2   | CKS1   | CKS0   | -                 |

| ABRKCR           | RTINTE | CSEL1  | CSEL0  | ACMP2  | ACMP1  | ACMP0  | DCMP1  | DCMP0  | Address           |

| ABRKSR           | ABIF   | ABIE   | _      | _      | _      | _      | _      | _      | - break           |

| BARH             | BARH7  | BARH6  | BARH5  | BARH4  | BARH3  | BARH2  | BARH1  | BARH0  | =                 |

| BARL             | BARL7  | BARL6  | BARL5  | BARL4  | BARL3  | BARL2  | BARL1  | BARL0  | =                 |

| BDRH             | BDRH7  | BDRH6  | BDRH5  | BDRH4  | BDRH3  | BDRH2  | BDRH1  | BDRH0  | -                 |

| BDRL             | BDRL7  | BDRL6  | BDRL5  | BDRL4  | BDRL3  | BDRL2  | BDRL1  | BDRL0  | =                 |

| BARE             | BARE7  | BARE6  | BARE5  | BARE4  | BARE3  | BARE2  | BARE1  | BARE0  | _                 |

| PUCR1            | PUCR17 | PUCR16 | PUCR15 | PUCR14 | _      | PUCR12 | PUCR11 | PUCR10 | I/O port          |

| PUCR5            | _      | _      | PUCR55 | PUCR54 | PUCR53 | PUCR52 | PUCR51 | PUCR50 | _                 |

| PDR1             | P17    | P16    | P15    | P14    | _      | P12    | P11    | P10    | -                 |

| PDR2             | _      | _      | _      | P24    | P23    | P22    | P21    | P20    | _                 |

| PDR3             | P37    | P36    | P35    | P34    | P33    | P32    | P31    | P30    | -                 |

| PDR5             | P57    | P56    | P55    | P54    | P53    | P52    | P51    | P50    | -                 |

| PDR6             | P67    | P66    | P65    | P64    | P63    | P62    | P61    | P60    | _                 |

| PDR7             | P77    | P76    | P75    | P74    | _      | P72    | P71    | P70    | -                 |

| PDR8             | P87    | P86    | P85    | P84    | P83    | P82    | P81    | P80    | -                 |

| PDR9             | P97    | P96    | P95    | P94    | P93    | P92    | P91    | P90    | _                 |

| PDRB             | PB7    | PB6    | PB5    | PB4    | PB3    | PB2    | PB1    | PB0    | -                 |

| PMR1             | IRQ3   | IRQ2   | IRQ1   | IRQ0   | TXD2   | PWM    | TXD    | TMOW   | -                 |

| PMR5             | POF57  | POF56  | WKP5   | WKP4   | WKP3   | WKP2   | WKP1   | WKP0   | _                 |

| PMR3             | _      | _      | _      | POF24  | POF23  | _      | _      | _      | _                 |

| PCR1             | PCR17  | PCR16  | PCR15  | PCR14  | _      | PCR12  | PCR11  | PCR10  | -                 |

| PCR2             | _      | _      | _      | PCR24  | PCR23  | PCR22  | PCR21  | PCR20  | -                 |

| PCR3             | PCR37  | PCR36  | PCR35  | PCR34  | PCR33  | PCR32  | PCR31  | PCR30  | _                 |

| PCR5             | PCR57  | PCR56  | PCR55  | PCR54  | PCR53  | PCR52  | PCR51  | PCR50  |                   |

## 22.3 Register States in Each Operating Mode

| Register<br>Name | Reset       | Active | Sleep | Subactive   | Subsleep    | Standby     | Module   |

|------------------|-------------|--------|-------|-------------|-------------|-------------|----------|

| SMR_3            | Initialized | _      | _     | Initialized | Initialized | Initialized | SCI3_3   |

| BRR_3            | Initialized | _      | _     | Initialized | Initialized | Initialized | _        |

| SCR3_3           | Initialized | _      | _     | Initialized | Initialized | Initialized | _        |

| TDR_3            | Initialized | _      | _     | Initialized | Initialized | Initialized | _        |

| SSR_3            | Initialized | _      | _     | Initialized | Initialized | Initialized | =        |

| RDR_3            | Initialized | _      | _     | Initialized | Initialized | Initialized | -        |

| SMCR_3           | Initialized | _      | _     | _           | _           | _           | -        |

| TCR_0            | Initialized | _      | _     | _           | _           | _           | Timer Z0 |

| TIORA_0          | Initialized | _      | _     | _           |             | _           | -        |

| TIORC_0          | Initialized | _      | _     | _           | _           | _           | -        |

| TSR_0            | Initialized | _      | _     | _           | _           | _           | _        |

| TIER_0           | Initialized | _      | _     | _           | _           | _           | _        |

| POCR_0           | Initialized | _      | _     | _           | _           | _           | _        |

| TCNT_0           | Initialized | _      | _     | _           | _           | _           | -        |

| GRA_0            | Initialized | _      | _     | _           | _           | _           | _        |

| GRB_0            | Initialized | _      | _     | _           | _           | _           | -        |

| GRC_0            | Initialized | _      | _     | _           | _           | _           | -        |

| GRD_0            | Initialized | _      | _     |             | _           | _           | _        |

| TCR_1            | Initialized | _      | _     | _           | _           | _           | Timer Z1 |

| TIORA_1          | Initialized | _      | _     | _           | _           | _           | -        |

| TIORC_1          | Initialized | _      | _     |             | _           | _           | _        |

| TSR_1            | Initialized | _      | _     | _           | _           | _           | _        |

| TIER_1           | Initialized | _      | _     | _           |             | _           | _        |

| POCR_1           | Initialized | _      | _     |             |             | _           | -        |

| TCNT_1           | Initialized | _      | _     | _           |             |             | _        |

| GRA_1            | Initialized | _      |       | _           |             | _           | _        |

| GRB_1            | Initialized | _      | _     |             |             | _           | -        |

| GRC_1            | Initialized | _      | _     | _           | _           | _           | _        |

| GRD_1            | Initialized | _      | _     | _           | _           | _           |          |

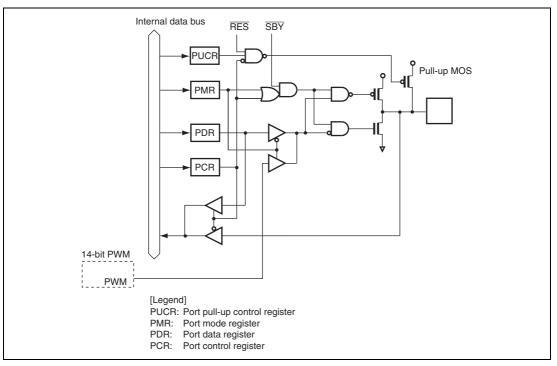

Figure B.5 Port 1 Block Diagram (P11)