Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | S12Z                                                                    |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 32MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SCI, SPI, UART/USART            |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 34                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 512 x 8                                                                 |

| RAM Size                   | 1K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 5.5V ~ 18V                                                              |

| Data Converters            | A/D 10x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-LQFP                                                                 |

| Supplier Device Package    | 48-LQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s912zvl12f0mlfr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Port | rt Pin Pin Function<br>& Priority |                             | I/O | Description                                                                            | Routing<br>Register Bit | Pin Function<br>after Reset |

|------|-----------------------------------|-----------------------------|-----|----------------------------------------------------------------------------------------|-------------------------|-----------------------------|

| Р    | PP7 <sup>3</sup>                  | (IOC1_0)                    | I/O | TIM1 channel 0                                                                         | T1C0RR                  | GPIO                        |

|      |                                   | PWM7                        | 0   | PWM option 7                                                                           | PWM7RR                  |                             |

|      |                                   | PTP[7]/<br>KWP[7]/<br>EVDD1 | I/O | General-purpose; with interrupt and key-wakeup                                         | _                       |                             |

|      | PP6                               | PWM6                        | 0   | PWM option 6                                                                           | PWM6RR                  |                             |

|      |                                   | (ETRIG0)                    | Ι   | ADC0 external trigger                                                                  | TRIGORR1:TRIGORR0       |                             |

|      |                                   | PTP[6]/<br>KWP[6]           | I/O | General-purpose; with interrupt and<br>key-wakeup                                      | —                       |                             |

|      | PP5 <sup>4</sup>                  | XIRQ <sup>5</sup>           | I   | Non-maskable level-sensitive interrupt                                                 | —                       |                             |

|      |                                   | PWM5                        | 0   | PWM option 5                                                                           | PWM5RR                  |                             |

|      |                                   | PTP[5]/<br>KWP[5]           | I/O | General-purpose; with interrupt and key-wakeup                                         | —                       |                             |

|      | PP4                               | PWM4                        | 0   | PWM option 4                                                                           | PWM4RR                  |                             |

|      |                                   | PTP[4]/<br>KWP[4]           | I/O | General-purpose; with interrupt and key-wakeup                                         | _                       |                             |

|      | PP3 <sup>4</sup>                  | ĪRQ                         | I   | Maskable level- or falling edge-sensitive interrupt                                    | _                       |                             |

|      |                                   | PWM3                        | 0   | PWM option 3                                                                           | —                       |                             |

|      |                                   | PTP[3]/<br>KWP[3]           | I/O | General-purpose; with interrupt and key-wakeup                                         | _                       |                             |

|      | PP2                               | PWM2                        | 0   | PWM option 2                                                                           | PWM2RR                  |                             |

|      |                                   | PTP[2]/<br>KWP[2]           | I/O | General-purpose; with interrupt and key-wakeup                                         | _                       |                             |

|      | PP1 <sup>4</sup>                  | (IOC1_1)                    | I/O | TIM1 channel 1                                                                         | T1C1RR                  |                             |

|      |                                   | PWM1                        | 0   | PWM option 1                                                                           | —                       |                             |

|      |                                   | PTP[1]/<br>KWP[1]           | I/O | General-purpose; with interrupt and key-wakeup                                         | _                       |                             |

| ľ    | PP0                               | PWM0                        | 0   | PWM option 0                                                                           | PWM0RR                  |                             |

|      |                                   | PTP[0]/<br>KWP[0]           | I/O | General-purpose; with interrupt and key-wakeup                                         | _                       |                             |

| J    | PJ1                               | (TXCAN0)                    | 0   | MSCAN0 transmit                                                                        | CAN0RR                  | GPIO                        |

|      |                                   | (PWM7)                      | 0   | PWM option 7                                                                           | PWM7RR                  |                             |

|      |                                   | SCL0                        | I/O | IICO                                                                                   | IICORR                  |                             |

|      |                                   | PTJ[1]                      | I/O | General-purpose                                                                        | —                       |                             |

| Ī    | PJ0                               | (RXCAN0)                    | Ι   | MSCAN0 receive                                                                         | CANORR                  |                             |

|      |                                   | (PWM5)                      | 0   | PWM option 5                                                                           | PWM5RR                  |                             |

|      |                                   | SDA0                        | I/O | IICO                                                                                   | licorr                  |                             |

|      |                                   | PTJ[0]                      | I/O | General-purpose                                                                        |                         |                             |

| L    | PL0                               | PTIL[0]/<br>KWL[0]          | Ι   | General-purpose high-voltage input (HVI); with interrupt and wakeup; optional ADC link | —                       | GPI (HVI)                   |

<sup>1</sup> Function active when RESET asserted <sup>2</sup> Routable input capture function

## 3.6.2 Register Descriptions

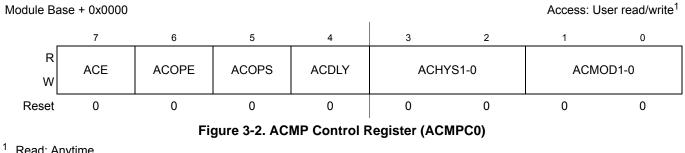

## 3.6.2.1 ACMP Control Register 0 (ACMPC0)

Read: Anytime Write: Anytime

#### Table 3-2. ACMPC0 Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ACE   | <ul> <li>ACMP Enable —         This bit enables the ACMP module. When set the related input pins are connected with the low pass input filters.     </li> <li>Note: After setting ACE to 1 an initialization delay of 127 bus clock cycles must be accounted for. During this time the comparator output path to all subsequent logic (ACO, ACIF, timer link) is held at its current state. When setting ACE to 0 the current state of the comparator will be maintained.For ACMPO a delay of t<sub>ACMP_delay_en</sub> must be accounted for.</li> <li>0 ACMP disabled</li> <li>1 ACMP enabled</li> </ul> |

| 6<br>ACOPE | ACMP Output Pin Enable —<br>This bit enables the ACMP output on external ACMPO pin.<br>0 ACMP output pin disabled<br>1 ACMP output is driven out to ACMPO                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5<br>ACOPS | ACMP Output Polarity Select —<br>This bit selects the output polarity on ACMPO.<br>0 ACMPO is ACMP output<br>1 ACMPO is ACMP output inverted                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4<br>ACDLY | ACMP Input Filter Select for Inputs ACMP_0 and ACMP_1 —<br>This bit selects the analog input filter characteristics resulting in a signal propagation delay of t <sub>ACMP_delay</sub> .<br>0 Select input filter with low speed characteristics<br>1 Select input filter with high speed characteristics                                                                                                                                                                                                                                                                                                  |

#### Background Debug Controller (S12ZBDCV2)

|                      |                           |                  |                  |                  | .11.32           |                  |   |

|----------------------|---------------------------|------------------|------------------|------------------|------------------|------------------|---|

|                      | 0x32                      |                  | Data[7-0]        |                  |                  |                  |   |

| host $\rightarrow$ A |                           | D<br>A<br>C<br>K | target →<br>host |                  |                  |                  |   |

|                      | 0x36                      |                  | Data[15-8]       | Data[7-0]        |                  |                  |   |

|                      | host → A<br>target C<br>K |                  | target →<br>host | target →<br>host |                  |                  |   |

|                      | 0x3A                      |                  | Data[31-24]      | Data[23-16]      | Data[15-8]       | Data[7-0]        |   |

|                      | host →<br>target          | D<br>A<br>C<br>K | target →<br>host | target →<br>host | target →<br>host | target →<br>host | - |

# DUMP\_MEM.sz\_WS

DUMD MEM er

Read memory specified by debug address register with status, Non-intrusive then increment address

| <br>0x33         |             | BDCCSRL          | Data[7-0]                 |                           |                  |                  |

|------------------|-------------|------------------|---------------------------|---------------------------|------------------|------------------|

| host →<br>target | D<br>L<br>Y | target →<br>host | target $\rightarrow$ host |                           |                  |                  |

| 0x37             |             | BDCCSRL          | Data[15-8]                | Data[7-0]                 |                  |                  |

| host →<br>target | D<br>L<br>Y | target →<br>host | target →<br>host          | target $\rightarrow$ host |                  |                  |

| <br>0x3B         |             | BDCCSRL          | Data[31-24]               | Data23-16]                | Data[15-8]       | Data[7-0]        |

| host →<br>target | D<br>L<br>Y | target →<br>host | target →<br>host          | target →<br>host          | target →<br>host | target →<br>host |

DUMP\_MEM{\_WS} is used with the READ\_MEM{\_WS} command to access large blocks of memory. An initial READ\_MEM{\_WS} is executed to set-up the starting address of the block and to retrieve the first result. The DUMP\_MEM{\_WS} command retrieves subsequent operands. The initial address is incremented by the operand size (1, 2, or 4) and saved in a temporary register. Subsequent DUMP\_MEM{\_WS} commands use this address, perform the memory read, increment it by the current operand size, and store the updated address in the temporary register. If the with-status option is specified, the BDCCSRL status byte is returned before the read data. This status byte reflects the state after the memory read was performed. If enabled, an ACK pulse is driven before the data bytes are transmitted. The effect of the access size and alignment on the next address to be accessed is explained in more detail in Section 5.4.5.2, "BDC Access Of Device Memory Mapped Resources". S12 Clock, Reset and Power Management Unit (S12CPMU\_UHV)

## 9.3 Memory Map and Registers

This section provides a detailed description of all registers accessible in the S12CPMU\_UHV.

### 9.3.1 Module Memory Map

The S12CPMU\_UHV registers are shown in Figure 9-3.

| Address<br>Offset | Register<br>Name            |             | Bit 7        | 6      | 5       | 4              | 3      | 2          | 1             | Bit 0          |       |       |  |             |  |  |

|-------------------|-----------------------------|-------------|--------------|--------|---------|----------------|--------|------------|---------------|----------------|-------|-------|--|-------------|--|--|

| 0x0000            | RESERVED                    | R           | 0            | 0      | 0       | 0              | 0      | 0          | 0             | 0              |       |       |  |             |  |  |

| 0,0000            | RESERVED                    | W           |              |        |         |                |        |            |               |                |       |       |  |             |  |  |

| 0.0004            | RESERVED                    | R           | 0            | 0      | 0       | 0              | U      | U          | U             | U              |       |       |  |             |  |  |

| 0x0001            | CPMU<br>VREGTRIM0           | W           |              |        |         |                |        |            |               |                |       |       |  |             |  |  |

| 0 0000            | RESERVED                    | R           | 0            | 0      | U       | U              | U      | U          | U             | U              |       |       |  |             |  |  |

| 0x0002            | CPMU<br>VREGTRIM1           | W           |              |        |         |                |        |            |               |                |       |       |  |             |  |  |

| 0x0003            | CPMURFLG                    | R           | 0            | PORF   | LVRF    | 0              | COPRF  | 0          | OMRF          | PMRF           |       |       |  |             |  |  |

| Chebbe            |                             | W           |              | i ora  | 2010    |                | 00114  |            | 0             |                |       |       |  |             |  |  |

| 0x0004            | CPMU<br>SYNR                | R<br>W      | VCOFR        | Q[1:0] |         |                | SYND   | IV[5:0]    |               |                |       |       |  |             |  |  |

| 0x0005            | CPMU                        |             | 0005         |        |         |                | CPMU F |            | REFFR         | 0[1:0]         | 0     | 0     |  | REFDIV[3:0] |  |  |

| 0x0005            | REFDIV                      | W           | NEFFN        | Q[1.0] |         |                |        |            |               |                |       |       |  |             |  |  |

| 0x0006            | CPMU                        | R           | 0            | 0      | 0       |                |        | POSTDIV[4: | 01            |                |       |       |  |             |  |  |

| 0,0000            | POSTDIV                     | W           |              |        |         |                |        |            |               |                |       |       |  |             |  |  |

| 0x0007            | 07 CPMUIELG                 | 07 CPMUIFLG | 007 CPMUIFLG | R      | RTIF    | 0              | 0      | LOCKIF     | LOCK          | 0              | OSCIF | UPOSC |  |             |  |  |

|                   | N N                         |             |              |        |         |                |        |            |               |                |       |       |  |             |  |  |

| 0x0008            | CPMUINT                     | R<br>W      | RTIE         | 0      | 0       | LOCKIE         | 0      | 0          | OSCIE         | 0              |       |       |  |             |  |  |

|                   |                             |             |              |        |         |                |        |            |               |                |       |       |  |             |  |  |

| 0x0009            | CPMUCLKS                    | R<br>W      | PLLSEL       | PSTP   | CSAD    | COP<br>OSCSEL1 | PRE    | PCE        | RTI<br>OSCSEL | COP<br>OSCSEL0 |       |       |  |             |  |  |

| 0x000A            | CPMUPLL                     | R           | 0            | 0      | FM1     | FM0            | 0      | 0          | 0             | 0              |       |       |  |             |  |  |

| 0,000,1           |                             | W           |              |        | 1 1011  | 1 100          |        |            |               |                |       |       |  |             |  |  |

| 0x000B            | CPMURTI                     | R<br>W      | RTDEC        | RTR6   | RTR5    | RTR4           | RTR3   | RTR2       | RTR1          | RTR0           |       |       |  |             |  |  |

| 0x000C            | CPMUCOP                     | R           | WCOP         | RSBCK  | 0       | 0              | 0      | CR2        | CR1           | CR0            |       |       |  |             |  |  |

| 0,0000            |                             | W           | VVCOF        | NOBUR  | WRTMASK |                |        | 0112       |               |                |       |       |  |             |  |  |

| 0x000D            | RESERVED                    | R           | 0            | 0      | 0       | 0              | 0      | 0          | 0             | 0              |       |       |  |             |  |  |

| CPMUTEST0         |                             | W           |              |        |         |                |        |            |               |                |       |       |  |             |  |  |

|                   | = Unimplemented or Reserved |             |              |        |         |                |        |            |               |                |       |       |  |             |  |  |

Figure 9-3. CPMU Register Summary

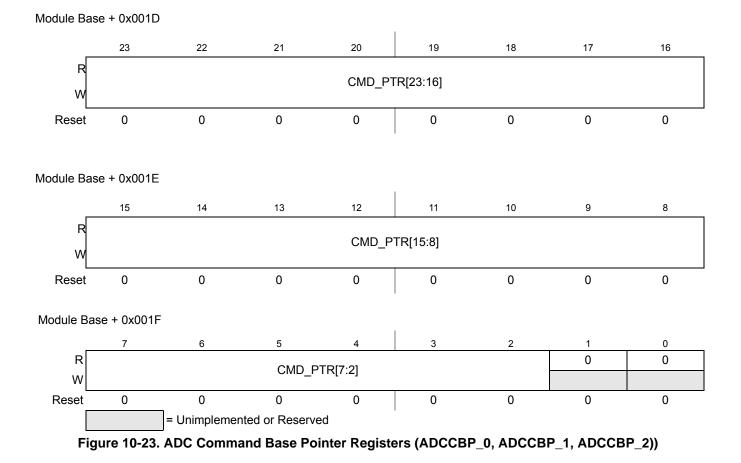

## 10.5.2.20 ADC Command Base Pointer Register (ADCCBP)

### Read: Anytime

### Write: Bits CMD\_PTR[23:2] writable if bit ADC\_EN clear or bit SMOD\_ACC set

#### Table 10-28. ADCCBP Field Descriptions

| Field                     | Description                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23-2<br>CMD_PTR<br>[23:2] | <b>ADC Command Base Pointer Address</b> — These bits define the base address of the two CSL areas inside the system RAM or NVM of the memory map. They are used to calculate the final address from which the conversion commands will be loaded depending on which list is active. For more details see Section 10.6.3.2.2, "Introduction of the two Command Sequence Lists (CSLs). |

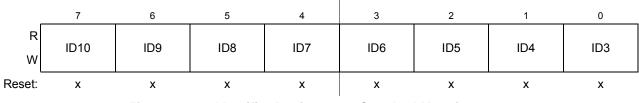

### 13.3.3.1.2 IDR0–IDR3 for Standard Identifier Mapping

Module Base + 0x00X0

Figure 13-29. Identifier Register 0 — Standard Mapping

#### Table 13-30. IDR0 Register Field Descriptions — Standard

| Field    | Description                                                                                                                                                                                                                                                                                                                                   |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ID[10:3] | <b>Standard Format Identifier</b> — The identifiers consist of 11 bits (ID[10:0]) for the standard format. ID10 is the most significant bit and is transmitted first on the CAN bus during the arbitration procedure. The priority of an identifier is defined to be highest for the smallest binary number. See also ID bits in Table 13-31. |

#### Module Base + 0x00X1

|        | 7   | 6   | 5   | 4   | 3        | 2 | 1 | 0 |

|--------|-----|-----|-----|-----|----------|---|---|---|

| R<br>W | ID2 | ID1 | ID0 | RTR | IDE (=0) |   |   |   |

| Reset: | х   | Х   | Х   | Х   | х        | Х | Х | x |

= Unused; always read 'x'

#### Figure 13-30. Identifier Register 1 — Standard Mapping

#### Table 13-31. IDR1 Register Field Descriptions

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-5<br>ID[2:0] | <b>Standard Format Identifier</b> — The identifiers consist of 11 bits (ID[10:0]) for the standard format. ID10 is the most significant bit and is transmitted first on the CAN bus during the arbitration procedure. The priority of an identifier is defined to be highest for the smallest binary number. See also ID bits in Table 13-30.                                                                                                        |

| 4<br>RTR       | <ul> <li>Remote Transmission Request — This flag reflects the status of the Remote Transmission Request bit in the CAN frame. In the case of a receive buffer, it indicates the status of the received frame and supports the transmission of an answering frame in software. In the case of a transmit buffer, this flag defines the setting of the RTR bit to be sent.</li> <li>0 Data frame</li> <li>1 Remote frame</li> </ul>                    |

| 3<br>IDE       | <ul> <li>ID Extended — This flag indicates whether the extended or standard identifier format is applied in this buffer. In the case of a receive buffer, the flag is set as received and indicates to the CPU how to process the buffer identifier registers. In the case of a transmit buffer, the flag indicates to the MSCAN what type of identifier to send.</li> <li>0 Standard format (11 bit)</li> <li>1 Extended format (29 bit)</li> </ul> |

#### Scalable Controller Area Network (S12MSCANV2)

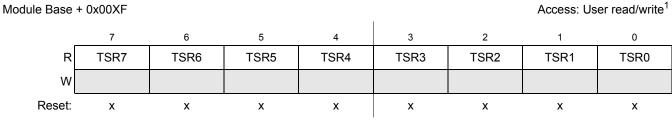

#### Figure 13-37. Time Stamp Register — Low Byte (TSRL)

<sup>1</sup> Read: or transmit buffers: Anytime when TXEx flag is set (see Section 13.3.2.7, "MSCAN Transmitter Flag Register (CANTFLG)") and the corresponding transmit buffer is selected in CANTBSEL (see Section 13.3.2.11, "MSCAN Transmit Buffer Selection Register (CANTBSEL)"). For receive buffers: Anytime when RXF is set. Write: Unimplemented

# Chapter 14 Supply Voltage Sensor (BATSV3)

| Rev. No.<br>(Item No.) | Data        | Sections<br>Affected  | Substantial Change(s)                                                                                 |  |  |  |  |

|------------------------|-------------|-----------------------|-------------------------------------------------------------------------------------------------------|--|--|--|--|

| V02.00                 | 16 Mar 2011 | 14.3.2.1<br>14.4.2.1  | <ul> <li>added BVLS[1] to support four voltage level</li> <li>moved BVHS to register bit 6</li> </ul> |  |  |  |  |

| V03.00                 | 26 Apr 2011 | allBATSV3             | - removed Vsense                                                                                      |  |  |  |  |

| V03.10                 | 04 Oct 2011 | 14.4.2.1 and 14.4.2.2 | - removed BSESE                                                                                       |  |  |  |  |

#### Table 14-1. Revision History Table

## 14.1 Introduction

The BATS module provides the functionality to measure the voltage of the chip supply pin VSUP.

### 14.1.1 Features

The VSUP pin can be routed via an internal divider to the internal Analog to Digital Converter. Independent of the routing to the Analog to Digital Converter, it is possible to route this voltage to a comparator to generate a low or a high voltage interrupt to alert the MCU.

## 14.1.2 Modes of Operation

The BATS module behaves as follows in the system power modes:

1. Run mode

The activation of the VSUP Level Sense Enable (BSUSE=1) or ADC connection Enable (BSUAE=1) closes the path from VSUP pin through the resistor chain to ground and enables the associated features if selected.

2. Stop mode

During stop mode operation the path from the VSUP pin through the resistor chain to ground is opened and the low and high voltage sense features are disabled. The content of the configuration register is unchanged.

#### Pulse-Width Modulator (S12PWM8B8CV2)

| Register<br>Name               |        | Bit 7   | 6          | 5             | 4       | 3       | 2       | 1       | Bit 0   |

|--------------------------------|--------|---------|------------|---------------|---------|---------|---------|---------|---------|

| 0x0006<br>PWMCLKAB<br>1        | R<br>W | PCLKAB7 | PCLKAB6    | PCLKAB5       | PCLKAB4 | PCLKAB3 | PCLKAB2 | PCLKAB1 | PCLKAB0 |

| 0x0007                         | R      | 0       | 0          | 0             | 0       | 0       | 0       | 0       | 0       |

| RESERVED                       | W      |         |            |               |         |         |         |         |         |

| 0x0008<br>PWMSCLA              | R<br>W | Bit 7   | 6          | 5             | 4       | 3       | 2       | 1       | Bit 0   |

| 0x0009<br>PWMSCLB              | R<br>W | Bit 7   | 6          | 5             | 4       | 3       | 2       | 1       | Bit 0   |

| 0x000A                         | R      | 0       | 0          | 0             | 0       | 0       | 0       | 0       | 0       |

| RESERVED                       | W      |         |            |               |         |         |         |         |         |

| 0x000B                         | R      | 0       | 0          | 0             | 0       | 0       | 0       | 0       | 0       |

| RESERVED                       | W      |         |            |               |         |         |         |         |         |

| 0x000C                         | R      | Bit 7   | 6          | 5             | 4       | 3       | 2       | 1       | Bit 0   |

| PWMCNT0 <sup>2</sup>           | W      | 0       | 0          | 0             | 0       | 0       | 0       | 0       | 0       |

| 0x000D                         | R      | Bit 7   | 6          | 5             | 4       | 3       | 2       | 1       | Bit 0   |

| PWMCNT1 <sup>2</sup>           | W      | 0       | 0          | 0             | 0       | 0       | 0       | 0       | 0       |

| 0x000E                         | R      | Bit 7   | 6          | 5             | 4       | 3       | 2       | 1       | Bit 0   |

| PWMCNT2 <sup>2</sup>           | w      | 0       | 0          | 0             | 0       | 0       | 0       | 0       | 0       |

| 0x000F                         | R      | Bit 7   | 6          | 5             | 4       | 3       | 2       | 1       | Bit 0   |

| PWMCNT3 <sup>2</sup>           | w      | 0       | 0          | 0             | 0       | 0       | 0       | 0       | 0       |

| 0x0010                         | R      | Bit 7   | 6          | 5             | 4       | 3       | 2       | 1       | Bit 0   |

| PWMCNT4 <sup>2</sup>           | w      | 0       | 0          | 0             | 0       | 0       | 0       | 0       | 0       |

| 0x0011                         | R      | Bit 7   | 6          | 5             | 4       | 3       | 2       | 1       | Bit 0   |

| PWMCNT5 <sup>2</sup>           | w      | 0       | 0          | 0             | 0       | 0       | 0       | 0       | 0       |

| 0x0012                         | R      | Bit 7   | 6          | 5             | 4       | 3       | 2       | 1       | Bit 0   |

| PWMCNT6 <sup>2</sup>           | w      | 0       | 0          | 0             | 0       | 0       | 0       | 0       | 0       |

| 0x0013                         | R      | Bit 7   | 6          | 5             | 4       | 3       | 2       | 1       | Bit 0   |

| PWMCNT7 <sup>2</sup>           | w      | 0       | 0          | 0             | 0       | 0       | 0       | 0       | 0       |

| 0x0014<br>PWMPER0 <sup>2</sup> | R<br>W | Bit 7   | 6          | 5             | 4       | 3       | 2       | 1       | Bit 0   |

|                                |        |         | = Unimplem | ented or Rese | rved    |         | l       | 1       |         |

### Figure 17-2. The scalable PWM Register Summary (Sheet 2 of 4)

#### Pulse-Width Modulator (S12PWM8B8CV2)

The SCI also sets a flag, the transmit data register empty flag (TDRE), every time it transfers data from the buffer (SCIDRH/L) to the transmitter shift register. The transmit driver routine may respond to this flag by writing another byte to the Transmitter buffer (SCIDRH/SCIDRL), while the shift register is still shifting out the first byte.

To initiate an SCI transmission:

- 1. Configure the SCI:

- a) Select a baud rate. Write this value to the SCI baud registers (SCIBDH/L) to begin the baud rate generator. Remember that the baud rate generator is disabled when the baud rate is zero. Writing to the SCIBDH has no effect without also writing to SCIBDL.

- b) Write to SCICR1 to configure word length, parity, and other configuration bits (LOOPS,RSRC,M,WAKE,ILT,PE,PT).

- c) Enable the transmitter, interrupts, receive, and wake up as required, by writing to the SCICR2 register bits (TIE,TCIE,RIE,ILIE,TE,RE,RWU,SBK). A preamble or idle character will now be shifted out of the transmitter shift register.

- 2. Transmit Procedure for each byte:

- a) Poll the TDRE flag by reading the SCISR1 or responding to the TDRE interrupt. Keep in mind that the TDRE bit resets to one.

- b) If the TDRE flag is set, write the data to be transmitted to SCIDRH/L, where the ninth bit is written to the T8 bit in SCIDRH if the SCI is in 9-bit data format. A new transmission will not result until the TDRE flag has been cleared.

- 3. Repeat step 2 for each subsequent transmission.

### NOTE

The TDRE flag is set when the shift register is loaded with the next data to be transmitted from SCIDRH/L, which happens, generally speaking, a little over half-way through the stop bit of the previous frame. Specifically, this transfer occurs 9/16ths of a bit time AFTER the start of the stop bit of the previous frame.

Writing the TE bit from 0 to a 1 automatically loads the transmit shift register with a preamble of 10 logic 1s (if M = 0) or 11 logic 1s (if M = 1). After the preamble shifts out, control logic transfers the data from the SCI data register into the transmit shift register. A logic 0 start bit automatically goes into the least significant bit position of the transmit shift register. A logic 1 stop bit goes into the most significant bit position.

Hardware supports odd or even parity. When parity is enabled, the most significant bit (MSB) of the data character is the parity bit.

The transmit data register empty flag, TDRE, in SCI status register 1 (SCISR1) becomes set when the SCI data register transfers a byte to the transmit shift register. The TDRE flag indicates that the SCI data register can accept new data from the internal data bus. If the transmit interrupt enable bit, TIE, in SCI control register 2 (SCICR2) is also set, the TDRE flag generates a transmitter interrupt request.

#### Serial Communication Interface (S12SCIV6)

indicating that the received byte can be read. If the receive interrupt enable bit, RIE, in SCI control register 2 (SCICR2) is also set, the RDRF flag generates an RDRF interrupt request.

### 18.4.6.3 Data Sampling

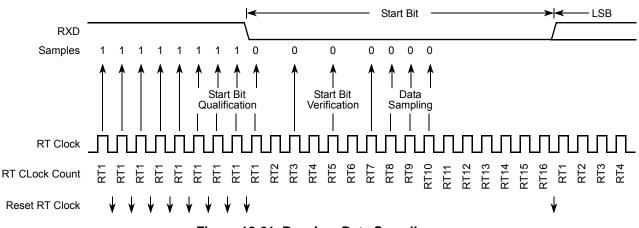

The RT clock rate. The RT clock is an internal signal with a frequency 16 times the baud rate. To adjust for baud rate mismatch, the RT clock (see Figure 18-21) is re-synchronized immediately at bus clock edge:

- After every start bit

- After the receiver detects a data bit change from logic 1 to logic 0 (after the majority of data bit samples at RT8, RT9, and RT10 returns a valid logic 1 and the majority of the next RT8, RT9, and RT10 samples returns a valid logic 0)

To locate the start bit, data recovery logic does an asynchronous search for a logic 0 preceded by three logic 1s.When the falling edge of a possible start bit occurs, the RT clock begins to count to 16.

Figure 18-21. Receiver Data Sampling

To verify the start bit and to detect noise, data recovery logic takes samples at RT3, RT5, and RT7. Figure 18-17 summarizes the results of the start bit verification samples.

| RT3, RT5, and RT7 Samples | Start Bit Verification | Noise Flag |

|---------------------------|------------------------|------------|

| 000                       | Yes                    | 0          |

| 001                       | Yes                    | 1          |

| 010                       | Yes                    | 1          |

| 011                       | No                     | 0          |

| 100                       | Yes                    | 1          |

| 101                       | No                     | 0          |

| 110                       | No                     | 0          |

| 111                       | No                     | 0          |

| Table 18-17. Start Bit Verification | Table | 18-17. | Start Bit | Verification |

|-------------------------------------|-------|--------|-----------|--------------|

|-------------------------------------|-------|--------|-----------|--------------|

If start bit verification is not successful, the RT clock is reset and a new search for a start bit begins.

| Table 19-2. SPICR1 | Field Descriptions | (continued) |

|--------------------|--------------------|-------------|

|                    |                    |             |

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3<br>CPOL  | <ul> <li>SPI Clock Polarity Bit — This bit selects an inverted or non-inverted SPI clock. To transmit data between SPI modules, the SPI modules must have identical CPOL values. In master mode, a change of this bit will abort a transmission in progress and force the SPI system into idle state.</li> <li>0 Active-high clocks selected. In idle state SCK is low.</li> <li>1 Active-low clocks selected. In idle state SCK is high.</li> </ul>     |

| 2<br>CPHA  | <ul> <li>SPI Clock Phase Bit — This bit is used to select the SPI clock format. In master mode, a change of this bit will abort a transmission in progress and force the SPI system into idle state.</li> <li>0 Sampling of data occurs at odd edges (1,3,5,) of the SCK clock.</li> <li>1 Sampling of data occurs at even edges (2,4,6,) of the SCK clock.</li> </ul>                                                                                   |

| 1<br>SSOE  | <b>Slave Select Output Enable</b> — The $\overline{SS}$ output feature is enabled only in master mode, if MODFEN is set, by asserting the SSOE as shown in Table 19-3. In master mode, a change of this bit will abort a transmission in progress and force the SPI system into idle state.                                                                                                                                                              |

| 0<br>LSBFE | <ul> <li>LSB-First Enable — This bit does not affect the position of the MSB and LSB in the data register. Reads and writes of the data register always have the MSB in the highest bit position. In master mode, a change of this bit will abort a transmission in progress and force the SPI system into idle state.</li> <li>0 Data is transferred most significant bit first.</li> <li>1 Data is transferred least significant bit first.</li> </ul> |

### Table 19-3. SS Input / Output Selection

|   | MODFEN | SSOE | Master Mode                | Slave Mode |

|---|--------|------|----------------------------|------------|

| Ī | 0      | 0    | SS not used by SPI         | SS input   |

| ſ | 0      | 1    | SS not used by SPI         | SS input   |

| ſ | 1      | 0    | SS input with MODF feature | SS input   |

| ſ | 1      | 1    | SS is slave select output  | SS input   |

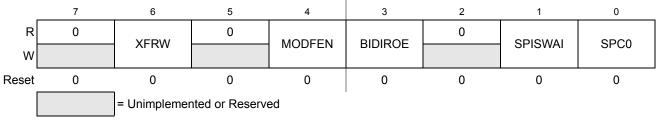

## 19.3.2.2 SPI Control Register 2 (SPICR2)

Module Base +0x0001

Figure 19-4. SPI Control Register 2 (SPICR2)

### Read: Anytime

Write: Anytime; writes to the reserved bits have no effect

| IBC[7:0]<br>(hex) | SCL Divider<br>(clocks) | SDA Hold<br>(clocks) | SCL Hold<br>(start) | SCL Hold<br>(stop) |

|-------------------|-------------------------|----------------------|---------------------|--------------------|

| 2D                | 640                     | 97                   | 318                 | 321                |

| 2E                | 768                     | 129                  | 382                 | 385                |

| 2F                | 960                     | 129                  | 478                 | 481                |

| 30                | 640                     | 65                   | 318                 | 321                |

| 31                | 768                     | 65                   | 382                 | 385                |

| 32                | 896                     | 129                  | 446                 | 449                |

| 33                | 1024                    | 129                  | 510                 | 513                |

| 34                | 1152                    | 193                  | 574                 | 577                |

| 35                | 1280                    | 193                  | 638                 | 641                |

| 36                | 1536                    | 257                  | 766                 | 769                |

| 37                | 1920                    | 257                  | 958                 | 961                |

| 38                | 1280                    | 129                  | 638                 | 641                |

| 39                | 1536                    | 129                  | 766                 | 769                |

| 3A                | 1792                    | 257                  | 894                 | 897                |

| 3B                | 2048                    | 257                  | 1022                | 1025               |

| 3C                | 2304                    | 385                  | 1150                | 1153               |

| 3D                | 2560                    | 385                  | 1278                | 1281               |

| 3E                | 3072                    | 513                  | 1534                | 1537               |

| 3F                | 3840                    | 513                  | 1918                | 1921               |

| UL=2              | 0040                    | 515                  | 1310                | 1321               |

| 40                | 40                      | 14                   | 12                  | 22                 |

| 41                | 44                      | 14                   | 14                  | 24                 |

| 42                | 48                      | 16                   | 16                  | 26                 |

| 43                | 52                      | 16                   | 18                  | 28                 |

| 44                | 56                      | 18                   | 20                  | 30                 |

| 45                | 60                      | 18                   | 22                  | 32                 |

| 46                | 68                      | 20                   | 26                  | 36                 |

| 47                | 80                      | 20                   | 32                  | 42                 |

| 48                | 56                      | 14                   | 20                  | 30                 |

| 49                | 64                      | 14                   | 24                  | 34                 |

| 40<br>4A          | 72                      | 18                   | 28                  | 38                 |

| 4B                | 80                      | 18                   | 32                  | 42                 |

| 4B<br>4C          | 88                      | 22                   | 36                  | 46                 |

| 40<br>4D          | 96                      | 22                   | 40                  | 50                 |

| 4D<br>4E          | 112                     | 22                   | 40                  | 58                 |

| 4E4F              |                         |                      |                     | 70                 |

|                   | 136<br>96               | 26                   | 60                  |                    |

| 50                |                         | 18                   | 36                  | 50                 |

| 51                | 112                     | 18                   | 44                  | 58                 |

| 52                | 128                     | 26                   | 52                  | 66                 |

| 53                | 144                     | 26                   | 60                  | 74                 |

| 54                | 160                     | 34                   | 68                  | 82                 |

| 55                | 176                     | 34                   | 76                  | 90                 |

| 56                | 208                     | 42                   | 92                  | 106                |

| 57                | 256                     | 42                   | 116                 | 130                |

| 58                | 160                     | 18                   | 76                  | 82                 |

Table 20-7. IIC Divider and Hold Values (Sheet 3 of 6)

### 20.4.1.5 Repeated START Signal

As shown in Figure 20-10, a repeated START signal is a START signal generated without first generating a STOP signal to terminate the communication. This is used by the master to communicate with another slave or with the same slave in different mode (transmit/receive mode) without releasing the bus.

### 20.4.1.6 Arbitration Procedure

The Inter-IC bus is a true multi-master bus that allows more than one master to be connected on it. If two or more masters try to control the bus at the same time, a clock synchronization procedure determines the bus clock, for which the low period is equal to the longest clock low period and the high is equal to the shortest one among the masters. The relative priority of the contending masters is determined by a data arbitration procedure, a bus master loses arbitration if it transmits logic 1 while another master transmits logic 0. The losing masters immediately switch over to slave receive mode and stop driving SDA output. In this case the transition from master to slave mode does not generate a STOP condition. Meanwhile, a status bit is set by hardware to indicate loss of arbitration.

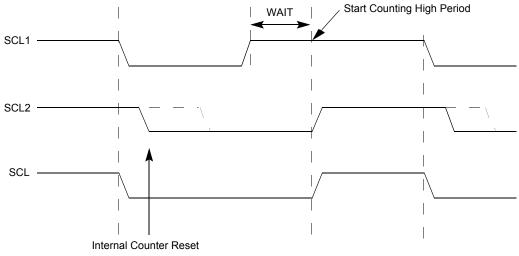

### 20.4.1.7 Clock Synchronization

Because wire-AND logic is performed on SCL line, a high-to-low transition on SCL line affects all the devices connected on the bus. The devices start counting their low period and as soon as a device's clock has gone low, it holds the SCL line low until the clock high state is reached. However, the change of low to high in this device clock may not change the state of the SCL line if another device clock is within its low period. Therefore, synchronized clock SCL is held low by the device with the longest low period. Devices with shorter low periods enter a high wait state during this time (see Figure 20-11). When all devices concerned have counted off their low period, the synchronized clock SCL line is released and pulled high. There is then no difference between the device clocks and the state of the SCL line and all the devices start counting their high periods. The first device to complete its high period pulls the SCL line low again.

Figure 20-12. IIC-Bus Clock Synchronization

| IIC       | <br> | <br>IBAL, TCF, IAAS | When either of IBAL, TCF or IAAS bits is set |

|-----------|------|---------------------|----------------------------------------------|

| Interrupt |      | bits in IBSR        | may cause an interrupt based on arbitration  |

|           |      | register            | lost, transfer complete or address detect    |

|           |      |                     | conditions                                   |

Internally there are three types of interrupts in IIC. The interrupt service routine can determine the interrupt type by reading the status register.

IIC Interrupt can be generated on

- 1. Arbitration lost condition (IBAL bit set)

- 2. Byte transfer condition (TCF bit set)

- 3. Address detect condition (IAAS bit set)

The IIC interrupt is enabled by the IBIE bit in the IIC control register. It must be cleared by writing 0 to the IBF bit in the interrupt service routine.

## 20.7 Application Information

## 20.7.1 IIC Programming Examples

### 20.7.1.1 Initialization Sequence

Reset will put the IIC bus control register to its default status. Before the interface can be used to transfer serial data, an initialization procedure must be carried out, as follows:

- 1. Update the frequency divider register (IBFD) and select the required division ratio to obtain SCL frequency from system clock.

- 2. Update the ADTYPE of IBCR2 to define the address length, 7 bits or 10 bits.

- 3. Update the IIC bus address register (IBAD) to define its slave address. If 10-bit address is applied IBCR2 should be updated to define the rest bits of address.

- 4. Set the IBEN bit of the IIC bus control register (IBCR) to enable the IIC interface system.

- 5. Modify the bits of the IIC bus control register (IBCR) to select master/slave mode, transmit/receive mode and interrupt enable or not.

- 6. If supported general call, the GCEN in IBCR2 should be asserted.

### 20.7.1.2 Generation of START

After completion of the initialization procedure, serial data can be transmitted by selecting the 'master transmitter' mode. If the device is connected to a multi-master bus system, the state of the IIC bus busy bit (IBB) must be tested to check whether the serial bus is free.

If the bus is free (IBB=0), the start condition and the first byte (the slave address) can be sent. The data written to the data register comprises the slave calling address and the LSB set to indicate the direction of transfer required from the slave.

The bus free time (i.e., the time between a STOP condition and the following START condition) is built into the hardware that generates the START cycle. Depending on the relative frequencies of the system

### 20.7.1.7 Arbitration Lost

If several masters try to engage the bus simultaneously, only one master wins and the others lose arbitration. The devices which lost arbitration are immediately switched to slave receive mode by the hardware. Their data output to the SDA line is stopped, but SCL continues to be generated until the end of the byte during which arbitration was lost. An interrupt occurs at the falling edge of the ninth clock of this transfer with IBAL=1 and MS/SL=0. If one master attempts to start transmission while the bus is being engaged by another master, the hardware will inhibit the transmission; switch the MS/SL bit from 1 to 0 without generating STOP condition; generate an interrupt to CPU and set the IBAL to indicate that the attempt to engage the bus is failed. When considering these cases, the slave service routine should test the IBAL first and the software should clear the IBAL bit if it is set.

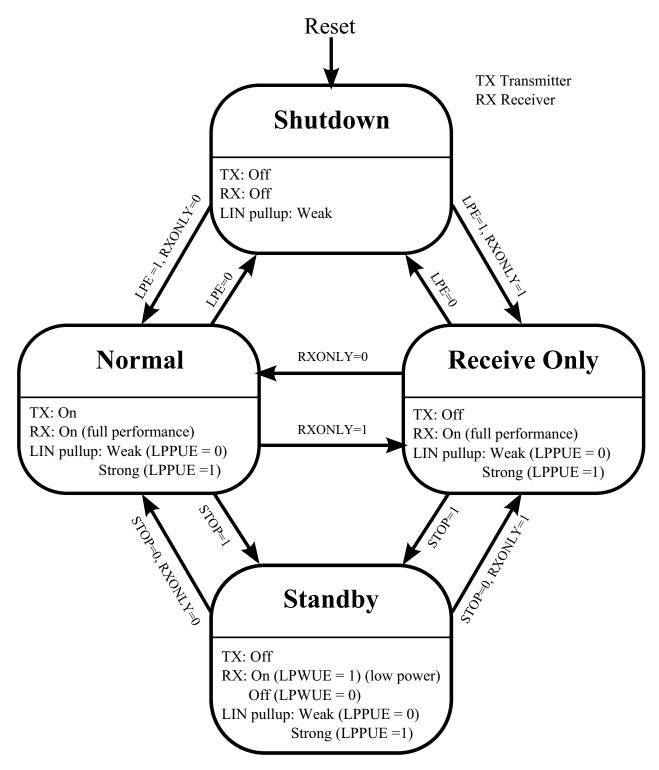

Figure 21-11. LIN Physical Layer Mode Transitions

#### **MCU Electrical Specifications**

**Detailed Register Address Map**

# O.4 0x0100-0x017F S12ZDBG (continued)

| Address       | Name     |   | Bit 7         | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

|---------------|----------|---|---------------|---|---|---|---|---|---|-------|

| 0x0141-       | Reserved | R | 0             | 0 | 0 | 0 | 0 | 0 | 0 | 0     |

| 0x0144        | 10001104 | W |               |   |   |   |   |   |   |       |

| 0x0145        | DBGDAH   | R | DBGDA[23:16]  |   |   |   |   |   |   |       |

| 0,0140        | DDOD/(II | W | W             |   |   |   |   |   |   |       |

| 0x0146        | DBGDAM   | R | R DBGDA[15:8] |   |   |   |   |   |   |       |

| 0,0140        | DDODAW   | W |               |   |   |   |   |   |   |       |

| 0x0147        | DBGDAL   | R |               |   |   |   |   |   |   |       |

| 0.0147        | DBGDAL   | W | DBGDA[7:0]    |   |   |   |   |   |   |       |

| 0x0148-       | Reserved | R | 0             | 0 | 0 | 0 | 0 | 0 | 0 | 0     |

| 0x017F Reserv | Reserveu | W |               |   |   |   |   |   |   |       |

## O.5 0x0200-0x037F PIM

| Global<br>Address | Register<br>Name | Bit 7           | 6        | 5        | 4             | 3        | 2            | 1            | Bit 0        |

|-------------------|------------------|-----------------|----------|----------|---------------|----------|--------------|--------------|--------------|

| 0x0200            | MODRR0           | R 0<br>W        | 0        | 0        | <b>IICORR</b> | SCI1RR   | S0L0RR2-0    |              |              |

| 0x0201            | MODRR1           | R<br>W PWM7RR   | PWM6RR   | PWM5RR   | PWM4RR        | 0        | PWM2RR       | 0            | PWM0RR       |

| 0x0202            | MODRR2           | R<br>W T1C1RR   | T1C0RR   | T0C5RR   | T0C4RR        | T0C3RR   | T0C2RR       | 0            | 0            |

| 0x0203            | MODRR3           | R 0<br>W        | 0        | 0        | 0             | 0        | TRIG0NE<br>G | TRIG0RR<br>1 | TRIG0RR<br>0 |

| 0x0204            | MODRR4           | R 0<br>W        | 0        | 0        | 0             | 0        | 0            | T0IC3RR1-0   |              |

| 0x0205–<br>0x0207 | Reserved         | R 0<br>W        | 0        | 0        | 0             | 0        | 0            | 0            | 0            |

| 0x0208            | ECLKCTL          | R<br>W NECLK    | 0        | 0        | 0             | 0        | 0            | 0            | 0            |

| 0x0209            | IRQCR            | R<br>W IRQE     | IRQEN    | 0        | 0             | 0        | 0            | 0            | 0            |

| 0x020A<br>0x020D  | Reserved         | R 0<br>W        | 0        | 0        | 0             | 0        | 0            | 0            | 0            |

| 0x020E            | Reserved         | R<br>W Reserved | Reserved | Reserved | Reserved      | Reserved | Reserved     | Reserved     | Reserved     |

| 0x020F            | Reserved         | R<br>Reserved   | Reserved | Reserved | Reserved      | Reserved | Reserved     | Reserved     | Reserved     |