Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | S12Z                                                                   |

| Core Size                  | 16-Bit                                                                 |

| Speed                      | 32MHz                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SCI, SPI, UART/USART           |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 34                                                                     |

| Program Memory Size        | 64KB (64K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 512 x 8                                                                |

| RAM Size                   | 1K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 5.5V ~ 18V                                                             |

| Data Converters            | A/D 10x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 48-LQFP                                                                |

| Supplier Device Package    | 48-LQFP (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s912zvl64f0clf |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table | 1-6. | Pin | Summary |

|-------|------|-----|---------|

|-------|------|-----|---------|

|    | FP /<br>N <sup>(2)</sup> | Q<br>F<br>N <sup>1</sup> |                    |              | Function             |                       |               |                       |                     | Power            | Intern<br>Resi |                |

|----|--------------------------|--------------------------|--------------------|--------------|----------------------|-----------------------|---------------|-----------------------|---------------------|------------------|----------------|----------------|

| 48 | 32                       | 32                       | Pin                | 1st<br>Func. | 2nd<br>Func.         | 3rd<br>Func.          | 4th<br>Func.  | 5th<br>Func.          | 6th<br>Func.        | Supply           | CTRL           | Reset<br>State |

| 23 | 15                       | 15                       | BCTL               | _            | _                    | _                     | _             | _                     | _                   | —                | _              | _              |

| 24 | 16                       | 16                       | LIN                | _            | _                    | _                     | _             | _                     | _                   | —                | —              | -              |

| 25 | 17                       | 17                       | LGND               | _            | _                    | _                     | _             | _                     | _                   | LGND             | _              |                |

| 26 | 18                       | 18                       | BKGD               | MODC         | —                    | —                     | _             | _                     | _                   | V <sub>DDX</sub> |                | Up             |

| 27 | 19                       | 19                       | PT1                | IOC0_1       | SCL0                 | TXD1                  | PWM0          | LPRXD0                | _                   | V <sub>DDX</sub> | PERT/<br>PPST  | Off            |

| 28 | 20                       | 20                       | PS0                | KWS0         | MISO0                | PWM4                  | RXD0          | IOC0_2                | RXCAN0 <sup>4</sup> | V <sub>DDX</sub> | PERS/<br>PPSS  | Up             |

| 29 | _                        | _                        | PT7                | IOC1_1       | _                    | _                     | _             | _                     | _                   | V <sub>DDX</sub> | PERT/<br>PPST  | Off            |

| 30 | _                        | —                        | PP0                | KWP0         | PWM0                 | _                     | _             | _                     | _                   | V <sub>DDX</sub> | PERP/<br>PPSP  | Off            |

| 31 | _                        | —                        | PP2                | KWP2         | PWM2                 | _                     | _             | _                     | _                   | V <sub>DDX</sub> | PERP/<br>PPSP  | Off            |

| 32 | _                        | _                        | PP4                | KWP4         | PWM4                 | _                     | _             | _                     | _                   | V <sub>DDX</sub> | PERP/<br>PPSP  | Off            |

| 33 | 21                       | 21                       | PS1                | KWS1         | MOSI0                | PWM6                  | TXD0<br>LPDC0 | IOC0_3                | _                   | V <sub>DDX</sub> | PERS/<br>PPSS  | Up             |

| 34 | 22                       | 22                       | PS2                | KWS2         | SCK0                 | IOC0_4                | DBGEEV        | TXCAN0 <sup>(4)</sup> | _                   | V <sub>DDX</sub> | PERS/<br>PPSS  | Up             |

| 35 | 23                       | 23                       | PS3                | KWS3         | SS0                  | IOC0_5                | ECLK          | _                     | _                   | V <sub>DDX</sub> | PERS/<br>PPSS  | Up             |

| 36 | 24                       | 24                       | RESET              | _            | —                    | —                     | —             | _                     | —                   | V <sub>DDX</sub> | TEST pin       | Up             |

| 37 | 25                       | 25                       | PP3 <sup>5</sup>   | IRQ          | KWP3                 | PWM3                  | _             | _                     | _                   | V <sub>DDX</sub> | PERP/<br>PPSP  | Off            |

| 38 | -                        | 26                       | VSSX2              | _            | —                    | _                     | —             | _                     | —                   | V <sub>DDX</sub> | —              | _              |

| 39 | 26                       | 27                       | PP5 <sup>(5)</sup> | XIRQ         | KWP5                 | PWM5                  | _             | -                     | _                   | V <sub>DDX</sub> | PERP/<br>PPSP  | Off            |

| 40 | 27                       | —                        | PT2                | IOC0_2       | ACMPO <sup>(3)</sup> | _                     | _             | _                     | _                   | V <sub>DDX</sub> | PERT/<br>PPST  | Off            |

| 41 | -                        | _                        | PJ0                | SDA0         | PWM5                 | RXCAN0 <sup>(4</sup>  | _             | _                     | _                   | V <sub>DDX</sub> | PERTJ/<br>PPSJ | Up             |

| 42 | -                        | —                        | PJ1                | SCL0         | PWM7                 | TXCAN0 <sup>(4)</sup> | _             | _                     | _                   | V <sub>DDX</sub> | PERJ/<br>PPSJ  | Up             |

| 43 | _                        | —                        | PT3                | IOC0_3       | _                    | _                     | _             | _                     |                     | V <sub>DDX</sub> | PERT/<br>PPST  | Off            |

| 44 | 28                       | 28                       | PP7 <sup>6</sup>   | KWP7         | PWM7                 | IOC1_0                | _             | _                     | _                   | V <sub>DDX</sub> | PERP/<br>PPSP  | Off            |

| 45 | 29                       | 29                       | VDDX               | _            | —                    | —                     | —             | _                     | _                   | V <sub>DDX</sub> | _              |                |

| 46 | 30                       | 30                       | VSSX1              | _            | _                    | _                     | _             | _                     | _                   | V <sub>SSX</sub> | _              |                |

MC912ZVL Family Reference Manual, Rev. 2.41

### NOTE

The term stop mode (STOP) is limited to voltage regulator operating in reduced performance mode (RPM). Refer to "Low Power Modes" section in device overview.

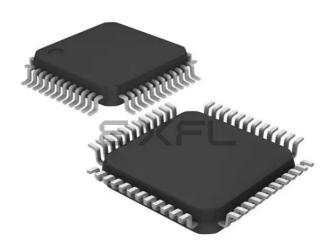

Figure 2-32. HVI Block Diagram

Voltages up to  $V_{HVI}$  can be applied to the HVI pin. Internal voltage dividers scale the input signals down to logic level. There are two modes, digital and analog, where these signals can be processed.

## 2.4.5.1 Digital Mode Operation

In digital mode (PTAENL=0) the input buffer is enabled if DIENL=1. The synchronized pin input state determined at threshold level  $V_{TH HVI}$  can be read in register PTIL. Interrupt flag (PIFL) is set on input

# Chapter 5 Background Debug Controller (S12ZBDCV2)

| Revision<br>Number | Revision<br>Date | Sections<br>Affected                                                                                  | Description of Changes                                                                                    |  |

|--------------------|------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--|

| V2.04              | 03.Dec.2012      | Section 5.1.3.3,<br>"Low-Power<br>Modes                                                               | Included BACKGROUND/ Stop mode dependency                                                                 |  |

| V2.05              | 22.Jan.2013      | Section 5.3.2.2,<br>"BDC Control<br>Status Register<br>Low (BDCCSRL)                                  | Improved NORESP description and added STEP1/ Wait mode depender                                           |  |

| V2.06              | 22.Mar.2013      | Section 5.3.2.2,<br>"BDC Control<br>Status Register<br>Low (BDCCSRL)                                  | Improved NORESP description of STEP1/ Wait mode dependency                                                |  |

| V2.07              | 11.Apr.2013      | Section 5.1.3.3.1,<br>"Stop Mode                                                                      | Improved STOP and BACKGROUND interdepency description                                                     |  |

| V2.08              | 31.May.2013      | Section 5.4.4.4,<br>"BACKGROUND<br>Section 5.4.7.1,<br>"Long-ACK<br>Hardware<br>Handshake<br>Protocol | Removed misleading WAIT and BACKGROUND interdepency description<br>Added subsection dedicated to Long-ACK |  |

| V2.09              | 29.Aug.2013      | Section 5.4.4.12,<br>"READ_DBGTB                                                                      | Noted that READ_DBGTB is only available for devices featuring a trace buffer.                             |  |

| V2.10              | 21.Oct.2013      | Section 5.1.3.3.2,<br>"Wait Mode                                                                      | Improved description of NORESP dependence on WAIT and BACKROUND                                           |  |

| V2.11              | 02.Feb.2015      | Section 5.1.3.3.1,<br>"Stop Mode<br>Section 5.3.2,<br>"Register<br>Descriptions                       | Corrected name of clock that can stay active in Stop mode                                                 |  |

Table 5-1. Revision History

## 5.1 Introduction

The background debug controller (BDC) is a single-wire, background debug system implemented in on-chip hardware for minimal CPU intervention. The device BKGD pin interfaces directly to the BDC.

The S12ZBDC maintains the standard S12 serial interface protocol but introduces an enhanced handshake protocol and enhanced BDC command set to support the linear instruction set family of S12Z devices and offer easier, more flexible internal resource access over the BDC serial interface.

$\label{eq:rescaled} \begin{array}{ll} \mbox{If XOSCLCP is enabled (OSCE=1)} & f_{REF} = \frac{f_{OSC}}{(REFDIV+1)} \\ \\ \mbox{If XOSCLCP is disabled (OSCE=0)} & f_{REF} = f_{IRC1M} \end{array}$

The REFFRQ[1:0] bits are used to configure the internal PLL filter for optimal stability and lock time. For correct PLL operation the REFFRQ[1:0] bits have to be selected according to the actual REFCLK frequency as shown in Table 9-4.

If IRC1M is selected as REFCLK (OSCE=0) the PLL filter is fixed configured for the 1MHz  $\leq f_{REF} \leq 2MHz$  range. The bits can still be written but will have no effect on the PLL filter configuration.

For OSCE=1, setting the REFFRQ[1:0] bits incorrectly can result in a non functional PLL (no locking and/or insufficient stability).

| REFCLK Frequency Ranges<br>(OSCE=1) | REFFRQ[1:0] |

|-------------------------------------|-------------|

| 1MHz <= f <sub>REF</sub> <= 2MHz    | 00          |

| 2MHz < f <sub>REF</sub> <= 6MHz     | 01          |

| 6MHz < f <sub>REF</sub> <= 12MHz    | 10          |

| f <sub>REF</sub> >12MHz             | 11          |

Table 9-4. Reference Clock Frequency Selection if OSC\_LCP is enabled

#### Table 9-34. Reset Summary

| Reset Source                   | Local Enable                                                      |

|--------------------------------|-------------------------------------------------------------------|

| Oscillator Clock Monitor Reset | OSCE Bit in CPMUOSC register and<br>OMRE Bit in CPMUOSC2 register |

| COP Reset                      | CR[2:0] in CPMUCOP register                                       |

## 9.5.2 Description of Reset Operation

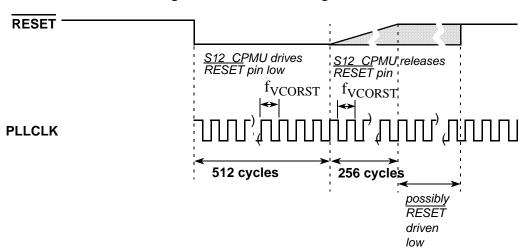

Upon detection of any reset of Table 9-34, an internal circuit drives the RESET pin low for 512 PLLCLK cycles. After 512 PLLCLK cycles the RESET pin is released. The internal reset of the MCU remains asserted while the reset generator completes the 768 PLLCLK cycles long reset sequence. In case the RESET pin is externally driven low for more than these 768 PLLCLK cycles (External Reset), the internal reset remains asserted longer.

### NOTE

While System Reset is asserted the PLLCLK runs with the frequency  $f_{\mbox{VCORST}}$

Figure 9-42. RESET Timing

## 9.5.3 Oscillator Clock Monitor Reset

If the external oscillator is enabled (OSCE=1) and the oscillator clock monitor reset is enabled (OMRE=1), then in case of loss of oscillation or the oscillator frequency drops below the failure assert frequency  $f_{CMFA}$  (see device electrical characteristics for values), the S12CPMU\_UHV generates an Oscillator Clock Monitor Reset. In Full Stop Mode the external oscillator and the oscillator clock monitor are disabled.

| Field           | Description                                                                                                                                                                                                                                                                                                                                  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>PGAOFFSCEN | <ul> <li>PGA offset compensation enable — This bit controls the switch between the plus and minus inputs of the amplifier for offset compensation.</li> <li>0 switch is off, no internal connection between PGAIN and PGAREF.</li> <li>1 PGAIN and PGAREF connected to allow offset compensation.</li> </ul>                                 |

| 0<br>PGAEN      | <ul> <li>PGA enable — This register bit enable or disables the PGA module.</li> <li>0 The PGA is disabled and in low power mode. All amplifier inputs are disconnected and all amplifier outputs are not driven.</li> <li>1 The PGA is enabled, the complete functionality and all configuration bits and features are available.</li> </ul> |

|                 | NOTE                                                                                                                                                                                                                                                                                                                                         |

|                 | After enabling, the PGA module needs a settling time $t_{PGA\_settling}$ to get fully operational.                                                                                                                                                                                                                                           |

### Table 12-3. PGAEN Field Description

## 13.1.1 Glossary

| ACK              | Acknowledge of CAN message            |

|------------------|---------------------------------------|

| CAN              | Controller Area Network               |

| CRC              | Cyclic Redundancy Code                |

| EOF              | End of Frame                          |

| FIFO             | First-In-First-Out Memory             |

| IFS              | Inter-Frame Sequence                  |

| SOF              | Start of Frame                        |

| CPU bus          | CPU related read/write data bus       |

| CAN bus          | CAN protocol related serial bus       |

| oscillator clock | Direct clock from external oscillator |

| bus clock        | CPU bus related clock                 |

| CAN clock        | CAN protocol related clock            |

Table 13-2. Terminology

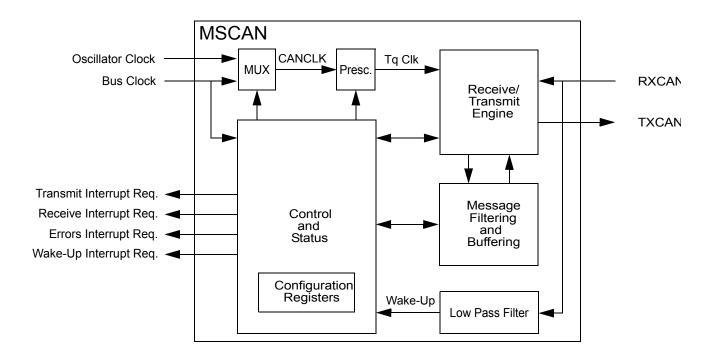

## 13.1.2 Block Diagram

Figure 13-1. MSCAN Block Diagram

| TSEG22 | TSEG21 | TSEG20 | Time Segment 2                |

|--------|--------|--------|-------------------------------|

| 0      | 0      | 0      | 1 Tq clock cycle <sup>1</sup> |

| 0      | 0      | 1      | 2 Tq clock cycles             |

| :      | :      | :      | :                             |

| 1      | 1      | 0      | 7 Tq clock cycles             |

| 1      | 1      | 1      | 8 Tq clock cycles             |

Table 13-9. Time Segment 2 Values

<sup>1</sup> This setting is not valid. Please refer to Table 13-36 for valid settings.

| TSEG13 | TSEG12 | TSEG11 | TSEG10 | Time segment 1                 |

|--------|--------|--------|--------|--------------------------------|

| 0      | 0      | 0      | 0      | 1 Tq clock cycle <sup>1</sup>  |

| 0      | 0      | 0      | 1      | 2 Tq clock cycles <sup>1</sup> |

| 0      | 0      | 1      | 0      | 3 Tq clock cycles <sup>1</sup> |

| 0      | 0      | 1      | 1      | 4 Tq clock cycles              |

| :      | :      | :      | :      | :                              |

| 1      | 1      | 1      | 0      | 15 Tq clock cycles             |

| 1      | 1      | 1      | 1      | 16 Tq clock cycles             |

Table 13-10. Time Segment 1 Values

This setting is not valid. Please refer to Table 13-36 for valid settings.

The bit time is determined by the oscillator frequency, the baud rate prescaler, and the number of time quanta (Tq) clock cycles per bit (as shown in Table 13-9 and Table 13-10).

Eqn. 13-1

Bit Time=  $\frac{(Prescaler value)}{f_{CANCLK}} \bullet (1 + TimeSegment1 + TimeSegment2)$

### 13.3.2.5 MSCAN Receiver Flag Register (CANRFLG)

A flag can be cleared only by software (writing a 1 to the corresponding bit position) when the condition which caused the setting is no longer valid. Every flag has an associated interrupt enable bit in the CANRIER register.

Module Base + 0x0004 Access: User read/write<sup>1</sup> 7 6 5 3 2 0 4 1 RSTAT1 RSTAT0 TSTAT1 TSTAT0 R WUPIF CSCIF **OVRIF** RXF W 0 0 0 0 0 0 0 Reset: 0 = Unimplemented Figure 13-8. MSCAN Receiver Flag Register (CANRFLG)

MC912ZVL Family Reference Manual, Rev. 2.41

1

## 13.4.5.7 Disabled Mode

The MSCAN is in disabled mode out of reset (CANE=0). All module clocks are stopped for power saving, however the register map can still be accessed as specified.

## 13.4.5.8 Programmable Wake-Up Function

The MSCAN can be programmed to wake up from sleep or power down mode as soon as CAN bus activity is detected (see control bit WUPE in MSCAN Control Register 0 (CANCTL0). The sensitivity to existing CAN bus action can be modified by applying a low-pass filter function to the RXCAN input line (see control bit WUPM in Section 13.3.2.2, "MSCAN Control Register 1 (CANCTL1)").

This feature can be used to protect the MSCAN from wake-up due to short glitches on the CAN bus lines. Such glitches can result from—for example—electromagnetic interference within noisy environments.

## 13.4.6 Reset Initialization

The reset state of each individual bit is listed in Section 13.3.2, "Register Descriptions," which details all the registers and their bit-fields.

## 13.4.7 Interrupts

This section describes all interrupts originated by the MSCAN. It documents the enable bits and generated flags. Each interrupt is listed and described separately.

## 13.4.7.1 Description of Interrupt Operation

The MSCAN supports four interrupt vectors (see Table 13-38), any of which can be individually masked (for details see Section 13.3.2.6, "MSCAN Receiver Interrupt Enable Register (CANRIER)" to Section 13.3.2.8, "MSCAN Transmitter Interrupt Enable Register (CANTIER)").

Refer to the device overview section to determine the dedicated interrupt vector addresses.

| Interrupt Source                          | CCR Mask | Local Enable           |

|-------------------------------------------|----------|------------------------|

| Wake-Up Interrupt (WUPIF)                 | l bit    | CANRIER (WUPIE)        |

| Error Interrupts Interrupt (CSCIF, OVRIF) | l bit    | CANRIER (CSCIE, OVRIE) |

| Receive Interrupt (RXF)                   | l bit    | CANRIER (RXFIE)        |

| Transmit Interrupts (TXE[2:0])            | I bit    | CANTIER (TXEIE[2:0])   |

Table 13-38. Interrupt Vectors

## 13.4.7.2 Transmit Interrupt

At least one of the three transmit buffers is empty (not scheduled) and can be loaded to schedule a message for transmission. The TXEx flag of the empty message buffer is set.

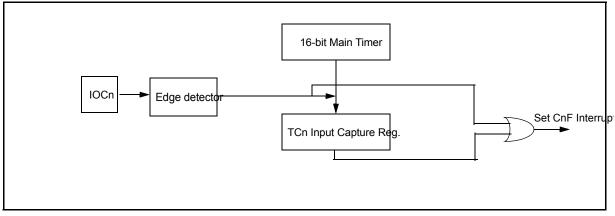

Figure 15-2. Interrupt Flag Setting

# 15.2 External Signal Description

The TIM16B6CV3 module has a selected number of external pins. Refer to device specification for exact number.

# 15.2.1 IOC5 - IOC0 — Input Capture and Output Compare Channel 5-0

Those pins serve as input capture or output compare for TIM16B6CV3 channel.

### NOTE

For the description of interrupts see Section 15.6, "Interrupts".

# 15.3 Memory Map and Register Definition

This section provides a detailed description of all memory and registers.

## 15.3.1 Module Memory Map

The memory map for the TIM16B6CV3 module is given below in Figure 15-3. The address listed for each register is the address offset. The total address for each register is the sum of the base address for the TIM16B6CV3 module and the address offset for each register.

## 15.3.2 Register Descriptions

This section consists of register descriptions in address order. Each description includes a standard register diagram with an associated figure number. Details of register bit and field function follow the register diagrams, in bit order.

| Field            | Description                                                                                                                                                                           |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6–4<br>PCKB[2:0] | <b>Prescaler Select for Clock B</b> — Clock B is one of two clock sources which can be used for all channels. These three bits determine the rate of clock B, as shown in Table 17-8. |

| 2–0<br>PCKA[2:0] | <b>Prescaler Select for Clock A</b> — Clock A is one of two clock sources which can be used for all channels. These three bits determine the rate of clock A, as shown in Table 17-8. |

#### Table 17-7. PWMPRCLK Field Descriptions

### Table 17-8. Clock A or Clock B Prescaler Selects

| PCKA/B2 | PCKA/B1 | PCKA/B0 | Value of Clock A/B |

|---------|---------|---------|--------------------|

| 0       | 0       | 0       | bus clock          |

| 0       | 0       | 1       | bus clock / 2      |

| 0       | 1       | 0       | bus clock / 4      |

| 0       | 1       | 1       | bus clock / 8      |

| 1       | 0       | 0       | bus clock / 16     |

| 1       | 0       | 1       | bus clock / 32     |

| 1       | 1       | 0       | bus clock / 64     |

| 1       | 1       | 1       | bus clock / 128    |

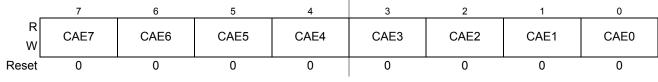

### 17.3.2.5 PWM Center Align Enable Register (PWMCAE)

The PWMCAE register contains eight control bits for the selection of center aligned outputs or left aligned outputs for each PWM channel. If the CAEx bit is set to a one, the corresponding PWM output will be center aligned. If the CAEx bit is cleared, the corresponding PWM output will be left aligned. See Section 17.4.2.5, "Left Aligned Outputs" and Section 17.4.2.6, "Center Aligned Outputs" for a more detailed description of the PWM output modes.

Module Base + 0x0004

Figure 17-7. PWM Center Align Enable Register (PWMCAE)

Read: Anytime

Write: Anytime

#### NOTE

Write these bits only when the corresponding channel is disabled.

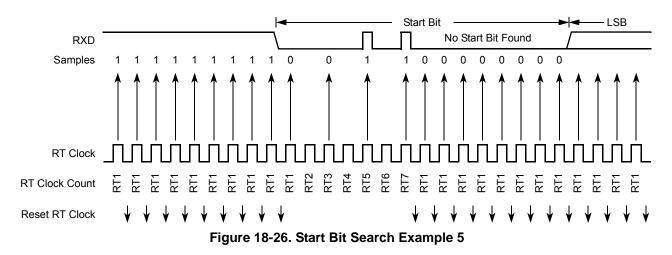

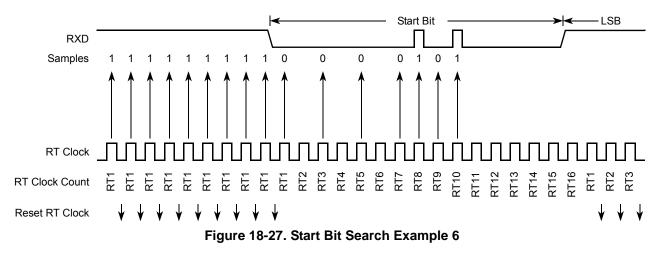

In Figure 18-27, a noise burst makes the majority of data samples RT8, RT9, and RT10 high. This sets the noise flag but does not reset the RT clock. In start bits only, the RT8, RT9, and RT10 data samples are ignored.

## 18.4.6.4 Framing Errors

If the data recovery logic does not detect a logic 1 where the stop bit should be in an incoming frame, it sets the framing error flag, FE, in SCI status register 1 (SCISR1). A break character also sets the FE flag because a break character has no stop bit. The FE flag is set at the same time that the RDRF flag is set.

### 18.4.6.5 Baud Rate Tolerance

A transmitting device may be operating at a baud rate below or above the receiver baud rate. Accumulated bit time misalignment can cause one of the three stop bit data samples (RT8, RT9, and RT10) to fall outside the actual stop bit. A noise error will occur if the RT8, RT9, and RT10 samples are not all the same logical values. A framing error will occur if the receiver clock is misaligned in such a way that the majority of the RT8, RT9, and RT10 stop bit samples are a logic zero.

## 20.4.1.11 General Call Address

To broadcast using a general call, a device must first generate the general call address(\$00), then after receiving acknowledge, it must transmit data.

In communication, as a slave device, provided the GCEN is asserted, a device acknowledges the broadcast and receives data until the GCEN is disabled or the master device releases the bus or generates a new transfer. In the broadcast, slaves always act as receivers. In general call, IAAS is also used to indicate the address match.

In order to distinguish whether the address match is the normal address match or the general call address match, IBDR should be read after the address byte has been received. If the data is \$00, the match is general call address match. The meaning of the general call address is always specified in the first data byte and must be dealt with by S/W, the IIC hardware does not decode and process the first data byte.

When one byte transfer is done, the received data can be read from IBDR. The user can control the procedure by enabling or disabling GCEN.

## 20.4.2 Operation in Run Mode

This is the basic mode of operation.

## 20.4.3 Operation in Wait Mode

IIC operation in wait mode can be configured. Depending on the state of internal bits, the IIC can operate normally when the CPU is in wait mode or the IIC clock generation can be turned off and the IIC module enters a power conservation state during wait mode. In the later case, any transmission or reception in progress stops at wait mode entry.

## 20.4.4 Operation in Stop Mode

The IIC is inactive in stop mode for reduced power consumption. The STOP instruction does not affect IIC register states.

## 20.5 Resets

The reset state of each individual bit is listed in Section 20.3, "Memory Map and Register Definition," which details the registers and their bit-fields.

## 20.6 Interrupts

IICV3 uses only one interrupt vector.

Table 20-11. Interrupt Summary

| Interrupt | Offset | Vector | Priority | Source | Description |

|-----------|--------|--------|----------|--------|-------------|

| 1         |        |        |          |        |             |

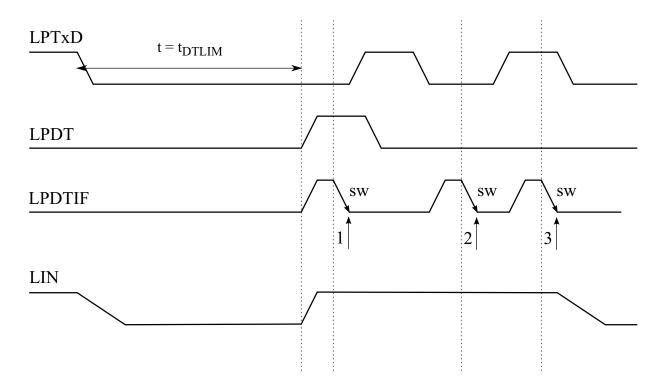

After clearing LPDTIF, if the TxD-dominant timeout condition is still present or the LPTxD pin is dominant while being in normal mode, the transmitter remains disabled and the LPDTIF flag is set after a time again to indicate that the attempt to re-enable has failed. This time is equal to:

- minimum 1 IRC period (1 us) + 2 bus periods

- maximum 2 IRC periods (2 us) + 3 bus periods

If the bit LPDTIE is set in the LPIE register, an interrupt is requested.

Figure 21-13 shows the different scenarios of TxD-dominant timeout interrupt handling.

- 1: Flag cleared, transmitter re-enable not successful because TxD-dominant timeout condition is still present

- 2: Flag cleared, transmitter re-enable not successful because LPTxD is dominant

- 3: Flag cleared, transmitter re-enable successful

Figure 21-13. TxD-dominant timeout interrupt handling

| Table 22-32. Erase Verify All Blocks | Command FCCOB Requirements |

|--------------------------------------|----------------------------|

|--------------------------------------|----------------------------|

| Register | FCCOB Parameters |              |

|----------|------------------|--------------|

| FCCOB0   | 0x01             | Not required |

Upon clearing CCIF to launch the Erase Verify All Blocks command, the Memory Controller will verify that the entire Flash memory space is erased. The CCIF flag will set after the Erase Verify All Blocks operation has completed. If all blocks are not erased, it means blank check failed, both MGSTAT bits will be set.

| Register | Error Bit | Error Condition                                                                                   |

|----------|-----------|---------------------------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 000 at command launch                                                       |

|          | FPVIOL    | None                                                                                              |

| FSTAT    | MGSTAT1   | Set if any errors have been encountered during the reador if blank check failed .                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read or if blank check failed. |

Table 22-33. Erase Verify All Blocks Command Error Handling

### 22.4.7.2 Erase Verify Block Command

The Erase Verify Block command allows the user to verify that an entire P-Flash or EEPROM block has been erased.

| Register | FCCOB Parameters                              |                                                   |

|----------|-----------------------------------------------|---------------------------------------------------|

| FCCOB0   | 0x02                                          | Global address [23:16] to<br>identify Flash block |

| FCCOB1   | Global address [15:0] to identify Flash block |                                                   |

Upon clearing CCIF to launch the Erase Verify Block command, the Memory Controller will verify that the selected P-Flash or EEPROM block is erased. The CCIF flag will set after the Erase Verify Block operation has completed. If the block is not erased, it means blank check failed, both MGSTAT bits will be set.

| Register | Error Bit | Error Condition                                                                                   |

|----------|-----------|---------------------------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 001 at command launch                                                       |

|          | ACCERK    | Set if an invalid global address [23:0] is supplied see Table 22-2)                               |

| FSTAT    | FPVIOL    | None                                                                                              |

|          | MGSTAT1   | Set if any errors have been encountered during the read or if blank check failed.                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read or if blank check failed. |

| FCCOB2 | Level Description                |

|--------|----------------------------------|

| 0x0000 | Return to Normal Level           |

| 0x0001 | User Margin-1 Level <sup>1</sup> |

| 0x0002 | User Margin-0 Level <sup>2</sup> |

Table 22-56. Valid Set User Margin Level Settings

<sup>1</sup> Read margin to the erased state

<sup>2</sup> Read margin to the programmed state

#### Table 22-57. Set User Margin Level Command Error Handling

| Register | Error Bit | Error Condition                                                     |  |

|----------|-----------|---------------------------------------------------------------------|--|

|          |           | Set if CCOBIX[2:0] != 010 at command launch                         |  |

|          | ACCERR    | Set if command not available in current mode (see Table 22-28)      |  |

|          | ACCERK    | Set if an invalid global address [23:0] is supplied see Table 22-2) |  |

| FSTAT    | FSTAT     | Set if an invalid margin level setting is supplied                  |  |

|          | FPVIOL    | None                                                                |  |

|          | MGSTAT1   | None                                                                |  |

| MGSTAT0  |           | None                                                                |  |

### NOTE

User margin levels can be used to check that Flash memory contents have adequate margin for normal level read operations. If unexpected results are encountered when checking Flash memory contents at user margin levels, a potential loss of information has been detected.

### 22.4.7.13 Set Field Margin Level Command

The Set Field Margin Level command, valid in special modes only, causes the Memory Controller to set the margin level specified for future read operations of the P-Flash or EEPROM block.

| Register | FCCOB Parameters                                    |  |

|----------|-----------------------------------------------------|--|

| FCCOB0   | 0x0E Global address [23:16] to identify Flash block |  |

| FCCOB1   | Global address [15:0] to identify Flash block       |  |

| FCCOB2   | Margin level setting.                               |  |

Table 22-58. Set Field Margin Level Command FCCOB Requirements

Upon clearing CCIF to launch the Set Field Margin Level command, the Memory Controller will set the field margin level for the targeted block and then set the CCIF flag.

maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level.

| Num | Rating                                                                                  | Symbol              | Min  | Max                | Unit |

|-----|-----------------------------------------------------------------------------------------|---------------------|------|--------------------|------|

| 1   | Voltage regulator and LINPHY supply voltage                                             | V <sub>SUP</sub>    | -0.3 | 42                 | V    |

| 2   | DC voltage on LIN                                                                       | V <sub>LIN</sub>    | -32  | 42                 | V    |

| 3   | Voltage Regulator Ballast Connection                                                    | V <sub>BCTL</sub>   | -0.3 | 42                 | V    |

| 4   | Supplies VDDA, VDDX                                                                     | V <sub>VDDACX</sub> | -0.3 | 6                  | V    |

| 5   | Voltage difference V <sub>DDX</sub> to V <sub>DDA</sub> <sup>2</sup>                    | $\Delta_{VDDX}$     | -0.3 | 0.3                | V    |

| 6   | Voltage difference V <sub>SSX</sub> to V <sub>SSA</sub>                                 | $\Delta_{VSSX}$     | -0.3 | 0.3                | V    |

| 7   | Digital I/O input voltage                                                               | V <sub>IN</sub>     | -0.3 | 6.0                | V    |

| 8   | HVI PL0 input voltage                                                                   | V <sub>Lx</sub>     | -27  | 42.0               | V    |

| 9   | EXTAL, XTAL <sup>3</sup>                                                                | V <sub>ILV</sub>    | -0.3 | 2.16               | V    |

| 10  | TEST input                                                                              | V <sub>TEST</sub>   | -0.3 | 10.0               | V    |

| 11  | Instantaneous maximum current<br>Single pin limit for all digital I/O pins <sup>4</sup> | I <sub>D</sub>      | -25  | +25                | mA   |

| 12  | Continuous current on LIN                                                               | I <sub>LIN</sub>    |      | ± 200 <sup>5</sup> | mA   |

| 13  | Instantaneous maximum current on PP7                                                    | I <sub>PP7</sub>    | -80  | +25                | mA   |

| 14  | Instantaneous maximum current on PP1, PP3 <sup>6</sup> and PP5 <sup>6</sup>             | I <sub>PP135</sub>  | -30  | +80                | mA   |

| 15  | Instantaneous maximum current<br>Single pin limit for EXTAL, XTAL                       | I <sub>DL</sub>     | -25  | +25                | mA   |

| 16  | Storage temperature range                                                               | T <sub>stg</sub>    | -65  | 155                | °C   |

### Table A-3. Absolute Maximum Ratings<sup>1</sup>

<sup>1</sup> Beyond absolute maximum ratings device might be damaged.

<sup>2</sup> VDDX and VDDA must be shorted

<sup>3</sup> EXTAL, XTAL pins configured for external oscillator operation only

<sup>4</sup> All digital I/O pins are internally clamped to  $V_{SSX}$  and  $V_{DDX}$ , or  $V_{SSA}$  and  $V_{DDA}$ .

<sup>5</sup> The current on the LIN pin is internally limited. Therefore, it should not be possible to reach the 200mA anyway.

<sup>6</sup> only applicable for PP3 and PP5 if pin VSSX2 is available

## A.1.4 ESD Protection and Latch-up Immunity

All ESD testing is in conformity with CDF-AEC-Q100 stress test qualification for automotive grade integrated circuits. During the device qualification ESD stresses were performed for the Human Body Model (HBM) and the Charged-Device Model.

A device will be defined as a failure if after exposure to ESD pulses the device no longer meets the device specification. Complete DC parametric and functional testing is performed per the applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

# **B.2** IRC and OSC Electrical Specifications

Table B-3. IRC electrical characteristics

| Num | Rating                                                                                      | Symbol                  | Min    | Тур   | Max    | Unit |

|-----|---------------------------------------------------------------------------------------------|-------------------------|--------|-------|--------|------|

| 1   | Junction Temperature - 40° to 150° Celsius<br>Internal Reference Frequency, factory trimmed | firc1m_trim             | 0.987  | 1.000 | 1.013  | MHz  |

| 2   | Junction Temperature 150° to 175° Celsius<br>Internal Reference Frequency, factory trimmed  | f <sub>IRC1M_TRIM</sub> | 0.9855 |       | 1.0145 | MHz  |

| Num | Rating                                                   | Symbol                 | Min | Тур | Max  | Unit |

|-----|----------------------------------------------------------|------------------------|-----|-----|------|------|

| 1   | Nominal crystal or resonator frequency                   | f <sub>OSC</sub>       | 4.0 | —   | 20   | MHz  |

| 2   | Startup Current                                          | i <sub>osc</sub>       | 100 | —   | —    | μA   |

| 3a  | Oscillator start-up time (4MHz) <sup>1</sup>             | t <sub>UPOSC</sub>     | —   | 2   | 10   | ms   |

| 3b  | Oscillator start-up time (8MHz) <sup>1</sup>             | t <sub>UPOSC</sub>     | —   | 1.6 | 8    | ms   |

| 3c  | Oscillator start-up time (16MHz) <sup>1</sup>            | t <sub>UPOSC</sub>     | —   | 1   | 5    | ms   |

| 3d  | Oscillator start-up time (20MHz) <sup>1</sup>            | t <sub>UPOSC</sub>     | —   | 1   | 4    | ms   |

| 4   | Clock Monitor Failure Assert Frequency                   | f <sub>CMFA</sub>      | 200 | 450 | 1200 | KHz  |

| 5   | Input Capacitance (EXTAL, XTAL pins)                     | C <sub>IN</sub>        | —   | 7   | —    | pF   |

| 6   | EXTAL Pin Input Hysteresis                               | V <sub>HYS,EXTAL</sub> | —   | 120 | —    | mV   |

| 7   | EXTAL Pin oscillation amplitude (loop controlled Pierce) | V <sub>PP,EXTAL</sub>  | -   | 1.0 | —    | V    |

| 8   | EXTAL Pin oscillation required amplitude <sup>2</sup>    | V <sub>PP,EXTAL</sub>  | 0.8 | —   | 1.5  | V    |

Table B-4. OSC electrical characteristics

<sup>1</sup> These values apply for carefully designed PCB layouts with capacitors that match the crystal/resonator requirements.

<sup>2</sup> Needs to be measured at room temperature on the application board using a probe with very low (<=5pF) input capacitance.</p>

# B.3 Phase Locked Loop

## **B.3.1** Jitter Information

With each transition of the feedback clock, the deviation from the reference clock is measured and the input voltage to the VCO is adjusted accordingly. The adjustment is done continuously with no abrupt changes in the VCOCLK frequency. Noise, voltage, temperature and other factors cause slight variations in the control loop resulting in a clock jitter. This jitter affects the real minimum and maximum clock periods as illustrated in Figure B-2.

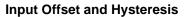

**ACMP Electrical Specifications**

Characteristics noted under conditions  $3.20V \le V_{DDA} \le 5.15V$ ,  $-40^{\circ}C \le T_J \le 175^{\circ}C^1$  unless otherwise noted. Typical values noted reflect the approximate parameter mean at  $T_A = 25^{\circ}C^2$  under nominal conditions unless otherwise noted.

| notou. |                                                                                                                               |                        |                         |                           |                            |                      |

|--------|-------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------------------|---------------------------|----------------------------|----------------------|

| Num    | Ratings                                                                                                                       | Symbol                 | Min                     | Тур                       | Max                        | Unit                 |

| 6      | Input Hysteresis in run mode<br>• [ACHYS] = 00<br>• [ACHYS] = 01<br>• [ACHYS] = 10<br>• [ACHYS] = 11                          | V <sub>ACMP_hyst</sub> | -3<br>-10<br>-30<br>-50 | -12<br>-24<br>-60<br>-125 | -22<br>-40<br>-100<br>-200 | mV<br>mV<br>mV<br>mV |

| 7      | Common Mode Input range<br>• V <sub>ACMP_0</sub><br>• V <sub>ACMP_1</sub><br>• V <sub>acmpi_0</sub><br>• V <sub>acmpi_1</sub> | V <sub>ACMP_in</sub>   | 0                       | V <sub>DDA</sub> /<br>2   | V <sub>DDA</sub>           | V                    |

$^{1}$  T<sub>J</sub>: Junction Temperature  $^{2}$  T<sub>A</sub>: Ambient Temperature