Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | S12Z                                                                    |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 32MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SCI, SPI, UART/USART            |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 34                                                                      |

| Program Memory Size        | 64KB (64K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 512 x 8                                                                 |

| RAM Size                   | 1K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 5.5V ~ 18V                                                              |

| Data Converters            | A/D 10x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-LQFP                                                                 |

| Supplier Device Package    | 48-LQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s912zvl64f0clfr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.4.2.2 Flash

On-chip flash memory on the MC9S12ZVL-Family

- Up to 128 KB of program flash memory

- Automated program and erase algorithm

- Protection scheme to prevent accidental program or erase

# 1.4.2.3 EEPROM

- Up to 2048 bytes EEPROM

- 16 data bits plus 6 syndrome ECC (error correction code) bits allow single bit error correction and double fault detection

- Erase sector size 4 bytes

- Automated program and erase algorithm

- User margin level setting for reads

## 1.4.2.4 SRAM

- Up to 8 KB of general-purpose RAM with ECC

- Single bit error correction and double bit error detection code based on 16-bit data words

# 1.4.3 Clocks, Reset & Power Management Unit (CPMU)

- Real time interrupt (RTI)

- Clock monitor, supervising the correct function of the oscillator (CM)

- Computer operating properly (COP) watchdog

- Configurable as window COP for enhanced failure detection

- Can be initialized out of reset using option bits located in flash memory

- System reset generation

- Autonomous periodic interrupt (API) (combination with cyclic, watchdog)

- Low Power Operation

- RUN mode is the main full performance operating mode with the entire device clocked.

- WAIT mode when the internal CPU clock is switched off, so the CPU does not execute instructions.

- Pseudo STOP system clocks are stopped but the oscillator the RTI, the COP, and API modules can be enabled

- STOP the oscillator is stopped in this mode, all clocks are switched off and all counters and dividers remain frozen, with the exception of the COP and API which can optionally run from ACLK.

# 1.4.3.1 Internal Phase-Locked Loop (IPLL)

• Phase-locked-loop clock frequency multiplier

# 1.7.2.24 BDC and Debug Signals

## 1.7.2.24.1 BKGD — Background Debug signal

The BKGD signal is used as a pseudo-open-drain signal for the background debug communication. The BKGD signal has an internal pull-up device.

## 1.7.2.24.2 DBGEEV — External Event Input

This signal is the DBG external event input. It is input only. Within the DBG module, it allows an external event to force a state sequencer transition. A falling edge at the external event signal constitutes an event. Rising edges have no effect. The maximum frequency of events is half the internal core bus frequency.

# 1.7.2.25 CAN0 Signals

### 1.7.2.25.1 RXCAN0 Signal

This signal is associated with the receive functionality of the scalable controller area network controller (MSCAN0).

### 1.7.2.25.2 TXCAN0 Signal

This signal is associated with the transmit functionality of the scalable controller area network controller (MSCAN0).

## 1.7.2.26 LIN Physical Layer Signals

### 1.7.2.26.1 LIN

This pad is connected to the single-wire LIN data bus.

### 1.7.2.26.2 LPTXD

This is the LIN physical layer transmitter input signal.

### 1.7.2.26.3 LPRXD

This is the LIN physical layer receiver output signal.

### 1.7.2.26.4 LPDR1

This is the LIN LP0DR1 register bit, visible at the designated pin for debug purposes.

## 1.7.2.27 BCTL

BCTL is the ballast connection for the on chip voltage regulator. It provides the base current of an external PNP transistor of the VDDX and VDDA supplies.

#### Port Integration Module (S12ZVLPIMV2)

| Port | Pin                  | Pin Function<br>& Priority | I/O                                                                                                                                     | Description                                              | Routing<br>Register Bit | Pin Function<br>after Reset |

|------|----------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------|-----------------------------|

| S    | PS3                  | ECLK                       | 0                                                                                                                                       | Free-running clock                                       | —                       | GPIO                        |

|      |                      | (IOC0_5)                   | I/O                                                                                                                                     | TIM0 channel 5                                           | T0C5RR                  |                             |

|      |                      | SS0                        | I/O                                                                                                                                     | SPI0 slave select                                        | —                       |                             |

|      |                      | PTS[3]/<br>KWS[3]          | I/O                                                                                                                                     | General-purpose; with interrupt and key-wakeup           | —                       |                             |

|      | PS2                  | DBGEEV                     | I                                                                                                                                       | DBG external event                                       | —                       |                             |

|      |                      | TXCAN0                     | 0                                                                                                                                       | MSCAN0 transmit                                          | CAN0RR                  |                             |

|      |                      | (IOC0_4)                   | I/O                                                                                                                                     | TIM0 channel 4                                           | T0C4RR                  |                             |

|      |                      | SCK0                       | I/O                                                                                                                                     | SPI0 serial clock                                        | —                       |                             |

|      |                      | PTS[2]/<br>KWS[2]          | I/O                                                                                                                                     | General-purpose; with interrupt and key-wakeup           | —                       |                             |

|      | PS1                  | (IOC0_3 <sup>2</sup> )     | I/O                                                                                                                                     | TIM0 channel 3                                           | T0C3RR, T0IC3RR1-0      |                             |

|      |                      | (TXD0)/<br>(LPDC0)         | 0                                                                                                                                       | SCI0 transmit/<br>LPTXD0 direct control by LP0DR[LP0DR1] | S0L0RR2-0               |                             |

|      |                      | (PWM6)                     | 0                                                                                                                                       | PWM option 6                                             | PWM6RR                  |                             |

|      |                      | MOSI0                      | MOSI0         I/O         SPI0 master out/slave in           PTS[1]/         I/O         General-purpose; with interrupt and key-wakeup |                                                          | —                       |                             |

|      |                      |                            |                                                                                                                                         |                                                          | _                       |                             |

|      | PS0                  | RXCAN0                     | Ι                                                                                                                                       | MSCAN0 receive                                           | CAN0RR                  |                             |

|      |                      | (IOC0_2)                   | I/O                                                                                                                                     | TIM0 channel 2                                           | T0C2RR                  |                             |

|      | (RXD0) I<br>(PWM4) O |                            | I                                                                                                                                       | SCI0 receive                                             | S0L0RR2-0               |                             |

|      |                      |                            | 0                                                                                                                                       | PWM option 4                                             | PWM4RR                  |                             |

|      |                      | MISO0                      | I/O                                                                                                                                     | SPI0 master in/slave out                                 | —                       |                             |

|      |                      | PTS[0]/<br>KWS[0]          | I/O                                                                                                                                     | General-purpose; with interrupt and key-wakeup           | _                       |                             |

| Global<br>Address | Register<br>Name |        | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

|-------------------|------------------|--------|-------|---|---|---|---|---|---|-------|

| 0x033F            | Reserved         | R<br>W | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0     |

|                   |                  | vv     |       |   |   |   |   |   |   |       |

| 0x0340–<br>0x037F | Reserved         | R      | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0     |

|                   | Reserved         | W      |       |   |   |   |   |   |   |       |

## 2.3.2 PIM Registers 0x0200-0x020F

This section details the specific purposes of register implemented in address range 0x0200-0x020F. These registers serve for specific PIM related functions not part of the generic port registers.

- If not stated differently, writing to reserved bits has no effect and read returns zero.

- All register read accesses are synchronous to internal clocks.

- Register bits can be written at any time if not stated differently.

## 2.3.2.1 Module Routing Register 0 (MODRR0)

Address 0x0200

Access: User read/write<sup>1</sup>

|       | 7 | 6 | 5      | 4      | 3      | 2        | 1             | 0         |

|-------|---|---|--------|--------|--------|----------|---------------|-----------|

| R     | 0 | 0 | CAN0RR | IIC0RR | SCI1RR |          | S0L0RR2-0     |           |

| W     |   |   | CANUKK | IICURK | SCHRR  |          | SULUKKZ-U     |           |

|       |   | _ | TXCAN0 | SDA0   | TXD1   | SCI0-LIN | IPHY0 (see Fi | oure 2-2) |

|       |   |   | RXCAN0 | SCL0   | RXD1   |          |               | galo 2 2) |

| Reset | 0 | 0 | 0      | 0      | 0      | 0        | 0             | 0         |

#### Figure 2-1. Module Routing Register 0 (MODRR0)

<sup>1</sup> Read: Anytime

Write: Once in normal, anytime in special mode

| Field       | Description                                                                                                |

|-------------|------------------------------------------------------------------------------------------------------------|

| 5<br>CAN0RR | Module Routing Register — CAN0 routing<br>1 RXCAN0 on PJ0; TXCAN0 on PJ1<br>0 RXCAN0 on PS0; TXCAN0 on PS2 |

| 4<br>IIC0RR | Module Routing Register — IIC0 routing<br>1 SDA0 on PT0; SCL0 on PT1<br>0 SDA0 on PJ0; SCL0 on PJ1         |

#### Background Debug Controller (S12ZBDCV2)

The hardware forces low-order address bits to zero longword accesses to ensure these accesses are on 0-modulo-size alignments. Byte alignment details are described in Section 5.4.5.2, "BDC Access Of Device Memory Mapped Resources".

# 5.4.4.17 WRITE\_Rn

| Write | e general-pur             | pose CPU reg     | Α                | ctive Backgro    | ound             |                  |

|-------|---------------------------|------------------|------------------|------------------|------------------|------------------|

|       | 0x40+CRN                  | Data [31–24]     | Data [23–16]     | Data [15–8]      | Data [7–0]       |                  |

|       | host $\rightarrow$ target | host →<br>target | host →<br>target | host →<br>target | host →<br>target | D<br>A<br>C<br>K |

If the device is in active BDM, this command writes the 32-bit operand to the selected CPU general-purpose register. See Section 5.4.5.1, "BDC Access Of CPU Registers for the CRN details. Accesses to CPU registers are always 32-bits wide, regardless of implemented register width. If enabled an ACK pulse is generated after the internal write access has been completed or aborted.

If the device is not in active BDM, this command is rejected as an illegal operation, the ILLCMD bit is set and no operation is performed.

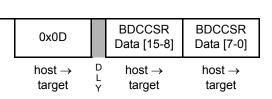

# 5.4.4.18 WRITE\_BDCCSR

Write BDCCSR

16-bit write to the BDCCSR register. No ACK pulse is generated. Writing to this register can be used to configure control bits or clear flag bits. Refer to the register bit descriptions.

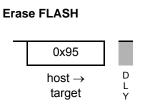

# 5.4.4.19 ERASE\_FLASH

Mass erase the internal flash. This command can always be issued. On receiving this command twice in succession, the BDC sets the ERASE bit in BDCCSR and requests a flash mass erase. Any other BDC command following a single ERASE\_FLASH initializes the sequence, such that thereafter the ERASE\_FLASH must be applied twice in succession to request a mass erase. If 512 BDCSI clock cycles

**Always Available**

**Always Available**

#### NOTE

Register Address = Module Base Address + Address Offset, where the Module Base Address is defined at the MCU level and the Address Offset is defined at the module level.

| Address Offset<br>Register Name |   | Bit 7                                   | 6 | 5 | 4     | 3       | 2       | 1     | Bit 0  |  |  |

|---------------------------------|---|-----------------------------------------|---|---|-------|---------|---------|-------|--------|--|--|

| 0x0000                          | R | 0                                       | 0 | 0 | 0     | 0       | 0       | 0     | RDY    |  |  |

| ECCSTAT                         | W |                                         |   |   |       |         |         |       |        |  |  |

| 0x0001                          | R | 0                                       | 0 | 0 | 0     | 0       | 0       | 0     | SBEEIE |  |  |

| ECCIE                           | W |                                         |   |   |       |         |         |       | SDEELE |  |  |

| 0x0002                          | R | 0                                       | 0 | 0 | 0     | 0       | 0       | 0     |        |  |  |

| ECCIF                           | W |                                         |   |   |       |         |         |       | SBEEIF |  |  |

| 0x0003 - 0x0006                 | R | 0                                       | 0 | 0 | 0     | 0       | 0       | 0     | 0      |  |  |

| Reserved                        | W |                                         |   |   |       |         |         |       |        |  |  |

| 0x0007                          | R |                                         |   |   | וסדסס | [22:46] |         |       |        |  |  |

| ECCDPTRH                        | W |                                         |   |   | DPIR  | [23:16] |         |       |        |  |  |

| 0x0008                          | R |                                         |   |   |       |         |         |       |        |  |  |

| ECCDPTRM                        | W | DPTR[15:8]                              |   |   |       |         |         |       |        |  |  |

| 0x0009                          | R |                                         | 0 |   |       |         |         |       |        |  |  |

| ECCDPTRL                        | W | DPTR[7:1]                               |   |   |       |         |         |       |        |  |  |

| 0x000A - 0x000B                 | R | 0                                       | 0 | 0 | 0     | 0       | 0       | 0     | 0      |  |  |

| Reserved                        | W |                                         |   |   |       |         |         |       |        |  |  |

| 0x000C                          | R |                                         |   |   | DDATA | A[15·9] |         |       |        |  |  |

| ECCDDH                          | W |                                         |   |   | DDAI  | 4[15.6] |         |       |        |  |  |

| 0x000D                          | R |                                         |   |   | DDAT  | ۰       |         |       |        |  |  |

| ECCDDL                          | W |                                         |   |   | DDAI  | A[7.0]  |         |       |        |  |  |

| 0x000E                          | R | 0                                       | 0 |   |       | DEC     | ວເຮົາດາ |       |        |  |  |

| ECCDE                           | W |                                         |   |   |       | DEC     | 5[5.0]  |       |        |  |  |

| 0x000F                          | R | ECCDRR                                  | 0 | 0 | 0     | 0       | 0       | ECCDW | ECCDR  |  |  |

| ECCDCMD                         | W | ECODAR                                  |   |   |       |         |         | ECCDW | ECCDR  |  |  |

|                                 |   | = Unimplemented, Reserved, Read as zero |   |   |       |         |         |       |        |  |  |

Figure 8-1. SRAM\_ECC Register Summary

MC912ZVL Family Reference Manual, Rev. 2.41

ECC Generation Module (SRAM\_ECCV2)

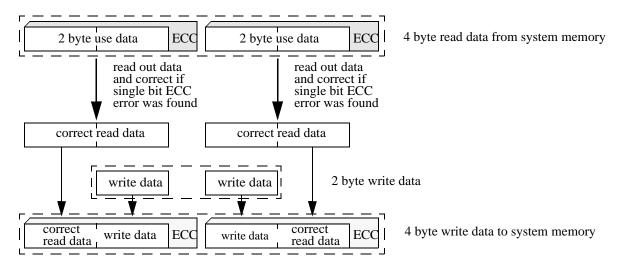

Figure 8-9. 2 byte non-aligned write access

# 8.3.3 Memory Read Access

During each memory read access an ECC check is performed. If the logic detects a single bit ECC error, then the module corrects the data, so that the access initiator module receives correct data. In parallel, the logic writes the corrected data back to the memory, so that this read access repairs the single bit ECC error. This automatic ECC read repair function is disabled by setting the ECCDRR bit.

If a single bit ECC error was detected, then the SBEEIF flag is set.

If the logic detects a double bit ECC error, then the data word is flagged as invalid, so that the access initiator module can ignore the data.

# 8.3.4 Memory Initialization

To avoid spurious ECC error reporting, memory operations that allow a read before a first write (like the read-modify-write operation of the non-aligned access) require that the memory contains valid ECC values before the first read-modify-write access is performed. The ECC module provides logic to initialize the complete memory content with zero during the power up phase. During the initialization process the access to the SRAM is disabled and the RDY status bit is cleared. If the initialization process is done, SRAM access is possible and the RDY status bit is set.

# 8.3.5 Interrupt Handling

This section describes the interrupts generated by the SRAM\_ECC module and their individual sources. Vector addresses and interrupt priority are defined at the MCU level.

| APICLK | APIR[15:0] | Selected Period           |

|--------|------------|---------------------------|

| 0      | 0000       | 0.2 ms <sup>1</sup>       |

| 0      | 0001       | 0.4 ms <sup>1</sup>       |

| 0      | 0002       | 0.6 ms <sup>1</sup>       |

| 0      | 0003       | 0.8 ms <sup>1</sup>       |

| 0      | 0004       | 1.0 ms <sup>1</sup>       |

| 0      | 0005       | 1.2 ms <sup>1</sup>       |

| 0      |            |                           |

| 0      | FFFD       | 13106.8 ms <sup>1</sup>   |

| 0      | FFFE       | 13107.0 ms <sup>1</sup>   |

| 0      | FFFF       | 13107.2 ms <sup>1</sup>   |

| 1      | 0000       | 2 * Bus Clock period      |

| 1      | 0001       | 4 * Bus Clock period      |

| 1      | 0002       | 6 * Bus Clock period      |

| 1      | 0003       | 8 * Bus Clock period      |

| 1      | 0004       | 10 * Bus Clock period     |

| 1      | 0005       | 12 * Bus Clock period     |

| 1      |            |                           |

| 1      | FFFD       | 131068 * Bus Clock period |

| 1      | FFFE       | 131070 * Bus Clock period |

| 1      | FFFF       | 131072 * Bus Clock period |

Table 9-23. Selectable Autonomous Periodical Interrupt Periods

<sup>1</sup> When  $f_{ACLK}$  is trimmed to 20KHz.

| CH_SEL[5] | CH_SEL[4] | CH_SEL[3] | CH_SEL[2] | CH_SEL[1] | CH_SEL[0] | Analog Input Channel                                                                             |

|-----------|-----------|-----------|-----------|-----------|-----------|--------------------------------------------------------------------------------------------------|

| 0         | 0         | 0         | 0         | 0         | 0         | VRL_0/1 (V1, V2, see Table 10-2)<br>VRL_0 (V3, see Table 10-2)                                   |

| 0         | 0         | 0         | 0         | 0         | 1         | VRH_0/1 (V1, V2, see Table 10-2)<br>VRH_0/1/2 (V3, see Table 10-2)                               |

| 0         | 0         | 0         | 0         | 1         | 0         | (VRH_0/1 + VRL_0/1) / 2 (V1, V2, see Table 10-2)<br>(VRH_0/1/2 + VRL_0) / 2 (V3, see Table 10-2) |

| 0         | 0         | 0         | 0         | 1         | 1         | Reserved                                                                                         |

| 0         | 0         | 0         | 1         | 0         | 0         | Reserved                                                                                         |

| 0         | 0         | 0         | 1         | 0         | 1         | Reserved                                                                                         |

| 0         | 0         | 0         | 1         | 1         | 0         | Reserved                                                                                         |

| 0         | 0         | 0         | 1         | 1         | 1         | Reserved                                                                                         |

| 0         | 0         | 1         | 0         | 0         | 0         | Internal_0<br>(ADC temperature sense)                                                            |

| 0         | 0         | 1         | 0         | 0         | 1         | Internal_1                                                                                       |

| 0         | 0         | 1         | 0         | 1         | 0         | Internal_2                                                                                       |

| 0         | 0         | 1         | 0         | 1         | 1         | Internal_3                                                                                       |

| 0         | 0         | 1         | 1         | 0         | 0         | Internal_4                                                                                       |

| 0         | 0         | 1         | 1         | 0         | 1         | Internal_5                                                                                       |

| 0         | 0         | 1         | 1         | 1         | 0         | Internal_6                                                                                       |

| 0         | 0         | 1         | 1         | 1         | 1         | Internal_7                                                                                       |

| 0         | 1         | 0         | 0         | 0         | 0         | ANO                                                                                              |

| 0         | 1         | 0         | 0         | 0         | 1         | AN1                                                                                              |

| 0         | 1         | 0         | 0         | 1         | 0         | AN2                                                                                              |

| 0         | 1         | 0         | 0         | 1         | 1         | AN3                                                                                              |

| 0         | 1         | 0         | 1         | 0         | 0         | AN4                                                                                              |

| 0         | 1         | x         | x         | x         | x         | ANx                                                                                              |

| 1         | x         | x         | x         | x         | x         | Reserved                                                                                         |

Table 10-24. Analog Input Channel Select

### NOTE

ANx in Table 10-24 is the maximum number of implemented analog input channels on the device. Please refer to the device overview of the reference manual for details regarding number of analog input channels.

MC912ZVL Family Reference Manual, Rev. 2.41

Scalable Controller Area Network (S12MSCANV2)

<sup>1</sup> Read: Anytime

Write: Anytime when not in initialization mode, except RSTAT[1:0] and TSTAT[1:0] flags which are read-only; write of 1 clears flag; write of 0 is ignored

### NOTE

The CANRFLG register is held in the reset state<sup>1</sup> when the initialization mode is active (INITRQ = 1 and INITAK = 1). This register is writable again as soon as the initialization mode is exited (INITRQ = 0 and INITAK = 0).

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>WUPIF        | <ul> <li>Wake-Up Interrupt Flag — If the MSCAN detects CAN bus activity while in sleep mode (see Section 13.4.5.5, "MSCAN Sleep Mode,") and WUPE = 1 in CANTCTL0 (see Section 13.3.2.1, "MSCAN Control Register 0 (CANCTL0)"), the module will set WUPIF. If not masked, a wake-up interrupt is pending while this flag is set.</li> <li>No wake-up activity observed while in sleep mode</li> <li>MSCAN detected activity on the CAN bus and requested wake-up</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6<br>CSCIF        | <ul> <li>CAN Status Change Interrupt Flag — This flag is set when the MSCAN changes its current CAN bus status due to the actual value of the transmit error counter (TEC) and the receive error counter (REC). An additional 4-bit (RSTAT[1:0], TSTAT[1:0]) status register, which is split into separate sections for TEC/REC, informs the system on the actual CAN bus status (see Section 13.3.2.6, "MSCAN Receiver Interrupt Enable Register (CANRIER)"). If not masked, an error interrupt is pending while this flag is set. CSCIF provides a blocking interrupt. That guarantees that the receiver/transmitter status bits (RSTAT/TSTAT) are only updated when no CAN status change interrupt is pending. If the TECs/RECs change their current value after the CSCIF is asserted, which would cause an additional state change in the RSTAT/TSTAT bits, these bits keep their status until the current CSCIF interrupt is cleared again.</li> <li>0 No change in CAN bus status occurred since last interrupt</li> <li>1 MSCAN changed current CAN bus status</li> </ul> |

| 5-4<br>RSTAT[1:0] | Receiver Status Bits — The values of the error counters control the actual CAN bus status of the MSCAN. As<br>soon as the status change interrupt flag (CSCIF) is set, these bits indicate the appropriate receiver related CAN<br>bus status of the MSCAN. The coding for the bits RSTAT1, RSTAT0 is:00 RxOK: $0 \le $ receive error counter < 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3-2<br>TSTAT[1:0] | Transmitter Status Bits — The values of the error counters control the actual CAN bus status of the MSCAN.As soon as the status change interrupt flag (CSCIF) is set, these bits indicate the appropriate transmitter relatedCAN bus status of the MSCAN. The coding for the bits TSTAT1, TSTAT0 is:00 TxOK: $0 \le$ transmit error counter < 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

1. The RSTAT[1:0], TSTAT[1:0] bits are not affected by initialization mode.

Serial Communication Interface (S12SCIV6)

# 18.4.5 Transmitter

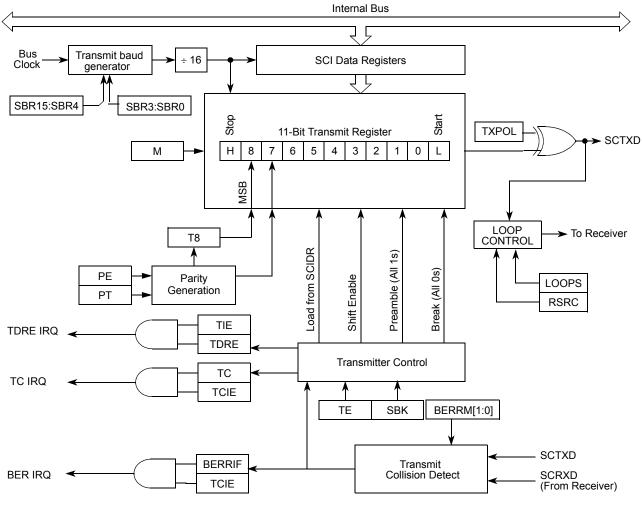

Figure 18-16. Transmitter Block Diagram

## 18.4.5.1 Transmitter Character Length

The SCI transmitter can accommodate either 8-bit or 9-bit data characters. The state of the M bit in SCI control register 1 (SCICR1) determines the length of data characters. When transmitting 9-bit data, bit T8 in SCI data register high (SCIDRH) is the ninth bit (bit 8).

## 18.4.5.2 Character Transmission

To transmit data, the MCU writes the data bits to the SCI data registers (SCIDRH/SCIDRL), which in turn are transferred to the transmitter shift register. The transmit shift register then shifts a frame out through the TXD pin, after it has prefaced them with a start bit and appended them with a stop bit. The SCI data registers (SCIDRH and SCIDRL) are the write-only buffers between the internal data bus and the transmit shift register.

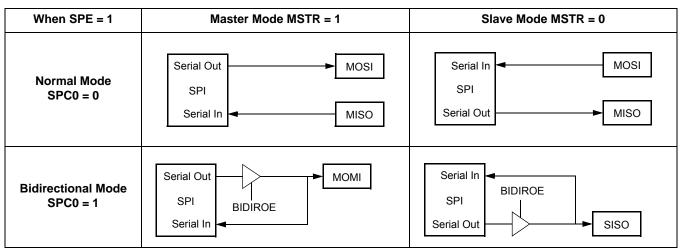

Table 19-11. Normal Mode and Bidirectional Mode

The direction of each serial I/O pin depends on the BIDIROE bit. If the pin is configured as an output, serial data from the shift register is driven out on the pin. The same pin is also the serial input to the shift register.

- The SCK is output for the master mode and input for the slave mode.

- The  $\overline{SS}$  is the input or output for the master mode, and it is always the input for the slave mode.

- The bidirectional mode does not affect SCK and  $\overline{SS}$  functions.

### NOTE

In bidirectional master mode, with mode fault enabled, both data pins MISO and MOSI can be occupied by the SPI, though MOSI is normally used for transmissions in bidirectional mode and MISO is not used by the SPI. If a mode fault occurs, the SPI is automatically switched to slave mode. In this case MISO becomes occupied by the SPI and MOSI is not used. This must be considered, if the MISO pin is used for another purpose.

# 19.4.6 Error Conditions

The SPI has one error condition:

• Mode fault error

# 19.4.6.1 Mode Fault Error

If the  $\overline{SS}$  input becomes low while the SPI is configured as a master, it indicates a system error where more than one master may be trying to drive the MOSI and SCK lines simultaneously. This condition is not permitted in normal operation, the MODF bit in the SPI status register is set automatically, provided the MODFEN bit is set.

In the special case where the SPI is in master mode and MODFEN bit is cleared, the  $\overline{SS}$  pin is not used by the SPI. In this special case, the mode fault error function is inhibited and MODF remains cleared. In case

| FCCOB2 | Level Description                |

|--------|----------------------------------|

| 0x0000 | Return to Normal Level           |

| 0x0001 | User Margin-1 Level <sup>1</sup> |

| 0x0002 | User Margin-0 Level <sup>2</sup> |

Table 22-56. Valid Set User Margin Level Settings

<sup>1</sup> Read margin to the erased state

<sup>2</sup> Read margin to the programmed state

#### Table 22-57. Set User Margin Level Command Error Handling

| Register | Error Bit | Error Condition                                                     |

|----------|-----------|---------------------------------------------------------------------|

|          |           | Set if CCOBIX[2:0] != 010 at command launch                         |

|          | ACCERR    | Set if command not available in current mode (see Table 22-28)      |

|          | ACCERK    | Set if an invalid global address [23:0] is supplied see Table 22-2) |

| FSTAT    |           | Set if an invalid margin level setting is supplied                  |

|          | FPVIOL    | None                                                                |

|          | MGSTAT1   | None                                                                |

|          | MGSTAT0   | None                                                                |

### NOTE

User margin levels can be used to check that Flash memory contents have adequate margin for normal level read operations. If unexpected results are encountered when checking Flash memory contents at user margin levels, a potential loss of information has been detected.

## 22.4.7.13 Set Field Margin Level Command

The Set Field Margin Level command, valid in special modes only, causes the Memory Controller to set the margin level specified for future read operations of the P-Flash or EEPROM block.

| Register | FC                    | COB Parameters                                    |  |  |  |

|----------|-----------------------|---------------------------------------------------|--|--|--|

| FCCOB0   | 0x0E                  | Global address [23:16] to identify Flash<br>block |  |  |  |

| FCCOB1   | Global address        | [15:0] to identify Flash block                    |  |  |  |

| FCCOB2   | Margin level setting. |                                                   |  |  |  |

Table 22-58. Set Field Margin Level Command FCCOB Requirements

Upon clearing CCIF to launch the Set Field Margin Level command, the Memory Controller will set the field margin level for the targeted block and then set the CCIF flag.

| Num | Rating                                                                                                 | Symbol                     | Min | Тур  | Max | Unit |

|-----|--------------------------------------------------------------------------------------------------------|----------------------------|-----|------|-----|------|

|     | 48LQFF                                                                                                 | 5                          |     |      |     |      |

| 1   | Thermal resistance 48LQFP, single sided PCB <sup>1</sup><br>Natural Convection                         | $\theta_{JA}$              | _   | 80   | _   | °C/W |

| 2   | Thermal resistance 48LQFP, double sided PCB with 2 internal planes <sup>2</sup> . Natural Convection.  | $\theta_{JA}$              | _   | 56   | _   | °C/W |

| 3   | Thermal resistance 48LQFP, single sided PCB <sup>1</sup><br>(@200 ft/min)                              | $\theta_{JA}$              | _   | 67   | _   | °C/W |

| 4   | Thermal resistance 48LQFP, double sided PCB with 2 internal planes <sup>2</sup> (@200 ft/min).         | $\theta_{JA}$              | _   | 50   | _   | °C/W |

| 5   | Junction to Board 48LQFP <sup>3</sup>                                                                  | $\theta_{JB}$              | _   | 34   | —   | °C/W |

| 6   | Junction to Case Top 48LQFP <sup>4</sup>                                                               | $\theta_{\text{JCtop}}$    | _   | 24   | —   | °C/W |

| 7   | Junction to Package Top 48LQFP <sup>5</sup>                                                            | $\Psi_{JT}$                | —   | 6    | —   | °C/W |

|     | 32LQFF                                                                                                 | 2                          |     |      |     | •    |

| 8   | Thermal resistance 32LQFP, single sided PCB <sup>1</sup> Natural Convection                            | $\theta_{JA}$              | _   | 84   | _   | °C/W |

| 9   | Thermal resistance 32LQFP, double sided PCB with 2 internal planes <sup>2</sup> . Natural Convection   | $\theta_{JA}$              | _   | 56   | _   | °C/W |

| 10  | Thermal resistance 32LQFP, single sided PCB <sup>1</sup><br>(@200 ft/min)                              | $\theta_{JA}$              | _   | 71   | _   | °C/W |

| 11  | Thermal resistance 32LQFP, double sided PCB with 2 internal planes <sup>2</sup> (@200 ft/min).         | $\theta_{JA}$              | _   | 49   | _   | °C/W |

| 12  | Junction to Board 32LQFP <sup>3</sup>                                                                  | $\theta_{JB}$              | _   | 32   | —   | °C/W |

| 13  | Junction to Case Top 32LQFP <sup>4</sup>                                                               | $\theta_{\text{JCtop}}$    | _   | 23   | _   | °C/W |

| 14  | Junction to Package Top 32LQFP <sup>5</sup>                                                            | $\Psi_{JT}$                |     | 6    |     | °C/W |

|     | 32QFN-E                                                                                                | P                          |     |      |     |      |

| 15  | Thermal resistance 32QFN-EP, single sided PCB <sup>1</sup><br>Natural Convection                       | $\theta_{JA}$              | _   | 96   | _   | °C/W |

| 16  | Thermal resistance 32QFN-EP, double sided PCB with 2 internal planes <sup>2</sup> . Natural Convection | $\theta_{JA}$              | _   | 33   | _   | °C/W |

| 17  | Thermal resistance 32QFN-EP, single sided PCB <sup>1</sup> (@200 ft/min)                               | $\theta_{JA}$              | _   | 80   | _   | °C/W |

| 18  | Thermal resistance 32QFN-EP, double sided PCB with 2 internal planes <sup>2</sup> (@200 ft/min).       | $\theta_{JA}$              | _   | 28   | _   | °C/W |

| 19  | Junction to Board 32QFN-EP <sup>3</sup>                                                                | $\theta_{JB}$              | _   | 13   | —   | °C/W |

| 20  | Junction to Case Top 32QFN-EP <sup>4</sup>                                                             | $\theta_{\text{JCtop}}$    | _   | 25   | —   | °C/W |

| 21  | Junction to Case Bottom 32QFN-EP <sup>5</sup>                                                          | $\theta_{\text{JCbottom}}$ |     | 2.22 | —   | °C/W |

| 22  | Junction to Package Top 32QFN-EP <sup>5</sup>                                                          | $\Psi_{JT}$                |     | 3    | —   | °C/W |

## Table A-8. Thermal Package Characteristics for ZVL(S)32/16/8<sup>1</sup>

<sup>1</sup> Junction to ambient thermal resistance,  $\theta_{JA}$  was simulated to be equivalent to JEDEC JESD51-2 with the single layer board (JESD51-3) horizontal.

| Num  | Characteristic                                                                                                                                                                                                                                         | Symbol                                 | Min                         | Typical                  | Мах                         | Unit    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-----------------------------|--------------------------|-----------------------------|---------|

| VDDX | =3.3V, VREG5VEN = 1'b0, ZVL(A)128/96/64 only                                                                                                                                                                                                           | <u> </u>                               |                             | <u> </u>                 |                             |         |

| 6a   | Output Voltage $V_{DDX}$ , with external PNP<br>Full Performance Mode $V_{SUP} > 5.5V^1$<br>Full Performance Mode $V_{SUP} > 5.5V^4$<br>Full Performance Mode $3.5V \le V_{SUP} \le 5.5V$<br>Reduced Performance Mode (stopmode)<br>$V_{SUP} > = 3.5V$ | V <sub>DDX</sub>                       | 3.2<br>3.23<br>3.13<br>2.2  | 3.3<br>3.3<br>-<br>3.3   | 3.39<br>3.36<br>3.39<br>3.6 | v       |

| 6b   | Output Voltage $V_{DDX}$ , without PNP<br>Full Performance Mode $V_{SUP} > 5.5V^1$<br>Full Performance Mode $V_{SUP} > 5.5V^4$<br>Full Performance Mode $3.5V \le V_{SUP} \le 5.5V$<br>Reduced Performance Mode (stopmode)<br>$V_{SUP} > = 3.5V$       | V <sub>DDX</sub>                       | 3.18<br>3.21<br>3.13<br>2.2 | 3.28<br>3.28<br>-<br>3.3 | 3.37<br>3.35<br>3.37<br>3.6 | v       |

| 7    | Load Current $V_{DDX}^{2,3}$ without external PNP<br>Full Performance Mode $V_{SUP} > 5.5V$<br>Full Performance Mode $3.5V \le V_{SUP} \le 5.5V$<br>Reduced Performance Mode (stopmode)                                                                | I <sub>DDX</sub>                       | 0<br>0<br>0                 |                          | 70<br>25<br>5               | mA      |

|      |                                                                                                                                                                                                                                                        |                                        |                             |                          |                             |         |

| 8    | Short Circuit $V_{DDX}$ fall back current $V_{DDX} \leq 0.5V$                                                                                                                                                                                          | I <sub>DDX</sub>                       | —                           | 100                      | —                           | mA      |

| 9    | Low Voltage Interrupt Assert Level <sup>5</sup><br>Low Voltage Interrupt Deassert Level                                                                                                                                                                | V <sub>LVIA</sub><br>V <sub>LVID</sub> | 4.04<br>4.19                | 4.23<br>4.38             | 4.40<br>4.49                | V       |

| 10a  | V <sub>DDX</sub> Low Voltage Reset deassert <sup>6</sup>                                                                                                                                                                                               | V <sub>LVRXD</sub>                     | _                           | —                        | 3.13                        | V       |

| 10b  | V <sub>DDX</sub> Low Voltage Reset assert                                                                                                                                                                                                              | V <sub>LVRXA</sub>                     | 2.95                        | 3.02                     |                             | V       |

| 11   | Trimmed ACLK output frequency <sup>7</sup>                                                                                                                                                                                                             | f <sub>ACLK</sub>                      | —                           | 20                       | —                           | KHz     |

| 12   | Trimmed ACLK internal clock $\Delta f / f_{nominal}^{8}$                                                                                                                                                                                               | df <sub>ACLK</sub>                     | - 6%                        | —                        | + 6%                        | —       |

| 13   | The first period after enabling the counter by APIFE might be reduced by API start up delay                                                                                                                                                            | t <sub>sdel</sub>                      | —                           | —                        | 100                         | μS      |

| 14   | Temperature Sensor Slope                                                                                                                                                                                                                               | dV <sub>HT</sub>                       | 5.05                        | 5.25                     | 5.45                        | mV/ºC   |

| 15   | Temperature Sensor Output Voltage (Tj=150°C)                                                                                                                                                                                                           | V <sub>HT</sub>                        | _                           | 2.4                      | —                           | V       |

| 16   | High Temperature Interrupt Assert <sup>9</sup><br>High Temperature Interrupt Deassert                                                                                                                                                                  | T <sub>HTIA</sub><br>T <sub>HTID</sub> | 120<br>110                  | 132<br>122               | 144<br>134                  | °C<br>℃ |

| 17   | Bandgap output voltage                                                                                                                                                                                                                                 | V <sub>BG</sub>                        | 1.14                        | 1.20                     | 1.28                        | V       |

| 18   | $V_{BG}$ voltage variation over input voltage $V_{SUP}$ 3.5V $\leq$ $V_{SUP}$ $\leq$ 18V, $T_{J}$ = 125°C                                                                                                                                              | $\Delta_{VBGV}$                        | -5                          |                          | 5                           | mV      |

#### Table B-1. Voltage Regulator Electrical Characteristics

#### **ADC Specifications**

# Appendix E NVM Electrical Parameters

# E.1 NVM Timing Parameters

The time base for all NVM program or erase operations is derived from the bus clock using the FCLKDIV register. The frequency of this derived clock must be set within the limits specified as  $f_{NVMOP}$ . The NVM module does not have any means to monitor the frequency and will not prevent program or erase operation at frequencies above or below the specified minimum. When attempting to program or erase the NVM module at a lower frequency, a full program or erase transition is not assured.

The device bus frequency  $f_{WSTAT}$ , below which the flash wait states can be disabled, is specified in the device operating conditions Table A-6.

The following sections provide equations which can be used to determine the time required to execute specific flash commands. All timing parameters are a function of the bus clock frequency,  $f_{NVMBUS}$ . All program and erase times are also a function of the NVM operating frequency,  $f_{NVMOP}$  A summary of key timing parameters can be found in Table E-1 and Table E-2.

| Num | Command                                  | f <sub>NVMOP</sub><br>cycle | f <sub>NVMBUS</sub> | Symbol                | Min <sup>1</sup> | Typ <sup>2</sup> | Max <sup>3</sup> | Lfmax <sup>4</sup> | Unit |  |  |  |

|-----|------------------------------------------|-----------------------------|---------------------|-----------------------|------------------|------------------|------------------|--------------------|------|--|--|--|

| 1   | Bus frequency                            | 1                           | _                   | f <sub>NVMBUS</sub>   | 1                | 32               | 32               |                    | MHz  |  |  |  |

| 2   | NVM Operating frequency                  |                             | 1                   | f <sub>NVMOP</sub>    | 0.8              | 1                | 1.05             |                    | MHz  |  |  |  |

| 3   | Erase Verify All Blocks <sup>5,6</sup>   | 0                           | 34528               | t <sub>RD1ALL</sub>   | 1.08             | 1.08             | 2.16             | 69.06              | ms   |  |  |  |

| 4   | Erase Verify Block (Pflash) <sup>5</sup> | 0                           | 33323               | t <sub>RD1BLK_P</sub> | 1.04             | 1.04             | 2.08             | 66.65              | ms   |  |  |  |

| 5   | Erase Verify Block (EEPROM) <sup>6</sup> | 0                           | 1591                | t <sub>RD1BLK_D</sub> | 0.05             | 0.05             | 0.10             | 3.18               | ms   |  |  |  |

| 6   | Erase Verify P-Flash Section             | 0                           | 508                 | t <sub>RD1SEC</sub>   | 0.02             | 0.02             | 0.03             | 1.02               | ms   |  |  |  |

| 7   | Read Once                                | 0                           | 481                 | t <sub>RDONCE</sub>   | 15.03            | 15.03            | 15.03            | 481.00             | us   |  |  |  |

| 8   | Program P-Flash (4 Word)                 | 164                         | 3133                | t <sub>PGM_4</sub>    | 0.25             | 0.26             | 0.56             | 12.74              | ms   |  |  |  |

| 9   | Program Once                             | 164                         | 3107                | t <sub>PGMONCE</sub>  | 0.25             | 0.26             | 0.26             | 3.31               | ms   |  |  |  |

| 10  | Erase All Blocks <sup>5,6</sup>          | 100066                      | 34991               | t <sub>ERSALL</sub>   | 96.39            | 101.16           | 102.25           | 195.06             | ms   |  |  |  |

| 11  | Erase Flash Block (Pflash) <sup>5</sup>  | 100060                      | 33692               | t <sub>ERSBLK_P</sub> | 96.35            | 101.11           | 102.17           | 192.46             | ms   |  |  |  |

| 12  | Erase Flash Block (EEPROM) <sup>6</sup>  | 100060                      | 1930                | t <sub>ERSBLK_D</sub> | 95.36            | 100.12           | 100.18           | 128.94             | ms   |  |  |  |

| 13  | Erase P-Flash Sector                     | 20015                       | 924                 | t <sub>ERSPG</sub>    | 19.09            | 20.04            | 20.07            | 26.87              | ms   |  |  |  |

| 14  | Unsecure Flash                           | 100066                      | 35069               | t <sub>UNSECU</sub>   | 96.40            | 101.16           | 102.26           | 195.22             | ms   |  |  |  |

| 15  | Verify Backdoor Access Key               | 0                           | 493                 | t <sub>VFYKEY</sub>   | 15.41            | 15.41            | 15.41            | 493.00             | us   |  |  |  |

| 16  | Set User Margin Level                    | 0                           | 436                 | t <sub>MLOADU</sub>   | 13.63            | 13.63            | 13.63            | 436.00             | us   |  |  |  |

| 17  | Set Factory Margin Level                 | 0                           | 445                 | t <sub>MLOADF</sub>   | 13.91            | 13.91            | 13.91            | 445.00             | us   |  |  |  |

| 18  | Erase Verify EEPROM Section              | 0                           | 583                 | t <sub>DRD1SEC</sub>  | 0.02             | 0.02             | 0.04             | 1.17               | ms   |  |  |  |

| 19  | Program EEPROM (1 Word)                  | 68                          | 1678                | t <sub>DPGM_1</sub>   | 0.12             | 0.12             | 0.28             | 6.80               | ms   |  |  |  |

| 20  | Program EEPROM (2 Word)                  | 136                         | 2702                | t <sub>DPGM_2</sub>   | 0.21             | 0.22             | 0.47             | 10.98              | ms   |  |  |  |

| 21  | Program EEPROM (3 Word)                  | 204                         | 3726                | t <sub>DPGM_3</sub>   | 0.31             | 0.32             | 0.67             | 15.16              | ms   |  |  |  |

| 22  | Program EEPROM (4 Word)                  | 272                         | 4750                | t <sub>DPGM_4</sub>   | 0.41             | 0.42             | 0.87             | 19.34              | ms   |  |  |  |

| 23  | Erase EEPROM Sector                      | 5015                        | 817                 | t <sub>DERSPG</sub>   | 4.80             | 5.04             | 20.49            | 38.96              | ms   |  |  |  |

| 24  | Protection Override                      | 0                           | 475                 | t <sub>PRTOVRD</sub>  | 14.84            | 14.84            | 14.84            | 475.00             | us   |  |  |  |

Table E-2. NVM Timing Characteristics ZVL(A)128/96/64

$^1$  Minimum times are based on maximum  $f_{\rm NVMOP}$  and maximum  $f_{\rm NVMBUS}$

$^2\,$  Typical times are based on typical  $f_{NVMOP}$  and typical  $f_{NVMBUS}$

$^3$  Maximum times are based on typical  $f_{\rm NVMOP}$  and typical  $f_{\rm NVMBUS}$  plus aging

$^4\,$  Lowest-frequency max times are based on minimum  $f_{NVMOP}$  and minimum  $f_{NVMBUS}$  plus aging

<sup>5</sup> Affected by Pflash size

<sup>6</sup> Affected by EEPROM size

# E.2 NVM Reliability Parameters

The reliability of the NVM blocks is guaranteed by stress test during qualification, constant process monitors and burn-in to screen early life failures.

# Appendix J PIM Electrical Specifications

# J.1 High-Voltage Inputs (HVI) Electrical Characteristics

| Num | Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Symbol                                                                                        | Min                                       | Тур                                                      | Max                                                      | Unit                       |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|----------------------------|

| 1   | $\label{eq:started} \begin{array}{l} \text{Digital Input Threshold} \\ \bullet \ \ V_{SUP} > 6.5 \text{V}, \ \ V_{DDX} \text{=}5 \text{V} \text{ selected} \\ \bullet \ \ 5.5 \text{V} \leq \ \ V_{SUP} \leq 6.5 \text{V}, \ \ \ V_{DDX} \text{=}5 \text{V} \text{ selected} \\ \bullet \ \ \ \ \ V_{SUP} > 5.5 \text{V}, \ \ \ \ \ \ \ \ V_{DDX} \text{=}3.3 \text{V} \text{ selected} \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>TH_HVI</sub>                                                                           | 2.8<br>2.0<br>0.8                         | 3.5<br>2.5<br>1.8                                        | 4.5<br>3.8<br>2.7                                        | V<br>V<br>V                |

| 2   | Input Hysteresis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | V <sub>HYS_HVI</sub>                                                                          | _                                         | 250                                                      | _                                                        | mV                         |

| 3   | Pin Input Divider Ratio with external series R <sub>EXT_HVI</sub><br>Ratio = V <sub>HVI</sub> / V <sub>Internal(ADC)</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Ratio <sub>L_HVI</sub><br>Ratio <sub>H_HVI</sub><br>Ratio <sub>12_HVI</sub>                   |                                           | 2<br>6<br>12                                             | _<br>_<br>_                                              |                            |

| 4   | $\begin{array}{l} \mbox{Analog Input Matching} \\ \mbox{Absolute Error on $V_{ADC}$^3$} \\ & \mbox{Compared to $V_{HVI}$ / Ratio_{L_HVI}$} \\ (1V < V_{HVI} < 7V), $V_{DDX}$=5V selected$} \\ (1V < V_{HVI} < 2.8V), $V_{DDX}$=3.3V selected$} \\ & \mbox{Compared to $V_{HVI}$ / Ratio_{H_HVI}$} \\ (3V < V_{HVI} < 21V), $V_{DDX}$=5V selected$} \\ (5V < V_{HVI} < 18V), $V_{DDX}$=5V selected$} \\ (3V < V_{HVI} < 18V), $V_{DDX}$=3.3V selected$} \\ & \mbox{Compared to $V_{HVI}$ / Ratio_{12_HVI}$} \\ (6V < V_{HVI} < 28V), $V_{DDX}$=5V selected$} \\ & \mbox{Compared to $V_{HVI}$ / Ratio_{12_HVI}$} \\ (6V < V_{HVI} < 28V), $V_{DDX}$=5V selected$} \\ & \mbox{Obsched} \\ & \mbox{Direct Mode (PTADIRL=1)$} \\ (0.5V < V_{HVI} < 3.5V), $V_{DDX}$=5V selected$} \\ & \mbox{Osched} \\ & \mbo$ | AIM <sub>L_HVI</sub><br>AIM <sub>H_HVI</sub><br>AIM <sub>12_HVI</sub><br>AIM <sub>D_HVI</sub> | -<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>- | ±2<br>±3<br>±2<br>±2<br>±3<br>±3<br>±3<br>±3<br>±2<br>±2 | ±5<br>±7<br>±5<br>±3<br>±7<br>±7<br>±7<br>±7<br>±5<br>±5 | %<br>%<br>%<br>%<br>%<br>% |

| 5   | High Voltage Input Series Resistor<br><b>Note:</b> Always required externally at HVI pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R <sub>EXT_HVI</sub>                                                                          | -                                         | 10                                                       | _                                                        | kΩ                         |