#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s912zvl64f0mfm |

|----------------------------|------------------------------------------------------------------------|

| Supplier Device Package    | 32-QFN-EP (5x5)                                                        |

| Package / Case             | 32-VFQFN Exposed Pad                                                   |

| Mounting Type              | Surface Mount, Wettable Flank                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Oscillator Type            | Internal                                                               |

| Data Converters            | A/D 6x10b                                                              |

| Voltage - Supply (Vcc/Vdd) | 5.5V ~ 18V                                                             |

| RAM Size                   | 1K x 8                                                                 |

| EEPROM Size                | 512 x 8                                                                |

| Program Memory Type        | FLASH                                                                  |

| Program Memory Size        | 64KB (64K x 8)                                                         |

| Number of I/O              | 19                                                                     |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SCI, SPI, UART/USART           |

| Speed                      | 32MHz                                                                  |

| Core Size                  | 16-Bit                                                                 |

| Core Processor             | S12Z                                                                   |

| Product Status             | Active                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Field | Description                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|       | <b>Port Interrupt Enable</b> — Activate pin interrupt (KWU)<br>This bit enables or disables the edge sensitive pin interrupt on the associated pin. An interrupt can be generated if<br>the pin is operating in input or output mode when in use with the general-purpose or related peripheral function.<br>1 Interrupt is enabled<br>0 Interrupt is disabled (interrupt flag masked) |  |  |  |

#### Table 2-15. Port Interrupt Enable Register Field Descriptions

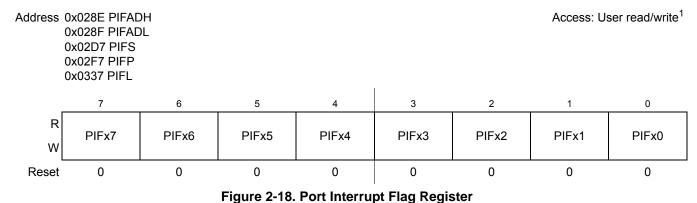

### 2.3.3.7 Port Interrupt Flag Register

Figure 2-16. Port interrupt Flag

<sup>1</sup> Read: Anytime

Write: Anytime, write 1 to clear

### Table 2-16. Port Interrupt Flag Register Field Descriptions

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7-0<br>PIFx7-0 | Port Interrupt Flag — Signal pin event (KWU)<br>This flag asserts after a valid active edge was detected on the related pin (see Section 2.4.4.2, "Pin interrupts and<br>Key-Wakeup (KWU)"). This can be a rising or a falling edge based on the state of the polarity select register. An<br>interrupt will occur if the associated interrupt enable bit is set.<br>Writing a logic "1" to the corresponding bit field clears the flag.<br>1 Active edge on the associated bit has occurred<br>0 No active edge occurred |  |  |  |  |

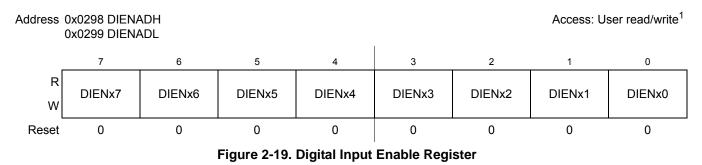

### 2.3.3.8 Digital Input Enable Register

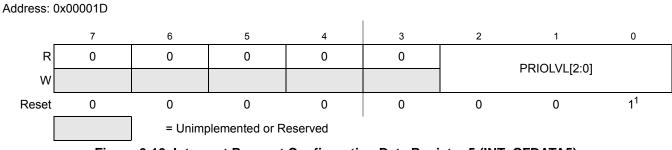

#### Interrupt (S12ZINTV0)

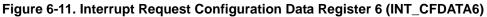

Figure 6-10. Interrupt Request Configuration Data Register 5 (INT\_CFDATA5)

<sup>1</sup> Please refer to the notes following the PRIOLVL[2:0] description below.

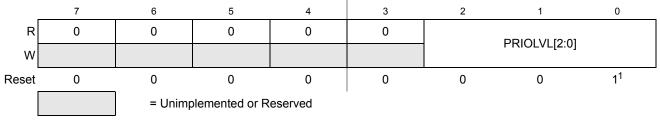

#### Address: 0x00001E

<sup>1</sup> Please refer to the notes following the PRIOLVL[2:0] description below.

#### Address: 0x00001F

### Figure 6-12. Interrupt Request Configuration Data Register 7 (INT\_CFDATA7)

<sup>1</sup> Please refer to the notes following the PRIOLVL[2:0] description below.

### Read: Anytime

Write: Anytime

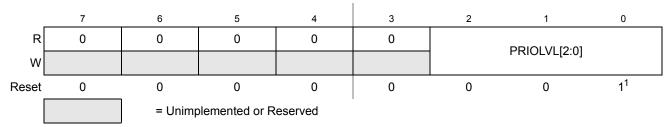

# 8.2.2.4 ECC Debug Pointer Register (ECCDPTRH, ECCDPTRM, ECCDPTRL)

<sup>1</sup> Read: Anytime Write: Anytime

### Table 8-5. ECCDPTR Register Field Descriptions

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DPTR<br>[23:0] | <b>ECC Debug Pointer</b> — This register contains the system memory address which will be used for a debug access. Address bits not relevant for SRAM address space are not writeable, so the software should read back the pointer value to make sure the register contains the intended memory address. It is possible to write an address value to this register which points outside the system memory. There is no additional monitoring of the register content; therefore, the software must make sure that the address value points to the system memory space. |

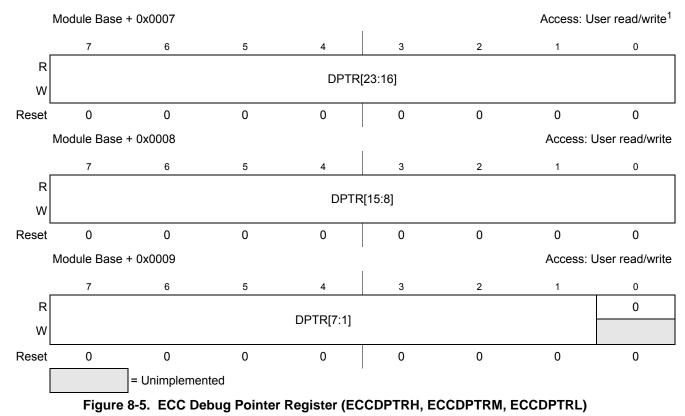

### 9.3.2.21 Reserved Register CPMUTEST3

### NOTE

This reserved register is designed for factory test purposes only, and is not intended for general user access. Writing to this register when in Special Mode can alter the S12CPMU\_UHV's functionality.

### Figure 9-27. Reserved Register (CPMUTEST3)

Read: Anytime

Write: Only in Special Mode

```

/* Procedure proposed by to setup PLL and Oscillator */

/* example for OSC = 4 MHz and Bus Clock = 25MHz, That is VCOCLK = 50MHz */

/* Initialize */

/* PLL Clock = 50 MHz, divide by one */

CPMUPOSTDIV = 0 \times 00;

/* Generally: Whenever changing PLL reference clock (REFCLK) frequency to a higher value */

/* it is recommended to write CPMUSYNR = 0x00 in order to stay within specified */

/* maximum frequency of the MCU */

CPMUSYNR = 0 \times 00;

/* configure PLL reference clock (REFCLK) for usage with Oscillator */

/* OSC=4MHz divide by 4 (3+1) = 1MHz, REFCLK range 1MHz to 2 MHz (REFFRQ[1:0] = 00) */

CPMUREFDV = 0 \times 03;

/* enable external Oscillator, switch PLL reference clock (REFCLK) to OSC */

CPMUOSC = 0x80;

/* multiply REFCLK = 1MHz by 2*(24+1)*1MHz = 50MHz */

/* VCO range 48 to 80 MHz (VCOFRQ[1:0] = 01) */

CPMUSYNR = 0 \times 58;

/* clear all flags, especially LOCKIF and OSCIF */

CPMUIFLG = 0xFF;

/* put your code to loop and wait for the LOCKIF and OSCIF or */

/* poll CPMUIFLG register until both UPOSC and LOCK status are "1" */

/* that is CPMIFLG == 0x1B */

/* in case later in your code you want to disable the Oscillator and use the */

/* 1MHz IRCCLK as PLL reference clock */

/* Generally: Whenever changing PLL reference clock (REFCLK) frequency to a higher value */

/* it is recommended to write CPMUSYNR = 0x00 in order to stay within specified */

/* maximum frequency of the MCU */

CPMUSYNR = 0 \times 00i

/* disable OSC and switch PLL reference clock to IRC */

CPMUOSC = 0 \times 00i

/* multiply REFCLK = 1MHz by 2*(24+1)*1MHz = 50MHz */

/* VCO range 48 to 80 MHz (VCOFRQ[1:0] = 01) */

CPMUSYNR = 0 \times 58;

/* clear all flags, especially LOCKIF and OSCIF */

CPMUIFLG = 0xFF;

/* put your code to loop and wait for the LOCKIF or */

/* poll CPMUIFLG register until both LOCK status is "1" */

/* that is CPMIFLG == 0x18 */

```

### NOTE

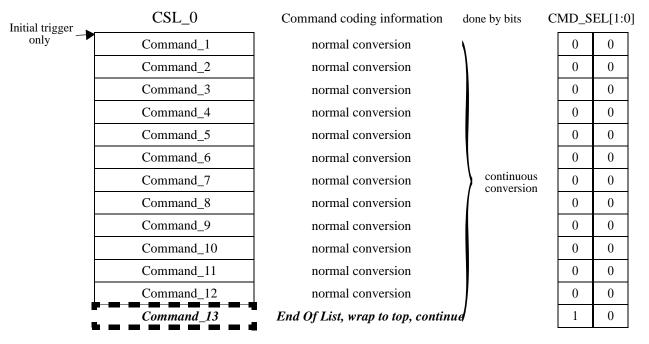

Each conversion flow control bit (SEQA, RSTA, TRIG, LDOK) must be controlled by software or internal interface according to the requirements described in Section 10.6.3.2.4, "The two conversion flow control Mode Configurations and overview summary in Table 10-11.

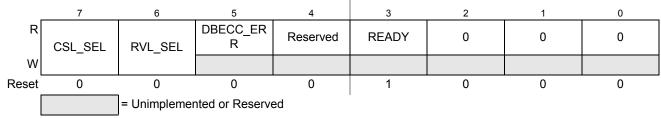

# 10.5.2.3 ADC Status Register (ADCSTS)

It is important to note that if flag DBECC\_ERR is set the ADC ceases operation. In order to make the ADC operational again an ADC Soft-Reset must be issued. An ADC Soft-Reset clears bits CSL\_SEL and RVL\_SEL.

Module Base + 0x0002

Figure 10-6. ADC Status Register (ADCSTS)

Read: Anytime

Write:

- Bits CSL\_SEL and RVL\_SEL anytime if bit ADC\_EN is clear or bit SMOD\_ACC is set

- Bits DBECC\_ERR and READY not writable

### Table 10-6. ADCSTS Field Descriptions

| Field              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7<br>CSL_SEL       | <b>Command Sequence List Select bit</b> — This bit controls and indicates which ADC Command List is active. This bit can only be written if ADC_EN bit is clear. This bit toggles in CSL double buffer mode when no conversion or conversion sequence is ongoing and bit LDOK is set and bit RSTA is set. In CSL single buffer mode this bit is forced to 1'b0 by bit CSL_BMOD.<br>0 ADC Command List 0 is active.<br>1 ADC Command List 1 is active.                                                                                                                                                                                                                        |  |  |  |

| 6<br>RVL_SEL       | <ul> <li>Result Value List Select Bit — This bit controls and indicates which ADC Result List is active. This bit can only be written if bit ADC_EN is clear. After storage of the initial Result Value List this bit toggles in RVL double buffer mode whenever the conversion result of the first conversion of the current CSL is stored or a CSL got aborted. In RVL single buffer mode this bit is forced to 1'b0 by bit RVL_BMOD.</li> <li>Please see also Section 10.3.1.2, "MCU Operating Modes for information regarding Result List usage in case of Stop or Wait Mode.</li> <li>0 ADC Result List 0 is active.</li> <li>1 ADC Result List 1 is active.</li> </ul> |  |  |  |

| 5<br>DBECC_ER<br>R | <ul> <li>Double Bit ECC Error Flag — This flag indicates that a double bit ECC error occurred during conversion command load or result storage and ADC ceases operation.</li> <li>In order to make the ADC operational again an ADC Soft-Reset must be issued.</li> <li>This bit is cleared if bit ADC_EN is clear.</li> <li>0 No double bit ECC error occurred.</li> <li>1 A double bit ECC error occurred.</li> </ul>                                                                                                                                                                                                                                                      |  |  |  |

| 3<br>READY         | <ul> <li>Ready For Restart Event Flag — This flag indicates that ADC is in its idle state and ready for a Restart Event. It can be used to verify after exit from Wait Mode if a Restart Event can be issued and processed immediately without any latency time due to an ongoing Sequence Abort Event after exit from MCU Wait Mode (see also the Note in Section 10.3.1.2, "MCU Operating Modes).</li> <li>0 ADC not in idle state.</li> <li>1 ADC is in idle state.</li> </ul>                                                                                                                                                                                            |  |  |  |

# 10.5.2.18 ADC Command Register 3 (ADCCMD\_3)

Module Base + 0x0017

#### Analog-to-Digital Converter (ADC12B\_LBA)

Figure 10-30. Example CSL for continues conversion

| Field             | Description                                                                                                                                                                                                                                                                                                                |  |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

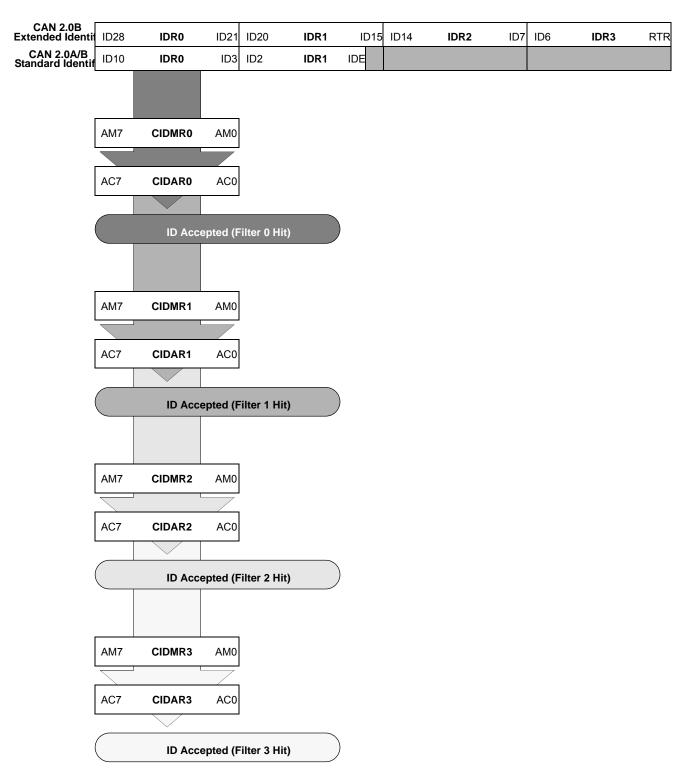

| 5-4<br>IDAM[1:0]  | <b>Identifier Acceptance Mode</b> — The CPU sets these flags to define the identifier acceptance filter organization (see Section 13.4.3, "Identifier Acceptance Filter"). Table 13-19 summarizes the different settings. In filter closed mode, no message is accepted such that the foreground buffer is never reloaded. |  |  |  |

| 2-0<br>IDHIT[2:0] | Identifier Acceptance Hit Indicator — The MSCAN sets these flags to indicate an identifier acceptance hit (see Section 13.4.3, "Identifier Acceptance Filter"). Table 13-20 summarizes the different settings.                                                                                                             |  |  |  |

### Table 13-18. CANIDAC Register Field Descriptions

| IDAM1 | IDAM0 | Identifier Acceptance Mode     |

|-------|-------|--------------------------------|

| 0     | 0     | Two 32-bit acceptance filters  |

| 0     | 1     | Four 16-bit acceptance filters |

| 1     | 0     | Eight 8-bit acceptance filters |

| 1     | 1     | Filter closed                  |

### Table 13-19. Identifier Acceptance Mode Settings

#### Table 13-20. Identifier Acceptance Hit Indication

| IDHIT2 | IDHIT1 | IDHIT0 | Identifier Acceptance Hit |

|--------|--------|--------|---------------------------|

| 0      | 0      | 0      | Filter 0 hit              |

| 0      | 0      | 1      | Filter 1 hit              |

| 0      | 1      | 0      | Filter 2 hit              |

| 0      | 1      | 1      | Filter 3 hit              |

| 1      | 0      | 0      | Filter 4 hit              |

| 1      | 0      | 1      | Filter 5 hit              |

| 1      | 1      | 0      | Filter 6 hit              |

| 1      | 1      | 1      | Filter 7 hit              |

The IDHITx indicators are always related to the message in the foreground buffer (RxFG). When a message gets shifted into the foreground buffer of the receiver FIFO the indicators are updated as well.

### 13.3.2.13 MSCAN Reserved Registers

These registers are reserved for factory testing of the MSCAN module and is not available in normal system operating modes.

#### Scalable Controller Area Network (S12MSCANV2)

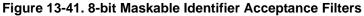

# 16.3.2.11 Main Timer Interrupt Flag 2 (TFLG2)

Module Base + 0x000F

Figure 16-17. Main Timer Interrupt Flag 2 (TFLG2)

TFLG2 indicates when interrupt conditions have occurred. To clear a bit in the flag register, write the bit to one while TEN bit of TSCR1.

Read: Anytime

Write: Used in clearing mechanism (set bits cause corresponding bits to be cleared).

Any access to TCNT will clear TFLG2 register if the TFFCA bit in TSCR register is set.

| Field    | Description                                                                                                                                                                                                     |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TOF | <b>Timer Overflow Flag</b> — Set when 16-bit free-running timer overflows from 0xFFFF to 0x0000. Clearing this bit requires writing a one to bit 7 of TFLG2 register while the TEN bit of TSCR1 is set to one . |

#### Pulse-Width Modulator (S12PWM8B8CV2)

# 18.3.1 Module Memory Map and Register Definition

The memory map for the SCI module is given below in Figure 18-2. The address listed for each register is the address offset. The total address for each register is the sum of the base address for the SCI module and the address offset for each register.

### 18.3.2 Register Descriptions

This section consists of register descriptions in address order. Each description includes a standard register diagram with an associated figure number. Writes to a reserved register locations do not have any effect and reads of these locations return a zero. Details of register bit and field function follow the register diagrams, in bit order.

| Register<br>Name               |        | Bit 7   | 6          | 5             | 4     | 3     | 2      | 1      | Bit 0 |

|--------------------------------|--------|---------|------------|---------------|-------|-------|--------|--------|-------|

| 0x0000<br>SCIBDH <sup>1</sup>  | R<br>W | SBR15   | SBR14      | SBR13         | SBR12 | SBR11 | SBR10  | SBR9   | SBR8  |

| 0x0001<br>SCIBDL <sup>1</sup>  | R<br>W | SBR7    | SBR6       | SBR5          | SBR4  | SBR3  | SBR2   | SBR1   | SBR0  |

| 0x0002<br>SCICR1 <sup>1</sup>  | R<br>W | LOOPS   | SCISWAI    | RSRC          | М     | WAKE  | ILT    | PE     | PT    |

| 0x0000<br>SCIASR1 <sup>2</sup> | R<br>W | RXEDGIF | 0          | 0             | 0     | 0     | BERRV  | BERRIF | BKDIF |

| 0x0001<br>SCIACR1 <sup>2</sup> | R<br>W | RXEDGIE | 0          | 0             | 0     | 0     | 0      | BERRIE | BKDIE |

| 0x0002<br>SCIACR2 <sup>2</sup> | R<br>W | IREN    | TNP1       | TNP0          | 0     | 0     | BERRM1 | BERRM0 | BKDFE |

| 0x0003<br>SCICR2               | R<br>W | TIE     | TCIE       | RIE           | ILIE  | TE    | RE     | RWU    | SBK   |

| 0x0004                         | R      | TDRE    | TC         | RDRF          | IDLE  | OR    | NF     | FE     | PF    |

| SCISR1                         | W      |         |            |               |       |       |        |        |       |

| 0x0005<br>SCISR2               | R<br>W | AMAP    | 0          | 0             | TXPOL | RXPOL | BRK13  | TXDIR  | RAF   |

|                                | [      |         | = Unimplem | ented or Rese | erved |       |        |        |       |

Figure 18-2. SCI Register Summary (Sheet 1 of 2)

Serial Communication Interface (S12SCIV6)

| Table 19-2. SPICR1 | Field Descriptions | (continued) |

|--------------------|--------------------|-------------|

|                    |                    |             |

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3<br>CPOL  | <ul> <li>SPI Clock Polarity Bit — This bit selects an inverted or non-inverted SPI clock. To transmit data between SPI modules, the SPI modules must have identical CPOL values. In master mode, a change of this bit will abort a transmission in progress and force the SPI system into idle state.</li> <li>0 Active-high clocks selected. In idle state SCK is low.</li> <li>1 Active-low clocks selected. In idle state SCK is high.</li> </ul>     |

| 2<br>CPHA  | <ul> <li>SPI Clock Phase Bit — This bit is used to select the SPI clock format. In master mode, a change of this bit will abort a transmission in progress and force the SPI system into idle state.</li> <li>0 Sampling of data occurs at odd edges (1,3,5,) of the SCK clock.</li> <li>1 Sampling of data occurs at even edges (2,4,6,) of the SCK clock.</li> </ul>                                                                                   |

| 1<br>SSOE  | <b>Slave Select Output Enable</b> — The $\overline{SS}$ output feature is enabled only in master mode, if MODFEN is set, by asserting the SSOE as shown in Table 19-3. In master mode, a change of this bit will abort a transmission in progress and force the SPI system into idle state.                                                                                                                                                              |

| 0<br>LSBFE | <ul> <li>LSB-First Enable — This bit does not affect the position of the MSB and LSB in the data register. Reads and writes of the data register always have the MSB in the highest bit position. In master mode, a change of this bit will abort a transmission in progress and force the SPI system into idle state.</li> <li>0 Data is transferred most significant bit first.</li> <li>1 Data is transferred least significant bit first.</li> </ul> |

### Table 19-3. SS Input / Output Selection

|   | MODFEN | SSOE | Master Mode                | Slave Mode |

|---|--------|------|----------------------------|------------|

| Ī | 0      | 0    | SS not used by SPI         | SS input   |

| ſ | 0      | 1    | SS not used by SPI         | SS input   |

| ſ | 1      | 0    | SS input with MODF feature | SS input   |

| Ī | 1      | 1    | SS is slave select output  | SS input   |

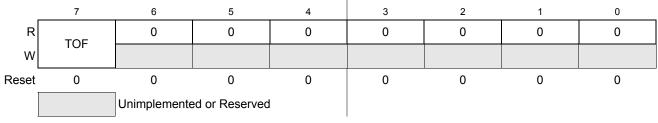

# 19.3.2.2 SPI Control Register 2 (SPICR2)

Module Base +0x0001

Figure 19-4. SPI Control Register 2 (SPICR2)

### Read: Anytime

Write: Anytime; writes to the reserved bits have no effect

# 22.4.7.10 Unsecure Flash Command

The Unsecure Flash command will erase the entire P-Flash and EEPROM memory space and, if the erase is successful, will release security.

| Register | FCCOB Parameters |              |  |  |  |

|----------|------------------|--------------|--|--|--|

| FCCOB0   | 0x0B             | Not required |  |  |  |

Upon clearing CCIF to launch the Unsecure Flash command, the Memory Controller will erase the entire P-Flash and EEPROM memory space and verify that it is erased. If the Memory Controller verifies that the entire Flash memory space was properly erased, security will be released. If the erase verify is not successful, the Unsecure Flash operation sets MGSTAT1 and terminates without changing the security state. During the execution of this command (CCIF=0) the user must not write to any Flash module register. The CCIF flag is set after the Unsecure Flash operation has completed.

| Table 22-52. Unsecure Flash | Command Error Handling |

|-----------------------------|------------------------|

|-----------------------------|------------------------|

| Register | Error Bit | Error Condition                                                                     |  |  |

|----------|-----------|-------------------------------------------------------------------------------------|--|--|

|          | ACCERR    | Set if CCOBIX[2:0] != 000 at command launch                                         |  |  |

|          | ACCERK    | Set if command not available in current mode (see Table 22-28)                      |  |  |

| FSTAT    | FPVIOL    | Set if any area of the P-Flash or EEPROM memory is protected                        |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |  |  |

### 22.4.7.11 Verify Backdoor Access Key Command

The Verify Backdoor Access Key command will only execute if it is enabled by the KEYEN bits in the FSEC register (see Table 22-9). The Verify Backdoor Access Key command releases security if user-supplied keys match those stored in the Flash security bytes of the Flash configuration field (see Table 22-3). The Verify Backdoor Access Key command must not be executed from the Flash block containing the backdoor comparison key to avoid code runaway.

| Table 22-53. Verify Backdoor Access | Key Command FCCOB Requirements |

|-------------------------------------|--------------------------------|

|-------------------------------------|--------------------------------|

| Register | FCCOB Parameters |              |  |  |  |  |  |

|----------|------------------|--------------|--|--|--|--|--|

| FCCOB0   | 0x0C             | Not required |  |  |  |  |  |

| FCCOB1   | Key 0            |              |  |  |  |  |  |

| FCCOB2   | Key 1            |              |  |  |  |  |  |

| FCCOB3   | Key 2            |              |  |  |  |  |  |

| FCCOB4   | Ke               | y 3          |  |  |  |  |  |

# 22.4.10 Stop Mode

If a Flash command is active (CCIF = 0) when the MCU requests stop mode, the current Flash operation will be completed before the MCU is allowed to enter stop mode.

# 22.5 Security

The Flash module provides security information to the MCU. The Flash security state is defined by the SEC bits of the FSEC register (see Table 22-10). During reset, the Flash module initializes the FSEC register using data read from the security byte of the Flash configuration field at global address 0xFF\_FE0F. The security state out of reset can be permanently changed by programming the security byte assuming that the MCU is starting from a mode where the necessary P-Flash erase and program commands are available and that the upper region of the P-Flash is unprotected. If the Flash security byte is successfully programmed, its new value will take affect after the next MCU reset.

The following subsections describe these security-related subjects:

- Unsecuring the MCU using Backdoor Key Access

- Unsecuring the MCU in Special Single Chip Mode using BDM

- Mode and Security Effects on Flash Command Availability

# 22.5.1 Unsecuring the MCU using Backdoor Key Access

The MCU may be unsecured by using the backdoor key access feature which requires knowledge of the contents of the backdoor keys (four 16-bit words programmed at addresses 0xFF\_FE00-0xFF\_FE07). If the KEYEN[1:0] bits are in the enabled state (see Section 22.3.2.2), the Verify Backdoor Access Key command (see Section 22.4.7.11) allows the user to present four prospective keys for comparison to the keys stored in the Flash memory via the Memory Controller. If the keys presented in the Verify Backdoor Access Key command match the backdoor keys stored in the Flash memory, the SEC bits in the FSEC register (see Table 22-10) will be changed to unsecure the MCU. Key values of 0x0000 and 0xFFFF are not permitted as backdoor keys. While the Verify Backdoor Access Key command is active, P-Flash memory and EEPROM memory will not be available for read access and will return invalid data.

The user code stored in the P-Flash memory must have a method of receiving the backdoor keys from an external stimulus. This external stimulus would typically be through one of the on-chip serial ports.

If the KEYEN[1:0] bits are in the enabled state (see Section 22.3.2.2), the MCU can be unsecured by the backdoor key access sequence described below:

- 1. Follow the command sequence for the Verify Backdoor Access Key command as explained in Section 22.4.7.11

- 2. If the Verify Backdoor Access Key command is successful, the MCU is unsecured and the SEC[1:0] bits in the FSEC register are forced to the unsecure state of 10

The Verify Backdoor Access Key command is monitored by the Memory Controller and an illegal key will prohibit future use of the Verify Backdoor Access Key command. A reset of the MCU is the only method to re-enable the Verify Backdoor Access Key command. The security as defined in the Flash security byte (0xFF\_FE0F) is not changed by using the Verify Backdoor Access Key command sequence. The backdoor

**Detailed Register Address Map**

# O.8 0x0400-0x042F TIM1 (continued)

| Address           | Name      |             | Bit 7        | 6            | 5            | 4            | 3            | 2            | 1     | Bit 0 |

|-------------------|-----------|-------------|--------------|--------------|--------------|--------------|--------------|--------------|-------|-------|

| 0x0413            | TIM1TC1L  | R<br>W      | Bit 7        | Bit 6        | Bit 5        | Bit 4        | Bit 3        | Bit 2        | Bit 1 | Bit 0 |

| 0x0414–<br>0x042B | Reserved  | R<br>W      |              |              |              |              |              |              |       |       |

| 0x042C            | TIM10CPD  | R<br>W      | RESERVE<br>D | RESERVE<br>D | RESERVE<br>D | RESERVE<br>D | RESERVE<br>D | RESERVE<br>D | OCPD1 | OCPD0 |

| 0x042D            | Reserved  | R<br>W      |              |              |              |              |              |              |       |       |

| 0x042E            | TIM1PTPSR | R<br>W      | PTPS7        | PTPS6        | PTPS5        | PTPS4        | PTPS3        | PTPS2        | PTPS1 | PTPS0 |

| 0x042F            | Reserved  | R<br>W<br>W |              |              |              |              |              |              |       |       |

# 0.9 0x0480-x04AF PWM0

| Address | Name         |        | Bit 7   | 6       | 5       | 4       | 3       | 2       | 1       | Bit 0   |

|---------|--------------|--------|---------|---------|---------|---------|---------|---------|---------|---------|

| 0x0480  | PWME         | R<br>W | PWME7   | PWME6   | PWME5   | PWME4   | PWME3   | PWME2   | PWME1   | PWME0   |

| 0x0481  | PWMPOL       | R<br>W | PPOL7   | PPOL6   | PPOL5   | PPOL4   | PPOL3   | PPOL2   | PPOL1   | PPOL0   |

| 0x0482  | PWMCLK       | R<br>W | PCLK7   | PCLKL6  | PCLK5   | PCLK4   | PCLK3   | PCLK2   | PCLK1   | PCLK0   |

| 0x0483  | PWMPRCL<br>K | R<br>W | 0       | PCKB2   | PCKB1   | PCKB0   | 0       | PCKA2   | PCKA1   | PCKA0   |

| 0x0484  | PWMCAE       | R<br>W | CAE7    | CAE6    | CAE5    | CAE4    | CAE3    | CAE2    | CAE1    | CAE0    |

| 0x0485  | PWMCTL       | R<br>W | CON67   | CON45   | CON23   | CON01   | PSWAI   | PFRZ    | 0       | 0       |

| 0x0486  | PWMCLKA<br>B | R<br>W | PCLKAB7 | PCLKAB6 | PCLKAB5 | PCLKAB4 | PCLKAB3 | PCLKAB2 | PCLKAB1 | PCLKAB0 |

| 0x0487  | RESERVED     | R<br>W | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

| 0x0488  | PWMSCLA      | R<br>W | Bit 7   | 6       | 5       | 4       | 3       | 2       | 1       | Bit 0   |

| 0x0489  | PWMSCLB      | R<br>W | Bit 7   | 6       | 5       | 4       | 3       | 2       | 1       | Bit 0   |

# O.14 0x0690-0x0697 ACMP

| Address           | Name     | _      | Bit 7 | 6     | 5         | 4     | 3   | 2     | 1           | Bit 0 |

|-------------------|----------|--------|-------|-------|-----------|-------|-----|-------|-------------|-------|

| 0x0690            | ACMPC0   | R<br>W | ACE   | ACOPE | ACOPS     | ACDLY | ACH | YS1-0 | ACMOD1-0    |       |

| 0x0b91            | ACMPC1   | R 0    |       | 0     | ACPSEL1-0 |       | 0   | 0     | ACNSEL1-0   |       |

| 0,0091            | ACIMPUT  | W      |       |       | AUFSELI-U |       |     |       | AGINGEL I-U |       |

| 0x0692            | ACMPC2   | R      | 0     | 0     | 0         | 0     | 0   | 0     | 0           | ACIE  |

| 0x0092            |          | w      |       |       |           |       |     |       |             | ACIL  |

| 0x0693            | ACMPS    | R      | ACO   | 0     | 0         | 0     | 0   | 0     | 0           | ACIF  |

| 0x0095            |          | W      |       |       |           |       |     |       |             | ACIE  |

| 0x0694–<br>0x0697 | Reserved | R      | 0     | 0     | 0         | 0     | 0   | 0     | 0           | 0     |

|                   |          | W      |       |       |           |       |     |       |             |       |

# O.15 0x06C0-0x06DF CPMU

| Address | Name       |           | Bit 7   | 6       | 5    | 4           | 3           | 2           | 1     | Bit 0 |        |         |

|---------|------------|-----------|---------|---------|------|-------------|-------------|-------------|-------|-------|--------|---------|

| 0x06C0  | CPMU       | R         | 0       | 0       | 0    | 0           | 0           | 0           | 0     | 0     |        |         |

| 0,0000  | RESERVED00 | W         |         |         |      |             |             |             |       |       |        |         |

| 0x06C1  | CPMU       | R         | 0       | 0       | 0    | 0           | 0           | 0           | 0     | 0     |        |         |

| 0,0001  | RESERVED01 | W         |         |         |      |             |             |             |       |       |        |         |

| 0x06C2  | CPMU       | R         | 0       | 0       | 0    | 0           | 0           | 0           | 0     | 0     |        |         |

| 0,0002  | RESERVED02 | W         |         |         |      |             |             |             |       |       |        |         |

| 0x06C3  | CPMURFLG   | R         | 0       | PORF    | LVRF | 0           | COPRF       | 0           | OMRF  | PMRF  |        |         |

| 0,0000  |            | W         |         |         |      |             |             |             | OMIN  |       |        |         |

| 0x06C4  | CPMU       | R         | VCOFF   |         |      |             | SVND        | 1\/[5:0]    |       |       |        |         |

| 0,0004  | SYNR       | W         | 00011   | (@[1.0] |      | SYNDIV[5:0] |             |             |       |       |        |         |

| 0x06C5  | CPMU       | R         | REFFF   | 20[1.0] | 0    | 0           | REFDIV[3:0] |             |       |       |        |         |

| 0,0000  | REFDIV     | W         | KEI I I | (Q[1.0] |      |             |             |             |       |       |        |         |

| 0x06C6  | CPMU       | R         | 0       | 0       | 0    |             | F           | POSTDIV[4:0 | 11    |       |        |         |

| 0,0000  | POSTDIV    | W         |         |         |      |             |             |             |       |       |        |         |

| 0x06C7  | CPMUIFLG   | R         | RTIF    | 0       | 0    | LOCKIF      | LOCK        | 0           | OSCIF | UPOSC |        |         |

| 0,0001  |            | W         | IXIII   |         |      | LOOKI       |             |             | 0301  |       |        |         |

| 0x06C8  | CPMUINT    | CPMUINT R | CPMUINT | CPMUINT | RTIE | 0           | 0           | LOCKIE      | 0     | 0     | OSCIE  | 0       |

| 0,00000 |            | W         |         |         |      | LOOKIL      |             |             | COOL  |       |        |         |

| 0x06C9  | CPMUCLKS   | R         | PLLSEL  | PSTP    | CSAD | COP         | PRE         | PCE         | RTI   | COP   |        |         |

| 0,00000 |            | W         | W       | W       |      | 1011        | 00/12       | OSCSEL1     |       | 102   | OSCSEL | OSCSEL0 |

| 0x06CA  | CPMUPLL    | R         | 0       | 0       | FM1  | FM0         | 0           | 0           | 0     | 0     |        |         |

|         |            | W         |         |         |      | 1 100       |             |             |       |       |        |         |

| 0x06CB  | CPMURTI    | R         | RTDEC   | RTR6    | RTR5 | RTR4        | RTR3        | RTR2        | RTR1  | RTR0  |        |         |

| 0,0000  |            | W         | NIDE0   |         |      |             |             | 11112       | 11111 |       |        |         |