Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | S12Z                                                                   |

| Core Size                  | 16-Bit                                                                 |

| Speed                      | 32MHz                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SCI, SPI, UART/USART           |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 34                                                                     |

| Program Memory Size        | 64KB (64K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 512 x 8                                                                |

| RAM Size                   | 1K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 5.5V ~ 18V                                                             |

| Data Converters            | A/D 10x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 48-LQFP                                                                |

| Supplier Device Package    | 48-LQFP (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s912zvl64f0mlf |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Port Integration Module (S12ZVLPIMV2)

| Global<br>Address | Register<br>Name | Bit 7          | 6        | 5        | 4        | 3        | 2        | 1         | Bit 0    |

|-------------------|------------------|----------------|----------|----------|----------|----------|----------|-----------|----------|

| 0x0288            | PPSADH           | R 0<br>W       | 0        | 0        | 0        | 0        | 0        | PPSADH1   | PPSADH0  |

| 0x0289            | PPSADL           | R<br>W PPSADL7 | PPSADL6  | PPSADL5  | PPSADL4  | PPSADL3  | PPSADL2  | PPSADL1   | PPSADL0  |

| 0x028A–<br>0x028B | Reserved         | R 0<br>W       | 0        | 0        | 0        | 0        | 0        | 0         | 0        |

| 0x028C            | PIEADH           | R 0<br>W       | 0        | 0        | 0        | 0        | 0        | · PIEADH1 | PIEADH0  |

| 0x028D            | PIEADL           | R<br>W PIEADL7 | PIEADL6  | PIEADL5  | PIEADL4  | PIEADL3  | PIEADL2  | PIEADL1   | PIEADL0  |

| 0x028E            | PIFADH           | R 0<br>W       | 0        | 0        | 0        | 0        | 0        | PIFADH1   | PIFADH0  |

| 0x028F            | PIFADL           | R<br>W PIFADL7 | PIFADL6  | PIFADL5  | PIFADL4  | PIFADL3  | PIFADL2  | PIFADL1   | PIFADL0  |

| 0x0290–<br>0x0297 | Reserved         | R 0<br>W       | 0        | 0        | 0        | 0        | 0        | 0         | 0        |

| 0x0298            | DIENADH          | R 0<br>W       | 0        | 0        | 0        | 0        | 0        | DIENADH1  | DIENADH0 |

| 0x0299            | DIENADL          | R<br>DIENADL7  | DIENADL6 | DIENADL5 | DIENADL4 | DIENADL3 | DIENADL2 | DIENADL1  | DIENADL0 |

| 0x029A–<br>0x02BF | Reserved         | R 0<br>W       | 0        | 0        | 0        | 0        | 0        | 0         | 0        |

| 0x02C0            | PTT              | R<br>PTT7<br>W | PTT6     | PTT5     | PTT4     | PTT3     | PTT2     | PTT1      | PTT0     |

| 0x02C1            | PTIT             | R PTIT7<br>W   | PTIT6    | PTIT5    | PTIT4    | PTIT3    | PTIT2    | PTIT1     | PTIT0    |

| 0x02C2            | DDRT             | R<br>W DDRT7   | DDRT6    | DDRT5    | DDRT4    | DDRT3    | DDRT2    | DDRT1     | DDRT0    |

| 0x02C3            | PERT             | R<br>W PERT7   | PERT6    | PERT5    | PERT4    | PERT3    | PERT2    | PERT1     | PERT0    |

| 0x02C4            | PPST             | R<br>W PPST7   | PPST6    | PPST5    | PPST4    | PPST3    | PPST2    | PPST1     | PPST0    |

Read: All modes through BDC operation only.

Write: All modes through BDC operation only, when not secured, but subject to the following:

- Bits 7,3 and 2 can only be written by WRITE\_BDCCSR commands.

- Bit 5 can only be written by WRITE\_BDCCSR commands when the device is not in stop mode.

- Bits 6, 1 and 0 cannot be written. They can only be updated by internal hardware.

#### Table 5-5. BDCCSRH Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ENBDC  | <ul> <li>Enable BDC — This bit controls whether the BDC is enabled or disabled. When enabled, active BDM can be entered and non-intrusive commands can be carried out. When disabled, active BDM is not possible and the valid command set is restricted. Further information is provided in Table 5-7.</li> <li>0 BDC disabled</li> <li>1 BDC enabled</li> <li>Note: ENBDC is set out of reset in special single chip mode.</li> </ul>                                                                                                                                                                                                                                                          |

| 6<br>BDMACT | <ul> <li>BDM Active Status — This bit becomes set upon entering active BDM. BDMACT is cleared as part of the active BDM exit sequence.</li> <li>0 BDM not active</li> <li>1 BDM active</li> <li>Note: BDMACT is set out of reset in special single chip mode.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5<br>BDCCIS | <ul> <li>BDC Continue In Stop — If ENBDC is set then BDCCIS selects the type of BDC operation in stop mode (as shown in Table 5-3). If ENBDC is clear, then the BDC has no effect on stop mode and no BDC communication is possible. If ACK pulse handshaking is enabled, then the first ACK pulse following stop mode entry is a long ACK. This bit cannot be written when the device is in stop mode.</li> <li>Only the BDCCLK clock continues in stop mode</li> <li>All clocks continue in stop mode</li> </ul>                                                                                                                                                                               |

| 3<br>STEAL  | <ul> <li>Steal enabled with ACK— This bit forces immediate internal accesses with the ACK handshaking protocol enabled. If ACK handshaking is disabled then BDC accesses steal the next bus cycle.</li> <li>0 If ACK is enabled then BDC accesses await a free cycle, with a timeout of 512 cycles</li> <li>1 If ACK is enabled then BDC accesses are carried out in the next bus cycle</li> </ul>                                                                                                                                                                                                                                                                                               |

| 2<br>CLKSW  | <ul> <li>Clock Switch — The CLKSW bit controls the BDCSI clock source. This bit is initialized to "0" by each reset and can be written to "1". Once it has been set, it can only be cleared by a reset. When setting CLKSW a minimum delay of 150 cycles at the initial clock speed must elapse before the next command can be sent. This guarantees that the start of the next BDC command uses the new clock for timing subsequent BDC communications.</li> <li>0 BDCCLK used as BDCSI clock source</li> <li>1 Device fast clock used as BDCSI clock source</li> <li>Note: Refer to the device specification to determine which clock connects to the BDCCLK and fast clock inputs.</li> </ul> |

| 1<br>UNSEC  | <ul> <li>Unsecure — If the device is unsecure, the UNSEC bit is set automatically.</li> <li>0 Device is secure.</li> <li>1 Device is unsecure.</li> <li>Note: When UNSEC is set, the device is unsecure and the state of the secure bits in the on-chip Flash EEPROM can be changed.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                  |

| 0<br>ERASE  | <ul> <li>Erase Flash — This bit can only be set by the dedicated ERASE_FLASH command. ERASE is unaffected by write accesses to BDCCSR. ERASE is cleared either when the mass erase sequence is completed, independent of the actual status of the flash array or by a soft reset.</li> <li>Reading this bit indicates the status of the requested mass erase sequence.</li> <li>0 No flash mass erase sequence pending completion</li> <li>1 Flash mass erase sequence pending completion.</li> </ul>                                                                                                                                                                                            |

#### NOTE

DUMP\_MEM{\_WS} is a valid command only when preceded by SYNC, NOP, READ\_MEM{\_WS}, or another DUMP\_MEM{\_WS} command. Otherwise, an illegal command response is returned, setting the ILLCMD bit. NOP can be used for inter-command padding without corrupting the address pointer.

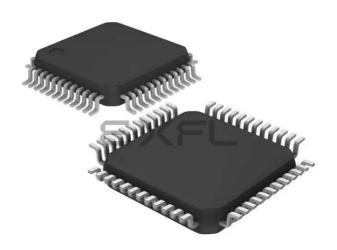

The size field (sz) is examined each time a DUMP\_MEM{\_WS} command is processed, allowing the operand size to be dynamically altered. The examples show the DUMP\_MEM.B{\_WS}, DUMP\_MEM.W{\_WS} and DUMP\_MEM.L{\_WS} commands.

### 5.4.4.6 FILL\_MEM.sz, FILL\_MEM.sz\_WS

#### FILL\_MEM.sz

Write memory specified by debug address register, then increment address **Non-intrusive**

#### FILL\_MEM.sz\_WS

Write memory specified by debug address register with status, then increment address **Non-intrusive**

| 0x13             | Data[7-0]        |             | BDCCSR           | L |                  |   |

|------------------|------------------|-------------|------------------|---|------------------|---|

| host →<br>target | host →<br>target | D<br>L<br>Y | target →<br>host |   |                  |   |

| 0x17             | Data[15-8]       |             | Data[7-0]        |   | BDCCSRL          |   |

| host →<br>target | host →<br>target |             | host →<br>target |   | target →<br>host | _ |

# returned before the read data. This status byte reflects the state after the memory read was performed. If enabled, an ACK pulse is driven before the data bytes are transmitted.

The examples show the READ\_MEM.B{\_WS}, READ\_MEM.W{\_WS} and READ\_MEM.L{\_WS} commands.

# 5.4.4.12 READ\_DBGTB

Read DBG trace buffer

| 0x07             |                  | TB Line<br>[31-24] | TB Line<br>[23-16] | TB Line<br>[15-8] | TB Line<br>[7-0] |                  | TB Line<br>[63-56] | TB Line<br>[55-48] | TB Line<br>[47-40] | TB Line<br>[39-32] |

|------------------|------------------|--------------------|--------------------|-------------------|------------------|------------------|--------------------|--------------------|--------------------|--------------------|

| host →<br>target | D<br>A<br>C<br>K | target →<br>host   | target →<br>host   | target →<br>host  | target →<br>host | D<br>A<br>C<br>K | target →<br>host   | target →<br>host   | target →<br>host   | target →<br>host   |

This command is only available on devices, where the DBG module includes a trace buffer. Attempted use of this command on devices without a traace buffer return 0x00.

Read 64 bits from the DBG trace buffer. Refer to the DBG module description for more detailed information. If enabled an ACK pulse is generated before each 32-bit longword is ready to be read by the host. After issuing the first ACK a timeout is still possible whilst accessing the second 32-bit longword, since this requires separate internal accesses. The first 32-bit longword corresponds to trace buffer line bits[31:0]; the second to trace buffer line bits[63:32]. If ACK handshaking is disabled, the host must wait 16 clock cycles (DLY) after completing the first 32-bit read before starting the second 32-bit read.

# 5.4.4.13 READ\_SAME.sz, READ\_SAME.sz\_WS

#### READ\_SAME

Read same location specified by previous READ\_MEM{\_WS}

| 0x54                      |                  | Data[15-8]       | Data[7-0]        | I |

|---------------------------|------------------|------------------|------------------|---|

| host $\rightarrow$ target | D<br>A<br>C<br>K | target →<br>host | target →<br>host | - |

#### READ\_SAME\_WS

Read same location specified by previous READ\_MEM{\_WS}

| 0x55             |             | BDCCSRL          | Data [15-8]      | Data [7-0]       |  |

|------------------|-------------|------------------|------------------|------------------|--|

| host →<br>target | D<br>L<br>Y | target →<br>host | target →<br>host | target →<br>host |  |

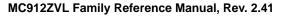

#### MC912ZVL Family Reference Manual, Rev. 2.41

Background Debug Controller (S12ZBDCV2)

Non-intrusive

Non-intrusive

Non-intrusive

#### Background Debug Controller (S12ZBDCV2)

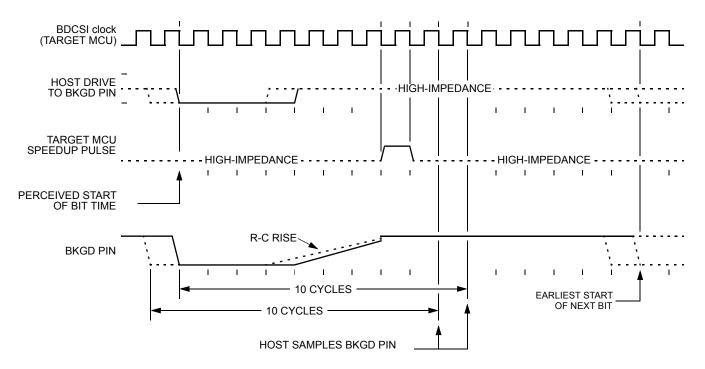

drive at the latest after 6 clock cycles, before the target drives a brief high speedup pulse seven target clock cycles after the perceived start of the bit time. The host should sample the bit level about 10 target clock cycles after it started the bit time.

Figure 5-7. BDC Target-to-Host Serial Bit Timing (Logic 1)

Figure 5-8 shows the host receiving a logic 0 from the target. The host initiates the bit time but the target finishes it. Since the target wants the host to receive a logic 0, it drives the BKGD pin low for 13 target clock cycles then briefly drives it high to speed up the rising edge. The host samples the bit level about 10 target clock cycles after starting the bit time.

S12 Clock, Reset and Power Management Unit (S12CPMU\_UHV)

| CR2 | CR1 | CR0 | COPCLK<br>Cycles to time-out<br>(COPCLK is ACLK divided by 2) |

|-----|-----|-----|---------------------------------------------------------------|

| 0   | 0   | 0   | COP disabled                                                  |

| 0   | 0   | 1   | 2 <sup>7</sup>                                                |

| 0   | 1   | 0   | 2 <sup>9</sup>                                                |

| 0   | 1   | 1   | 2 <sup>11</sup>                                               |

| 1   | 0   | 0   | 2 <sup>13</sup>                                               |

| 1   | 0   | 1   | 2 <sup>15</sup>                                               |

| 1   | 1   | 0   | 2 <sup>16</sup>                                               |

| 1   | 1   | 1   | 2 <sup>17</sup>                                               |

Table 9-16. COP Watchdog Rates if COPOSCSEL1=1.

### • MCU Wait Mode

Depending on the ADC Wait Mode configuration bit SWAI, the ADC either continues conversion in MCU Wait Mode or freezes conversion at the next conversion boundary before MCU Wait Mode is entered.

### ADC behavior for configuration SWAI =1'b0:

The ADC continues conversion during Wait Mode according to the conversion flow control sequence. It is assumed that the conversion flow control sequence is continued (conversion flow control bits TRIG, RSTA, SEQA, and LDOK are serviced accordingly).

### ADC behavior for configuration SWAI = 1'b1:

At MCU Wait Mode request the ADC should be idle (no conversion or conversion sequence or Command Sequence List ongoing).

If a conversion, conversion sequence, or CSL is in progress when an MCU Wait Mode request is issued, a Sequence Abort Event occurs automatically and any ongoing conversion finish. After the Sequence Abort Event finishes, if the STR\_SEQA bit is set (STR\_SEQA=1), then the conversion result is stored and the corresponding flags are set. If the STR\_SEQA bit is cleared (STR\_SEQA=0), then the conversion result is not stored and the corresponding flags are not set. Alternatively the Sequence Abort Event can be issued by software before MCU Wait Mode request. As soon as flag SEQAD\_IF is set, the MCU Wait Mode request can be issued. With the occurrence of the MCU Wait Mode request until exit from Wait Mode all flow control

signals (RSTA, SEQA, LDOK, TRIG) are cleared.

After exiting MCU Wait Mode, the following happens in the order given with expected event(s) depending on the conversion flow control mode:

- In ADC conversion flow control mode "Trigger Mode", a Restart Event is expected to occur. This simultaneously sets bit TRIG and RSTA causing the ADC to execute the Restart Event (CMD\_IDX and RVL\_IDX cleared) followed by the Trigger Event. The Restart Event can be generated automatically after exit from MCU Wait Mode if bit AUT\_RSTA is set.

- In ADC conversion flow control mode "Restart Mode", a Restart Event is expected to set bit RSTA only (ADC already aborted at MCU Wait Mode entry hence bit SEQA must not be set simultaneously) causing the ADC to execute the Restart Event (CDM\_IDX and RVL\_IDX cleared). The Restart Event can be generated automatically after exit from MCU Wait Mode if bit AUT\_RSTA is set.

- The RVL buffer select (RVL\_SEL) is not changed if a CSL is in process at MCU Wait Mode request. Hence the same RVL buffer will be used after exit from Wait Mode that was used when Wait Mode request occurred.

#### Analog-to-Digital Converter (ADC12B\_LBA)

| CMD_SEL[1] | CMD_SEL[0] | Conversion Command Type Description                                                                                                                                   |

|------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | 0          | End Of List<br>(Automatic wrap to top of CSL<br>and Continue Conversion)                                                                                              |

| 1          | 1          | End Of List<br>(Wrap to top of CSL and:<br>- In "Restart Mode" wait for Restart Event followed by a Trigger<br>- In "Trigger Mode" wait for Trigger or Restart Event) |

### Table 10-21. Conversion Command Type Select

### 12.2.5.1 PGA\_REF0 Pin

This analog pin is used as reference voltage and amplifier minus input voltage if the associated control register bit is set.

### 12.2.5.2 PGA\_REF1 Pin

This analog pin is used as reference voltage and amplifier minus input voltage if the associated control register bit is set.

### 12.2.5.3 PGA\_IN0 Pin

This analog pin is used as amplifier plus input voltage if the associated control register bit is set.

### 12.2.5.4 PGA\_IN1 Pin

This analog pin is used as amplifier plus input voltage if the associated control register bit is set.

### 12.2.6 PGA\_OUT Pin

This analog pin provides the analog amplifier output voltage of the PGA as a function of the gain, offset and the reference voltage.

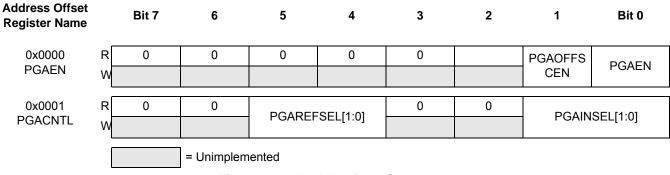

# 12.3 Memory Map and Register Definition

This sections provides the detailed information of all registers for the PGA module.

## 12.3.1 Register Summary

Figure 12-2 shows the summary of all implemented registers inside the PGA module.

NOTE

Register Address = Module Base Address + Address Offset, where the Module Base Address is defined at the MCU level and the Address Offset is defined at the module level.

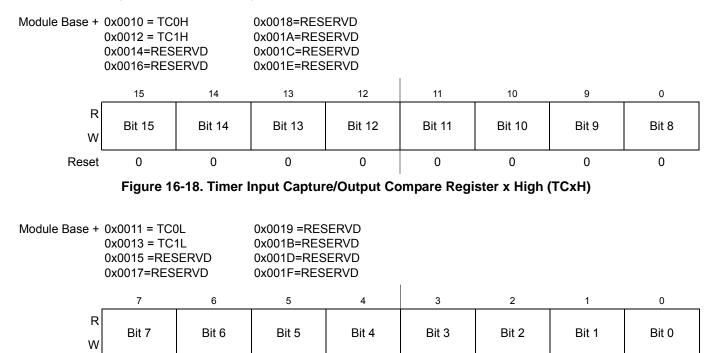

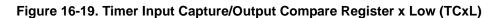

### 16.3.2.12 Timer Input Capture/Output Compare Registers High and Low 0– 1(TCxH and TCxL)

0

0

0

0

0

0

<sup>1</sup> This register is available only when the corresponding channel exists and is reserved if that channel does not exist. Writes to a reserved register have no functional effect. Reads from a reserved register return zeroes.

Depending on the TIOS bit for the corresponding channel, these registers are used to latch the value of the free-running counter when a defined transition is sensed by the corresponding input capture edge detector or to trigger an output action for output compare.

#### Read: Anytime

Reset

0

0

Write: Anytime for output compare function. Writes to these registers have no meaning or effect during input capture. All timer input capture/output compare registers are reset to 0x0000.

#### NOTE

Read/Write access in byte mode for high byte should take place before low byte otherwise it will give a different result.

Setting OCPDx to zero allows the internal register to drive the programmed state to OCx. This allows a glitch free switch over of port from general purpose I/O to timer output once the OCPDx bit is set to zero.

# 16.5 Resets

The reset state of each individual bit is listed within Section 16.3, "Memory Map and Register Definition" which details the registers and their bit fields

# 16.6 Interrupts

This section describes interrupts originated by the TIM16B2CV3 block. Table 16-18 lists the interrupts generated by the TIM16B2CV3 to communicate with the MCU.

| Interrupt | Offset | Vector | Priority | Source            | Description                              |

|-----------|--------|--------|----------|-------------------|------------------------------------------|

| C[1:0]F   | —      | _      | —        | Timer Channel 1–0 | Active high timer channel interrupts 1–0 |

| TOF       |        |        | _        | Timer Overflow    | Timer Overflow interrupt                 |

Table 16-18. TIM16B2CV3 Interrupts

The TIM16B2CV3 could use up to 3 interrupt vectors. The interrupt vector offsets and interrupt numbers are chip dependent.

# 16.6.1 Channel [1:0] Interrupt (C[1:0]F)

This active high outputs will be asserted by the module to request a timer channel 7 - 0 interrupt. The TIM block only generates the interrupt and does not service it. Only bits related to implemented channels are valid.

# 16.6.2 Timer Overflow Interrupt (TOF)

This active high output will be asserted by the module to request a timer overflow interrupt. The TIM block only generates the interrupt and does not service it.

| Field            | Description                                                                                                                                                                           |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6–4<br>PCKB[2:0] | <b>Prescaler Select for Clock B</b> — Clock B is one of two clock sources which can be used for all channels. These three bits determine the rate of clock B, as shown in Table 17-8. |

| 2–0<br>PCKA[2:0] | <b>Prescaler Select for Clock A</b> — Clock A is one of two clock sources which can be used for all channels. These three bits determine the rate of clock A, as shown in Table 17-8. |

#### Table 17-7. PWMPRCLK Field Descriptions

#### Table 17-8. Clock A or Clock B Prescaler Selects

| PCKA/B2 | PCKA/B1 | PCKA/B0 | Value of Clock A/B |

|---------|---------|---------|--------------------|

| 0       | 0       | 0       | bus clock          |

| 0       | 0       | 1       | bus clock / 2      |

| 0       | 1       | 0       | bus clock / 4      |

| 0       | 1       | 1       | bus clock / 8      |

| 1       | 0       | 0       | bus clock / 16     |

| 1       | 0       | 1       | bus clock / 32     |

| 1       | 1       | 0       | bus clock / 64     |

| 1       | 1       | 1       | bus clock / 128    |

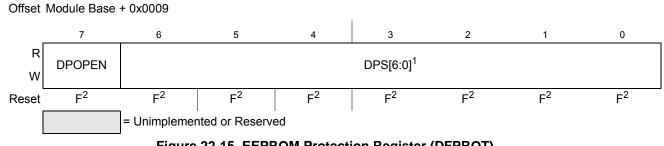

### 17.3.2.5 PWM Center Align Enable Register (PWMCAE)

The PWMCAE register contains eight control bits for the selection of center aligned outputs or left aligned outputs for each PWM channel. If the CAEx bit is set to a one, the corresponding PWM output will be center aligned. If the CAEx bit is cleared, the corresponding PWM output will be left aligned. See Section 17.4.2.5, "Left Aligned Outputs" and Section 17.4.2.6, "Center Aligned Outputs" for a more detailed description of the PWM output modes.

Module Base + 0x0004

Figure 17-7. PWM Center Align Enable Register (PWMCAE)

Read: Anytime

Write: Anytime

#### NOTE

Write these bits only when the corresponding channel is disabled.

#### Table 17-9. PWMCAE Field Descriptions

Note: Bits related to available channels have functional significance. Writing to unavailable bits has no effect. Read from unavailable bits return a zero

|   | Field | Description                                                                                                                                                 |

|---|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ( |       | Center Aligned Output Modes on Channels 7–0<br>0 Channels 7–0 operate in left aligned output mode.<br>1 Channels 7–0 operate in center aligned output mode. |

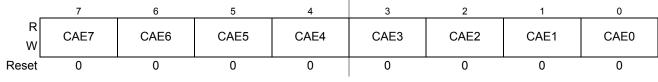

## 17.3.2.6 PWM Control Register (PWMCTL)

The PWMCTL register provides for various control of the PWM module.

Module Base + 0x0005

#### Read: Anytime

Write: Anytime

There are up to four control bits for concatenation, each of which is used to concatenate a pair of PWM channels into one 16-bit channel. If the corresponding channels do not exist on a particular derivative, then writes to these bits have no effect and reads will return zeroes. When channels 6 and 7 are concatenated, channel 6 registers become the high order bytes of the double byte channel. When channels 4 and 5 are concatenated, channel 4 registers become the high order bytes of the double byte channel. When channels 2 and 3 are concatenated, channel 2 registers become the high order bytes of the double byte of the double byte channel. When channels 0 and 1 are concatenated, channel 0 registers become the high order bytes of the double byte of the double byte channel.

See Section 17.4.2.7, "PWM 16-Bit Functions" for a more detailed description of the concatenation PWM Function.

### NOTE

Change these bits only when both corresponding channels are disabled.

| SPPR2 | SPPR1 | SPPR0 | SPR2 | SPR1 | SPR0 | Baud Rate<br>Divisor | Baud Rate      |  |

|-------|-------|-------|------|------|------|----------------------|----------------|--|

| 0     | 0     | 1     | 0    | 0    | 1    | 8                    | 3.125 Mbit/s   |  |

| 0     | 0     | 1     | 0    | 1    | 0    | 16                   | 1.5625 Mbit/s  |  |

| 0     | 0     | 1     | 0    | 1    | 1    | 32                   | 781.25 kbit/s  |  |

| 0     | 0     | 1     | 1    | 0    | 0    | 64                   | 390.63 kbit/s  |  |

| 0     | 0     | 1     | 1    | 0    | 1    | 128                  | 195.31 kbit/s  |  |

| 0     | 0     | 1     | 1    | 1    | 0    | 256                  | 97.66 kbit/s   |  |

| 0     | 0     | 1     | 1    | 1    | 1    | 512                  | 48.83 kbit/s   |  |

| 0     | 1     | 0     | 0    | 0    | 0    | 6                    | 4.16667 Mbit/s |  |

| 0     | 1     | 0     | 0    | 0    | 1    | 12                   | 2.08333 Mbit/s |  |

| 0     | 1     | 0     | 0    | 1    | 0    | 24                   | 1.04167 Mbit/s |  |

| 0     | 1     | 0     | 0    | 1    | 1    | 48                   | 520.83 kbit/s  |  |

| 0     | 1     | 0     | 1    | 0    | 0    | 96                   | 260.42 kbit/s  |  |

| 0     | 1     | 0     | 1    | 0    | 1    | 192                  | 130.21 kbit/s  |  |

| 0     | 1     | 0     | 1    | 1    | 0    | 384                  | 65.10 kbit/s   |  |

| 0     | 1     | 0     | 1    | 1    | 1    | 768                  | 32.55 kbit/s   |  |

| 0     | 1     | 1     | 0    | 0    | 0    | 8                    | 3.125 Mbit/s   |  |

| 0     | 1     | 1     | 0    | 0    | 1    | 16                   | 1.5625 Mbit/s  |  |

| 0     | 1     | 1     | 0    | 1    | 0    | 32                   | 781.25 kbit/s  |  |

| 0     | 1     | 1     | 0    | 1    | 1    | 64                   | 390.63 kbit/s  |  |

| 0     | 1     | 1     | 1    | 0    | 0    | 128                  | 195.31 kbit/s  |  |

| 0     | 1     | 1     | 1    | 0    | 1    | 256                  | 97.66 kbit/s   |  |

| 0     | 1     | 1     | 1    | 1    | 0    | 512                  | 48.83 kbit/s   |  |

| 0     | 1     | 1     | 1    | 1    | 1    | 1024                 | 24.41 kbit/s   |  |

| 1     | 0     | 0     | 0    | 0    | 0    | 10                   | 2.5 Mbit/s     |  |

| 1     | 0     | 0     | 0    | 0    | 1    | 20                   | 1.25 Mbit/s    |  |

| 1     | 0     | 0     | 0    | 1    | 0    | 40                   | 625 kbit/s     |  |

| 1     | 0     | 0     | 0    | 1    | 1    | 80                   | 312.5 kbit/s   |  |

| 1     | 0     | 0     | 1    | 0    | 0    | 160                  | 156.25 kbit/s  |  |

| 1     | 0     | 0     | 1    | 0    | 1    | 320                  | 78.13 kbit/s   |  |

| 1     | 0     | 0     | 1    | 1    | 0    | 640                  | 39.06 kbit/s   |  |

| 1     | 0     | 0     | 1    | 1    | 1    | 1280                 | 19.53 kbit/s   |  |

| 1     | 0     | 1     | 0    | 0    | 0    | 12                   | 2.08333 Mbit/s |  |

| 1     | 0     | 1     | 0    | 0    | 1    | 24                   | 1.04167 Mbit/s |  |

| 1     | 0     | 1     | 0    | 1    | 0    | 48                   | 520.83 kbit/s  |  |

| 1     | 0     | 1     | 0    | 1    | 1    | 96                   | 260.42 kbit/s  |  |

| 1     | 0     | 1     | 1    | 0    | 0    | 192                  | 130.21 kbit/s  |  |

| 1     | 0     | 1     | 1    | 0    | 1    | 384                  | 65.10 kbit/s   |  |

| 1     | 0     | 1     | 1    | 1    | 0    | 768                  | 32.55 kbit/s   |  |

| 1     | 0     | 1     | 1    | 1    | 1    | 1536                 | 16.28 kbit/s   |  |

| 1     | 1     | 0     | 0    | 0    | 0    | 14                   | 1.78571 Mbit/s |  |

| 1     | 1     | 0     | 0    | 0    | 1    | 28                   | 892.86 kbit/s  |  |

| 1     | 1     | 0     | 0    | 1    | 0    | 56                   | 446.43 kbit/s  |  |

Table 19-7. Example SPI Baud Rate Selection (25 MHz Bus Clock) (Sheet 2 of 3)

# 21.2.2 LGND — LIN Ground Pin

This pin is the device LIN ground connection. It is used to sink currents related to the LIN Bus pin. A de-coupling capacitor external to the device (typically 220 pF, X7R ceramic) between LIN and LGND can further improve the quality of this ground and filter noise.

# 21.2.3 VLINSUP — Positive Power Supply

External power supply to the chip. The VLINSUP supply mapping is described in device level documentation.

# 21.2.4 LPTxD — LIN Transmit Pin

This pin can be routed to the SCI, LPDR1 register bit, an external pin, or other options. Please refer to the PIM chapter of the device specification for the available routing options.

This input is only used in normal mode; in other modes the value of this pin is ignored.

# 21.2.5 LPRxD — LIN Receive Pin

This pin can be routed to the SCI, an external pin, or other options. Please refer to the PIM chapter of the device specification for the available routing options.

In standby mode this output is disabled, and sends only a short pulse in case the wake-up functionality is enabled and a valid wake-up pulse was received in the LIN Bus.

# 21.3 Memory Map and Register Definition

This section provides a detailed description of all registers accessible in the LIN Physical Layer.

# 21.3.1 Module Memory Map

A summary of the registers associated with the S12LINPHYV2 module is shown in Table 21-2. Detailed descriptions of the registers and bits are given in the subsections that follow.

### NOTE

Register Address = Module Base Address + Address Offset, where the Module Base Address is defined at the MCU level and the Address Offset is defined at the module level.

### 22.3.2.9.1 P-Flash Protection Restrictions

In Normal Single Chip mode the general guideline is that P-Flash protection can only be added and not removed. Table 22-22 specifies all valid transitions between P-Flash protection scenarios. Any attempt to write an invalid scenario to the FPROT register will be ignored. The contents of the FPROT register reflect the active protection scenario. See the FPHS and FPLS bit descriptions for additional restrictions.

| From                   | To Protection Scenario <sup>1</sup> |   |   |   |   |   |   |   |  |

|------------------------|-------------------------------------|---|---|---|---|---|---|---|--|

| Protection<br>Scenario | 0                                   | 1 | 2 | 3 | 4 | 5 | 6 | 7 |  |

| 0                      | Х                                   | Х | Х | Х |   |   |   |   |  |

| 1                      |                                     | Х |   | Х |   |   |   |   |  |

| 2                      |                                     |   | Х | Х |   |   |   |   |  |

| 3                      |                                     |   |   | Х |   |   |   |   |  |

| 4                      |                                     |   |   | Х | Х |   |   |   |  |

| 5                      |                                     |   | Х | Х | Х | Х |   |   |  |

| 6                      |                                     | Х |   | Х | Х |   | Х |   |  |

| 7                      | Х                                   | Х | Х | Х | Х | Х | Х | Х |  |

Table 22-22. P-Flash Protection Scenario Transitions

<sup>1</sup> Allowed transitions marked with X, see Figure 22-14 for a definition of the scenarios.

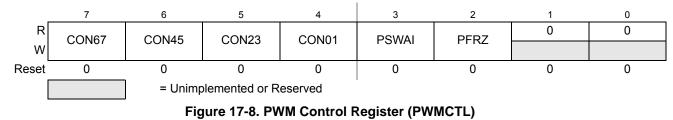

# 22.3.2.10 EEPROM Protection Register (DFPROT)

The DFPROT register defines which EEPROM sectors are protected against program and erase operations.

Figure 22-15. EEPROM Protection Register (DFPROT)

<sup>1</sup> The number of implemented DPS bits depends on the EEPROM memory size, as explained below.

<sup>2</sup> Loaded from Flash configuration field, during reset sequence.

The (unreserved) bits of the DFPROT register are writable in Normal Single Chip mode with the restriction that protection can be added but not removed. Writes in Normal Single Chip mode must increase the DPS value and the DPOPEN bit can only be written from 1 (protection disabled) to 0 (protection enabled). If the DPOPEN bit is set, the state of the DPS bits is irrelevant. All DPOPEN/DPS bit registers are writable without restriction in Special Single Chip Mode.

# Appendix L MSCAN Electrical Specifications

# L.1 MSCAN Wake-up Pulse Timing

#### Table L-1. MSCAN Wake-up Pulse Characteristics (Junction Temperature From –40°C To +175°C)

| Condi | Conditions are 3.2 V < $V_{DDX}$ < 5.15 V, unless otherwise noted. |                                       |                  |     |     |     |      |  |  |  |  |

|-------|--------------------------------------------------------------------|---------------------------------------|------------------|-----|-----|-----|------|--|--|--|--|

| Num   | С                                                                  | Rating                                | Symbol           | Min | Тур | Мах | Unit |  |  |  |  |

| 1     |                                                                    | MSCAN wake-up dominant pulse filtered | t <sub>WUP</sub> | —   | —   | 1.5 | μS   |  |  |  |  |

| 2     |                                                                    | MSCAN wake-up dominant pulse pass     | t <sub>WUP</sub> | 5   | —   | _   | μS   |  |  |  |  |

### NOTE

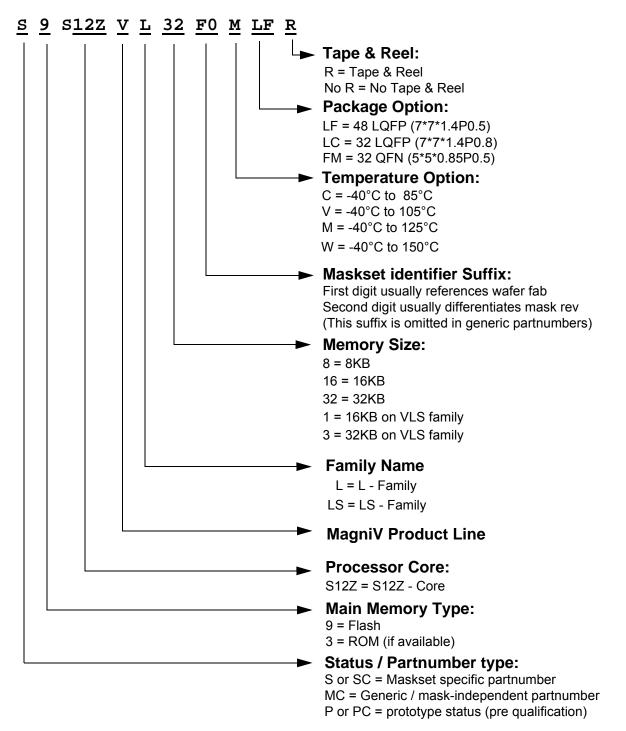

Not every combination is offered. Table 1-2 lists available derivatives. The mask identifier suffix and the Tape & Reel suffix are always both omitted from the partnumber which is actually marked on the device.