#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | S12Z                                                                   |

| Core Size                  | 16-Bit                                                                 |

| Speed                      | 32MHz                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SCI, SPI, UART/USART           |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 19                                                                     |

| Program Memory Size        | 64KB (64K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 512 x 8                                                                |

| RAM Size                   | 1K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 5.5V ~ 18V                                                             |

| Data Converters            | A/D 6x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 32-LQFP                                                                |

| Supplier Device Package    | 32-LQFP (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s912zvl64f0vlc |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Revision History**

| Date              | Revision<br>Level | Description                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|-------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 13 May 2015       | 2.00 Draft E      | <ul> <li>Added new version of Chapter 12, "Programmable Gain Amplifier<br/>(PGAV1)</li> <li>Added new version of Chapter 11, "Digital Analog Converter<br/>(DAC_8B5V_V2)</li> <li>added missing modules DAC, PGA, ACMP, PWM1 to Appendix O,<br/>"Detailed Register Address Map</li> <li>update voltage range inside Appendix I, "ACMP Electrical Specifications<br/>and Appendix G, "DAC_8B5V Electrical Specifications</li> </ul> |  |  |

| 05 June 2015      | 2.00 Draft F      | <ul> <li>Added new version of Chapter 1, "Device Overview MC9S12ZVL-Family"</li> <li>Added new version of Appendix A, "MCU Electrical Specifications</li> </ul>                                                                                                                                                                                                                                                                    |  |  |

| 27 October 2015   | 2.00 Draft G      | <ul> <li>Added new version v0.4 of Appendix A, "MCU Electrical Specifications"</li> <li>correct Order Information</li> </ul>                                                                                                                                                                                                                                                                                                       |  |  |

| 25 February 2016  | 2.00Draft I       | <ul> <li>change to NXP style</li> <li>Added new version of Appendix A, "MCU Electrical Specifications</li> </ul>                                                                                                                                                                                                                                                                                                                   |  |  |

| 10 May 2016       | 2.00              | <ul> <li>Added version 0.80 of Appendix A, "MCU Electrical Specifications</li> <li>changed to Chapter 10, "Analog-to-Digital Converter (ADC12B_LBA) version V3</li> </ul>                                                                                                                                                                                                                                                          |  |  |

| 08 August 2017    | 2.10              | <ul> <li>Added version 0.90 of Appendix A, "MCU Electrical Specifications</li> <li>Added version 2.00 of Chapter 1, "Device Overview MC9S12ZVL-Family</li> </ul>                                                                                                                                                                                                                                                                   |  |  |

| 12 September 2017 | 2.20              | Added version 1.0 of Appendix A, "MCU Electrical Specifications                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 10 October 2017   | 2.30              | Added version 1.1 of Appendix A, "MCU Electrical Specifications                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 19 October 2017   | 2.40              | Added version 1.2 of Appendix A, "MCU Electrical Specifications                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 24 October 2017   | 2.41              | Added version 1.21 of Appendix A, "MCU Electrical Specifications                                                                                                                                                                                                                                                                                                                                                                   |  |  |

NXP Semiconductor reserves the right to make changes without further notice to any products herein. NXP Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does NXP Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. NXP Semiconductor does not convey any license under its patent rights nor the rights of others. NXP Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the NXP Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold NXP Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that NXP Semiconductor was negligent regarding the design or manufacture of the part.

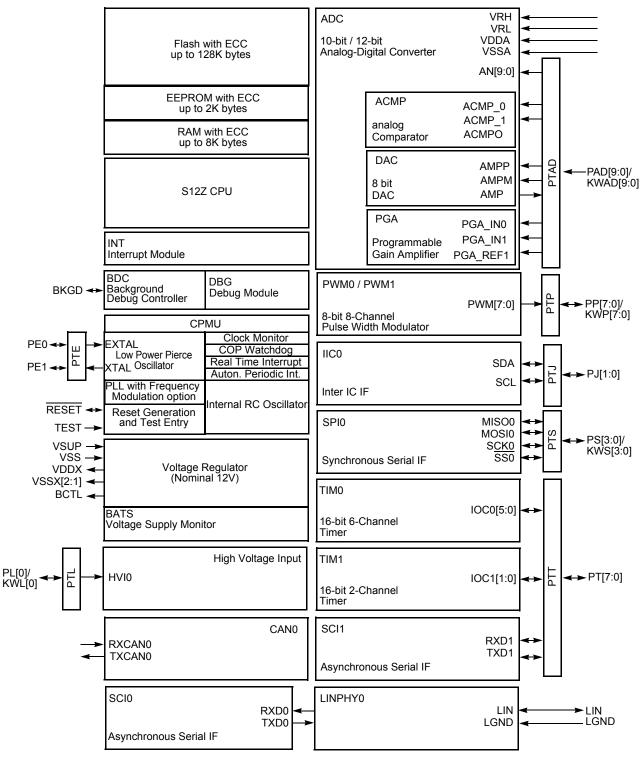

### 1.5 Block Diagram

Block Diagram shows the maximum configuration Not all pins or all peripherals are available on all devices and packages. Rerouting options are not shown.

COP is stopped during Full Stop Mode and COP continues to operate after exit from Full Stop Mode. For this COP configuration (ACLK clock source, CSAD set) a latency time (please refer to CSAD bit description for details) occurs when entering or exiting (Full, Pseudo) Stop Mode. When bit CSAD is clear the ACLK clock source is on for the COP during Full Stop Mode and COP is operating.

During Full Stop Mode the RTI counter halts.

After wake-up from Full Stop Mode the Core Clock and Bus Clock are running on PLLCLK (PLLSEL=1). The COP runs on ACLK and RTI is running on IRCCLK (COPOSCSEL0=0, RTIOSCSEL=0).

### • Pseudo Stop Mode (PSTP = 1 and OSCE=1)

External oscillator (XOSCLCP) continues to run.

— If COPOSCSEL1=0:

If the respective enable bits are set (PCE=1 and PRE=1) the COP and RTI will continue to run with a clock derived from the oscillator clock.

The clock configuration bits PLLSEL, COPOSCSEL0, RTIOSCSEL are unchanged.

— If COPOSCSEL1=1:

If the respective enable bit for the RTI is set (PRE=1) the RTI will continue to run with a clock derived from the oscillator clock.

The clock for the COP is derived from ACLK (trimmable internal RC-Oscillator clock). During Pseudo Stop Mode the ACLK for the COP can be stopped (COP static) or running (COP active) depending on the setting of bit CSAD. When bit CSAD is set the ACLK for the COP is stopped during Pseudo Stop Mode and COP continues to operate after exit from Pseudo Stop Mode. For this COP configuration (ACLK clock source, CSAD set) a latency time (please refer to CSAD bit description for details) occurs when entering or exiting (Pseudo, Full) Stop Mode. When bit CSAD is clear the ACLK clock source is on for the COP during Pseudo Stop Mode and COP is operating.

The clock configuration bits PLLSEL, COPOSCSEL0, RTIOSCSEL are unchanged.

### NOTE

When starting up the external oscillator (either by programming OSCE bit to 1 or on exit from Full Stop Mode with OSCE bit already 1) the software must wait for a minimum time equivalent to the startup-time of the external oscillator  $t_{UPOSC}$  before entering Pseudo Stop Mode.

### 9.1.2.4 Freeze Mode (BDM active)

For S12CPMU\_UHV Freeze Mode is the same as Run Mode except for RTI and COP which can be frozen in Active BDM Mode with the RSBCK bit in the CPMUCOP register. After exiting BDM Mode RTI and COP will resume its operations starting from this frozen status.

Additionally the COP can be forced to the maximum time-out period in Active BDM Mode. For details please see also the RSBCK and CR[2:0] bit description field of Table 9-14 in Section 9.3.2.12, "S12CPMU\_UHV COP Control Register (CPMUCOP)

This supply domain is monitored by the Low Voltage Reset circuit.

VDDX has to be connected externally to VDDA.

### 9.2.6 BCTL — Base Control Pin for external PNP

BCTL is the ballast connection for the on chip voltage regulator. It provides the base current of an external

BJT (PNP) of the VDDX and VDDA supplies. An additional  $1K\Omega$  resistor between emitter and base of the BJT is required. See the device specification if this pin is available on this device.

### 9.2.7 VSS — Core Logic Ground Pin

VSS is the core logic supply return pin. It must be grounded.

### 9.2.8 VDD — Internal Regulator Output Supply (Core Logic)

Node VDD is a device internal supply output of the voltage regulator that provides the power supply for the internal core logic.

This supply domain is monitored by the Low Voltage Reset circuit and The Power On Reset circuit.

### 9.2.9 VDDF — Internal Regulator Output Supply (NVM Logic)

Node VDDF is a device internal supply output of the voltage regulator that provides the power supply for the NVM logic.

This supply domain is monitored by the Low Voltage Reset circuit.

### 9.2.10 API\_EXTCLK — API external clock output pin

This pin provides the signal selected via APIES and is enabled with APIEA bit. See the device specification if this clock output is available on this device and to which pin it might be connected.

### 9.2.11 **TEMPSENSE** — Internal Temperature Sensor Output Voltage

Depending on the VSEL setting either the voltage level generated by the temperature sensor or the VREG bandgap voltage is driven to a special channel input of the ADC Converter. See device level specification for connectivity of ADC special channels.

S12 Clock, Reset and Power Management Unit (S12CPMU\_UHV)

### 9.3.2 Register Descriptions

This section describes all the S12CPMU\_UHV registers and their individual bits.

Address order is as listed in Figure 9-3

### 9.3.2.1 Reserved Register CPMUVREGTRIM0

### NOTE

This reserved register is designed for factory test purposes only, and is not intended for general user access. Writing to this register when in Special Mode can alter the S12CPMU\_UHV's functionality.

Module Base + 0x0001

|                   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------------|---|---|---|---|---|---|---|---|

| R                 | 0 | 0 | 0 | 0 |   | 1 | 1 |   |

| w                 |   |   |   |   |   | Ĺ | ) |   |

| Reset             | 0 | 0 | 0 | 0 | F | F | F | F |

| Power<br>on Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Note: After de-assert of System Reset a value is automatically loaded from the Flash memory.

Figure 9-4. Reserved Register (CPMUVREGTRIM0)

Read: Anytime

Write: Only in Special Mode

### 9.3.2.2 Reserved Register CPMUVREGTRIM1

#### NOTE

This reserved register is designed for factory test purposes only, and is not intended for general user access. Writing to this register when in Special Mode can alter the S12CPMU\_UHV's functionality.

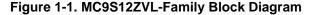

### 9.3.2.25 S12CPMU\_UHV Protection Register (CPMUPROT)

This register protects the following important configuration registers from accidental overwrite:

# CPMUSYNR, CPMUREFDIV, CPMUCLKS, CPMUPLL, CPMUIRCTRIMH/L, CPMUOSC and CPMUOSC2

Module Base + 0x001B

Figure 9-34. S12CPMU\_UHV Protection Register (CPMUPROT)

Read: Anytime

Write: Anytime

| Field | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PROT  | <ul> <li>Clock Configuration Registers Protection Bit — This bit protects the clock and voltage regulator configuration registers from accidental overwrite (see list of protected registers above): Writing 0x26 to the CPMUPROT register clears the PROT bit, other write accesses set the PROT bit.</li> <li>Protection of clock and voltage regulator configuration registers is disabled.</li> <li>Protection of clock and voltage regulator configuration registers is enabled. (see list of protected registers above).</li> </ul> |

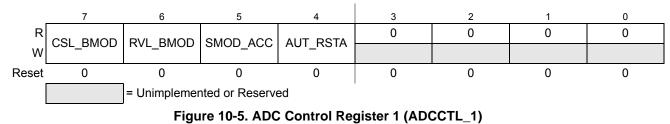

### 10.5.2.2 ADC Control Register 1 (ADCCTL\_1)

Module Base + 0x0001

Read: Anytime

Write:

- Bit CSL\_BMOD and RVL\_BMOD writable if bit ADC\_EN clear or bit SMOD\_ACC set

- Bit SMOD\_ACC only writable in MCU Special Mode

- Bit AUT\_RSTA writable anytime

#### Table 10-5. ADCCTL\_1 Field Descriptions

| Field         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CSL_BMOD | <ul> <li>CSL Buffer Mode Select Bit — This bit defines the CSL buffer mode. This bit is only writable if ADC_EN is clear.</li> <li>0 CSL single buffer mode.</li> <li>1 CSL double buffer mode.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6<br>RVL_BMOD | <ul> <li>RVL Buffer Mode Select Bit — This bit defines the RVL buffer mode.</li> <li>0 RVL single buffer mode</li> <li>1 RVL double buffer mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5<br>SMOD_ACC | <ul> <li>Special Mode Access Control Bit — This bit controls register access rights in MCU Special Mode. This bit is automatically cleared when leaving MCU Special Mode.</li> <li>Note: When this bit is set also the ADCCMD register is writeable via the data bus to allow modification of the current command for debugging purpose. But this is only possible if the current command is not already processed (conversion not started).</li> <li>Please see access details given for each register.</li> <li>Care must be taken when modifying ADC registers while bit SMOD_ACC is set to not corrupt a possible ongoing conversion.</li> <li>0 Normal user access - Register write restrictions exist as specified for each bit.</li> <li>1 Special access - Register write restrictions are lifted.</li> </ul> |

| 4<br>AUT_RSTA | <ul> <li>Automatic Restart Event after exit from MCU Stop and Wait Mode (SWAI set) — This bit controls if a Restart Event is automatically generated after exit from MCU Stop Mode or Wait Mode with bit SWAI set. It can be configured for ADC conversion flow control mode "Trigger Mode" and "Restart Mode" (anytime during application runtime).</li> <li>0 No automatic Restart Event after exit from MCU Stop Mode.</li> <li>1 Automatic Restart Event occurs after exit from MCU Stop Mode.</li> </ul>                                                                                                                                                                                                                                                                                                         |

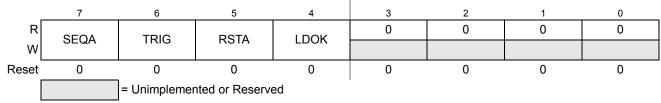

### 10.5.2.6 ADC Conversion Flow Control Register (ADCFLWCTL)

Bit set and bit clear instructions should not be used to access this register.

When the ADC is enabled the bits of ADCFLWCTL register can be modified after a latency time of three Bus Clock cycles.

All bits are cleared if bit ADC\_EN is clear or via ADC soft-reset.

Module Base + 0x0005

#### Figure 10-9. ADC Conversion Flow Control Register (ADCFLWCTL)

Read: Anytime

Write:

- Bits SEQA, TRIG, RSTA, LDOK can only be set if bit ADC\_EN is set.

- Writing 1'b0 to any of these bits does not have an effect

Timing considerations (Trigger Event - channel sample start) depending on ADC mode configuration:

• Restart Mode

When the Restart Event has been processed (initial command of current CSL is loaded) it takes two Bus Clock cycles plus two ADC conversion clock cycles (pump phase) from the Trigger Event (bit TRIG set) until the select channel starts to sample.

During a conversion sequence (back to back conversions) it takes five Bus Clock cycles plus two ADC conversion clock cycles (pump phase) from current conversion period end until the newly selected channel is sampled in the following conversion period.

• Trigger Mode

When a Restart Event occurs a Trigger Event is issued simultaneously. The time required to process the Restart Event is mainly defined by the internal read data bus availability and therefore can vary. In this mode the Trigger Event is processed immediately after the Restart Event is finished and both conversion flow control bits are cleared simultaneously. From de-assert of bit TRIG until sampling begins five Bus Clock cycles are required. Hence from occurrence of a Restart Event until channel sampling it takes five Bus Clock cycles plus an uncertainty of a few Bus Clock cycles.

For more details regarding the sample phase please refer to Section 10.6.2.2, "Sample and Hold Machine with Sample Buffer Amplifier.

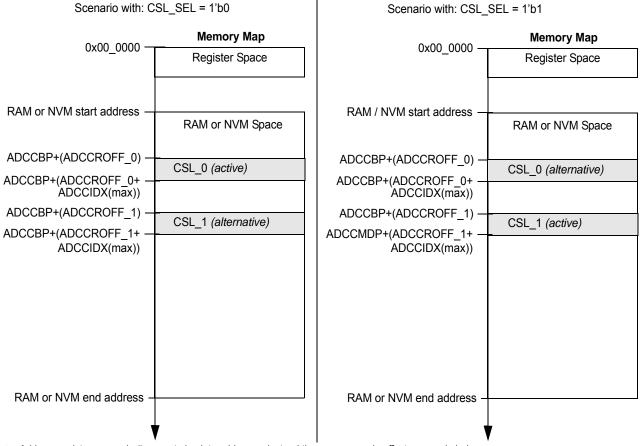

### 10.6.3.2.2 Introduction of the two Command Sequence Lists (CSLs)

The two Command Sequence Lists (CSLs) can be referred to via the Command Base Pointer Register plus the Command and Result Offset Registers plus the Command Index Register (ADCCBP, ADCCROFF\_0/1, ADCCIDX).

The final address for conversion command loading is calculated by the sum of these registers (e.g.: ADCCBP+ADCCROFF\_0+ADCCIDX or ADCCBP+ADCCROFF\_1+ADCCIDX).

Bit CSL\_BMOD selects if the CSL is used in double buffer or single buffer mode. In double buffer mode, the CSL can be swapped by flow control bits LDOK and RSTA. For detailed information about when and how the CSL is swapped, please refer to Section 10.6.3.2.5, "The four ADC conversion flow control bits - description of Restart Event + CSL Swap, Section 10.9.7.1, "Initial Start of a Command Sequence List and Section 10.9.7.3, "Restart CSL execution with new/other CSL (alternative CSL becomes active CSL) -- CSL swapping

Which list is actively used for ADC command loading is indicated by bit CSL\_SEL. The register to define the CSL start addresses (ADCCBP) can be set to any even location of the system RAM or NVM area. It is the user's responsibility to make sure that the different ADC lists do not overlap or exceed the system RAM or the NVM area, respectively. The error flag IA\_EIF will be set for accesses to ranges outside system RAM area and cause an error interrupt if enabled.

Note: Address register names in () are not absolute addresses instead they are a sample offset or sample index

#### Figure 10-31. Command Sequence List Schema in Double Buffer Mode

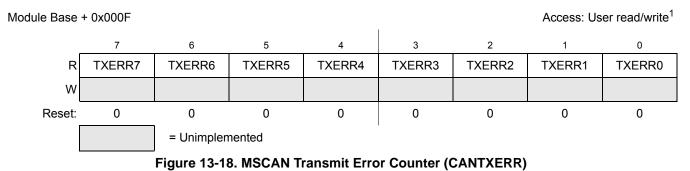

### 13.3.2.15 MSCAN Transmit Error Counter (CANTXERR)

This register reflects the status of the MSCAN transmit error counter.

Read: Only when in sleep mode (SLPRQ = 1 and SLPAK = 1) or initialization mode (INITRQ = 1 and INITAK = 1) Write: Unimplemented

#### NOTE

Reading this register when in any other mode other than sleep or initialization mode, may return an incorrect value. For MCUs with dual CPUs, this may result in a CPU fault condition.

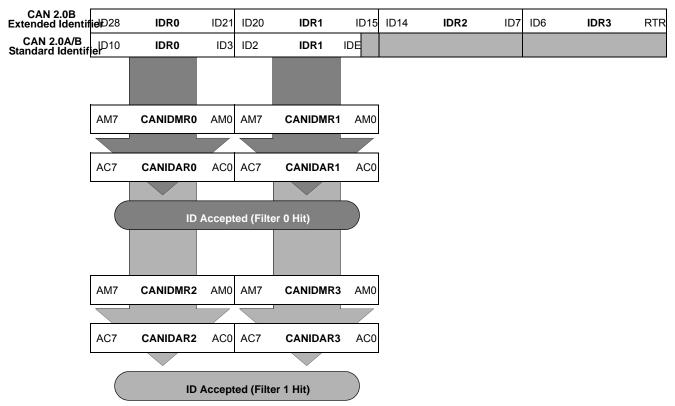

### 13.3.2.16 MSCAN Identifier Acceptance Registers (CANIDAR0-7)

On reception, each message is written into the background receive buffer. The CPU is only signalled to read the message if it passes the criteria in the identifier acceptance and identifier mask registers (accepted); otherwise, the message is overwritten by the next message (dropped).

The acceptance registers of the MSCAN are applied on the IDR0–IDR3 registers (see Section 13.3.3.1, "Identifier Registers (IDR0–IDR3)") of incoming messages in a bit by bit manner (see Section 13.4.3, "Identifier Acceptance Filter").

For extended identifiers, all four acceptance and mask registers are applied. For standard identifiers, only the first two (CANIDAR0/1, CANIDMR0/1) are applied.

Module Base + 0x0010 to Module Base + 0x0013

Access: User read/write<sup>1</sup>

|        | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| R<br>W | AC7 | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

#### Figure 13-19. MSCAN Identifier Acceptance Registers (First Bank) — CANIDAR0–CANIDAR3

<sup>1</sup> Read: Anytime

Write: Anytime in initialization mode (INITRQ = 1 and INITAK = 1)

#### Scalable Controller Area Network (S12MSCANV2)

#### Figure 13-40. 16-bit Maskable Identifier Acceptance Filters

#### Supply Voltage Sensor (BATSV3)

The comparator outputs BVLC and BVHC are forced to zero if the comparator is disabled (configuration bit BSUSE is cleared). If the software disables the comparator during a high or low Voltage condition (BVHC or BVLC active), then an additional interrupt is generated. To avoid this behavior the software must disable the interrupt generation before disabling the comparator.

The BATS interrupt vector is named in Table 14-6. Vector addresses and interrupt priorities are defined at MCU level.

The module internal interrupt sources are combined into one module interrupt signal.

Table 14-6. BATSV3 Interrupt Sources

| Module Interrupt Source | Module Internal Interrupt Source             | Local Enable |

|-------------------------|----------------------------------------------|--------------|

| BATSV3 Interrupt (BATI) | BATS Voltage Low Condition Interrupt (BVLI)  | BVLIE = 1    |

|                         | BATS Voltage High Condition Interrupt (BVHI) | BVHIE = 1    |

### 14.4.2.1 BATS Voltage Low Condition Interrupt (BVLI)

To use the Voltage Low Interrupt the Level Sensing must be enabled (BSUSE =1).

If measured when

a)  $V_{LBI1}$  selected with BVLS[1:0] = 0x0

$V_{measure} < V_{LBI1_A}$  (falling edge) or  $V_{measure} < V_{LBI1_D}$  (rising edge)

or when

b) V<sub>LBI2</sub> selected with BVLS[1:0] = 0x1 at pin VSUP

V<sub>measure</sub> < V<sub>LBI2</sub> A (falling edge) or V<sub>measure</sub> < V<sub>LBI2</sub> D (rising edge)

or when

c) V<sub>LBI3</sub> selected with BVLS[1:0] = 0x2 V<sub>measure</sub> < V<sub>LBI3\_A</sub> (falling edge) or V<sub>measure</sub> < V<sub>LBI3\_D</sub> (rising edge)

or when

d) V<sub>LBI4</sub> selected with BVLS[1:0] = 0x3

V<sub>measure</sub> < V<sub>LBI4\_A</sub> (falling edge) or V<sub>measure</sub> < V<sub>LBI4\_D</sub> (rising edge)

then BVLC is set. BVLC status bit indicates that a low voltage at pin VSUP is present. The Low Voltage Interrupt flag (BVLIF) is set to 1 when the Voltage Low Condition (BVLC) changes state. The Interrupt flag BVLIF can only be cleared by writing a 1. If the interrupt is enabled by bit BVLIE the module requests an interrupt to MCU (BATI).

### 14.4.2.2 BATS Voltage High Condition Interrupt (BVHI)

To use the Voltage High Interrupt the Level Sensing must be enabled (BSUSE=1).

#### Pulse-Width Modulator (S12PWM8B8CV2)

Clock A and B can be software selected to be 1, 1/2, 1/4, 1/8,..., 1/64, 1/128 times the bus clock. Clock SA uses clock A as an input and divides it further with a reloadable counter. Similarly, clock SB uses clock B as an input and divides it further with a reloadable counter. The rates available for clock SA are software selectable to be clock A divided by 2, 4, 6, 8,..., or 512 in increments of divide by 2. Similar rates are available for clock SB. Each PWM channel has the capability of selecting one of four clocks, clock A, Clock B, clock SB.

The block diagram in Figure 17-15 shows the four different clocks and how the scaled clocks are created.

### 17.4.1.1 Prescale

The input clock to the PWM prescaler is the bus clock. It can be disabled whenever the part is in freeze mode by setting the PFRZ bit in the PWMCTL register. If this bit is set, whenever the MCU is in freeze mode (freeze mode signal active) the input clock to the prescaler is disabled. This is useful for emulation in order to freeze the PWM. The input clock can also be disabled when all available PWM channels are disabled (PWMEx-0 = 0). This is useful for reducing power by disabling the prescale counter.

Clock A and clock B are scaled values of the input clock. The value is software selectable for both clock A and clock B and has options of 1, 1/2, 1/4, 1/8, 1/16, 1/32, 1/64, or 1/128 times the bus clock. The value selected for clock A is determined by the PCKA2, PCKA1, PCKA0 bits in the PWMPRCLK register. The value selected for clock B is determined by the PCKB2, PCKB1, PCKB0 bits also in the PWMPRCLK register.

### 17.4.1.2 Clock Scale

The scaled A clock uses clock A as an input and divides it further with a user programmable value and then divides this by 2. The scaled B clock uses clock B as an input and divides it further with a user programmable value and then divides this by 2. The rates available for clock SA are software selectable to be clock A divided by 2, 4, 6, 8,..., or 512 in increments of divide by 2. Similar rates are available for clock SB.

| Table 18-8 | . IRSCI | Transmit | Pulse  | Width    |

|------------|---------|----------|--------|----------|

|            |         | manomit  | 1 4100 | <b>T</b> |

| TNP[1:0] | Narrow Pulse Width |

|----------|--------------------|

| 00       | 3/16               |

#### Table 18-9. Bit Error Mode Coding

| BERRM1 | BERRM0 | Function                                                                                             |

|--------|--------|------------------------------------------------------------------------------------------------------|

| 0      | 0      | Bit error detect circuit is disabled                                                                 |

| 0      | 1      | Receive input sampling occurs during the 9th time tick of a transmitted bit (refer to Figure 18-19)  |

| 1      | 0      | Receive input sampling occurs during the 13th time tick of a transmitted bit (refer to Figure 18-19) |

| 1      | 1      | Reserved                                                                                             |

### 18.3.2.6 SCI Control Register 2 (SCICR2)

Module Base + 0x0003

|        | 7   | 6    | 5   | 4    | 3  | 2  | 1   | 0   |

|--------|-----|------|-----|------|----|----|-----|-----|

| R<br>W | TIE | TCIE | RIE | ILIE | TE | RE | RWU | SBK |

| Reset  | 0   | 0    | 0   | 0    | 0  | 0  | 0   | 0   |

Figure 18-9. SCI Control Register 2 (SCICR2)

Read: Anytime

Write: Anytime

#### Table 18-10. SCICR2 Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                         |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TIE  | Transmitter Interrupt Enable Bit — TIE enables the transmit data register empty flag, TDRE, to generate interrupt requests.         0       TDRE interrupt requests disabled         1       TDRE interrupt requests enabled                                        |

| 6<br>TCIE | Transmission Complete Interrupt Enable Bit — TCIE enables the transmission complete flag, TC, to generate interrupt requests.         0       TC interrupt requests disabled         1       TC interrupt requests enabled                                          |

| 5<br>RIE  | Receiver Full Interrupt Enable Bit — RIE enables the receive data register full flag, RDRF, or the overrun flag, OR, to generate interrupt requests.         0       RDRF and OR interrupt requests disabled         1       RDRF and OR interrupt requests enabled |

| 4<br>ILIE | Idle Line Interrupt Enable Bit — ILIE enables the idle line flag, IDLE, to generate interrupt requests.         0       IDLE interrupt requests disabled         1       IDLE interrupt requests enabled                                                            |

#### **MCU Electrical Specifications**

# Appendix F BATS Electrical Specifications

This section describe the electrical characteristics of the Supply Voltage Sense module.Static Electrical Characteristics.

| Num | Ratings                                                                                                                                                                 | Symbol                                                                     | Min            | Тур              | Max              | Unit        |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------|------------------|------------------|-------------|

| 1   | Low Voltage Warning (LBI 1)                                                                                                                                             |                                                                            |                |                  |                  |             |

|     | Ratio = 9<br>Assert (Measured on selected pin, falling edge)<br>Deassert (Measured on selected pin, rising edge)<br>Hysteresis (measured on selected pin)               | V <sub>LBI1_A_9</sub><br>V <sub>LBI1_D_9</sub><br>V <sub>LBI1_H_9</sub>    | 4.75<br>_<br>_ | 5.5<br>_<br>0.4  | 6<br>6.5<br>–    | V<br>V<br>V |

|     | Ratio = 17 <sup>2</sup><br>Assert (Measured on selected pin, falling edge)<br>Deassert (Measured on selected pin, rising edge)<br>Hysteresis (measured on selected pin) | V <sub>lbi1_A_17</sub><br>V <sub>lbi1_D_17</sub><br>V <sub>lbi1_H_17</sub> | 5.0<br>_<br>_  | 5.5<br>-<br>1.0  | 6.5<br>7.5<br>–  | V<br>V<br>V |

| 2   | Low Voltage Warning (LBI 2)                                                                                                                                             |                                                                            |                |                  |                  |             |

|     | Ratio = 9<br>Assert (Measured on selected pin, falling edge) on<br>S12ZVL(S)32/16/8<br>Assert (Measured on selected pin, falling edge) on                               | V <sub>LBI2_A_9</sub><br>V <sub>LBI2 A 9</sub>                             | 5.75<br>5.5    | 6.75<br>6.75     | 7.25<br>7.25     | V<br>V<br>V |

|     | S12ZVL(A)128/96/64<br>Deassert (Measured on selected pin, rising edge)<br>Hysteresis (measured on selected pin)                                                         | V <sub>LBI2_D_9</sub><br>V <sub>LBI2_H_9</sub>                             |                | _<br>0.4         | 7.75<br>-        | V           |

|     | Ratio = 17 <sup>2</sup><br>Assert (Measured on selected pin, falling edge)<br>Deassert (Measured on selected pin, rising edge)<br>Hysteresis (measured on selected pin) | V <sub>LBI2_A_17</sub><br>V <sub>LBI2_D_17</sub><br>V <sub>LBI2_H_17</sub> | 6.5<br>_<br>_  | 7.5<br>_<br>1.0  | 9.0<br>10.0<br>- | V<br>V      |

| 3   | Low Voltage Warning (LBI 3)                                                                                                                                             |                                                                            |                |                  |                  |             |

|     | Ratio = 9<br>Assert (Measured on selected pin, falling edge)<br>Deassert (Measured on selected pin, rising edge)<br>Hysteresis (measured on selected pin)               | V <sub>lbi3_A_9</sub><br>V <sub>lbi3_D_9</sub><br>V <sub>lbi3_H_9</sub>    | 7<br><br>-     | 7.75<br>_<br>0.4 | 8.5<br>9<br>–    | V<br>V<br>V |

|     | Ratio = 17 <sup>2</sup><br>Assert (Measured on selected pin, falling edge)<br>Deassert (Measured on selected pin, rising edge)<br>Hysteresis (measured on selected pin) | V <sub>LBI3_A_17</sub><br>V <sub>LBI3_D_17</sub><br>V <sub>LBI3_H_17</sub> | 6.5<br>_<br>_  | 7.5<br>-<br>1.0  | 8.5<br>9.5<br>—  | V<br>V<br>V |

#### Table F-1. Static Electrical Characteristics - Supply Voltage Sense - (BATS)

**Detailed Register Address Map**

### O.8 0x0400-0x042F TIM1

| Address           | Name      |        | Bit 7        | 6            | 5            | 4            | 3            | 2            | 1            | Bit 0        |

|-------------------|-----------|--------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| 0x0400            | TIM1TIOS  | R<br>W | RESERVE<br>D | RESERVE<br>D | RESERVE<br>D | RESERVE<br>D | RESERVE<br>D | RESERVE<br>D | IOS1         | IOS0         |

| 0x0401            | TIM1CFORC | R<br>W | RESERVE<br>D | RESERVE<br>D | RESERVE<br>D | RESERVE<br>D | RESERVE<br>D | RESERVE<br>D | FOC1         | FOC0         |

| 0x0402-<br>0x0403 | Reserved  | R<br>W |              |              |              |              |              |              |              |              |

| 0x0404            | TIM1TCNTH | R<br>W | TCNT15       | TCNT14       | TCNT13       | TCNT12       | TCNT11       | TCNT10       | TCNT9        | TCNT8        |

| 0x0405            | TIM1TCNTL | R<br>W | TCNT7        | TCNT6        | TCNT5        | TCNT4        | TCNT3        | TCNT2        | TCNT1        | TCNT0        |

| 0x0406            | TIM1TSCR1 | R<br>W | TEN          | TSWAI        | TSFRZ        | TFFCA        | PRNT         | 0            | 0            | 0            |

| 0x0047            | TIM1TTOV  | R<br>W | RESERVE<br>D | RESERVE<br>D | RESERVE<br>D | RESERVE<br>D | RESERVE<br>D | RESERVE<br>D | TOV1         | TOV0         |

| 0x0408            | TIM1TCTL1 | R<br>W | RESERVE<br>D |

| 0x0409            | TIM1TCTL2 | R<br>W | RESERVE<br>D | RESERVE<br>D | OM2          | OL2          | OM1          | OL1          | OM0          | OL0          |

| 0x040A            | TIM1TCTL3 | R<br>W | RESERVE<br>D |

| 0x040B            | TIM1TCTL4 | R<br>W | RESERVE<br>D | RESERVE<br>D | RESERVE<br>D | RESERVE<br>D | EDG1B        | EDG1A        | EDG0B        | EDG0A        |

| 0x040C            | TIM1TIE   | R<br>W | RESERVE<br>D | RESERVE<br>D | RESERVE<br>D | RESERVE<br>D | RESERVE<br>D | RESERVE<br>D | C1I          | COI          |

| 0x040D            | TIM1TSCR2 | R<br>W | TOI          | 0            | 0            | 0            | RESERVE<br>D | PR2          | PR1          | PR0          |

| 0x040E            | TIM1TFLG1 | R<br>W | RESERVE<br>D | RESERVE<br>D | RESERVE<br>D | RESERVE<br>D | RESERVE<br>D | RESERVE<br>D | C1F          | C0F          |

| 0x040F            | TIM1TFLG2 | R<br>W | TOF          | 0            | 0            | 0            | 0            | 0            | 0            | 0            |

| 0x0400            | TIM1TC0H  | R<br>W | Bit 15       | Bit 14       | Bit 13       | Bit 12       | Bit 11       | Bit 10       | Bit 9        | Bit 8        |

| 0x0411            | TIM1TC0L  | R<br>W | Bit 7        | Bit 6        | Bit 5        | Bit 4        | Bit 3        | Bit 2        | Bit 1        | Bit 0        |

| 0x0412            | TIM1TC1H  | R<br>W | Bit 15       | Bit 14       | Bit 13       | Bit 12       | Bit 11       | Bit 10       | Bit 9        | Bit 8        |

# O.9 0x0480-x04AF PWM0 (continued)

| Address  | Name     |             | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

|----------|----------|-------------|-------|---|---|---|---|---|---|-------|

| 0x048A - | RESERVED | R           | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0     |

| 0x048B   | N N      |             |       |   |   |   |   |   |   |       |

| 0x048C   | PWMCNT0  | R           | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

|          |          | W           | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0     |

| 0x048D   | PWMCNT1  | R           | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

| 0.00.002 |          | W           | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0     |

| 0x048E   | PWMCNT2  | R           | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

| 0.00101  |          | W           | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0     |

| 0x048F   | PWMCNT3  | R           | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

|          |          | W           | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0     |

| 0x0490   | PWMCNT4  | R           | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

|          |          | W           | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0     |

| 0x0491   | PWMCNT5  | R           | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

|          |          | W           | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0     |

| 0x0492   | PWMCNT6  | R<br>R      | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

| 0.00.102 |          | W           | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0     |

| 0x0493   | PWMCNT7  | R<br>NMCNT7 | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

|          |          | W           | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0     |

| 0x0494   | PWMPER0  | R<br>W      | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

| 0x0495   | PWMPER1  | R<br>W      | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

| 0x0496   | PWMPER2  | R<br>W      | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

| 0x0497   | PWMPER3  | R<br>W      | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

| 0x0498   | PWMPER4  | R<br>W      | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

| 0x0499   | PWMPER5  | R<br>W      | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

| 0x049A   | PWMPER6  | R<br>W      | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

| 0x049B   | PWMPER7  | R<br>W      | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

## O.15 0x06C0-0x06DF CPMU (continued)

| Address | Name                  |        | Bit 7      | 6            | 5                | 4          | 3            | 2          | 1          | Bit 0      |

|---------|-----------------------|--------|------------|--------------|------------------|------------|--------------|------------|------------|------------|

| 0x06CC  | CPMUCOP               | R<br>W | WCOP       | RSBCK        | 0<br>WRTMAS<br>K | 0          | 0            | CR2        | CR1        | CR0        |

| 0x06CD  | RESERVED<br>CPMUTEST0 | R<br>W | 0          | 0            | 0                | 0          | 0            | 0          | 0          | 0          |

| 0x06CE  | RESERVED<br>CPMUTEST1 | R<br>W | 0          | 0            | 0                | 0          | 0            | 0          | 0          | 0          |

| 0x06CF  | CPMU<br>ARMCOP        | R<br>W | 0<br>Bit 7 | 0<br>Bit 6   | 0<br>Bit 5       | 0<br>Bit 4 | 0<br>Bit 3   | 0<br>Bit 2 | 0<br>Bit 1 | 0<br>Bit 0 |

| 0x06D0  | CPMU<br>HTCTL         | R<br>W | 0          | 0            | VSEL             | 0          | HTE          | HTDS       | HTIE       | HTIF       |

| 0x06D1  | CPMU<br>LVCTL         | R<br>W | 0          | 0            | 0                | 0          | 0            | LVDS       | LVIE       | LVIF       |

| 0x06D2  | CPMU<br>APICTL        | R<br>W | APICLK     | 0            | 0                | APIES      | APIEA        | APIFE      | APIE       | APIF       |

| 0x06D3  | CPMUACLKT<br>R        | R<br>W | ACLKTR5    | ACLKTR4      | ACLKTR3          | ACLKTR2    | ACLKTR1      | ACLKTR0    | 0          | 0          |

| 0x06D4  | CPMUAPIRH             | R<br>W | APIR15     | APIR14       | APIR13           | APIR12     | APIR11       | APIR10     | APIR9      | APIR8      |

| 0x06D5  | CPMUAPIRL             | R<br>W | APIR7      | APIR6        | APIR5            | APIR4      | APIR3        | APIR2      | APIR1      | APIR0      |

| 0x06D6  | RESERVED<br>CPMUTEST3 | R<br>W | 0          | 0            | 0                | 0          | 0            | 0          | 0          | 0          |

| 0x06D7  | CPMUHTTR              | R<br>W | HTOE       | 0            | 0                | 0          | HTTR3        | HTTR2      | HTTR1      | HTTR0      |

| 0x06D8  | CPMU<br>IRCTRIMH      | R<br>W |            | -            | TCTRIM[4:0       | 0          | IRCTRIM[9:8] |            |            |            |

| 0x06D9  | CPMU<br>IRCTRIML      | R<br>W |            | IRCTRIM[7:0] |                  |            |              |            |            |            |

| 0x06DA  | CPMUOSC               | R<br>W | OSCE       | Reserved     | Reserved         | Reserved   |              |            |            |            |

| 0x06DB  | CPMUPROT              | R<br>W | 0          | 0            | 0                | 0          | 0            | 0          | 0          | PROT       |

| 0x06DC  | RESERVED<br>CPMUTEST2 | R<br>W | 0          | 0            | 0                | 0          | 0            | 0          | 0          | 0          |

# O.17 0x0700-0x0707 SCI0 (continued)

| Address | Name    |   | Bit 7 | 6  | 5  | 4  | 3  | 2  | 1  | Bit 0 |

|---------|---------|---|-------|----|----|----|----|----|----|-------|

| 0x0706  | SCI0DRH | R | R R8  | Т8 | 0  | 0  | 0  | 0  | 0  | 0     |

|         |         | W |       |    |    |    |    |    |    |       |

|         |         | R | R7    | R6 | R5 | R4 | R3 | R2 | R1 | R0    |

| 0x0707  | SCI0DRL | W | T7    | T6 | T5 | T4 | Т3 | T2 | T1 | Т0    |

1 These registers are accessible if the AMAP bit in the SCISR2 register is set to zero.

2 These registers are accessible if the AMAP bit in the SCISR2 register is set to one.

### O.18 0x0710-0x0717 SCI1

| Address | Name                  |        | Bit 7   | 6       | 5     | 4     | 3     | 2      | 1      | Bit 0 |

|---------|-----------------------|--------|---------|---------|-------|-------|-------|--------|--------|-------|

| 0x0710  | SCI1BDH <sup>1</sup>  | R<br>W | SBR15   | SBR14   | SBR13 | SBR12 | SBR11 | SBR10  | SBR9   | SBR8  |

| 0x0711  | SCI1BDL <sup>1</sup>  | R<br>W | SBR7    | SBR6    | SBR5  | SBR4  | SBR3  | SBR2   | SBR1   | SBR0  |

| 0x0712  | SCI1CR1 <sup>1</sup>  | R<br>W | LOOPS   | SCISWAI | RSRC  | Μ     | WAKE  | ILT    | PE     | PT    |

| 0x0710  | SCI1ASR1 <sup>2</sup> | R<br>W | RXEDGIF | 0       | 0     | 0     | 0     | BERRV  | BERRIF | BKDIF |

| 0x0711  | SCI1ACR1 <sup>2</sup> | R<br>W | RXEDGIE | 0       | 0     | 0     | 0     | 0      | BERRIE | BKDIE |

| 0x0712  | SCI1ACR2 <sup>2</sup> | R<br>W | IREN    | TNP1    | TNP0  | 0     | 0     | BERRM1 | BERRM0 | BKDFE |

| 0x0713  | SCI1CR2               | R<br>W | TIE     | TCIE    | RIE   | ILIE  | TE    | RE     | RWU    | SBK   |

| 0x0714  | SCI1SR1               | R      | TDRE    | TC      | RDRF  | IDLE  | OR    | NF     | FE     | PF    |

|         |                       | W      |         |         |       |       |       |        |        |       |

| 0x0715  | SCI1SR2               | R      | AMAP    | 0       | 0     | TXPOL | RXPOL | BRK13  | TXDIR  | RAF   |

|         |                       | W      |         |         |       |       |       |        |        |       |

| 0x0716  | SCI1DRH               | R      | R8      | Т8      | 0     | 0     | 0     | 0      | 0      | 0     |

|         | 20                    | W      |         |         |       |       |       |        |        |       |

| 0x0717  | SCI1DRL               | R      | R7      | R6      | R5    | R4    | R3    | R2     | R1     | R0    |

| 0x0717  |                       | W      | T7      | T6      | T5    | T4    | Т3    | T2     | T1     | Т0    |

1 These registers are accessible if the AMAP bit in the SCISR2 register is set to zero.

2 These registers are accessible if the AMAP bit in the SCISR2 register is set to one.