#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | S12Z                                                                    |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 32MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SCI, SPI, UART/USART            |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 19                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 512 x 8                                                                 |

| RAM Size                   | 1K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 5.5V ~ 18V                                                              |

| Data Converters            | A/D 6x10b; D/A 1x8b                                                     |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 32-LQFP                                                                 |

| Supplier Device Package    | 32-LQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s912zvla12f0mlc |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|      | 18.4.3 Data Format                     |  |

|------|----------------------------------------|--|

|      | 18.4.4 Baud Rate Generation            |  |

|      | 18.4.5 Transmitter                     |  |

|      | 18.4.6 Receiver                        |  |

|      | 18.4.7 Single-Wire Operation           |  |

|      | 18.4.8 Loop Operation                  |  |

| 18.5 | Initialization/Application Information |  |

|      | 18.5.1 Reset Initialization            |  |

|      | 18.5.2 Modes of Operation              |  |

|      | 18.5.3 Interrupt Operation             |  |

|      | 18.5.4 Recovery from Wait Mode         |  |

|      | 18.5.5 Recovery from Stop Mode         |  |

# Chapter 19 Serial Peripheral Interface (S12SPIV5)

| 19.1 | Introduc | ction                              | 543 |

|------|----------|------------------------------------|-----|

|      | 19.1.1   | Glossary of Terms                  | 543 |

|      | 19.1.2   | Features                           | 543 |

|      | 19.1.3   | Modes of Operation                 | 543 |

|      | 19.1.4   | Block Diagram                      | 544 |

| 19.2 | External | l Signal Description               | 545 |

|      | 19.2.1   | MOSI — Master Out/Slave In Pin     | 545 |

|      | 19.2.2   | MISO — Master In/Slave Out Pin     | 546 |

|      | 19.2.3   | $\overline{SS}$ — Slave Select Pin | 546 |

|      | 19.2.4   | SCK — Serial Clock Pin             | 546 |

| 19.3 | Memory   | y Map and Register Definition      | 546 |

|      | 19.3.1   | Module Memory Map                  | 546 |

|      | 19.3.2   | Register Descriptions              | 547 |

| 19.4 | Function | nal Description                    | 555 |

|      | 19.4.1   | Master Mode                        | 556 |

|      | 19.4.2   | Slave Mode                         | 557 |

|      | 19.4.3   | Transmission Formats               | 558 |

|      | 19.4.4   | SPI Baud Rate Generation           | 563 |

|      | 19.4.5   | Special Features                   | 564 |

|      | 19.4.6   | Error Conditions                   | 565 |

|      | 19.4.7   | Low Power Mode Options             | 566 |

# Chapter 20

# Inter-Integrated Circuit (IICV3)

| 20.1 | Introduction                | 569 |

|------|-----------------------------|-----|

|      | 20.1.1 Features             | 569 |

|      | 20.1.2 Modes of Operation   | 570 |

|      | 20.1.3 Block Diagram        | 570 |

| 20.2 | External Signal Description | 570 |

- Broadcast mode support

- 10-bit address support

## 1.4.8 LIN physical layer transceiver

- Compliant with LIN Physical Layer 2.2 specification

- Compliant with the SAE J2602-2 LIN standard

- Standby mode with glitch-filtered wake-up

- Slew rate selection optimized for the baud rates: 10.4kBit/s, 20kBit/s and Fast Mode (up to 250kBit/s)

- Switchable  $34k\Omega/330k\Omega$  pull-ups

- Current limitation for LIN Bus pin falling edge

- Over-current protection

- LIN TxD-dominant timeout feature monitoring the LPTxD signal

- Automatic transmitter shutdown in case of an over-current or TxD-dominant timeout

- Fulfills the OEM "Hardware Requirements for LIN (CAN and FlexRay) Interfaces in Automotive Applications" v1.3

## **1.4.9** Serial Communication Interface Module (SCI)

- Full-duplex or single-wire operation

- Standard mark/space non-return-to-zero (NRZ) format

- Selectable IrDA 1.4 return-to-zero-inverted (RZI) format with programmable pulse widths

- Baud rate generator by a 16-bit divider from the bus clock

- Programmable character length

- Programmable polarity for transmitter and receiver

- Active edge receive wakeup

- Break detect and transmit collision detect supporting LIN

## 1.4.10 Serial Peripheral Interface Module (SPI)

- Configurable 8- or 16-bit data size

- Full-duplex or single-wire bidirectional

- Double-buffered transmit and receive

- Master or slave mode

- MSB-first or LSB-first shifting

- Serial clock phase and polarity options

## 1.4.11 Multi-Scalable Controller Area Network (MSCAN)

• Implementation of CAN protocol - Version 2.0A/B

| Field        | Description                                                                                                                                                                                                                                                                                     |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0 (ММСРСМ) | <b>S12ZCPU Program Counter Value</b> — The CPUPC[23:0] stores the CPU's program counter value at the time the access violation occurred. CPUPC[23:0] always points to the instruction which triggered the violation. These bits are undefined if the error code registers (MMCECn) are cleared. |

# 4.4 Functional Description

This section provides a complete functional description of the S12ZDBG module.

# 4.4.1 Global Memory Map

The S12ZDBG maps all on-chip resources into an 16MB address space, the global memory map. The exact resource mapping is shown in Figure 4-8. The global address space is used by the S12ZCPU, ADC, and the S12ZBDC module.

#### Memory Mapping Control (S12ZMMCV1)

• All illegal accesses performed by the ADC module trigger error interrupts. See ADC section for details.

### NOTE

Illegal accesses caused by S12ZCPU opcode prefetches will also trigger machine exceptions, even if those opcodes might not be executed in the program flow. To avoid these machine exceptions, S12ZCPU instructions must not be executed from the last (high addresses) 8 bytes of RAM, EEPROM, and Flash.

## 4.4.3 Uncorrectable ECC Faults

RAM and flash use error correction codes (ECC) to detect and correct memory corruption. Each uncorrectable memory corruption, which is detected during a S12ZCPU or ADC access triggers a machine exception. Uncorrectable memory corruptions which are detected during a S12ZBDC access, are captured in the RAMWF or the RDINV bit of the BDCCSRL register.

#### Background Debug Controller (S12ZBDCV2)

| 0x1B                      | Data[31-24]      | Data[23-16]               | Data[15-8]       | Data[7-0]        |             | BDCCSRL          |

|---------------------------|------------------|---------------------------|------------------|------------------|-------------|------------------|

| host $\rightarrow$ target | host →<br>target | host $\rightarrow$ target | host →<br>target | host →<br>target | D<br>L<br>Y | target →<br>host |

FILL\_MEM.sz\_WS

FILL\_MEM{\_WS} is used with the WRITE\_MEM{\_WS} command to access large blocks of memory. An initial WRITE\_MEM{\_WS} is executed to set up the starting address of the block and write the first datum. If an initial WRITE\_MEM{\_WS} is not executed before the first FILL\_MEM{\_WS}, an illegal command response is returned. The FILL\_MEM{\_WS} command stores subsequent operands. The initial address is incremented by the operand size (1, 2, or 4) and saved in a temporary register. Subsequent FILL\_MEM{\_WS} command size, and store the updated address in the temporary register. If the with-status option is specified, the BDCCSRL status byte is returned after the write data. This status byte reflects the state after the memory write was performed. If enabled an ACK pulse is generated after the internal write access has been completed or aborted. The effect of the access size and alignment on the next address to be accessed is explained in more detail in Section 5.4.5.2, "BDC Access Of Device Memory Mapped Resources"

### NOTE

FILL\_MEM{\_WS} is a valid command only when preceded by SYNC, NOP, WRITE\_MEM{\_WS}, or another FILL\_MEM{\_WS} command. Otherwise, an illegal command response is returned, setting the ILLCMD bit. NOP can be used for inter command padding without corrupting the address pointer.

The size field (sz) is examined each time a FILL\_MEM{\_WS} command is processed, allowing the operand size to be dynamically altered. The examples show the FILL\_MEM.B{\_WS}, FILL\_MEM.W{\_WS} and FILL\_MEM.L{\_WS} commands.

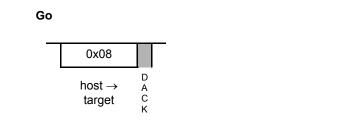

### 5.4.4.7 GO

Non-intrusive

This command is used to exit active BDM and begin (or resume) execution of CPU application code. The CPU pipeline is flushed and refilled before normal instruction execution resumes. Prefetching begins at the current address in the PC. If any register (such as the PC) is altered by a BDC command whilst in BDM, the updated value is used when prefetching resumes. If enabled, an ACK is driven on exiting active BDM.

If a GO command is issued whilst the BDM is inactive, an illegal command response is returned and the ILLCMD bit is set.

## 5.4.5.2.2 READ\_SAME Effects Of Variable Access Size

READ\_SAME uses the unadjusted address given in the previous READ\_MEM command as a base address for subsequent READ\_SAME commands. When the READ\_MEM and READ\_SAME size parameters differ then READ\_SAME uses the original base address buts aligns 32-bit and 16-bit accesses, where those accesses would otherwise cross the aligned 4-byte boundary. Table 5-12 shows some examples of this.

| Row | Command      | Base Address | 00       | 01       | 10       | 11       |

|-----|--------------|--------------|----------|----------|----------|----------|

| 1   | READ_MEM.32  | 0x004003     | Accessed | Accessed | Accessed | Accessed |

| 2   | READ_SAME.32 | —            | Accessed | Accessed | Accessed | Accessed |

| 3   | READ_SAME.16 | —            |          |          | Accessed | Accessed |

| 4   | READ_SAME.08 | —            |          |          |          | Accessed |

| 5   | READ_MEM.08  | 0x004000     | Accessed |          |          |          |

| 6   | READ_SAME.08 | —            | Accessed |          |          |          |

| 7   | READ_SAME.16 | —            | Accessed | Accessed |          |          |

| 8   | READ_SAME.32 | —            | Accessed | Accessed | Accessed | Accessed |

| 9   | READ_MEM.08  | 0x004002     |          |          | Accessed |          |

| 10  | READ_SAME.08 | —            |          |          | Accessed |          |

| 11  | READ_SAME.16 | —            |          |          | Accessed | Accessed |

| 12  | READ_SAME.32 | _            | Accessed | Accessed | Accessed | Accessed |

| 13  | READ_MEM.08  | 0x004003     |          |          |          | Accessed |

| 14  | READ_SAME.08 | —            |          |          |          | Accessed |

| 15  | READ_SAME.16 | —            |          |          | Accessed | Accessed |

| 16  | READ_SAME.32 | —            | Accessed | Accessed | Accessed | Accessed |

| 17  | READ_MEM.16  | 0x004001     |          | Accessed | Accessed |          |

| 18  | READ_SAME.08 | —            |          | Accessed |          |          |

| 19  | READ_SAME.16 | —            |          | Accessed | Accessed |          |

| 20  | READ_SAME.32 | —            | Accessed | Accessed | Accessed | Accessed |

| 21  | READ_MEM.16  | 0x004003     |          |          | Accessed | Accessed |

| 22  | READ_SAME.08 |              |          |          |          | Accessed |

| 23  | READ_SAME.16 |              |          |          | Accessed | Accessed |

| 24  | READ_SAME.32 |              | Accessed | Accessed | Accessed | Accessed |

Table 5-12. Consecutive READ\_SAME Accesses With Variable Size

## 5.4.6 BDC Serial Interface

The BDC communicates with external devices serially via the BKGD pin. During reset, this pin is a mode select input which selects between normal and special modes of operation. After reset, this pin becomes the dedicated serial interface pin for the BDC.

The BDC serial interface uses an internal clock source, selected by the CLKSW bit in the BDCCSR register. This clock is referred to as the target clock in the following explanation.

ECC Generation Module (SRAM\_ECCV2)

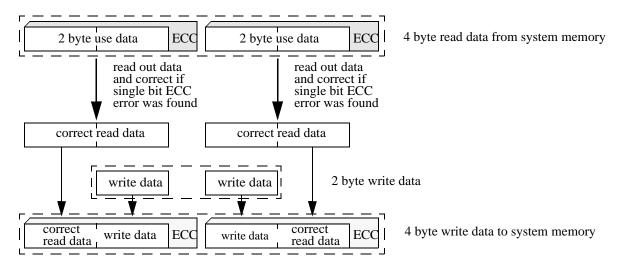

Figure 8-9. 2 byte non-aligned write access

## 8.3.3 Memory Read Access

During each memory read access an ECC check is performed. If the logic detects a single bit ECC error, then the module corrects the data, so that the access initiator module receives correct data. In parallel, the logic writes the corrected data back to the memory, so that this read access repairs the single bit ECC error. This automatic ECC read repair function is disabled by setting the ECCDRR bit.

If a single bit ECC error was detected, then the SBEEIF flag is set.

If the logic detects a double bit ECC error, then the data word is flagged as invalid, so that the access initiator module can ignore the data.

## 8.3.4 Memory Initialization

To avoid spurious ECC error reporting, memory operations that allow a read before a first write (like the read-modify-write operation of the non-aligned access) require that the memory contains valid ECC values before the first read-modify-write access is performed. The ECC module provides logic to initialize the complete memory content with zero during the power up phase. During the initialization process the access to the SRAM is disabled and the RDY status bit is cleared. If the initialization process is done, SRAM access is possible and the RDY status bit is set.

## 8.3.5 Interrupt Handling

This section describes the interrupts generated by the SRAM\_ECC module and their individual sources. Vector addresses and interrupt priority are defined at the MCU level.

## NOTE

The first period after enabling the counter by APIFE might be reduced by API start up delay  $t_{sdel}$ .

It is possible to generate with the API a waveform at the external pin API\_EXTCLK by setting APIFE and enabling the external access with setting APIEA.

# 9.7 Initialization/Application Information

# 9.7.1 General Initialization Information

Usually applications run in MCU Normal Mode.

It is recommended to write the CPMUCOP register in any case from the application program initialization routine after reset no matter if the COP is used in the application or not, even if a configuration is loaded via the flash memory after reset. By doing a "controlled" write access in MCU Normal Mode (with the right value for the application) the write once for the COP configuration bits (WCOP,CR[2:0]) takes place which protects these bits from further accidental change. In case of a program sequencing issue (code runaway) the COP configuration can not be accidentally modified anymore.

# 9.7.2 Application information for COP and API usage

In many applications the COP is used to check that the program is running and sequencing properly. Often the COP is kept running during Stop Mode and periodic wake-up events are needed to service the COP on time and maybe to check the system status.

For such an application it is recommended to use the ACLK as clock source for both COP and API. This guarantees lowest possible IDD current during Stop Mode. Additionally it eases software implementation using the same clock source for both, COP and API.

The Interrupt Service Routine (ISR) of the Autonomous Periodic Interrupt API should contain the write instruction to the CPMUARMCOP register. The value (byte) written is derived from the "main routine" (alternating sequence of \$55 and \$AA) of the application software.

Using this method, then in the case of a runtime or program sequencing issue the application "main routine" is not executed properly anymore and the alternating values are not provided properly. Hence the COP is written at the correct time (due to independent API interrupt request) but the wrong value is written (alternating sequence of \$55 and \$AA is no longer maintained) which causes a COP reset.

If the COP is stopped during any Stop Mode it is recommended to service the COP shortly before Stop Mode is entered.

# 9.7.3 Application Information for PLL and Oscillator Startup

The following C-code example shows a recommended way of setting up the system clock system using the PLL and Oscillator:

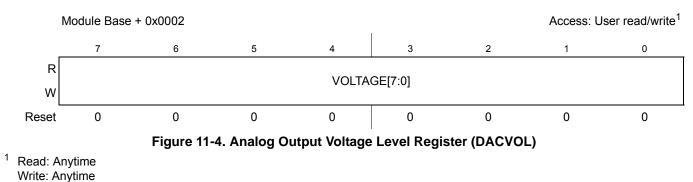

## 11.4.2.2 Analog Output Voltage Level Register (DACVOL)

| Field | Description                                                                                                                                        |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>VOLTAGE</b> — This register defines (together with the FVR bit) the analog output voltage. For more detail see Equation 11-1 and Equation 11-2. |

## 11.4.2.3 Reserved Register

| Module Base + 0x0007 |   |                       |          |          | Access: Us | ser read/write <sup>1</sup> |          |          |

|----------------------|---|-----------------------|----------|----------|------------|-----------------------------|----------|----------|

|                      | 7 | 6                     | 5        | 4        | 3          | 2                           | 1        | 0        |

| R                    | 0 | Deserved              | Reserved | Reserved | Reserved   | Reserved                    | Reserved | Reserved |

| W                    |   | Reserved              | Reserved | Reserveu | Reserved   | Reserved                    | Reserved | Reserved |

| Reset                | 0 | 0                     | 0        | 0        | 0          | 0                           | 0        | 0        |

|                      |   | <b>F</b> <sup>1</sup> |          |          |            |                             |          |          |

Figure 11-5. Reserved Registerfv\_dac\_8b5v\_RESERVED

<sup>1</sup> Read: Anytime Write: Only in special mode

NOTE

This reserved register bits are designed for factory test purposes only and are not intended for general user access. Writing to this register when in special modes can alter the modules functionality.

#### Scalable Controller Area Network (S12MSCANV2)

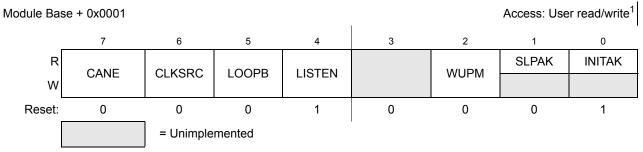

#### Figure 13-5. MSCAN Control Register 1 (CANCTL1)

<sup>1</sup> Read: AnytimeWrite: Anytime in initialization mode (INITRQ = 1 and INITAK = 1), except CANE which is write once in normal and anytime in special system operation modes when the MSCAN is in initialization mode (INITRQ = 1 and INITAK = 1)

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CANE   | MSCAN Enable         0       MSCAN module is disabled         1       MSCAN module is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6<br>CLKSRC | MSCAN Clock Source — This bit defines the clock source for the MSCAN module (only for systems with a clock generation module; Section 13.4.3.2, "Clock System," and Section Figure 13-42., "MSCAN Clocking Scheme,").<br>0 MSCAN clock source is the oscillator clock<br>1 MSCAN clock source is the bus clock                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5<br>LOOPB  | Loopback Self Test Mode — When this bit is set, the MSCAN performs an internal loopback which can be used<br>for self test operation. The bit stream output of the transmitter is fed back to the receiver internally. The RXCAN<br>input is ignored and the TXCAN output goes to the recessive state (logic 1). The MSCAN behaves as it does<br>normally when transmitting and treats its own transmitted message as a message received from a remote node.<br>In this state, the MSCAN ignores the bit sent during the ACK slot in the CAN frame acknowledge field to ensure<br>proper reception of its own message. Both transmit and receive interrupts are generated.<br>0 Loopback self test disabled<br>1 Loopback self test enabled |

| 4<br>LISTEN | Listen Only Mode — This bit configures the MSCAN as a CAN bus monitor. When LISTEN is set, all valid CAN messages with matching ID are received, but no acknowledgement or error frames are sent out (see Section 13.4.4.4, "Listen-Only Mode"). In addition, the error counters are frozen. Listen only mode supports applications which require "hot plugging" or throughput analysis. The MSCAN is unable to transmit any messages when listen only mode is active.<br>0 Normal operation<br>1 Listen only mode activated                                                                                                                                                                                                                |

| 2<br>WUPM   | Wake-Up Mode — If WUPE in CANCTL0 is enabled, this bit defines whether the integrated low-pass filter is<br>applied to protect the MSCAN from spurious wake-up (see Section 13.4.5.5, "MSCAN Sleep Mode").0MSCAN wakes up on any dominant level on the CAN bus<br>11MSCAN wakes up only in case of a dominant pulse on the CAN bus that has a length of Twup                                                                                                                                                                                                                                                                                                                                                                                |

#### Table 13-4. CANCTL1 Register Field Descriptions

#### Timer Module (TIM16B6CV3)

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TEN   | <ul> <li>Timer Enable</li> <li>0 Disables the main timer, including the counter. Can be used for reducing power consumption.</li> <li>1 Allows the timer to function normally.</li> <li>If for any reason the timer is not active, there is no ÷64 clock for the pulse accumulator because the ÷64 is generated by the timer prescaler.</li> </ul>                                                                                                                                                                                                            |

| 6<br>TSWAI | <ul> <li>Timer Module Stops While in Wait</li> <li>Allows the timer module to continue running during wait.</li> <li>Disables the timer module when the MCU is in the wait mode. Timer interrupts cannot be used to get the MCU out of wait.</li> <li>TSWAI also affects pulse accumulator.</li> </ul>                                                                                                                                                                                                                                                        |

| 5<br>TSFRZ | <ul> <li>Timer Stops While in Freeze Mode</li> <li>0 Allows the timer counter to continue running while in freeze mode.</li> <li>1 Disables the timer counter whenever the MCU is in freeze mode. This is useful for emulation.</li> <li>TSFRZ does not stop the pulse accumulator.</li> </ul>                                                                                                                                                                                                                                                                |

| 4<br>TFFCA | <ul> <li>Timer Fast Flag Clear All</li> <li>Allows the timer flag clearing to function normally.</li> <li>For TFLG1(0x000E), a read from an input capture or a write to the output compare channel (0x0010–0x001F) causes the corresponding channel flag, CnF, to be cleared. For TFLG2 (0x000F), any access to the TCNT register (0x0004, 0x0005) clears the TOF flag. This has the advantage of eliminating software overhead in a separate clear sequence. Extra care is required to avoid accidental flag clearing due to unintended accesses.</li> </ul> |

| 3<br>PRNT  | <ul> <li>Precision Timer</li> <li>0 Enables legacy timer. PR0, PR1, and PR2 bits of the TSCR2 register are used for timer counter prescaler selection.</li> <li>1 Enables precision timer. All bits of the PTPSR register are used for Precision Timer Prescaler Selection, and all bits.</li> <li>This bit is writable only once out of reset.</li> </ul>                                                                                                                                                                                                    |

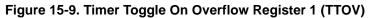

## 15.3.2.5 Timer Toggle On Overflow Register 1 (TTOV)

Module Base + 0x0007

|        | 7        | 6        | 5    | 4    | 3    | 2    | 1    | 0    |

|--------|----------|----------|------|------|------|------|------|------|

| R<br>W | RESERVED | RESERVED | TOV5 | TOV4 | TOV3 | TOV2 | TOV1 | TOV0 |

| Reset  | 0        | 0        | 0    | 0    | 0    | 0    | 0    | 0    |

ī.

Read: Anytime

Write: Anytime

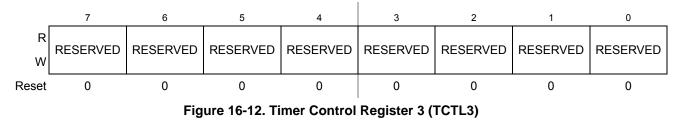

## 16.3.2.7 Timer Control Register 3/Timer Control Register 4 (TCTL3 and TCTL4)

Module Base + 0x000A

Module Base + 0x000B

Read: Anytime

Write: Anytime.

#### Table 16-8. TCTL3/TCTL4 Field Descriptions

Note: Writing to unavailable bits has no effect. Reading from unavailable bits return a zero.

| Field | Description                                                                                            |

|-------|--------------------------------------------------------------------------------------------------------|

| 1:0   | Input Capture Edge Control — These two pairs of control bits configure the input capture edge detector |

| EDGnB | circuits.                                                                                              |

| EDGnA |                                                                                                        |

### Table 16-9. Edge Detector Circuit Configuration

| EDGnB | EDGnA | Configuration                           |

|-------|-------|-----------------------------------------|

| 0     | 0     | Capture disabled                        |

| 0     | 1     | Capture on rising edges only            |

| 1     | 0     | Capture on falling edges only           |

| 1     | 1     | Capture on any edge (rising or falling) |

### Table 17-10. PWMCTL Field Descriptions

Note: Bits related to available channels have functional significance. Writing to unavailable bits has no effect. Read from unavailable bits return a zero

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CON67 | <ul> <li>Concatenate Channels 6 and 7</li> <li>Channels 6 and 7 are separate 8-bit PWMs.</li> <li>Channels 6 and 7 are concatenated to create one 16-bit PWM channel. Channel 6 becomes the high order byte and channel 7 becomes the low order byte. Channel 7 output pin is used as the output for this 16-bit PWM (bit 7 of port PWMP). Channel 7 clock select control-bit determines the clock source, channel 7 polarity bit determines the polarity, channel 7 enable bit enables the output and channel 7 center aligned enable bit determines the output mode.</li> </ul>                                                                                                                                                                                                                                                          |

| 6<br>CON45 | <ul> <li>Concatenate Channels 4 and 5</li> <li>Channels 4 and 5 are separate 8-bit PWMs.</li> <li>Channels 4 and 5 are concatenated to create one 16-bit PWM channel. Channel 4 becomes the high order byte and channel 5 becomes the low order byte. Channel 5 output pin is used as the output for this 16-bit PWM (bit 5 of port PWMP). Channel 5 clock select control-bit determines the clock source, channel 5 polarity bit determines the polarity, channel 5 enable bit enables the output and channel 5 center aligned enable bit determines the output mode.</li> </ul>                                                                                                                                                                                                                                                          |

| 5<br>CON23 | <ul> <li>Concatenate Channels 2 and 3</li> <li>Channels 2 and 3 are separate 8-bit PWMs.</li> <li>Channels 2 and 3 are concatenated to create one 16-bit PWM channel. Channel 2 becomes the high order byte and channel 3 becomes the low order byte. Channel 3 output pin is used as the output for this 16-bit PWM (bit 3 of port PWMP). Channel 3 clock select control-bit determines the clock source, channel 3 polarity bit determines the polarity, channel 3 enable bit enables the output and channel 3 center aligned enable bit determines the output mode.</li> </ul>                                                                                                                                                                                                                                                          |

| 4<br>CON01 | <ul> <li>Concatenate Channels 0 and 1</li> <li>Channels 0 and 1 are separate 8-bit PWMs.</li> <li>Channels 0 and 1 are concatenated to create one 16-bit PWM channel. Channel 0 becomes the high order byte and channel 1 becomes the low order byte. Channel 1 output pin is used as the output for this 16-bit PWM (bit 1 of port PWMP). Channel 1 clock select control-bit determines the clock source, channel 1 polarity bit determines the polarity, channel 1 enable bit enables the output and channel 1 center aligned enable bit determines the output mode.</li> </ul>                                                                                                                                                                                                                                                          |

| 3<br>PSWAI | <ul> <li>PWM Stops in Wait Mode — Enabling this bit allows for lower power consumption in wait mode by disabling the input clock to the prescaler.</li> <li>0 Allow the clock to the prescaler to continue while in wait mode.</li> <li>1 Stop the input clock to the prescaler whenever the MCU is in wait mode.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2<br>PFRZ  | <ul> <li>PWM Counters Stop in Freeze Mode — In freeze mode, there is an option to disable the input clock to the prescaler by setting the PFRZ bit in the PWMCTL register. If this bit is set, whenever the MCU is in freeze mode, the input clock to the prescaler is disabled. This feature is useful during emulation as it allows the PWM function to be suspended. In this way, the counters of the PWM can be stopped while in freeze mode so that once normal program flow is continued, the counters are re-enabled to simulate real-time operations. Since the registers can still be accessed in this mode, to re-enable the prescaler clock, either disable the PFRZ bit or exit freeze mode.</li> <li>1 Disable PWM input clock to the prescaler whenever the part is in freeze mode. This is useful for emulation.</li> </ul> |

## 17.3.2.7 PWM Clock A/B Select Register (PWMCLKAB)

Each PWM channel has a choice of four clocks to use as the clock source for that channel as described below.

#### Serial Communication Interface (S12SCIV6)

When the transmit shift register is not transmitting a frame, the TXD pin goes to the idle condition, logic 1. If at any time software clears the TE bit in SCI control register 2 (SCICR2), the transmitter enable signal goes low and the transmit signal goes idle.

If software clears TE while a transmission is in progress (TC = 0), the frame in the transmit shift register continues to shift out. To avoid accidentally cutting off the last frame in a message, always wait for TDRE to go high after the last frame before clearing TE.

To separate messages with preambles with minimum idle line time, use this sequence between messages:

- 1. Write the last byte of the first message to SCIDRH/L.

- 2. Wait for the TDRE flag to go high, indicating the transfer of the last frame to the transmit shift register.

- 3. Queue a preamble by clearing and then setting the TE bit.

- 4. Write the first byte of the second message to SCIDRH/L.

## 18.4.5.3 Break Characters

Writing a logic 1 to the send break bit, SBK, in SCI control register 2 (SCICR2) loads the transmit shift register with a break character. A break character contains all logic 0s and has no start, stop, or parity bit. Break character length depends on the M bit in SCI control register 1 (SCICR1). As long as SBK is at logic 1, transmitter logic continuously loads break characters into the transmit shift register. After software clears the SBK bit, the shift register finishes transmitting the last break character and then transmits at least one logic 1. The automatic logic 1 at the end of a break character guarantees the recognition of the start bit of the next frame.

The SCI recognizes a break character when there are 10 or 11(M = 0 or M = 1) consecutive zero received. Depending if the break detect feature is enabled or not receiving a break character has these effects on SCI registers.

If the break detect feature is disabled (BKDFE = 0):

- Sets the framing error flag, FE

- Sets the receive data register full flag, RDRF

- Clears the SCI data registers (SCIDRH/L)

- May set the overrun flag, OR, noise flag, NF, parity error flag, PE, or the receiver active flag, RAF (see 3.4.4 and 3.4.5 SCI Status Register 1 and 2)

If the break detect feature is enabled (BKDFE = 1) there are two scenarios<sup>1</sup>

The break is detected right from a start bit or is detected during a byte reception.

- Sets the break detect interrupt flag, BKDIF

- Does not change the data register full flag, RDRF or overrun flag OR

- Does not change the framing error flag FE, parity error flag PE.

- Does not clear the SCI data registers (SCIDRH/L)

- May set noise flag NF, or receiver active flag RAF.

<sup>1.</sup> A Break character in this context are either 10 or 11 consecutive zero received bits

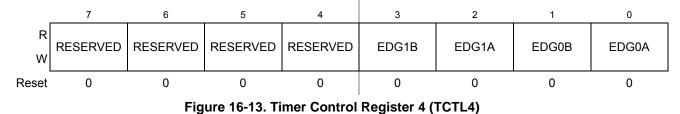

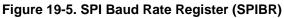

## 19.3.2.3 SPI Baud Rate Register (SPIBR)

Module Base +0x0002

### Read: Anytime

Write: Anytime; writes to the reserved bits have no effect

### Table 19-6. SPIBR Field Descriptions

| Field            | Description                                                                                                                                                                                                                   |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6–4<br>SPPR[2:0] | <b>SPI Baud Rate Preselection Bits</b> — These bits specify the SPI baud rates as shown in Table 19-7. In master mode, a change of these bits will abort a transmission in progress and force the SPI system into idle state. |

| 2–0<br>SPR[2:0]  | <b>SPI Baud Rate Selection Bits</b> — These bits specify the SPI baud rates as shown in Table 19-7. In master mode, a change of these bits will abort a transmission in progress and force the SPI system into idle state.    |

The baud rate divisor equation is as follows:

| BaudRateDivisor = (SPPR + 1 | ) • 2 <sup>(SPR + 1)</sup> | Ean. | 19-1 |

|-----------------------------|----------------------------|------|------|

| DauukateDivisor = (SPPK + 1 | )• Z` '                    | Eqn. | 19-  |

The baud rate can be calculated with the following equation:

### Baud Rate = BusClock / BaudRateDivisor Eqn. 19-2

### NOTE

For maximum allowed baud rates, please refer to the SPI Electrical Specification in the Electricals chapter of this data sheet.

| Table 19-7. Example SPI Baud Rate | e Selection (25 MHz Bus Clock) | (Sheet 1 of 3) |

|-----------------------------------|--------------------------------|----------------|

|                                   |                                | (0             |

| SPPR2 | SPPR1 | SPPR0 | SPR2 | SPR1 | SPR0 | Baud Rate<br>Divisor | Baud Rate     |

|-------|-------|-------|------|------|------|----------------------|---------------|

| 0     | 0     | 0     | 0    | 0    | 0    | 2                    | 12.5 Mbit/s   |

| 0     | 0     | 0     | 0    | 0    | 1    | 4                    | 6.25 Mbit/s   |

| 0     | 0     | 0     | 0    | 1    | 0    | 8                    | 3.125 Mbit/s  |

| 0     | 0     | 0     | 0    | 1    | 1    | 16                   | 1.5625 Mbit/s |

| 0     | 0     | 0     | 1    | 0    | 0    | 32                   | 781.25 kbit/s |

| 0     | 0     | 0     | 1    | 0    | 1    | 64                   | 390.63 kbit/s |

| 0     | 0     | 0     | 1    | 1    | 0    | 128                  | 195.31 kbit/s |

| 0     | 0     | 0     | 1    | 1    | 1    | 256                  | 97.66 kbit/s  |

| 0     | 0     | 1     | 0    | 0    | 0    | 4                    | 6.25 Mbit/s   |

MC912ZVL Family Reference Manual, Rev. 2.41

# 20.4.1.8 Handshaking

The clock synchronization mechanism can be used as a handshake in data transfer. Slave devices may hold the SCL low after completion of one byte transfer (9 bits). In such case, it halts the bus clock and forces the master clock into wait states until the slave releases the SCL line.

## 20.4.1.9 Clock Stretching

The clock synchronization mechanism can be used by slaves to slow down the bit rate of a transfer. After the master has driven SCL low the slave can drive SCL low for the required period and then release it. If the slave SCL low period is greater than the master SCL low period then the resulting SCL bus signal low period is stretched.

## 20.4.1.10 Ten-bit Address

A ten-bit address is indicated if the first 5 bits of the first address byte are 0x11110. The following rules apply to the first address byte.

| SLAVE<br>ADDRESS | R/W BIT | DESCRIPTION                          |

|------------------|---------|--------------------------------------|

| 0000000          | 0       | General call address                 |

| 0000010          | x       | Reserved for different bus<br>format |

| 0000011          | х       | Reserved for future purposes         |

| 11111XX          | x       | Reserved for future purposes         |

| 11110XX          | Х       | 10-bit slave addressing              |

Figure 20-13. Definition of bits in the first byte.

The address type is identified by ADTYPE. When ADTYPE is 0, 7-bit address is applied. Reversely, the address is 10-bit address.Generally, there are two cases of 10-bit address.See the Figure 20-14 and Figure 20-15.

| s | 1 | Slave Add1st 7bits<br>11110+ADR10+ADR9 | A1 | Slave Add 2nd byte<br>ADR[8:1] | A2 | Data | A3 |  |

|---|---|----------------------------------------|----|--------------------------------|----|------|----|--|

|---|---|----------------------------------------|----|--------------------------------|----|------|----|--|

Figure 20-14. A master-transmitter addresses a slave-receiver with a 10-bit address

| 1 11110+ADR10+ADR9 0 ADR[8:1] 11110+ADR10+ADR9 1 | s | Slave Add1st 7bits<br>11110+ADR10+ADR9 | R/W<br>0 | A1 | Slave Add 2nd byte<br>ADR[8:1] | A2 | Sr | Slave Add 1st 7bits<br>11110+ADR10+ADR9 | R/W<br>1 | A3 | Data | A4 |

|--------------------------------------------------|---|----------------------------------------|----------|----|--------------------------------|----|----|-----------------------------------------|----------|----|------|----|

|--------------------------------------------------|---|----------------------------------------|----------|----|--------------------------------|----|----|-----------------------------------------|----------|----|------|----|

### Figure 20-15. A master-receiver addresses a slave-transmitter with a 10-bit address.

In the Figure 20-15, the first two bytes are the similar to Figure 20-14. After the repeated START(Sr), the first slave address is transmitted again, but the R/W is 1, meaning that the slave is acted as a transmitter.

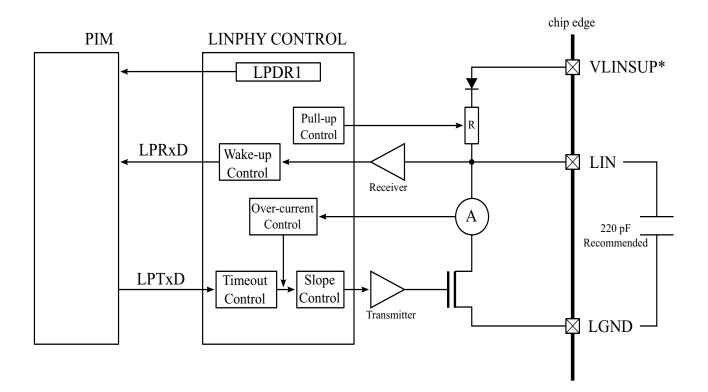

\*The VLINSUP supply mapping is described in device level documentation

### Figure 21-1. S12LINPHYV2 Block Diagram

### NOTE

The external 220 pF capacitance between LIN and LGND is strongly recommended for correct operation.

# 21.2 External Signal Description

This section lists and describes the signals that connect off chip as well as internal supply nodes and special signals.

# 21.2.1 LIN — LIN Bus Pin

This pad is connected to the single-wire LIN data bus.

## A.1.8.1 Measurement Conditions

Current is measured on VSUP. VDDX is connected to VDDA. It does not include the current to drive external loads. Unless otherwise noted the currents are measured in special single chip mode and the CPU code is executed from RAM. For Run and Wait current measurements PLL is on and the reference clock is the IRC1M trimmed to 1MHz. The bus clock frequency is set to the max value of 32MHz. Table A-13, Table A-14 and Table A-15 show the configuration of the CPMU module and the peripherals for Run, Wait and Stop current measurement.

| CPMU REGISTER | Bit settings/Conditions                                                                       |

|---------------|-----------------------------------------------------------------------------------------------|

| CPMUCLKS      | PLLSEL=0, PSTP=1, CSAD=0,<br>PRE=PCE=RTIOSCSEL=1<br>COPOSCSEL[1:0]=01                         |

| CPMUOSC       | OSCE=1, External Square wave on EXTAL f <sub>EXTAL</sub> =4MHz, $V_{IH}$ = 1.8V, $V_{IL}$ =0V |

| CPMURTI       | RTDEC=0, RTR[6:4]=111, RTR[3:0]=1111;                                                         |

| CPMUCOP       | WCOP=1, CR[2:0]=111                                                                           |

Table A-13. CPMU Configuration for Pseudo Stop Current Measurement

| CPMU REGISTER | Bit settings/Conditions                                                                    |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------|--|--|--|--|

| CPMUSYNR      | VCOFRQ[1:0]= 1,SYNDIV[5:0] = 31                                                            |  |  |  |  |

| CPMUPOSTDIV   | POSTDIV[4:0]=0                                                                             |  |  |  |  |

| CPMUCLKS      | PLLSEL=1, CSAD=0                                                                           |  |  |  |  |

| CPMUOSC       | OSCE=0,<br>Reference clock for PLL is f <sub>ref</sub> =f <sub>irc1m</sub> trimmed to 1MHz |  |  |  |  |

|               | API settings for STOP current measurement                                                  |  |  |  |  |

| CPMUAPICTL    | APIEA=0, APIFE=1, APIE=0                                                                   |  |  |  |  |

| CPMUACLKTR    | trimmed to >=20Khz                                                                         |  |  |  |  |

| CPMUAPIRH/RL  | set to 0xFFFF                                                                              |  |  |  |  |

#### Table A-15. Peripheral Configurations for Run & Wait Current Measurement

| Peripheral | Configuration                                            |  |  |  |

|------------|----------------------------------------------------------|--|--|--|

| SCI        | Continuously transmit data (0x55) at speed of 19200 baud |  |  |  |

| Conditions are: V <sub>SUP</sub> = 12V, API, COP & RTI enabled |                       |                    |     |     |     |      |

|----------------------------------------------------------------|-----------------------|--------------------|-----|-----|-----|------|

| Num                                                            | Rating                | Symbol             | Min | Тур | Max | Unit |

| 1                                                              | T <sub>J</sub> = 25°C | I <sub>SUPPS</sub> |     | 180 | 370 | μA   |

Table A-21. Pseudo Stop Current Characteristics for ZVL(A)128/96/64

# A.1.9 ADC Calibration Configuration

The reference voltage  $V_{BG}$  is measured under the conditions shown in Table A-22. The values stored in the IFR are the average of eight consecutive conversions at Tj=150 °C and eight consecutive conversions at Tj=-40 °C. The code is executed from RAM. The result is programmed to the IFR, otherwise there is no flash activity.

| Description                                 | Symbol              | Value       | Unit             |

|---------------------------------------------|---------------------|-------------|------------------|

| Regulator Supply Voltage at VSUP            | V <sub>SUP</sub>    | 5           | V                |

| Supply Voltage at VDDX and VDDA             | V <sub>DDX,A</sub>  | 5           | V                |

| ADC reference voltage high                  | V <sub>RH</sub>     | 5           | V                |

| ADC reference voltage low                   | V <sub>RL</sub>     | 0           | V                |

| ADC clock                                   | f <sub>ATDCLK</sub> | 2           | MHz              |

| ADC sample time                             | t <sub>SMP</sub>    | 4           | ADC clock cycles |

| Bus clock frequency                         | f <sub>bus</sub>    | 32          | MHz              |

| Junction temperature for S12ZVL(S)32/16/8   | Тj                  | -40 and 150 | °C               |

| Junction temperature for S12ZVL(A)128/96/64 | Тj                  | 150         | °C               |

Table A-22. Measurement Conditions

Package Information