Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | S12Z                                                                    |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SCI, SPI, UART/USART                    |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 34                                                                      |

| Program Memory Size        | 32KB (32K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 128 x 8                                                                 |

| RAM Size                   | 1K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 5.5V ~ 18V                                                              |

| Data Converters            | A/D 10x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-LQFP                                                                 |

| Supplier Device Package    | 48-LQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12zvl32f0clf |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|      | 18.4.3 Data Format                     |  |

|------|----------------------------------------|--|

|      | 18.4.4 Baud Rate Generation            |  |

|      | 18.4.5 Transmitter                     |  |

|      | 18.4.6 Receiver                        |  |

|      | 18.4.7 Single-Wire Operation           |  |

|      | 18.4.8 Loop Operation                  |  |

| 18.5 | Initialization/Application Information |  |

|      | 18.5.1 Reset Initialization            |  |

|      | 18.5.2 Modes of Operation              |  |

|      | 18.5.3 Interrupt Operation             |  |

|      | 18.5.4 Recovery from Wait Mode         |  |

|      | 18.5.5 Recovery from Stop Mode         |  |

# Chapter 19 Serial Peripheral Interface (S12SPIV5)

| 19.1 | Introduc | ction                              | 543 |

|------|----------|------------------------------------|-----|

|      | 19.1.1   | Glossary of Terms                  | 543 |

|      | 19.1.2   | Features                           | 543 |

|      | 19.1.3   | Modes of Operation                 | 543 |

|      | 19.1.4   | Block Diagram                      | 544 |

| 19.2 | External | l Signal Description               | 545 |

|      | 19.2.1   | MOSI — Master Out/Slave In Pin     | 545 |

|      | 19.2.2   | MISO — Master In/Slave Out Pin     | 546 |

|      | 19.2.3   | $\overline{SS}$ — Slave Select Pin | 546 |

|      | 19.2.4   | SCK — Serial Clock Pin             | 546 |

| 19.3 | Memory   | y Map and Register Definition      | 546 |

|      | 19.3.1   | Module Memory Map                  | 546 |

|      | 19.3.2   | Register Descriptions              | 547 |

| 19.4 | Function | nal Description                    | 555 |

|      | 19.4.1   | Master Mode                        | 556 |

|      | 19.4.2   | Slave Mode                         | 557 |

|      | 19.4.3   | Transmission Formats               | 558 |

|      | 19.4.4   | SPI Baud Rate Generation           | 563 |

|      | 19.4.5   | Special Features                   | 564 |

|      | 19.4.6   | Error Conditions                   | 565 |

|      | 19.4.7   | Low Power Mode Options             | 566 |

# Chapter 20

# Inter-Integrated Circuit (IICV3)

| 20.1 | Introduction                | 569 |

|------|-----------------------------|-----|

|      | 20.1.1 Features             | 569 |

|      | 20.1.2 Modes of Operation   | 570 |

|      | 20.1.3 Block Diagram        | 570 |

| 20.2 | External Signal Description | 570 |

| Feature                                                                                                                             | MC9S12ZVL128<br>MC9S12ZVLA128                       | MC9S12ZVL96<br>MC9S12ZVLA96 | MC9S12ZVL64<br>MC9S12ZVLA64 | MC9S12ZVL32 | MC9S12ZVL16 | MC9S12ZVL8 | MC9S12ZVLS32 | MC9S12ZVLS16 |  |

|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------------------|-----------------------------|-------------|-------------|------------|--------------|--------------|--|

| SCI <sup>6</sup>                                                                                                                    |                                                     | 2                           |                             | 2           |             |            | 2            |              |  |

| SPI                                                                                                                                 | 1                                                   |                             |                             | 1           |             |            | 1            |              |  |

| IIC                                                                                                                                 | 1                                                   |                             | 1                           |             |             | 1          |              |              |  |

| MSCAN                                                                                                                               | 1                                                   |                             | -                           |             |             | -          |              |              |  |

| max SRAM_ECC access width                                                                                                           |                                                     | 4 Byte                      |                             | 2 Byte      |             |            | 2 Byte       |              |  |

| Supported ADC option bits                                                                                                           |                                                     | yes                         |                             |             | no          |            |              | no           |  |

| General purpose I/O<br>- pin to support 25 mA driver strength to VSSX<br>- pin to support 20 mA driver strength from VDDX<br>(EVDD) | 34 <sup>(3)</sup> / 19<br>3 <sup>(3)</sup> / 1<br>1 |                             |                             |             |             |            | 8<br>3<br>1  |              |  |

| Interrupt capable pins <sup>7</sup> 5V / 12V                                                                                        | 22 <sup>(3)</sup> / 16 / 1                          |                             | 22 <sup>(3)</sup> / 16 / 1  |             |             | 14         | / 1          |              |  |

### Table 1-2. MC9S12ZVL-Family Comparison

<sup>1</sup> total current capability for MCU and MCU - external loads (on same PCB - board)

<sup>2</sup> MC9S12ZVLA device only

<sup>3</sup> available in 48-pin packages only

<sup>4</sup> to internally feed the ACMP or bonded out in 48-LQFP

<sup>5</sup> only 5V operation mode supported

<sup>6</sup> one SCI routed to the LINPHY

<sup>7</sup> IRQ / XIRQ and KWx pins

### NOTE

After power up, the MC9S12ZVL(A)128/96/64 devices starts in 3.3V VDDX mode. Then is possible to switch to the 5.0V VDDX behavior. For more details see the "Clock, Reset and Power Management Unit" section, 9.3.2.27, "Voltage Regulator Control Register (CPMUVREGCTL)

# 1.3 Chip-Level Features

On-chip modules available within the family include the following features:

- S12Z CPU core

- 128, 96, 64, 32, 16 or 8 KB on-chip flash with ECC

- 2048, 1024, 128 byte EEPROM with ECC

- 8192, 4096, 1024 or 512 byte on-chip SRAM with ECC

- Phase locked loop (IPLL) frequency multiplier with internal filter

- 1 MHz internal RC oscillator with +/-1.3% accuracy over rated temperature range

- 4-20 MHz amplitude controlled pierce oscillator

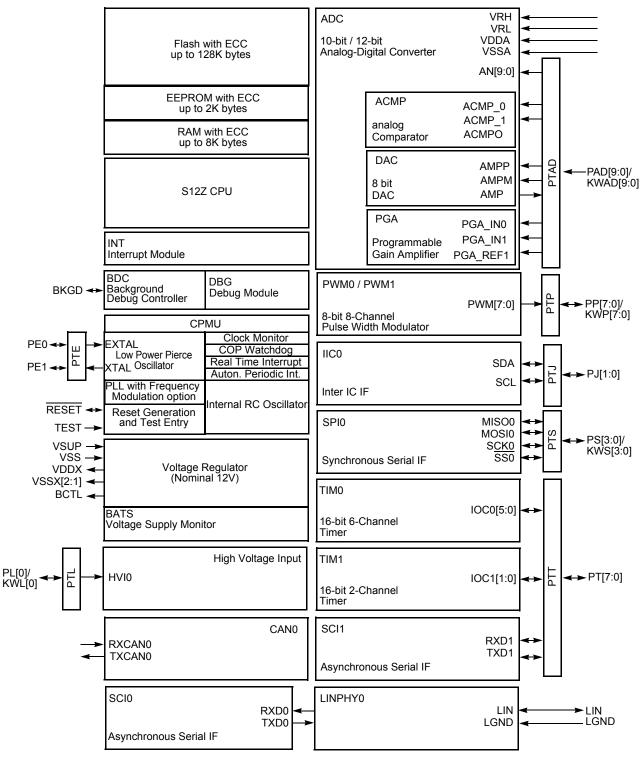

## 1.5 Block Diagram

Block Diagram shows the maximum configuration Not all pins or all peripherals are available on all devices and packages. Rerouting options are not shown.

To avoid current drawn from floating inputs, all non-bonded pins should be configured as output or configured as input with a pull up or pull down device enabled

## 1.7.2 Detailed External Signal Descriptions

This section describes the properties of signals available at device pins. Signal names associated with modules that can be instantiated more than once on an S12 are indexed, even if the module is only instantiated once on the MC9S12ZVL-Family. If a signal already includes a channel number, then the index is inserted before the channel number. Thus ANx\_y corresponds to AN instance x, channel number y.

## 1.7.2.1 RESET — External Reset Signal

The  $\overline{\text{RESET}}$  signal is an active low bidirectional control signal. It acts as an input to initialize the MCU to a known start-up state, and an output when an internal MCU function causes a reset. The  $\overline{\text{RESET}}$  pin has an internal pull-up device.

## 1.7.2.2 TEST — Test Pin

This input only pin is reserved for factory test. This pin has an internal pull-down device.

### NOTE

The TEST pin must be tied to ground in all applications.

## 1.7.2.3 MODC — Mode C Signal

The MODC signal is used as a MCU operating mode select during reset. The state of this signal is latched to the MODC bit at the rising edge of RESET. Out of reset the pull-up device is enabled.

## 1.7.2.4 PAD[9:0] / KWAD[9:0] — Port AD, Input Pins of ADC

PAD[9:0] are general-purpose input or output signals. The signals can be configured on per signal basis as interrupt inputs with wake-up capability (KWAD[9:0]). These signals can have a pull-up or pull-down device selected and enabled on per signal basis. During and out of reset the pull devices are disabled.

## 1.7.2.5 PE[1:0] — Port E I/O Signals

PE[1:0] are general-purpose input or output signals. The signals can have a pull-down device, enabled by on a per pin basis. Out of reset the pull-down devices are enabled.

## 1.7.2.6 PL0 — Port L Input Signal

PL0 is the high voltage input port. The signal can be configured as interrupt input with wake-up capability (KWL[0]). The pin voltage is divided and mapped to an ADC channel.

# 2.5 Initialization and Application Information

## 2.5.1 Port Data and Data Direction Register writes

It is not recommended to write PORTx/PTx and DDRx in a word access. When changing the register pins from inputs to outputs, the data may have extra transitions during the write access. Initialize the port data register before enabling the outputs.

# 2.5.2 SCI Baud Rate Detection

The baud rate for SCI0 and SCI1 can be determined by using a timer channel to measure the data rate on the related RXD signal.

- 1. Establish the link:

- For SCI0: Set MODRR4[T0IC3RR1:T0IC3RR0]=0b01 to disconnect the pin from TIM0 input capture channel 3 and reroute the timer input to the internal RXD0 signal of SCI0.

- For SCI1: Set MODRR4[T0IC3RR1:T0IC3RR0]=0b10 to disconnect the pin from TIM0 input capture channel 3 and reroute the timer input to the internal RXD1 signal of SCI1.

- 2. Determine pulse width of incoming data: Configure TIM0 input capture channel 3 to measure time between incoming signal edges.

# 2.5.3 Over-Current Protection on EVDD1

Pin PP7 can be used as general-purpose I/O or due to its increased current capability in output mode as a switchable external power supply pin (EVDD1) for external devices like Hall sensors.

EVDD1 connects the load to the digital supply VDDX.

An over-current monitor is implemented to protect the controller from short circuits or excess currents on the output which can only arise if the pin is configured for full drive. Although the full drive current is available on the high and low side, the protection is only available on the high side when sourcing current from EVDD1 to VSSX. There is also no protection to voltages higher than  $V_{DDX}$ .

To power up the over-current monitor set the related OCPEx bit.

In stop mode the over-current monitor is disabled for power saving. The increased current capability cannot be maintained to supply the external device. Therefore when using the pin as power supply the external load must be powered down prior to entering stop mode by driving the output low.

An over-current condition is detected if the output current level exceeds the threshold  $I_{OCD}$  in run mode. The output driver is immediately forced low and the over-current interrupt flag OCIFx asserts. Refer to Section 2.4.4.3, "Over-Current Interrupt".

# 2.5.4 Over-Current Protection on PP[5,3,1]

Pins PP[5,3,1] can be used as general-purpose I/O or due to their increased current capability in output mode as a switchable external power ground pin for external devices like LEDs supplied by VDDX.

| Field                    | Description                                                                                                                                                                                                                                                                                                                 |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-4 (MMCECL)<br>ACC[3:0] | Access Type Field — The ACC[3:0] bits capture the type of memory access, which caused the access violation. The access type is captured in form of a 4 bit value which is assigned as follows:<br>0:none (no error condition detected)<br>1:opcode fetch<br>2:vector fetch<br>3:data load<br>4:data store<br>5-15: reserved |

| 3-0 (MMCECL)<br>ERR[3:0] | Error Type Field — The EC[3:0] bits capture the type of the access violation. The type is captured in form of a 4 bit value which is assigned as follows:<br>0:none (no error condition detected)<br>1:access to an illegal address<br>2:uncorrectable ECC error<br>3-15:reserved                                           |

The MMCEC register captures debug information about access violations. It is set to a non-zero value if a S12ZCPU access violation or an uncorrectable ECC error has occurred. At the same time this register is set to a non-zero value, access information is captured in the MMCPCn and MMCCCRn registers. The MMCECn, the MMCPCn and the MMCCCRn registers are not updated if the MMCECn registers contain a non-zero value. The MMCECn registers are cleared by writing the value 0xFFFF.

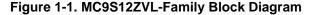

## 4.3.2.3 Captured S12ZCPU Condition Code Register (MMCCCRH, MMCCCRL)

Address: 0x0082 (MMCCCRH)

Read: Anytime

Write: Never

S12 Clock, Reset and Power Management Unit (S12CPMU\_UHV)

|            | RTR[6:4] =                  |                             |                             |                              |                              |                              |                               |                               |

|------------|-----------------------------|-----------------------------|-----------------------------|------------------------------|------------------------------|------------------------------|-------------------------------|-------------------------------|

| RTR[3:0]   | 000<br>(1x10 <sup>3</sup> ) | 001<br>(2x10 <sup>3</sup> ) | 010<br>(5x10 <sup>3</sup> ) | 011<br>(10x10 <sup>3</sup> ) | 100<br>(20x10 <sup>3</sup> ) | 101<br>(50x10 <sup>3</sup> ) | 110<br>(100x10 <sup>3</sup> ) | 111<br>(200x10 <sup>3</sup> ) |

| 0000 (÷1)  | 1x10 <sup>3</sup>           | 2x10 <sup>3</sup>           | 5x10 <sup>3</sup>           | 10x10 <sup>3</sup>           | 20x10 <sup>3</sup>           | 50x10 <sup>3</sup>           | 100x10 <sup>3</sup>           | 200x10 <sup>3</sup>           |

| 0001 (÷2)  | 2x10 <sup>3</sup>           | 4x10 <sup>3</sup>           | 10x10 <sup>3</sup>          | 20x10 <sup>3</sup>           | 40x10 <sup>3</sup>           | 100x10 <sup>3</sup>          | 200x10 <sup>3</sup>           | 400x10 <sup>3</sup>           |

| 0010 (÷3)  | 3x10 <sup>3</sup>           | 6x10 <sup>3</sup>           | 15x10 <sup>3</sup>          | 30x10 <sup>3</sup>           | 60x10 <sup>3</sup>           | 150x10 <sup>3</sup>          | 300x10 <sup>3</sup>           | 600x10 <sup>3</sup>           |

| 0011 (÷4)  | 4x10 <sup>3</sup>           | 8x10 <sup>3</sup>           | 20x10 <sup>3</sup>          | 40x10 <sup>3</sup>           | 80x10 <sup>3</sup>           | 200x10 <sup>3</sup>          | 400x10 <sup>3</sup>           | 800x10 <sup>3</sup>           |

| 0100 (÷5)  | 5x10 <sup>3</sup>           | 10x10 <sup>3</sup>          | 25x10 <sup>3</sup>          | 50x10 <sup>3</sup>           | 100x10 <sup>3</sup>          | 250x10 <sup>3</sup>          | 500x10 <sup>3</sup>           | 1x10 <sup>6</sup>             |

| 0101 (÷6)  | 6x10 <sup>3</sup>           | 12x10 <sup>3</sup>          | 30x10 <sup>3</sup>          | 60x10 <sup>3</sup>           | 120x10 <sup>3</sup>          | 300x10 <sup>3</sup>          | 600x10 <sup>3</sup>           | 1.2x10 <sup>6</sup>           |

| 0110 (÷7)  | 7x10 <sup>3</sup>           | 14x10 <sup>3</sup>          | 35x10 <sup>3</sup>          | 70x10 <sup>3</sup>           | 140x10 <sup>3</sup>          | 350x10 <sup>3</sup>          | 700x10 <sup>3</sup>           | 1.4x10 <sup>6</sup>           |

| 0111 (÷8)  | 8x10 <sup>3</sup>           | 16x10 <sup>3</sup>          | 40x10 <sup>3</sup>          | 80x10 <sup>3</sup>           | 160x10 <sup>3</sup>          | 400x10 <sup>3</sup>          | 800x10 <sup>3</sup>           | 1.6x10 <sup>6</sup>           |

| 1000 (÷9)  | 9x10 <sup>3</sup>           | 18x10 <sup>3</sup>          | 45x10 <sup>3</sup>          | 90x10 <sup>3</sup>           | 180x10 <sup>3</sup>          | 450x10 <sup>3</sup>          | 900x10 <sup>3</sup>           | 1.8x10 <sup>6</sup>           |

| 1001 (÷10) | 10 x10 <sup>3</sup>         | 20x10 <sup>3</sup>          | 50x10 <sup>3</sup>          | 100x10 <sup>3</sup>          | 200x10 <sup>3</sup>          | 500x10 <sup>3</sup>          | 1x10 <sup>6</sup>             | 2x10 <sup>6</sup>             |

| 1010 (÷11) | 11 x10 <sup>3</sup>         | 22x10 <sup>3</sup>          | 55x10 <sup>3</sup>          | 110x10 <sup>3</sup>          | 220x10 <sup>3</sup>          | 550x10 <sup>3</sup>          | 1.1x10 <sup>6</sup>           | 2.2x10 <sup>6</sup>           |

| 1011 (÷12) | 12x10 <sup>3</sup>          | 24x10 <sup>3</sup>          | 60x10 <sup>3</sup>          | 120x10 <sup>3</sup>          | 240x10 <sup>3</sup>          | 600x10 <sup>3</sup>          | 1.2x10 <sup>6</sup>           | 2.4x10 <sup>6</sup>           |

| 1100 (÷13) | 13x10 <sup>3</sup>          | 26x10 <sup>3</sup>          | 65x10 <sup>3</sup>          | 130x10 <sup>3</sup>          | 260x10 <sup>3</sup>          | 650x10 <sup>3</sup>          | 1.3x10 <sup>6</sup>           | 2.6x10 <sup>6</sup>           |

| 1101 (÷14) | 14x10 <sup>3</sup>          | 28x10 <sup>3</sup>          | 70x10 <sup>3</sup>          | 140x10 <sup>3</sup>          | 280x10 <sup>3</sup>          | 700x10 <sup>3</sup>          | 1.4x10 <sup>6</sup>           | 2.8x10 <sup>6</sup>           |

| 1110 (÷15) | 15x10 <sup>3</sup>          | 30x10 <sup>3</sup>          | 75x10 <sup>3</sup>          | 150x10 <sup>3</sup>          | 300x10 <sup>3</sup>          | 750x10 <sup>3</sup>          | 1.5x10 <sup>6</sup>           | 3x10 <sup>6</sup>             |

| 1111 (÷16) | 16x10 <sup>3</sup>          | 32x10 <sup>3</sup>          | 80x10 <sup>3</sup>          | 160x10 <sup>3</sup>          | 320x10 <sup>3</sup>          | 800x10 <sup>3</sup>          | 1.6x10 <sup>6</sup>           | 3.2x10 <sup>6</sup>           |

| Table 9-13. RTI Frequency D | Divide Rates for RTDEC=1 |

|-----------------------------|--------------------------|

|-----------------------------|--------------------------|

Three control bits in the CPMUCOP register allow selection of seven COP time-out periods.

When COP is enabled, the program must write \$55 and \$AA (in this order) to the CPMUARMCOP register during the selected time-out period. Once this is done, the COP time-out period is restarted. If the program fails to do this and the COP times out, a COP reset is generated. Also, if any value other than \$55 or \$AA is written, a COP reset is generated.

Windowed COP operation is enabled by setting WCOP in the CPMUCOP register. In this mode, writes to the CPMUARMCOP register to clear the COP timer must occur in the last 25% of the selected time-out period. A premature write will immediately reset the part.

In MCU Normal Mode the COP time-out period (CR[2:0]) and COP window (WCOP) setting can be automatically pre-loaded at reset release from NVM memory (if values are defined in the NVM by the application). By default the COP is off and no window COP feature is enabled after reset release via NVM memory. The COP control register CPMUCOP can be written once in an application in MCU Normal Mode to update the COP time-out period (CR[2:0]) and COP window (WCOP) setting loaded from NVM memory at reset release. Any value for the new COP time-out period and COP window setting is allowed except COP off value if the COP was enabled during pre-load via NVM memory.

The COP clock source select bits can not be pre-loaded via NVM memory at reset release. The IRC clock is the default COP clock source out of reset.

The COP clock source select bits (COPOSCSEL0/1) and ACLK clock control bit in Stop Mode (CSAD) can be modified until the CPMUCOP register write once has taken place. Therefore these control bits should be modified before the final COP time-out period and window COP setting is written. The CPMUCOP register access to modify the COP time-out period and window COP setting in MCU Normal Mode after reset release must be done with the WRTMASK bit cleared otherwise the update is ignored and this access does not count as the write once.

# 9.5.6 Power-On Reset (POR)

The on-chip POR circuitry detects when the internal supply VDD drops below an appropriate voltage level. The POR is deasserted, if the internal supply VDD exceeds an appropriate voltage level (voltage levels not specified, because the internal supply can not be monitored externally). The POR circuitry is always active. It acts as LVR in Stop Mode.

# 9.5.7 Low-Voltage Reset (LVR)

The on-chip LVR circuitry detects when one of the supply voltages VDD, VDDX and VDDF drops below an appropriate voltage level. If LVR is deasserted the MCU is fully operational at the specified maximum speed. The LVR assert and deassert levels for the supply voltage VDDX are  $V_{LVRXA}$  and  $V_{LVRXD}$  and are specified in the device Reference Manual.The LVR circuitry is active in Run- and Wait Mode.

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>RSTA | Restart Event (Restart from Top of Command Sequence List) — This bit indicates that a Restart Event is executed. The ADC loads the conversion command from top of the active Sequence Command List when no conversion or conversion sequence is ongoing. This bit is cleared when the first conversion command of the sequence from top of active Sequence Command List has been loaded into the ADCCMD register. This bit can only be set if bit ADC_EN is set. This bit is cleared if bit ADC_EN is clear. Data Bus Control: |

|           | This bit can be controlled via the data bus if access control is configured accordingly via ACC_CFG[1:0].<br>Writing a value of 1'b0 does not clear the flag.<br>Writing a one to this bit does not clear it but causes an overrun if the bit has already been set. See also<br>Section 10.6.3.2.6, "Conversion flow control in case of conversion sequence control bit overrun scenarios for<br>more details.                                                                                                                 |

|           | Internal Interface Control:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|           | This bit can be controlled via the internal interface Signal "Restart" if access control is configured accordingly via ACC_CFG[1:0]. After being set an additional request via internal interface Signal "Restart" causes an overrun. See conversion flow control in case of overrun situations for more details.                                                                                                                                                                                                              |

|           | General:<br>In conversion flow control mode "Trigger Mode" when bit RSTA gets set bit TRIG is set simultaneously if one of<br>the following has been executed:<br>- "End Of List" command type has been executed or is about to be executed                                                                                                                                                                                                                                                                                    |

|           | <ul> <li>Sequence Abort Event</li> <li>Continue with commands from active Sequence Command List.</li> <li>Restart from top of active Sequence Command List.</li> </ul>                                                                                                                                                                                                                                                                                                                                                         |

| 4<br>LDOK | Load OK for alternative Command Sequence List — This bit indicates if the preparation of the alternative<br>Sequence Command List is done and Command Sequence List must be swapped with the Restart Event. This<br>bit is cleared when bit RSTA is set (Restart Event executed) and the Command Sequence List got swapped.<br>This bit can only be set if bit ADC_EN is set.<br>This bit is cleared if bit ADC_EN is clear.<br>This bit is forced to zero if bit CSL_BMOD is clear.                                           |

|           | Data Bus Control:         This bit can be controlled via the data bus if access control is configured accordingly via ACC_CFG[1:0].         Writing a value of 1'b0 does not clear the flag.         To set bit LDOK the bits LDOK and RSTA must be written simultaneously.         After being set this bit can not be cleared by writing a value of 1'b1. See also Section 10.6.3.2.6, "Conversion flow control in case of conversion sequence control bit overrun scenarios for more details.                               |

|           | Internal Interface Control:<br>This bit can be controlled via the internal interface Signal "LoadOK" and "Restart" if access control is configured<br>accordingly via ACC_CFG[1:0]. With the assertion of Interface Signal "Restart" the interface Signal "LoadOK" is<br>evaluated and bit LDOK set accordingly (bit LDOK set if Interface Signal "LoadOK" asserted when Interface<br>Signal "Restart" asserts).<br>General:                                                                                                   |

|           | Only in "Restart Mode" if a Restart Event occurs without bit LDOK being set the error flag LDOK_EIF is set except<br>when the respective Restart Request occurred after or simultaneously with a Sequence Abort Request.<br>The LDOK_EIF error flag is also not set in "Restart Mode" if the first Restart Event occurs after:<br>- ADC got enabled<br>- Exit from Stop Mode<br>- ADC Soft-Reset                                                                                                                               |

|           | <ul><li>0 Load of alternative list done.</li><li>1 Load alternative list.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                            |

## 10.5.2.17 ADC Command Register 2 (ADCCMD\_2)

A command which contains reserved bit settings causes the error flag CMD\_EIF being set and ADC cease operation.

Module Base + 0x0016

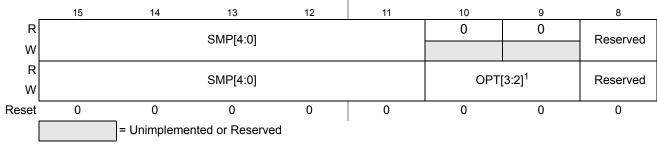

### Figure 10-20. ADC Command Register 2 (ADCCMD\_2)

<sup>1</sup> Only available on ADC12B\_LBA V2 and V3 (see Table 10-2 for details)

### Read: Anytime

Write: Only writable if bit SMOD\_ACC is set

(see also Section 10.5.2.2, "ADC Control Register 1 (ADCCTL\_1) bit SMOD\_ACC description for more details)

#### Table 10-25. ADCCMD\_2 Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                         |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-11<br>SMP[4:0] | Sample Time Select Bits — These four bits select the length of the sample time in units of ADC conversion clock cycles. Note that the ADC conversion clock period is itself a function of the prescaler value (bits PRS[6:0]). Table 10-26 lists the available sample time lengths. |

|                   | ADC12B_LBA V2 and V3 (includes OPT[3:2])                                                                                                                                                                                                                                            |

| 10-9<br>OPT[3:2]  | <b>Option Bits</b> — These two option bits can be used to control a SoC level feature/function. These bits are used together with Option bits OPT[1:0]. Please refer to the device reference manual for details of the feature/functionality controlled by these bits.              |

### NOTE

If bit SMOD\_ACC is set modifying this register must be done carefully only when no conversion and conversion sequence is ongoing.

| SMP[4] | SMP[3] | SMP[2] | SMP[1] | SMP[0] | Sample Time<br>in Number of<br>ADC Clock Cycles |

|--------|--------|--------|--------|--------|-------------------------------------------------|

| 0      | 0      | 0      | 0      | 0      | 4                                               |

| 0      | 0      | 0      | 0      | 1      | 5                                               |

| 0      | 0      | 0      | 1      | 0      | 6                                               |

| 0      | 0      | 0      | 1      | 1      | 7                                               |

#### Table 10-26. Sample Time Select

MC912ZVL Family Reference Manual, Rev. 2.41

- When finished:

This bit is cleared when the first conversion command of the sequence from top of active Sequence Command List is loaded

- Mandatory Requirement:

- In all ADC conversion flow control modes a Restart Event causes bit RSTA to be set. Bit SEQA is set simultaneously by ADC hardware if:

\* ADC not idle (a conversion or conversion sequence is ongoing and current CSL not finished) and no Sequence Abort Event in progress (bit SEQA not already set or set simultaneously via internal interface or data bus)

\* ADC idle but RVL done condition not reached

The RVL done condition is reached by one of the following:

\* A "End Of List" command type has been executed

\* A Sequence Abort Event is in progress or has been executed (bit SEQA already set or set simultaneously via internal interface or data bus)

The ADC executes the Sequence Abort Event followed by the Restart Event for the conditions described before or only a Restart Event.

- In ADC conversion flow control mode "Trigger Mode" a Restart Event causes bit TRIG being set automatically. Bit TRIG is set when no conversion or conversion sequence is ongoing (ADC idle) and the RVL done condition is reached by one of the following:

\* A "End Of List" command type has been executed

\* A Sequence Abort Event is in progress or has been executed

The ADC executes the Restart Event followed by the Trigger Event.

- In ADC conversion flow control mode "Trigger Mode" a Restart Event and a simultaneous Trigger Event via internal interface or data bus causes the TRIG\_EIF bit being set and ADC cease operation.

### • Restart Event + CSL Exchange (Swap)

Internal Interface Signals: Restart + LoadOK Corresponding Bit Names: RSTA + LDOK

– Function:

Go to top of active CSL (clear index register for CSL) and switch to other offset register for address calculation if configured for double buffer mode (exchange the CSL list) *Requested by:*

- Internal interface with the assertion of Interface Signal Restart the interface Signal LoadOK is evaluated and bit LDOK is set accordingly (bit LDOK set if Interface Signal LoadOK asserted when Interface Signal Restart asserts).

- Write Access via data bus to set control bit RSTA simultaneously with bit LDOK.

- When finished:

Bit LDOK can only be cleared if it was set as described before and both bits (LDOK, RSTA) are cleared when the first conversion command from top of active Sequence Command List is loaded

*– Mandatory Requirement:*

No ongoing conversion or conversion sequence Details if using the internal interface:

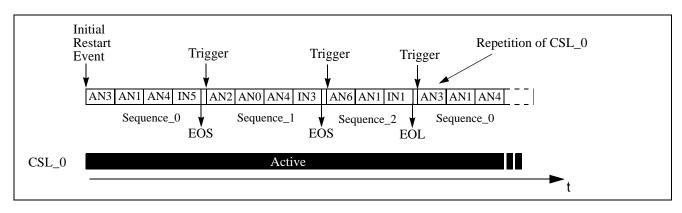

# 10.9.9 Triggered Conversion — Single CSL

Applications that require the conversion of one or more groups of different channels in a periodic and timed manner can make use of a configuration in "Trigger Mode" with a single CSL containing a list of sequences. This means the CSL consists of several sequences each separated by an "End of Sequence" command. The last command of the CSL uses the "End Of List" command with wrap to top of CSL and waiting for a Trigger (CMD\_SEL[1:0] =2'b11). Hence after the initial Restart Event each sequence can be launched via a Trigger Event and repetition of the CSL can be launched via a Trigger after execution of the "End Of List" command.

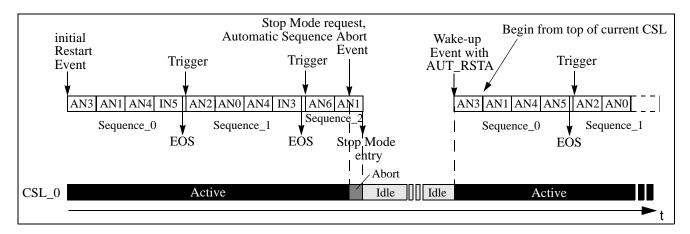

Figure 10-42. Conversion Flow Control Diagram — Triggered Conversion (CSL Repetition)

Figure 10-43. Conversion Flow Control Diagram — Triggered Conversion (with Stop Mode)

In case a Low Power Mode is used:

If bit AUT\_RSTA is set before Low Power Mode is entered, the conversion continues automatically as soon as a low power mode (Stop Mode or Wait Mode with bit SWAI set) is exited.

| Register<br>Name            |        | Bit 7 | 6                           | 5             | 4            | 3             | 2           | 1      | Bit 0 |  |

|-----------------------------|--------|-------|-----------------------------|---------------|--------------|---------------|-------------|--------|-------|--|

| 0x0010–0x0013<br>CANIDAR0–3 | R<br>W | AC7   | AC6                         | AC5           | AC4          | AC3           | AC2         | AC1    | AC0   |  |

| 0x0014–0x0017<br>CANIDMRx   | R<br>W | AM7   | AM6                         | AM5           | AM4          | AM3           | AM2         | AM1    | AM0   |  |

| 0x0018–0x001B<br>CANIDAR4–7 | R<br>W | AC7   | AC6                         | AC5           | AC4          | AC3           | AC2         | AC1    | AC0   |  |

| 0x001C–0x001F<br>CANIDMR4–7 | R<br>W | AM7   | AM6                         | AM5           | AM4          | AM3           | AM2         | AM1    | AM0   |  |

| 0x0020–0x002F<br>CANRXFG    | R<br>W |       | See S                       | ection 13.3.3 | s, "Programm | er's Model of | Message Sto | orage" |       |  |

| 0x0030–0x003F<br>CANTXFG    | R<br>W |       | See S                       | ection 13.3.3 | s, "Programm | er's Model of | Message Sto | orage" |       |  |

|                             |        |       | = Unimplemented or Reserved |               |              |               |             |        |       |  |

Figure 13-3. MSCAN Register Summary (continued)

## 13.3.2 Register Descriptions

This section describes in detail all the registers and register bits in the MSCAN module. Each description includes a standard register diagram with an associated figure number. Details of register bit and field function follow the register diagrams, in bit order. All bits of all registers in this module are completely synchronous to internal clocks during a register read.

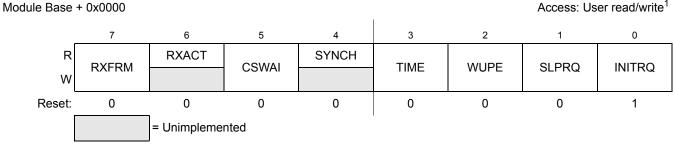

## 13.3.2.1 MSCAN Control Register 0 (CANCTL0)

The CANCTL0 register provides various control bits of the MSCAN module as described below.

Figure 13-4. MSCAN Control Register 0 (CANCTL0)

<sup>1</sup> Read: Anytime

Write: Anytime when out of initialization mode; exceptions are read-only RXACT and SYNCH, RXFRM (which is set by the module only), and INITRQ (which is also writable in initialization mode)

## NOTE

The CANCTL0 register, except WUPE, INITRQ, and SLPRQ, is held in the reset state when the initialization mode is active (INITRQ = 1 and INITAK = 1). This register is writable again as soon as the initialization mode is exited (INITRQ = 0 and INITAK = 0).

### Table 13-3. CANCTL0 Register Field Descriptions

| Field                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>RXFRM              | <ul> <li>Received Frame Flag — This bit is read and clear only. It is set when a receiver has received a valid message correctly, independently of the filter configuration. After it is set, it remains set until cleared by software or reset. Clearing is done by writing a 1. Writing a 0 is ignored. This bit is not valid in loopback mode.</li> <li>0 No valid message was received since last clearing this flag</li> <li>1 A valid message was received since last clearing of this flag</li> </ul>                                                                                                                                                                                                                               |

| 6<br>RXACT              | <ul> <li>Receiver Active Status — This read-only flag indicates the MSCAN is receiving a message<sup>1</sup>. The flag is controlled by the receiver front end. This bit is not valid in loopback mode.</li> <li>0 MSCAN is transmitting or idle</li> <li>1 MSCAN is receiving a message (including when arbitration is lost)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5<br>CSWAI <sup>2</sup> | <ul> <li>CAN Stops in Wait Mode — Enabling this bit allows for lower power consumption in wait mode by disabling all the clocks at the CPU bus interface to the MSCAN module.</li> <li>0 The module is not affected during wait mode</li> <li>1 The module ceases to be clocked during wait mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4<br>SYNCH              | <ul> <li>Synchronized Status — This read-only flag indicates whether the MSCAN is synchronized to the CAN bus and able to participate in the communication process. It is set and cleared by the MSCAN.</li> <li>0 MSCAN is not synchronized to the CAN bus</li> <li>1 MSCAN is synchronized to the CAN bus</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3<br>TIME               | <ul> <li>Timer Enable — This bit activates an internal 16-bit wide free running timer which is clocked by the bit clock rate. If the timer is enabled, a 16-bit time stamp will be assigned to each transmitted/received message within the active TX/RX buffer. Right after the EOF of a valid message on the CAN bus, the time stamp is written to the highest bytes (0x000E, 0x000F) in the appropriate buffer (see Section 13.3.3, "Programmer's Model of Message Storage"). In loopback mode no receive timestamp is generated. The internal timer is reset (all bits set to 0) when disabled. This bit is held low in initialization mode.</li> <li>0 Disable internal MSCAN timer</li> <li>1 Enable internal MSCAN timer</li> </ul> |

| 2<br>WUPE <sup>3</sup>  | <ul> <li>Wake-Up Enable — This configuration bit allows the MSCAN to restart from sleep mode or from power down mode (entered from sleep) when traffic on CAN is detected (see Section 13.4.5.5, "MSCAN Sleep Mode"). This bit must be configured before sleep mode entry for the selected function to take effect.</li> <li>0 Wake-up disabled — The MSCAN ignores traffic on CAN</li> <li>1 Wake-up enabled — The MSCAN is able to restart</li> </ul>                                                                                                                                                                                                                                                                                    |

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>AM[7:0] | <ul> <li>Acceptance Mask Bits — If a particular bit in this register is cleared, this indicates that the corresponding bit in the identifier acceptance register must be the same as its identifier bit before a match is detected. The message is accepted if all such bits match. If a bit is set, it indicates that the state of the corresponding bit in the identifier acceptance register does not affect whether or not the message is accepted.</li> <li>Match corresponding acceptance code register and identifier bits</li> <li>Ignore corresponding acceptance code register bit</li> </ul> |

#### Table 13-23. CANIDMR0–CANIDMR3 Register Field Descriptions

#### Module Base + 0x001C to Module Base + 0x001F

Access: User read/write<sup>1</sup>

| _      | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   | _ |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|---|

| R<br>W | AM7 | AM6 | AM5 | AM4 | AM3 | AM2 | AM1 | AM0 |   |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | • |

#### Figure 13-22. MSCAN Identifier Mask Registers (Second Bank) — CANIDMR4–CANIDMR7

Read: Anytime

Write: Anytime in initialization mode (INITRQ = 1 and INITAK = 1)

#### Table 13-24. CANIDMR4–CANIDMR7 Register Field Descriptions

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>AM[7:0] | <ul> <li>Acceptance Mask Bits — If a particular bit in this register is cleared, this indicates that the corresponding bit in the identifier acceptance register must be the same as its identifier bit before a match is detected. The message is accepted if all such bits match. If a bit is set, it indicates that the state of the corresponding bit in the identifier acceptance register does not affect whether or not the message is accepted.</li> <li>Match corresponding acceptance code register and identifier bits</li> <li>Ignore corresponding acceptance code register bit</li> </ul> |

## 13.3.3 Programmer's Model of Message Storage

The following section details the organization of the receive and transmit message buffers and the associated control registers.

To simplify the programmer interface, the receive and transmit message buffers have the same outline. Each message buffer allocates 16 bytes in the memory map containing a 13 byte data structure.

An additional transmit buffer priority register (TBPR) is defined for the transmit buffers. Within the last two bytes of this memory map, the MSCAN stores a special 16-bit time stamp, which is sampled from an internal timer after successful transmission or reception of a message. This feature is only available for transmit and receiver buffers, if the TIME bit is set (see Section 13.3.2.1, "MSCAN Control Register 0 (CANCTL0)").

The time stamp register is written by the MSCAN. The CPU can only read these registers.

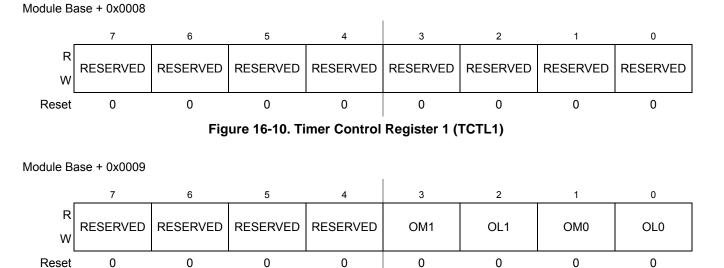

## 16.3.2.6 Timer Control Register 1/Timer Control Register 2 (TCTL1/TCTL2)

Figure 16-11. Timer Control Register 2 (TCTL2)

### Read: Anytime

Write: Anytime

#### Table 16-6. TCTL1/TCTL2 Field Descriptions

Note: Writing to unavailable bits has no effect. Reading from unavailable bits return a zero

| Field      | Description                                                                                                                                                                                                                                                                                                         |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1:0<br>OMx | Output Mode — These two pairs of control bits are encoded to specify the output action to be taken as a result<br>of a successful OCx compare. When either OMx or OLx is 1, the pin associated with OCx becomes an output<br>tied to OCx.Note:For an output line to be driven by an OCx the OCPDx must be cleared.  |

| 1:0<br>OLx | Output Level — These two pairs of control bits are encoded to specify the output action to be taken as a result<br>of a successful OCx compare. When either OMx or OLx is 1, the pin associated with OCx becomes an output<br>tied to OCx.Note:For an output line to be driven by an OCx the OCPDx must be cleared. |

#### Table 16-7. Compare Result Output Action

| ОМх | OLx | Action                                                 |

|-----|-----|--------------------------------------------------------|

| 0   | 0   | No output compare<br>action on the timer output signal |

| 0   | 1   | Toggle OCx output line                                 |

| 1   | 0   | Clear OCx output line to zero                          |

| 1   | 1   | Set OCx output line to one                             |

- For channels 0, 1, 4, and 5 the clock choices are clock A.

- For channels 2, 3, 6, and 7 the clock choices are clock B.

# 17.6 Interrupts

The PWM module has no interrupt.

| Field       | Description                                                                                                                                                                                                                        |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>BERRIE | <ul> <li>Bit Error Interrupt Enable — BERRIE enables the bit error interrupt flag, BERRIF, to generate interrupt requests.</li> <li>0 BERRIF interrupt requests disabled</li> <li>1 BERRIF interrupt requests enabled</li> </ul>   |

| 0<br>BKDIE  | <ul> <li>Break Detect Interrupt Enable — BKDIE enables the break detect interrupt flag, BKDIF, to generate interrupt requests.</li> <li>0 BKDIF interrupt requests disabled</li> <li>1 BKDIF interrupt requests enabled</li> </ul> |

#### Table 18-6. SCIACR1 Field Descriptions (continued)

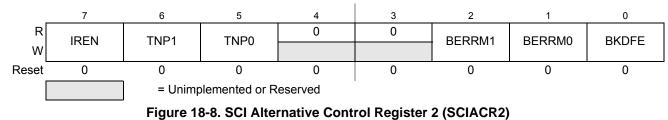

## 18.3.2.5 SCI Alternative Control Register 2 (SCIACR2)

Module Base + 0x0002

Read: Anytime, if AMAP = 1

Write: Anytime, if AMAP = 1

### Table 18-7. SCIACR2 Field Descriptions

| Field             | Description                                                                                                                                                                  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>IREN         | Infrared Enable Bit — This bit enables/disables the infrared modulation/demodulation submodule.<br>0 IR disabled<br>1 IR enabled                                             |

| 6:5<br>TNP[1:0]   | <b>Transmitter Narrow Pulse Bits</b> — These bits enable whether the SCI transmits a 1/16, 3/16, 1/32 or 1/4 narrow pulse. See Table 18-8.                                   |

| 2:1<br>BERRM[1:0] | <b>Bit Error Mode</b> — Those two bits determines the functionality of the bit error detect feature. See Table 18-9.                                                         |

| 0<br>BKDFE        | <ul> <li>Break Detect Feature Enable — BKDFE enables the break detect circuitry.</li> <li>0 Break detect circuit disabled</li> <li>1 Break detect circuit enabled</li> </ul> |

#### Table 18-8. IRSCI Transmit Pulse Width

| TNP[1:0] | Narrow Pulse Width |

|----------|--------------------|

| 11       | 1/4                |

| 10       | 1/32               |

| 01       | 1/16               |

#### **MCU Electrical Specifications**

<sup>5</sup> Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2.

## A.1.7 I/O Characteristics

This section describes the characteristics of I/O pins.

### Table A-10. 5V I/O Characteristics (Junction Temperature From -40°C To +175°C)

| MC9S<br>MC9S | tions are:<br>$12ZVL(S)32\16\8: 4.5V \le V_{DDX} \le 5.5V,$<br>$12ZVL(A)128\96\64: 4.85V \le V_{DDX} \le 5.15V,$<br>s otherwise noted. I/O Characteristics for all GPIO pins (d                                                | lefined in A.1       | I.1.1/A-671).          |     |                       |      |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------------|-----|-----------------------|------|

| Num          | Rating                                                                                                                                                                                                                         | Symbol               | Min                    | Тур | Max                   | Unit |

| 1a           | Input high voltage                                                                                                                                                                                                             | V <sub>IH</sub>      | 0.65*V <sub>DDX</sub>  | _   | _                     | V    |

| 1b           | Input high voltage BKGD pin, 3.15 V < V <sub>DDX</sub> <5.5V                                                                                                                                                                   | V <sub>IH</sub>      | 0.65*V <sub>DDX</sub>  |     | —                     | V    |

| 2            | Input high voltage                                                                                                                                                                                                             | V <sub>IH</sub>      | —                      |     | V <sub>DDX</sub> +0.3 | V    |

| 3a           | Input low voltage                                                                                                                                                                                                              | V <sub>IL</sub>      | _                      |     | 0.35*V <sub>DDX</sub> | V    |

| 3b           | Input low voltage BKGD pin, 3.15 V < V <sub>DDX</sub> <5.5V                                                                                                                                                                    | V <sub>IL</sub>      | —                      | _   | 0.35*V <sub>DDX</sub> | V    |

| 4            | Input low voltage                                                                                                                                                                                                              | V <sub>IL</sub>      | V <sub>SSX</sub> –0.3  | _   | _                     | V    |

| 5            | Input hysteresis                                                                                                                                                                                                               | V <sub>HYS</sub>     | —                      | 250 | —                     | mV   |

| 6            | Input leakage current on all GPIO<br>- except PP1, PP3, PP5 and PP7<br>- except PAD0 and PAD1 for $150^{\circ}C < T_{J} < 175^{\circ}C$<br>(Pins in high impedance input mode) <sup>1</sup><br>$V_{in} = V_{DDX}$ or $V_{SSX}$ | l <sub>.</sub><br>in | -1                     | _   | 1                     | μΑ   |

| 7            | Input leakage current on PAD0 for $150^{\circ}C < T_J < 175^{\circ}C$<br>(Pin in high impedance input mode) <sup>1</sup><br>$V_{in} = V_{DDX} \text{ or } V_{SSX}$                                                             | l <sub>in</sub>      | -1.5                   | _   | 1.5                   | μA   |

| 8            | Input leakage current on PAD1 for $150^{\circ}C < T_{J} < 175^{\circ}C$<br>(Pin in high impedance input mode) <sup>1</sup><br>$V_{in} = V_{DDX}$ or $V_{SSX}$                                                                  | l <sub>in</sub>      | -3.5                   | —   | 3.5                   | μA   |

| 9            | Input leakage current on PP1, PP3, PP5 and PP7 for<br>$-40^{\circ}C < T_{J} < 150^{\circ}C$<br>(Pins in high impedance input mode) <sup>1</sup><br>$V_{in} = V_{DDX} \text{ or } V_{SSX}$                                      | l <sub>.</sub><br>in | -2.5                   | _   | 2.5                   | μA   |

| 10           | Input leakage current on PP1, PP3, PP5 and PP7 for<br>$150^{\circ}C < T_{J} < 175^{\circ}C$<br>(Pins in high impedance input mode) <sup>1</sup><br>$V_{in} = V_{DDX} \text{ or } V_{SSX}$                                      | l <sub>.</sub> in    | -3.5                   | _   | 7                     | μA   |

| 11           | Output high voltage<br>(All GPIO except PP1, PP3 <sup>2</sup> , PP5 <sup>2</sup> and PP7)<br>$I_{OH} = -4 \text{ mA}$                                                                                                          | V <sub>OH</sub>      | V <sub>DDX</sub> – 0.8 | _   | _                     | V    |

| 12           | Output low voltage<br>(All GPIO except PP1, PP3 <sup>2</sup> , PP5 <sup>2</sup> and PP7)<br>I <sub>OL</sub> = +4mA                                                                                                             | V <sub>OL</sub>      | _                      | _   | 0.8                   | V    |

1. The values for thermal resistance are achieved by package simulations

# I.3 Dynamic Electrical Characteristics

### Table I-3. Dynamic Electrical Characteristics of the analog comparator - ACMP

Characteristics noted under conditions  $3.20V \le V_{DDA} \le 5.15V$ ,  $-40^{\circ}C \le T_J \le 175^{\circ}C^1$  unless otherwise noted. Typical values noted reflect the approximate parameter mean at  $T_A = 25^{\circ}C^2$  under nominal conditions unless otherwise noted.

| Num | Ratings                                                                                                                                                                                                                                                                                | Symbol                   | Min       | Тур       | Max        | Unit     |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------|-----------|------------|----------|

| 1   | Output uncertain time after module enable                                                                                                                                                                                                                                              | t <sub>ACMP_dly_en</sub> | -         | 1         | 2          | μS       |

| 2   | ACMP Propagation Delay of Inputs ACMP0 and<br>ACMP1 for -2*V <sub>hyst(typ)</sub> to +2*V <sub>hyst(typ)</sub> input step (w/o<br>synchronize delay)<br>• ACDLY=0 Low speed mode<br>• ACDLY=1 High speed mode<br>ACMPP is crossing ACMPN in positive direction                         | t <sub>ACMP_delay</sub>  | 130<br>20 | 300<br>70 | 750<br>400 | ns<br>ns |

| 3   | ACMP Propagation Delay of Inputs ACMP0 and ACMP1 for $-2^*V_{hyst(typ)}$ to $+2^*V_{hyst(typ)}$ input step (w/o synchronize delay) $150^\circ$ C $\leq T_J \leq 175^\circ$ C<br>• ACDLY=0 Low speed mode<br>• ACDLY=1 High speed mode<br>ACMPP is crossing ACMPN in positive direction | t <sub>ACMP_delay</sub>  | -         | -         | 800<br>450 | ns<br>ns |

$1 T_{J}$ : Junction Temperature

<sup>2</sup> T<sub>A</sub>: Ambient Temperature