#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | S12Z                                                                     |

| Core Size                  | 16-Bit                                                                   |

| Speed                      | 32MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SCI, SPI, UART/USART                     |

| Peripherals                | LVD, POR, PWM, WDT                                                       |

| Number of I/O              | 19                                                                       |

| Program Memory Size        | 32KB (32K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 1K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 5.5V ~ 18V                                                               |

| Data Converters            | A/D 6x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 32-LQFP                                                                  |

| Supplier Device Package    | 32-LQFP (7x7)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12zvl32f0mlcr |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.7.3 Power Supply Pins

The power and ground pins are described below. Because fast signal transitions place high, short-duration current demands on the power supply, use bypass capacitors with high-frequency characteristics and place them as close to the MCU as possible.

### NOTE

All ground pins must be connected together in the application.

# 1.7.3.1 VDDX, VSSX1, VSSX2 — Digital I/O Power and Ground Pins

VDDX is the voltage regulator output to supply the digital I/O drivers. It supplies the VDDX domain pads. The VSSX1 and VSSX2 pin are the ground pin for the digital I/O drivers.

Bypass requirements on VDDX, VSSX2 depend on how heavily the MCU pins are loaded.

# 1.7.3.2 VDDA, VSSA — Power Supply Pins for ADC

These are the power supply and ground pins for the analog-to-digital converter and the voltage regulator. These pins must be externally connected to the voltage regulator (VDDX, VSSX). A separate bypass capacitor for the ADC supply is recommended.

# 1.7.3.3 VSS — Core Ground Pin

The voltage supply of nominally 1.8V is generated by the internal voltage regulator. The return current path is through the VSS pin.

### 1.7.3.4 LGND — LINPHY Ground Pin

LGND is the ground pin for the LIN physical layer LINPHY. This pin must be connected to board ground, even if the LINPHY is not used.

# 1.7.3.5 VSUP — Voltage Supply Pin for Voltage Regulator

VSUP is the 12V/18V supply voltage pin for the on chip voltage regulator. This is the voltage supply input from which the voltage regulator generates the on chip voltage supplies. It must be protected externally against a reverse battery connection.

# 1.8 Device Pinouts

MC9S12ZVL-Family is available in 48-pin package and 32-pin package. Signals in parentheses in Figure 1-3 to Figure 1-5 denote alternative module routing options.

The exposed pad must be connected to a grounded contact pad on the PCB. The exposed pad has an electrical connection within the package to VSSFLAG (VSSX die connection).

in system wait mode. For further power consumption the peripherals can individually turn off their local clocks. Asserting  $\overline{\text{RESET}}$ ,  $\overline{\text{XIRQ}}$ ,  $\overline{\text{IRQ}}$ , or any other interrupt that is not masked, either locally or globally by a CCR bit, ends system wait mode.

• Static power modes:

Static power (Stop) modes are entered following the CPU STOP instruction unless an NVM command is active. When no NVM commands are active, the Stop request is acknowledged and the device enters either Stop or Pseudo Stop mode.

- Pseudo-stop: In this mode the system clocks are stopped but the oscillator is still running and the real time interrupt (RTI), watchdog (COP) and Autonomous Periodic Interrupt (API) may be enabled. Other peripherals are turned off. This mode consumes more current than system STOP mode but, as the oscillator continues to run, the full speed wake up time from this mode is significantly shorter.

- Stop: In this mode the oscillator is stopped and clocks are switched off. The counters and dividers remain frozen. The autonomous periodic interrupt (API) may remain active but has a very low power consumption. If the BDC is enabled in Stop mode, the VREG remains in full performance mode and the CPMU continues operation as in run mode. With BDC enabled and BDCCIS bit set, then all clocks remain active to allow BDC access to internal peripherals. If the BDC is enabled and BDCCIS is clear, then the BDCSI clock remains active, but bus and core clocks are disabled.

# 1.11 Security

The MCU security mechanism prevents unauthorized access to the flash memory. It must be emphasized that part of the security must lie with the application code. An extreme example would be application code that dumps the contents of the internal memory. This would defeat the purpose of security. Also, if an application has the capability of downloading code through a serial port and then executing that code (e.g. an application containing bootloader code), then this capability could potentially be used to read the EEPROM and Flash memory contents even when the microcontroller is in the secure state. In this example, the security of the application could be enhanced by requiring a response authentication before any code can be downloaded.

Device security details are also described in the flash block description.

### 1.11.1 Features

The security features of the S12Z chip family are:

- Prevent external access of the non-volatile memories (Flash, EEPROM) content

- Restrict execution of NVM commands

### 1.11.2 Securing the Microcontroller

The chip can be secured by programming the security bits located in the options/security byte in the Flash memory array. These non-volatile bits keep the device secured through reset and power-down.

#### Background Debug Controller (S12ZBDCV2)

| 0x1B                      | Data[31-24]      | Data[23-16]      | Data[15-8]       | Data[7-0]                 |             | BDCCSRL          |

|---------------------------|------------------|------------------|------------------|---------------------------|-------------|------------------|

| host $\rightarrow$ target | host →<br>target | host →<br>target | host →<br>target | host $\rightarrow$ target | D<br>L<br>Y | target →<br>host |

FILL\_MEM.sz\_WS

FILL\_MEM{\_WS} is used with the WRITE\_MEM{\_WS} command to access large blocks of memory. An initial WRITE\_MEM{\_WS} is executed to set up the starting address of the block and write the first datum. If an initial WRITE\_MEM{\_WS} is not executed before the first FILL\_MEM{\_WS}, an illegal command response is returned. The FILL\_MEM{\_WS} command stores subsequent operands. The initial address is incremented by the operand size (1, 2, or 4) and saved in a temporary register. Subsequent FILL\_MEM{\_WS} command size, and store the updated address in the temporary register. If the with-status option is specified, the BDCCSRL status byte is returned after the write data. This status byte reflects the state after the memory write was performed. If enabled an ACK pulse is generated after the internal write access has been completed or aborted. The effect of the access size and alignment on the next address to be accessed is explained in more detail in Section 5.4.5.2, "BDC Access Of Device Memory Mapped Resources"

### NOTE

FILL\_MEM{\_WS} is a valid command only when preceded by SYNC, NOP, WRITE\_MEM{\_WS}, or another FILL\_MEM{\_WS} command. Otherwise, an illegal command response is returned, setting the ILLCMD bit. NOP can be used for inter command padding without corrupting the address pointer.

The size field (sz) is examined each time a FILL\_MEM{\_WS} command is processed, allowing the operand size to be dynamically altered. The examples show the FILL\_MEM.B{\_WS}, FILL\_MEM.W{\_WS} and FILL\_MEM.L{\_WS} commands.

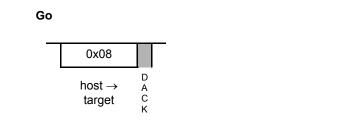

### 5.4.4.7 GO

Non-intrusive

This command is used to exit active BDM and begin (or resume) execution of CPU application code. The CPU pipeline is flushed and refilled before normal instruction execution resumes. Prefetching begins at the current address in the PC. If any register (such as the PC) is altered by a BDC command whilst in BDM, the updated value is used when prefetching resumes. If enabled, an ACK is driven on exiting active BDM.

If a GO command is issued whilst the BDM is inactive, an illegal command response is returned and the ILLCMD bit is set.

**Active Background**

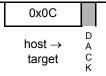

### 5.4.4.8 GO\_UNTIL

This command is used to exit active BDM and begin (or resume) execution of application code. The CPU pipeline is flushed and refilled before normal instruction execution resumes. Prefetching begins at the current address in the PC. If any register (such as the PC) is altered by a BDC command whilst in BDM, the updated value is used when prefetching resumes.

After resuming application code execution, if ACK is enabled, the BDC awaits a return to active BDM before driving an ACK pulse. timeouts do not apply when awaiting a GO\_UNTIL command ACK.

If a GO\_UNTIL is not acknowledged then a SYNC command must be issued to end the pending GO\_UNTIL.

If a GO\_UNTIL command is issued whilst BDM is inactive, an illegal command response is returned and the ILLCMD bit is set.

If ACK handshaking is disabled, the GO\_UNTIL command is identical to the GO command.

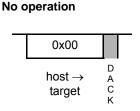

### 5.4.4.9 NOP

Active Background

NOP performs no operation and may be used as a null command where required.

### 5.4.4.10 READ\_Rn

#### Read CPU register

Active Background

| 0x60+CRN                  |        | Data [31-24]     | Data [23-16]     | Data [15-8]      | Data [7-0]       |

|---------------------------|--------|------------------|------------------|------------------|------------------|

| host $\rightarrow$ target | D<br>R | target →<br>host | target →<br>host | target →<br>host | target →<br>host |

This command reads the selected CPU registers and returns the 32-bit result. Accesses to CPU registers are always 32-bits wide, regardless of implemented register width. Bytes that are not implemented return zero. The register is addressed through the CPU register number (CRN). See Section 5.4.5.1, "BDC

# returned before the read data. This status byte reflects the state after the memory read was performed. If enabled, an ACK pulse is driven before the data bytes are transmitted.

The examples show the READ\_MEM.B{\_WS}, READ\_MEM.W{\_WS} and READ\_MEM.L{\_WS} commands.

# 5.4.4.12 READ\_DBGTB

Read DBG trace buffer

| 0x07             |                  | TB Line<br>[31-24] | TB Line<br>[23-16] | TB Line<br>[15-8] | TB Line<br>[7-0] |                  | TB Line<br>[63-56] | TB Line<br>[55-48] | TB Line<br>[47-40] | TB Line<br>[39-32] |

|------------------|------------------|--------------------|--------------------|-------------------|------------------|------------------|--------------------|--------------------|--------------------|--------------------|

| host →<br>target | D<br>A<br>C<br>K | target →<br>host   | target →<br>host   | target →<br>host  | target →<br>host | D<br>A<br>C<br>K | target →<br>host   | target →<br>host   | target →<br>host   | target →<br>host   |

This command is only available on devices, where the DBG module includes a trace buffer. Attempted use of this command on devices without a traace buffer return 0x00.

Read 64 bits from the DBG trace buffer. Refer to the DBG module description for more detailed information. If enabled an ACK pulse is generated before each 32-bit longword is ready to be read by the host. After issuing the first ACK a timeout is still possible whilst accessing the second 32-bit longword, since this requires separate internal accesses. The first 32-bit longword corresponds to trace buffer line bits[31:0]; the second to trace buffer line bits[63:32]. If ACK handshaking is disabled, the host must wait 16 clock cycles (DLY) after completing the first 32-bit read before starting the second 32-bit read.

### 5.4.4.13 READ\_SAME.sz, READ\_SAME.sz\_WS

#### READ\_SAME

Read same location specified by previous READ\_MEM{\_WS}

| 0x54                      |                  | Data[15-8]       | Data[7-0]        | I |

|---------------------------|------------------|------------------|------------------|---|

| host $\rightarrow$ target | D<br>A<br>C<br>K | target →<br>host | target →<br>host | - |

#### READ\_SAME\_WS

Read same location specified by previous READ\_MEM{\_WS}

| 0x55             |             | BDCCSRL          | Data [15-8]      | Data [7-0]       |  |

|------------------|-------------|------------------|------------------|------------------|--|

| host →<br>target | D<br>L<br>Y | target →<br>host | target →<br>host | target →<br>host |  |

#### MC912ZVL Family Reference Manual, Rev. 2.41

Background Debug Controller (S12ZBDCV2)

Non-intrusive

Non-intrusive

Non-intrusive

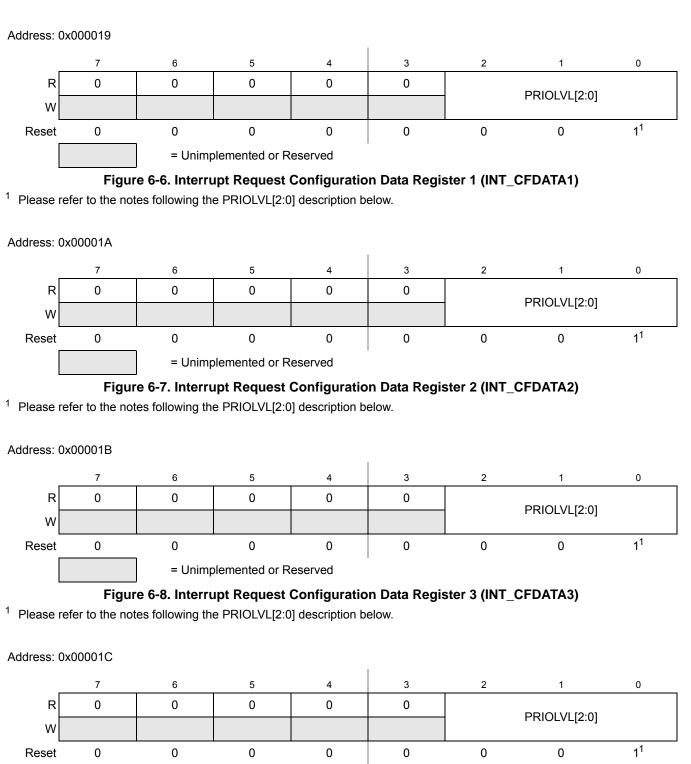

#### Interrupt (S12ZINTV0)

= Unimplemented or Reserved

### Figure 6-9. Interrupt Request Configuration Data Register 4 (INT\_CFDATA4)

<sup>1</sup> Please refer to the notes following the PRIOLVL[2:0] description below.

| Term | Definition                                                                                                                              |

|------|-----------------------------------------------------------------------------------------------------------------------------------------|

| BDM  | Background Debug Mode.<br>In this mode CPU application code execution is halted.<br>Execution of BDC "active BDM" commands is possible. |

| BDC  | Background Debug Controller                                                                                                             |

| WORD | 16-bit data entity                                                                                                                      |

| CPU  | S12Z CPU module                                                                                                                         |

#### Table 7-2. Glossary Of Terms

### 7.1.2 Overview

The comparators monitor the bus activity of the CPU. A single comparator match or a series of matches can generate breakpoints. A state sequencer determines if the correct series of matches occurs. Similarly an external event can generate breakpoints.

### 7.1.3 Features

- Three comparators (A, B, and D)

- Comparator A compares the full address bus and full 32-bit data bus

- Comparator A features a data bus mask register

- Comparators B and D compare the full address bus only

- Each comparator can be configured to monitor PC addresses or addresses of data accesses

- Each comparator can select either read or write access cycles

- Comparator matches can force state sequencer state transitions

- Three comparator modes

- Simple address/data comparator match mode

- Inside address range mode, Addmin  $\leq$  Address  $\leq$  Addmax

- Outside address range match mode, Address < Addmin or Address > Addmax

- State sequencer control

- State transitions forced by comparator matches

- State transitions forced by software write to TRIG

- State transitions forced by an external event

- The following types of breakpoints

- CPU breakpoint entering active BDM on breakpoint (BDM)

- CPU breakpoint executing SWI on breakpoint (SWI)

# 10.7 Resets

At reset the ADC12B\_LBA is disabled and in a power down state. The reset state of each individual bit is listed within Section 10.5.2, "Register Descriptions" which details the registers and their bit-fields.

# 10.8 Interrupts

The ADC supports three types of interrupts:

- Conversion Interrupt

- Sequence Abort Interrupt

- Error and Conversion Flow Control Issue Interrupt

Each of the interrupt types is associated with individual interrupt enable bits and interrupt flags.

# **10.8.1 ADC Conversion Interrupt**

The ADC provides one conversion interrupt associated to 16 interrupt enable bits with dedicated interrupt flags. The 16 interrupt flags consist of:

- 15 conversion interrupt flags which can be associated to any conversion completion.

- One additional interrupt flag which is fixed to the "End Of List" conversion command type within the active CSL.

The association of the conversion number with the interrupt flag number is done in the conversion command.

# **10.8.2** ADC Sequence Abort Done Interrupt

The ADC provides one sequence abort done interrupt associated with the sequence abort request for conversion flow control. Hence, there is only one dedicated interrupt flag and interrupt enable bit for conversion sequence abort and it occurs when the sequence abort is done.

Scalable Controller Area Network (S12MSCANV2)

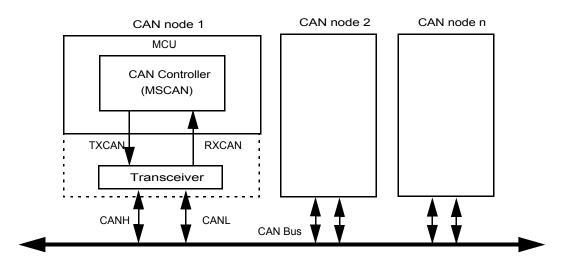

# 13.2 External Signal Description

The MSCAN uses two external pins.

### NOTE

On MCUs with an integrated CAN physical interface (transceiver) the MSCAN interface is connected internally to the transceiver interface. In these cases the external availability of signals TXCAN and RXCAN is optional.

# 13.2.1 RXCAN — CAN Receiver Input Pin

RXCAN is the MSCAN receiver input pin.

# 13.2.2 TXCAN — CAN Transmitter Output Pin

TXCAN is the MSCAN transmitter output pin. The TXCAN output pin represents the logic level on the CAN bus:

0 = Dominant state

1 =Recessive state

# 13.2.3 CAN System

A typical CAN system with MSCAN is shown in Figure 13-2. Each CAN station is connected physically to the CAN bus lines through a transceiver device. The transceiver is capable of driving the large current needed for the CAN bus and has current protection against defective CAN or defective stations.

Figure 13-2. CAN System

# **13.3 Memory Map and Register Definition**

This section provides a detailed description of all registers accessible in the MSCAN.

# 13.3.1 Module Memory Map

Figure 13-3 gives an overview on all registers and their individual bits in the MSCAN memory map. The *register address* results from the addition of *base address* and *address offset*. The *base address* is determined at the MCU level and can be found in the MCU memory map description. The *address offset* is defined at the module level.

The MSCAN occupies 64 bytes in the memory space. The base address of the MSCAN module is determined at the MCU level when the MCU is defined. The register decode map is fixed and begins at the first address of the module address offset.

The detailed register descriptions follow in the order they appear in the register map.

| Field             | Description                                                                                                                                                                                                                                                                                                                |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5-4<br>IDAM[1:0]  | <b>Identifier Acceptance Mode</b> — The CPU sets these flags to define the identifier acceptance filter organization (see Section 13.4.3, "Identifier Acceptance Filter"). Table 13-19 summarizes the different settings. In filter closed mode, no message is accepted such that the foreground buffer is never reloaded. |

| 2-0<br>IDHIT[2:0] | Identifier Acceptance Hit Indicator — The MSCAN sets these flags to indicate an identifier acceptance hit (see Section 13.4.3, "Identifier Acceptance Filter"). Table 13-20 summarizes the different settings.                                                                                                             |

#### Table 13-18. CANIDAC Register Field Descriptions

| IDAM1 | IDAM0 | Identifier Acceptance Mode     |

|-------|-------|--------------------------------|

| 0     | 0     | Two 32-bit acceptance filters  |

| 0     | 1     | Four 16-bit acceptance filters |

| 1     | 0     | Eight 8-bit acceptance filters |

| 1     | 1     | Filter closed                  |

#### Table 13-19. Identifier Acceptance Mode Settings

#### Table 13-20. Identifier Acceptance Hit Indication

| IDHIT2 | IDHIT1 | IDHIT0 | Identifier Acceptance Hit |

|--------|--------|--------|---------------------------|

| 0      | 0      | 0      | Filter 0 hit              |

| 0      | 0      | 1      | Filter 1 hit              |

| 0      | 1      | 0      | Filter 2 hit              |

| 0      | 1      | 1      | Filter 3 hit              |

| 1      | 0      | 0      | Filter 4 hit              |

| 1      | 0      | 1      | Filter 5 hit              |

| 1      | 1      | 0      | Filter 6 hit              |

| 1      | 1      | 1      | Filter 7 hit              |

The IDHITx indicators are always related to the message in the foreground buffer (RxFG). When a message gets shifted into the foreground buffer of the receiver FIFO the indicators are updated as well.

### 13.3.2.13 MSCAN Reserved Registers

These registers are reserved for factory testing of the MSCAN module and is not available in normal system operating modes.

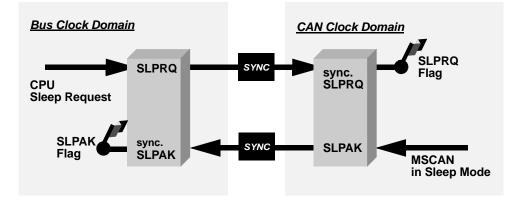

# 13.4.5.5 MSCAN Sleep Mode

The CPU can request the MSCAN to enter this low power mode by asserting the SLPRQ bit in the CANCTL0 register. The time when the MSCAN enters sleep mode depends on a fixed synchronization delay and its current activity:

- If there are one or more message buffers scheduled for transmission (TXEx = 0), the MSCAN will continue to transmit until all transmit message buffers are empty (TXEx = 1, transmitted successfully or aborted) and then goes into sleep mode.

- If the MSCAN is receiving, it continues to receive and goes into sleep mode as soon as the CAN bus next becomes idle.

- If the MSCAN is neither transmitting nor receiving, it immediately goes into sleep mode.

Figure 13-45. Sleep Request / Acknowledge Cycle

### NOTE

The application software must avoid setting up a transmission (by clearing one or more TXEx flag(s)) and immediately request sleep mode (by setting SLPRQ). Whether the MSCAN starts transmitting or goes into sleep mode directly depends on the exact sequence of operations.

If sleep mode is active, the SLPRQ and SLPAK bits are set (Figure 13-45). The application software must use SLPAK as a handshake indication for the request (SLPRQ) to go into sleep mode.

When in sleep mode (SLPRQ = 1 and SLPAK = 1), the MSCAN stops its internal clocks. However, clocks that allow register accesses from the CPU side continue to run.

If the MSCAN is in bus-off state, it stops counting the 128 occurrences of 11 consecutive recessive bits due to the stopped clocks. TXCAN remains in a recessive state. If RXF = 1, the message can be read and RXF can be cleared. Shifting a new message into the foreground buffer of the receiver FIFO (RxFG) does not take place while in sleep mode.

It is possible to access the transmit buffers and to clear the associated TXE flags. No message abort takes place while in sleep mode.

#### Table 17-10. PWMCTL Field Descriptions

Note: Bits related to available channels have functional significance. Writing to unavailable bits has no effect. Read from unavailable bits return a zero

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CON67 | <ul> <li>Concatenate Channels 6 and 7</li> <li>Channels 6 and 7 are separate 8-bit PWMs.</li> <li>Channels 6 and 7 are concatenated to create one 16-bit PWM channel. Channel 6 becomes the high order byte and channel 7 becomes the low order byte. Channel 7 output pin is used as the output for this 16-bit PWM (bit 7 of port PWMP). Channel 7 clock select control-bit determines the clock source, channel 7 polarity bit determines the polarity, channel 7 enable bit enables the output and channel 7 center aligned enable bit determines the output mode.</li> </ul>                                                                                                                                                                                                                                                          |

| 6<br>CON45 | <ul> <li>Concatenate Channels 4 and 5</li> <li>Channels 4 and 5 are separate 8-bit PWMs.</li> <li>Channels 4 and 5 are concatenated to create one 16-bit PWM channel. Channel 4 becomes the high order byte and channel 5 becomes the low order byte. Channel 5 output pin is used as the output for this 16-bit PWM (bit 5 of port PWMP). Channel 5 clock select control-bit determines the clock source, channel 5 polarity bit determines the polarity, channel 5 enable bit enables the output and channel 5 center aligned enable bit determines the output mode.</li> </ul>                                                                                                                                                                                                                                                          |

| 5<br>CON23 | <ul> <li>Concatenate Channels 2 and 3</li> <li>Channels 2 and 3 are separate 8-bit PWMs.</li> <li>Channels 2 and 3 are concatenated to create one 16-bit PWM channel. Channel 2 becomes the high order byte and channel 3 becomes the low order byte. Channel 3 output pin is used as the output for this 16-bit PWM (bit 3 of port PWMP). Channel 3 clock select control-bit determines the clock source, channel 3 polarity bit determines the polarity, channel 3 enable bit enables the output and channel 3 center aligned enable bit determines the output mode.</li> </ul>                                                                                                                                                                                                                                                          |

| 4<br>CON01 | <ul> <li>Concatenate Channels 0 and 1</li> <li>Channels 0 and 1 are separate 8-bit PWMs.</li> <li>Channels 0 and 1 are concatenated to create one 16-bit PWM channel. Channel 0 becomes the high order byte and channel 1 becomes the low order byte. Channel 1 output pin is used as the output for this 16-bit PWM (bit 1 of port PWMP). Channel 1 clock select control-bit determines the clock source, channel 1 polarity bit determines the polarity, channel 1 enable bit enables the output and channel 1 center aligned enable bit determines the output mode.</li> </ul>                                                                                                                                                                                                                                                          |

| 3<br>PSWAI | <ul> <li>PWM Stops in Wait Mode — Enabling this bit allows for lower power consumption in wait mode by disabling the input clock to the prescaler.</li> <li>0 Allow the clock to the prescaler to continue while in wait mode.</li> <li>1 Stop the input clock to the prescaler whenever the MCU is in wait mode.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2<br>PFRZ  | <ul> <li>PWM Counters Stop in Freeze Mode — In freeze mode, there is an option to disable the input clock to the prescaler by setting the PFRZ bit in the PWMCTL register. If this bit is set, whenever the MCU is in freeze mode, the input clock to the prescaler is disabled. This feature is useful during emulation as it allows the PWM function to be suspended. In this way, the counters of the PWM can be stopped while in freeze mode so that once normal program flow is continued, the counters are re-enabled to simulate real-time operations. Since the registers can still be accessed in this mode, to re-enable the prescaler clock, either disable the PFRZ bit or exit freeze mode.</li> <li>1 Disable PWM input clock to the prescaler whenever the part is in freeze mode. This is useful for emulation.</li> </ul> |

# 17.3.2.7 PWM Clock A/B Select Register (PWMCLKAB)

Each PWM channel has a choice of four clocks to use as the clock source for that channel as described below.

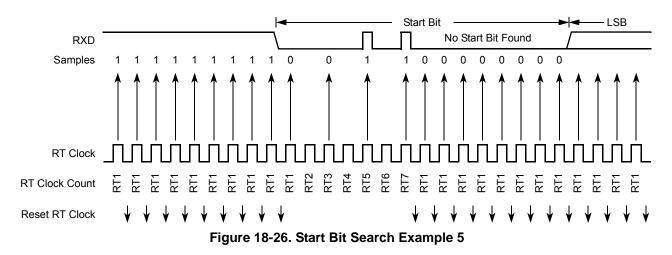

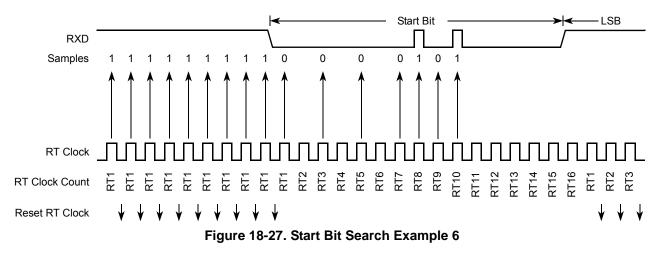

In Figure 18-27, a noise burst makes the majority of data samples RT8, RT9, and RT10 high. This sets the noise flag but does not reset the RT clock. In start bits only, the RT8, RT9, and RT10 data samples are ignored.

### 18.4.6.4 Framing Errors

If the data recovery logic does not detect a logic 1 where the stop bit should be in an incoming frame, it sets the framing error flag, FE, in SCI status register 1 (SCISR1). A break character also sets the FE flag because a break character has no stop bit. The FE flag is set at the same time that the RDRF flag is set.

### 18.4.6.5 Baud Rate Tolerance

A transmitting device may be operating at a baud rate below or above the receiver baud rate. Accumulated bit time misalignment can cause one of the three stop bit data samples (RT8, RT9, and RT10) to fall outside the actual stop bit. A noise error will occur if the RT8, RT9, and RT10 samples are not all the same logical values. A framing error will occur if the receiver clock is misaligned in such a way that the majority of the RT8, RT9, and RT10 stop bit samples are a logic zero.

from where was during the previous transmission. It is not possible for the IIC to wake up the CPU when its internal clocks are stopped.

If it were the case that the IBSWAI bit was cleared when the WAI instruction was executed, the IIC internal clocks and interface would remain alive, continuing the operation which was currently underway. It is also possible to configure the IIC such that it will wake up the CPU via an interrupt at the conclusion of the current operation. See the discussion on the IBIF and IBIE bits in the IBSR and IBCR, respectively.

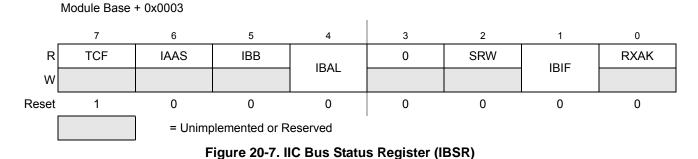

# 20.3.1.4 IIC Status Register (IBSR)

This status register is read-only with exception of bit 1 (IBIF) and bit 4 (IBAL), which are software clearable.

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TCF  | <ul> <li>Data Transferring Bit — While one byte of data is being transferred, this bit is cleared. It is set by the falling edge of the 9th clock of a byte transfer. Note that this bit is only valid during or immediately following a transfer to the IIC module or from the IIC module.</li> <li>0 Transfer in progress</li> <li>1 Transfer complete</li> </ul>                                                                                                                                                                                                                                                                                                                                                                  |

| 6<br>IAAS | <ul> <li>Addressed as a Slave Bit — When its own specific address (I-bus address register) is matched with the calling address or it receives the general call address with GCEN== 1,this bit is set. The CPU is interrupted provided the IBIE is set. Then the CPU needs to check the SRW bit and set its Tx/Rx mode accordingly. Writing to the I-bus control register clears this bit.</li> <li>0 Not addressed</li> <li>1 Addressed as a slave</li> </ul>                                                                                                                                                                                                                                                                        |

| 5<br>IBB  | <ul> <li>Bus Busy Bit</li> <li>0 This bit indicates the status of the bus. When a START signal is detected, the IBB is set. If a STOP signal is detected, IBB is cleared and the bus enters idle state.</li> <li>1 Bus is busy</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4<br>IBAL | <ul> <li>Arbitration Lost — The arbitration lost bit (IBAL) is set by hardware when the arbitration procedure is lost. Arbitration is lost in the following circumstances:         <ol> <li>SDA sampled low when the master drives a high during an address or data transmit cycle.</li> <li>SDA sampled low when the master drives a high during the acknowledge bit of a data receive cycle.</li> <li>A start cycle is attempted when the bus is busy.</li> <li>A repeated start cycle is requested in slave mode.</li> <li>A stop condition is detected when the master did not request it.</li> </ol> </li> <li>This bit must be cleared by software, by writing a one to it. A write of 0 has no effect on this bit.</li> </ul> |

#### Table 20-9. IBSR Field Descriptions

# 20.4.1.8 Handshaking

The clock synchronization mechanism can be used as a handshake in data transfer. Slave devices may hold the SCL low after completion of one byte transfer (9 bits). In such case, it halts the bus clock and forces the master clock into wait states until the slave releases the SCL line.

# 20.4.1.9 Clock Stretching

The clock synchronization mechanism can be used by slaves to slow down the bit rate of a transfer. After the master has driven SCL low the slave can drive SCL low for the required period and then release it. If the slave SCL low period is greater than the master SCL low period then the resulting SCL bus signal low period is stretched.

### 20.4.1.10 Ten-bit Address

A ten-bit address is indicated if the first 5 bits of the first address byte are 0x11110. The following rules apply to the first address byte.

| SLAVE<br>ADDRESS | R/W BIT | DESCRIPTION                          |

|------------------|---------|--------------------------------------|

| 0000000          | 0       | General call address                 |

| 0000010          | Х       | Reserved for different bus<br>format |

| 0000011          | х       | Reserved for future purposes         |

| 11111XX          | х       | Reserved for future purposes         |

| 11110XX          | Х       | 10-bit slave addressing              |

Figure 20-13. Definition of bits in the first byte.

The address type is identified by ADTYPE. When ADTYPE is 0, 7-bit address is applied. Reversely, the address is 10-bit address.Generally, there are two cases of 10-bit address.See the Figure 20-14 and Figure 20-15.

| s | Slave Add1st 7bits<br>11110+ADR10+ADR9 | R/W<br>0 | A1 | Slave Add 2nd byte<br>ADR[8:1] | A2 | Data | A3 |  |

|---|----------------------------------------|----------|----|--------------------------------|----|------|----|--|

|---|----------------------------------------|----------|----|--------------------------------|----|------|----|--|

Figure 20-14. A master-transmitter addresses a slave-receiver with a 10-bit address

| 1 11110+ADR10+ADR9 0 ADR[8:1] 11110+ADR10+ADR9 1 | s | Slave Add1st 7bits<br>11110+ADR10+ADR9 | R/W<br>0 | A1 | Slave Add 2nd byte<br>ADR[8:1] | A2 | Sr | Slave Add 1st 7bits<br>11110+ADR10+ADR9 | R/W<br>1 | A3 | Data | A4 |

|--------------------------------------------------|---|----------------------------------------|----------|----|--------------------------------|----|----|-----------------------------------------|----------|----|------|----|

|--------------------------------------------------|---|----------------------------------------|----------|----|--------------------------------|----|----|-----------------------------------------|----------|----|------|----|

### Figure 20-15. A master-receiver addresses a slave-transmitter with a 10-bit address.

In the Figure 20-15, the first two bytes are the similar to Figure 20-14. After the repeated START(Sr), the first slave address is transmitted again, but the R/W is 1, meaning that the slave is acted as a transmitter.

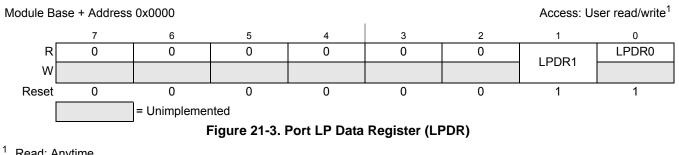

# 21.3.2.1 Port LP Data Register (LPDR)

Read: Anytime Write: Anytime

#### Table 21-2. LPDR Field Description

| Field      | Description                                                                                                                                                                                                                                                                    |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>LPDR1 | Port LP Data Bit 1 — The S12LINPHYV2 LPTxD input (see Figure 21-1) can be directly controlled by this register bit. The routing of the LPTxD input is done in the Port Inetrgation Module (PIM). Please refer to the PIM chapter of the device Reference Manual for more info. |

| 0<br>LPDR0 | Port LP Data Bit 0 — Read-only bit. The S12LINPHYV2 LPRxD output state can be read at any time.                                                                                                                                                                                |

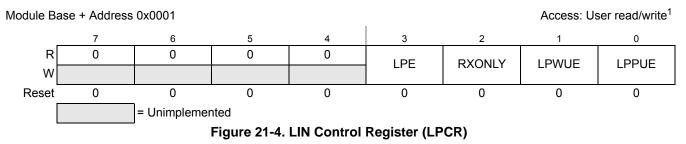

# 21.3.2.2 LIN Control Register (LPCR)

<sup>1</sup> Read: Anytime

Write: Anytime,

#### Table 21-3. LPCR Field Description

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3<br>LPE    | <ul> <li>LIN Enable Bit — If set, this bit enables the LIN Physical Layer.</li> <li>The LIN Physical Layer is in shutdown mode. None of the LIN Physical Layer functions are available, except that the bus line is held in its recessive state by a high ohmic (330kΩ) resistor. All registers are normally accessible.</li> <li>The LIN Physical Layer is not in shutdown mode.</li> </ul> |

| 2<br>RXONLY | Receive Only Mode bit — This bit controls RXONLY mode.<br>0 The LIN Physical Layer is not in receive only mode.<br>1 The LIN Physical Layer is in receive only mode.                                                                                                                                                                                                                         |

# G.1 Static Electrical Characteristics

#### Table G-1. Static Electrical Characteristics - dac\_8b5v\_analog\_II18 @5V VDDA

Characteristics noted under conditions  $4.85V \le V_{DDA} \le 5.15V$ ,  $-40^{\circ}C \le T_{J} \le 175^{\circ}C$ ,  $V_{RH} = V_{DDA}$ ,  $V_{RL} = V_{SSA}$  unless otherwise noted. Typical values noted reflect the approximate parameter mean at  $T_{A} = 25^{\circ}C$  under nominal conditions unless otherwise noted.

| Num | Ratings                                                                                                                                                                                                                                                                                                                               | Symbol              | Min                                                          | Тур              | Max                    | Unit |  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------------------------------------------|------------------|------------------------|------|--|

| 1   | Supply Current of dac_8b5v_analog_ll18<br>buffer disabled<br>buffer enabled FVR=0 DRIVE=1<br>buffer enabled FVR=1 DRIVE=0                                                                                                                                                                                                             | l <sub>buf</sub>    |                                                              | -<br>365<br>215  | 5<br>800<br>800        | μA   |  |

| 2   | Reference current<br>reference disabled<br>reference enabled                                                                                                                                                                                                                                                                          | I <sub>ref</sub>    | -                                                            | -<br>50          | 1<br>150               | μA   |  |

| 3   | Resolution                                                                                                                                                                                                                                                                                                                            |                     |                                                              | 8                |                        | bit  |  |

| 4   | Relative Accuracy measured at AMP -40°C < $T_J \le 150^{\circ}C$ 150°C < $T_J < 175^{\circ}C$                                                                                                                                                                                                                                         | INL                 | -0.5<br>-0.75                                                | LSB              |                        |      |  |

| 5   | $ \begin{array}{c c} \text{Differential Nonlinearity measure at AMP} \\ -40^{\circ}\text{C} < \text{T}_{\text{J}} \leq 150^{\circ}\text{C} \\ 150^{\circ}\text{C} < \text{T}_{\text{J}} < 175^{\circ}\text{C} \end{array} \end{array} \begin{array}{c c} \text{DNL} & -0.5 \\ -0.75 \\ -0.75 \end{array} + 0.5 \\ +0.75 \end{array} $ |                     |                                                              |                  |                        |      |  |

| 6   | DAC Range A (FVR bit = 1)                                                                                                                                                                                                                                                                                                             | V <sub>out</sub>    | 0255/256(V <sub>RH</sub> -V <sub>RL</sub> )+V <sub>RL</sub>  |                  |                        |      |  |

| 7   | DAC Range B (FVR bit = 0                                                                                                                                                                                                                                                                                                              | 32287               | 32287/320(V <sub>RH</sub> -V <sub>RL</sub> )+V <sub>RL</sub> |                  |                        |      |  |

| 8   | Output Voltage<br>unbuffered range A or B (load >= $50M\Omega$ )                                                                                                                                                                                                                                                                      | V <sub>out</sub>    | full D                                                       | V                |                        |      |  |

| 9   | Output Voltage (DRIVE bit = 0) <sup>*)</sup><br>buffered range A (load >= $100K\Omega$ to VSSA) or<br>buffered range A (load >= $100K\Omega$ to VDDA)                                                                                                                                                                                 | V <sub>out</sub>    | 0 - V <sub>DDA</sub> -0.15<br>0.15 - V <sub>DDA</sub>        |                  |                        | V    |  |

|     | buffered range B (load >= $100K\Omega$ to VSSA)<br>buffered range B (load >= $100K\Omega$ to VDDA)                                                                                                                                                                                                                                    | Vout                |                                                              |                  |                        |      |  |

| 10  | Output Voltage (DRIVE bit = 1) <sup>**)</sup><br>buffered range B with $6.4K\Omega$ load into resistor<br>divider of $800\Omega$ / $6.56K\Omega$ between VDDA and<br>VSSA.<br>(equivalent load is >= $65K\Omega$ to VSSA) or<br>(equivalent load is >= $7.5K\Omega$ to VDDA)                                                          | V <sub>out</sub>    | full DAC Range B                                             |                  |                        |      |  |

| 11  | Buffer Output Capacitive load                                                                                                                                                                                                                                                                                                         | C <sub>load</sub>   | 0 - 100                                                      |                  |                        | pF   |  |

| 12  | Buffer Output Offset                                                                                                                                                                                                                                                                                                                  | V <sub>offset</sub> | -30                                                          | -                | +30                    | mV   |  |

| 13  | Settling time                                                                                                                                                                                                                                                                                                                         | t <sub>delay</sub>  | -                                                            | 3                | 5                      | μS   |  |

| 14  | Reverence voltage high                                                                                                                                                                                                                                                                                                                | V <sub>refh</sub>   | V <sub>DDA</sub> -0.1V                                       | V <sub>DDA</sub> | V <sub>DDA</sub> +0.1V | V    |  |

\*) DRIVE bit = 1 is not recomended in this case.

#### **ACMP Electrical Specifications**

# O.20 0x07C0-0x07C7 IIC0

| Address  | Name        | _      | Bit 7 | 6      | 5      | 4     | 3      | 2     | 1    | Bit 0  |  |  |  |

|----------|-------------|--------|-------|--------|--------|-------|--------|-------|------|--------|--|--|--|

| 0x07C0   | IBAD        | R<br>W | ADR7  | ADR6   | ADR5   | ADR4  | ADR3   | ADR2  | ADR1 | 0      |  |  |  |

| 0x07C1   | IBFD        | R<br>W | IBC7  | IBC6   | IBC5   | IBC4  | IBC3   | IBC2  | IBC1 | IBC0   |  |  |  |

| 0x07C2   | IBCR        | R      | IBEN  | IBIE   | MS/SL  | Tx/Rx | ТХАК   | 0     | 0    | IBSWAI |  |  |  |

| 0,0102   | IDOIX       | W      | IDEN  | IDIE   | WIO/OL |       | 170 11 | RSTA  |      | IBOWAI |  |  |  |

| 0x07C3   | IBSR        | R      | TCF   | IAAS   | IBB    | IBAL  | 0      | SRW   | IBIF | RXAK   |  |  |  |

| 0,07 00  | IBOIR       | W W    | W     |        |        |       |        |       |      |        |  |  |  |

| 0x07C4   | IBDR        | R<br>W | D7    | D6     | D5     | D4    | D3     | D2    | D1   | D0     |  |  |  |

| 0x07C5   | IBCR2       | R      | GCEN  | ADTYPE | 0      | 0     | 0      | ADR10 | ADR9 | ADR8   |  |  |  |

| 010705   | IDUKZ       | IDUNZ  |       | IDONZ  | W      | GOLN  | AUTHE  |       |      |        |  |  |  |

| 0x07C6 - | Reserved    | R      | 0     | 0      | 0      | 0     | 0      | 0     | 0    | 0      |  |  |  |

| 0x07C7   | i vesel veu | W      |       |        |        |       |        |       |      |        |  |  |  |