Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | S12Z                                                                     |

| Core Size                  | 16-Bit                                                                   |

| Speed                      | 32MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SCI, SPI, UART/USART                     |

| Peripherals                | LVD, POR, PWM, WDT                                                       |

| Number of I/O              | 34                                                                       |

| Program Memory Size        | 32KB (32K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 1K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 5.5V ~ 18V                                                               |

| Data Converters            | A/D 10x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 48-LQFP                                                                  |

| Supplier Device Package    | 48-LQFP (7x7)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12zvl32f0mlfr |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| External | I Signal Description                                                                                           | 181                                                                                                                 |

|----------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| 7.2.1    | External Event Input                                                                                           | 181                                                                                                                 |

| Memory   | Map and Registers                                                                                              | 182                                                                                                                 |

| 7.3.1    | Module Memory Map                                                                                              | 182                                                                                                                 |

| 7.3.2    | Register Descriptions                                                                                          | 184                                                                                                                 |

| Function | nal Description                                                                                                | 196                                                                                                                 |

| 7.4.1    | DBG Operation                                                                                                  | 196                                                                                                                 |

| 7.4.2    | Comparator Modes                                                                                               | 197                                                                                                                 |

| 7.4.3    | Events                                                                                                         | 200                                                                                                                 |

| 7.4.4    | State Sequence Control                                                                                         | 202                                                                                                                 |

| 7.4.5    | Breakpoints                                                                                                    | 202                                                                                                                 |

| Applica  | tion Information                                                                                               | 204                                                                                                                 |

| 7.5.1    | Avoiding Unintended Breakpoint Re-triggering                                                                   | 204                                                                                                                 |

| 7.5.2    | Breakpoints from other S12Z sources                                                                            | 204                                                                                                                 |

|          | 7.2.1<br>Memory<br>7.3.1<br>7.3.2<br>Function<br>7.4.1<br>7.4.2<br>7.4.3<br>7.4.4<br>7.4.5<br>Applica<br>7.5.1 | 7.4.4State Sequence Control7.4.5BreakpointsApplication Information7.5.1Avoiding Unintended Breakpoint Re-triggering |

# Chapter 8 ECC Generation Module (SRAM\_ECCV2)

| 8.1 | Introduc | xtion                           |   | 05 |

|-----|----------|---------------------------------|---|----|

|     | 8.1.1    | Features                        |   | 05 |

| 8.2 | Memory   | / Map and Register Definition   |   | 06 |

|     | 8.2.1    | Register Summary                |   | 06 |

|     | 8.2.2    | Register Descriptions           |   | 08 |

| 8.3 | Function | nal Description                 |   | 12 |

|     | 8.3.1    | Aligned Memory Write Access     |   | 13 |

|     | 8.3.2    | Non-aligned Memory Write Access |   | 13 |

|     | 8.3.3    | Memory Read Access              |   | 14 |

|     | 8.3.4    | Memory Initialization           |   | 14 |

|     | 8.3.5    | Interrupt Handling              | 2 | 14 |

|     | 8.3.6    | ECC Algorithm                   | 2 | 15 |

|     | 8.3.7    | ECC Debug Behavior              | 2 | 15 |

|     |          |                                 |   |    |

# Chapter 9

# S12 Clock, Reset and Power Management Unit (S12CPMU\_UHV)

| 9.1 | Introdu  | ction                                        |  |

|-----|----------|----------------------------------------------|--|

|     | 9.1.1    | Features                                     |  |

|     | 9.1.2    | Modes of Operation                           |  |

|     | 9.1.3    | S12CPMU_UHV Block Diagram                    |  |

| 9.2 | Signal I | Description                                  |  |

|     | 9.2.1    | RESET                                        |  |

|     | 9.2.2    | EXTAL and XTAL                               |  |

|     | 9.2.3    | VSUP — Regulator Power Input Pin             |  |

|     | 9.2.4    | VDDA, VSSA — Regulator Reference Supply Pins |  |

|     | 9.2.5    | VDDX, VSSX — Pad Supply Pins                 |  |

|     | 9.2.6    | BCTL — Base Control Pin for external PNP     |  |

|     |          |                                              |  |

# 5.1.1 Glossary

| Term  | Definition                                                                                               |  |  |  |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| DBG   | On chip Debug Module                                                                                     |  |  |  |  |  |  |

| BDM   | Active Background Debug Mode                                                                             |  |  |  |  |  |  |

| CPU   | S12Z CPU                                                                                                 |  |  |  |  |  |  |

| SSC   | Special Single Chip Mode (device operating mode                                                          |  |  |  |  |  |  |

| NSC   | Normal Single Chip Mode (device operating mode)                                                          |  |  |  |  |  |  |

| BDCSI | Background Debug Controller Serial Interface. This refers to the single pin BKGD serial interface.       |  |  |  |  |  |  |

| EWAIT | Optional S12 feature which allows external devices to delay external accesses until deassertion of EWAIT |  |  |  |  |  |  |

### 5.1.2 Features

The BDC includes these distinctive features:

- Single-wire communication with host development system

- SYNC command to determine communication rate

- Genuine non-intrusive handshake protocol

- Enhanced handshake protocol for error detection and stop mode recognition

- Active out of reset in special single chip mode

- Most commands not requiring active BDM, for minimal CPU intervention

- Full global memory map access without paging

- Simple flash mass erase capability

### 5.1.3 Modes of Operation

S12 devices feature power modes (run, wait, and stop) and operating modes (normal single chip, special single chip). Furthermore, the operation of the BDC is dependent on the device security status.

### 5.1.3.1 BDC Modes

The BDC features module specific modes, namely disabled, enabled and active. These modes are dependent on the device security and operating mode. In active BDM the CPU ceases execution, to allow BDC system access to all internal resources including CPU internal registers.

### 5.1.3.2 Security and Operating mode Dependency

In device run mode the BDC dependency is as follows

• Normal modes, unsecure device

General BDC operation available. The BDC is disabled out of reset.

# returned before the read data. This status byte reflects the state after the memory read was performed. If enabled, an ACK pulse is driven before the data bytes are transmitted.

The examples show the READ\_MEM.B{\_WS}, READ\_MEM.W{\_WS} and READ\_MEM.L{\_WS} commands.

# 5.4.4.12 READ\_DBGTB

Read DBG trace buffer

| 0x07             |                  | TB Line<br>[31-24] | TB Line<br>[23-16] | TB Line<br>[15-8] | TB Line<br>[7-0] |                  | TB Line<br>[63-56] | TB Line<br>[55-48] | TB Line<br>[47-40] | TB Line<br>[39-32] |

|------------------|------------------|--------------------|--------------------|-------------------|------------------|------------------|--------------------|--------------------|--------------------|--------------------|

| host →<br>target | D<br>A<br>C<br>K | target →<br>host   | target →<br>host   | target →<br>host  | target →<br>host | D<br>A<br>C<br>K | target →<br>host   | target →<br>host   | target →<br>host   | target →<br>host   |

This command is only available on devices, where the DBG module includes a trace buffer. Attempted use of this command on devices without a traace buffer return 0x00.

Read 64 bits from the DBG trace buffer. Refer to the DBG module description for more detailed information. If enabled an ACK pulse is generated before each 32-bit longword is ready to be read by the host. After issuing the first ACK a timeout is still possible whilst accessing the second 32-bit longword, since this requires separate internal accesses. The first 32-bit longword corresponds to trace buffer line bits[31:0]; the second to trace buffer line bits[63:32]. If ACK handshaking is disabled, the host must wait 16 clock cycles (DLY) after completing the first 32-bit read before starting the second 32-bit read.

### 5.4.4.13 READ\_SAME.sz, READ\_SAME.sz\_WS

#### READ\_SAME

Read same location specified by previous READ\_MEM{\_WS}

| 0x54                      |                  | Data[15-8]       | Data[7-0]        | I |

|---------------------------|------------------|------------------|------------------|---|

| host $\rightarrow$ target | D<br>A<br>C<br>K | target →<br>host | target →<br>host | - |

#### READ\_SAME\_WS

Read same location specified by previous READ\_MEM{\_WS}

| 0x55             |             | BDCCSRL          | Data [15-8]      | Data [7-0]       |  |

|------------------|-------------|------------------|------------------|------------------|--|

| host →<br>target | D<br>L<br>Y | target →<br>host | target →<br>host | target →<br>host |  |

#### MC912ZVL Family Reference Manual, Rev. 2.41

Background Debug Controller (S12ZBDCV2)

Non-intrusive

Non-intrusive

Non-intrusive

S12 Clock, Reset and Power Management Unit (S12CPMU\_UHV)

# 9.3 Memory Map and Registers

This section provides a detailed description of all registers accessible in the S12CPMU\_UHV.

### 9.3.1 Module Memory Map

The S12CPMU\_UHV registers are shown in Figure 9-3.

| Address<br>Offset | Register<br>Name  |        | Bit 7  | 6          | 5             | 4              | 3     | 2          | 1             | Bit 0          |          |  |

|-------------------|-------------------|--------|--------|------------|---------------|----------------|-------|------------|---------------|----------------|----------|--|

| 0x0000            | RESERVED          | R      | 0      | 0          | 0             | 0              | 0     | 0          | 0             | 0              |          |  |

| 0,0000            | RESERVED          | W      |        |            |               |                |       |            |               |                |          |  |

| 0.0004            | RESERVED          | R      | 0      | 0          | 0             | 0              | U     | U          | U             | U              |          |  |

| 0x0001            | CPMU<br>VREGTRIM0 | W      |        |            |               |                |       |            |               |                |          |  |

| 0 0000            | RESERVED          | R      | 0      | 0          | U             | U              | U     | U          | U             | U              |          |  |

| 0x0002            | CPMU<br>VREGTRIM1 | W      |        |            |               |                |       |            |               |                |          |  |

| 0x0003            | CPMURFLG          | R      | 0      | PORF       | LVRF          | 0              | COPRF | 0          | OMRF          | PMRF           |          |  |

| Chebbe            |                   | W      |        | i ora      | 2010          |                | 00114 |            | 0             |                |          |  |

| 0x0004            | CPMU<br>SYNR      | R<br>W | VCOFR  | Q[1:0]     |               |                | SYND  | IV[5:0]    |               |                |          |  |

| 0x0005            | CPMU              | R      | REFFR  | 0[1:0]     | 0             | 0              |       | DEEL       | DIV[3:0]      |                |          |  |

| 0x0005            | REFDIV            |        | REFDIV |            | NEFFN         | Q[1.0]         |       |            |               | NEFL           | 010[3.0] |  |

| 0x0006            | CPMU              | R      | 0      | 0          | 0             |                |       | POSTDIV[4: | 01            |                |          |  |

| 0,0000            | POSTDIV           | W      |        |            |               |                |       |            |               |                |          |  |

| 0x0007            | CPMUIFLG          | R      | RTIF   | 0          | 0             | LOCKIF         | LOCK  | 0          | OSCIF         | UPOSC          |          |  |

|                   |                   |        |        | W          |               |                |       |            |               |                |          |  |

| 0x0008            | CPMUINT           | R      | RTIE   | 0          | 0             | LOCKIE         | 0     | 0          | OSCIE         | 0              |          |  |

|                   |                   | W      |        |            |               |                |       |            |               |                |          |  |

| 0x0009            | CPMUCLKS          | R<br>W | PLLSEL | PSTP       | CSAD          | COP<br>OSCSEL1 | PRE   | PCE        | RTI<br>OSCSEL | COP<br>OSCSEL0 |          |  |

| 0x000A            | CPMUPLL           | R      | 0      | 0          | FM1           | FM0            | 0     | 0          | 0             | 0              |          |  |

| 0,000,1           |                   | W      |        |            | 1 1011        | 1 100          |       |            |               |                |          |  |

| 0x000B            | CPMURTI           | R<br>W | RTDEC  | RTR6       | RTR5          | RTR4           | RTR3  | RTR2       | RTR1          | RTR0           |          |  |

| 0x000C            | CPMUCOP           | R      | WCOP   | RSBCK      | 0             | 0              | 0     | CR2        | CR1           | CR0            |          |  |

| 0,0000            |                   | W      | VVCOF  | NOBUR      | WRTMASK       |                |       | 0112       |               |                |          |  |

| 0x000D            | RESERVED          | R      | 0      | 0          | 0             | 0              | 0     | 0          | 0             | 0              |          |  |

| 0,0000            | CPMUTEST0         | W      |        |            |               |                |       |            |               |                |          |  |

|                   |                   |        |        | = Unimplen | nented or Res | served         |       |            |               |                |          |  |

Figure 9-3. CPMU Register Summary

S12 Clock, Reset and Power Management Unit (S12CPMU\_UHV)

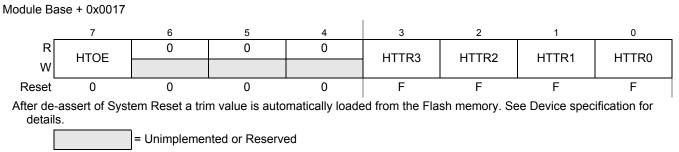

### 9.3.2.22 High Temperature Trimming Register (CPMUHTTR)

The CPMUHTTR register configures the trimming of the S12CPMU\_UHV temperature sense.

### Figure 9-28. High Temperature Trimming Register (CPMUHTTR)

Read: Anytime

Write: Anytime

### Table 9-25. CPMUHTTR Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                           |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>HTOE        | <ul> <li>High Temperature Offset Enable Bit — If set the temperature sense offset is enabled.</li> <li>0 The temperature sense offset is disabled. HTTR[3:0] bits don't care.</li> <li>1 The temperature sense offset is enabled. HTTR[3:0] select the temperature offset.</li> </ul> |

| 3–0<br>HTTR[3:0] | High Temperature Trimming Bits — See Table 9-26 for trimming effects.                                                                                                                                                                                                                 |

#### Table 9-26. Trimming Effect of HTTR

| HTTR[3:0] | Temperature<br>sensor voltage V <sub>HT</sub> | Interrupt threshold<br>temperatures T <sub>HTIA</sub> and T <sub>HTID</sub> |

|-----------|-----------------------------------------------|-----------------------------------------------------------------------------|

| 0000      | lowest                                        | highest                                                                     |

| 0001      |                                               |                                                                             |

|           | increasing                                    | decreasing                                                                  |

| 1110      |                                               |                                                                             |

| 1111      | highest                                       | lowest                                                                      |

# 11.5 Functional Description

### 11.5.1 Functional Overview

The DAC resistor network and the operational amplifier can be used together or stand alone. Following modes are supported:

|                                              |     | Description                                   |          |                                       |                                     |  |  |

|----------------------------------------------|-----|-----------------------------------------------|----------|---------------------------------------|-------------------------------------|--|--|

| DACM[2:0]                                    |     | Submo                                         | odules   | Out                                   | put                                 |  |  |

|                                              |     | DAC resistor Operational<br>network Amplifier |          | DACU                                  | АМР                                 |  |  |

| Off                                          | 000 | disabled                                      | disabled | disconnected                          | disconnected                        |  |  |

| Operational amplifier                        | 001 | disabled                                      | enabled  | disabled                              | depend on AMPP<br>and AMPM input    |  |  |

| Internal DAC only                            | 010 | enabled                                       | disabled | disconnected                          | disconnected                        |  |  |

| Unbuffered DAC                               | 100 | enabled                                       | disabled | unbuffered resistor<br>output voltage | disconnected                        |  |  |

| Unbuffered DAC with<br>Operational amplifier | 101 | enabled                                       | enabled  | unbuffered resistor<br>output voltage | depend on AMPP<br>and AMPM input    |  |  |

| Buffered DAC                                 | 111 | enabled                                       | enabled  | disconnected                          | buffered resistor<br>output voltage |  |  |

#### Table 11-5. DAC Modes of Operation

The DAC resistor network itself can work on two different voltage ranges:

#### Table 11-6. DAC Resistor Network Voltage ranges

| DAC Mode                 | Description                                                                                               |

|--------------------------|-----------------------------------------------------------------------------------------------------------|

| Full Voltage Range (FVR) | DAC resistor network provides a output voltage over the complete input voltage range, default after reset |

| Reduced Voltage Range    | DAC resistor network provides a output voltage over a reduced input voltage range                         |

Table 11-7 shows the control signal decoding for each mode. For more detailed mode description see the sections below.

Table 11-7. DAC Control Signals

| DACM                  |     | DAC resistor<br>network | Operational<br>Amplifier | Switch S1 | Switch S2 | Switch S3 |

|-----------------------|-----|-------------------------|--------------------------|-----------|-----------|-----------|

| Off                   | 000 | disabled                | disabled                 | open      | open      | open      |

| Operational amplifier | 001 | disabled                | enabled                  | closed    | open      | open      |

| Internal DAC only     | 010 | enabled                 | disabled                 | open      | open      | open      |

| Unbuffered DAC        | 100 | enabled                 | disabled                 | open      | open      | closed    |

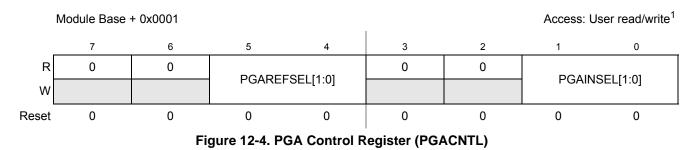

# 12.3.2.2 PGA Control Register (PGACNTL)

<sup>1</sup> Read: Anytime Write: Anytime

### Table 12-4. PGACNTL Field Description

| Field                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5:4<br>PGAREFSEL[1:0] | <ul> <li>PGA reference voltage selection — If PGAEN=1 these register bits select the source for the reference voltage (PGAREF, minus input of both amplifier stages).</li> <li>00 Internally generated V<sub>DDA</sub> / 2 is selected as reference voltage (PGAREF)</li> <li>01 Reserved</li> <li>10 External PGA_REF0 input is selected as reference voltage (PGAREF).</li> <li>11 External PGA_REF1 input is selected as reference voltage (PGAREF).</li> </ul>                                           |

| 1:0<br>PGAINSEL[1:0]  | <ul> <li>PGA input voltages selection — This register bit defines the source for the plus input voltage of the amplifier.</li> <li>00 no input voltage selected (PGAIN).</li> <li>01 input voltage selection controlled by external modules, please see SoC level connection for more details. If the external control signals enables both inputs, then PGA_IN0 is selected.</li> <li>10 PGA_IN0 is selected as input voltage (PGAIN).</li> <li>11 PGA_IN1 is selected as input voltage (PGAIN).</li> </ul> |

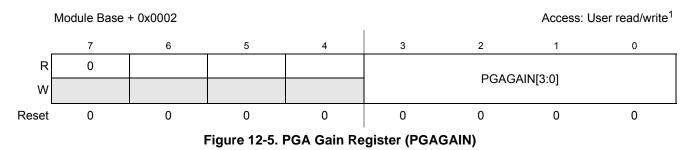

### 12.3.2.3 PGA Gain Register (PGAGAIN)

<sup>1</sup> Read: Anytime Write: Anytime

### Table 12-5. PGAGAIN Field Description

| Field               | Description                                                                                                                                 |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 3:0<br>PGAGAIN[3:0] | <b>PGA1 gain</b> — These register bits select the gain $A_{PGA}$ (amplification factor) for the PGA stage, see Table 12-6., "Amplifier Gain |

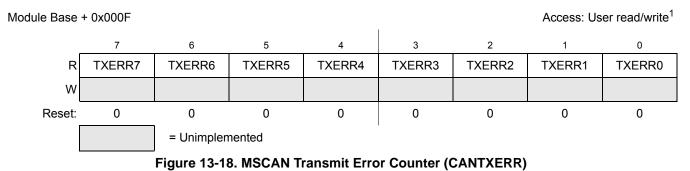

### 13.3.2.15 MSCAN Transmit Error Counter (CANTXERR)

This register reflects the status of the MSCAN transmit error counter.

Read: Only when in sleep mode (SLPRQ = 1 and SLPAK = 1) or initialization mode (INITRQ = 1 and INITAK = 1) Write: Unimplemented

### NOTE

Reading this register when in any other mode other than sleep or initialization mode, may return an incorrect value. For MCUs with dual CPUs, this may result in a CPU fault condition.

### 13.3.2.16 MSCAN Identifier Acceptance Registers (CANIDAR0-7)

On reception, each message is written into the background receive buffer. The CPU is only signalled to read the message if it passes the criteria in the identifier acceptance and identifier mask registers (accepted); otherwise, the message is overwritten by the next message (dropped).

The acceptance registers of the MSCAN are applied on the IDR0–IDR3 registers (see Section 13.3.3.1, "Identifier Registers (IDR0–IDR3)") of incoming messages in a bit by bit manner (see Section 13.4.3, "Identifier Acceptance Filter").

For extended identifiers, all four acceptance and mask registers are applied. For standard identifiers, only the first two (CANIDAR0/1, CANIDMR0/1) are applied.

Module Base + 0x0010 to Module Base + 0x0013

Access: User read/write<sup>1</sup>

|        | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| R<br>W | AC7 | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

#### Figure 13-19. MSCAN Identifier Acceptance Registers (First Bank) — CANIDAR0–CANIDAR3

<sup>1</sup> Read: Anytime

Write: Anytime in initialization mode (INITRQ = 1 and INITAK = 1)

#### Scalable Controller Area Network (S12MSCANV2)

| Register<br>Name |        | Bit 7 | 6    | 5    | 4        | 3        | 2    | 1    | Bit0 |

|------------------|--------|-------|------|------|----------|----------|------|------|------|

| 0x00X0<br>IDR0   | R<br>W | ID28  | ID27 | ID26 | ID25     | ID24     | ID23 | ID22 | ID21 |

| 0x00X1<br>IDR1   | R<br>W | ID20  | ID19 | ID18 | SRR (=1) | IDE (=1) | ID17 | ID16 | ID15 |

| 0x00X2<br>IDR2   | R<br>W | ID14  | ID13 | ID12 | ID11     | ID10     | ID9  | ID8  | ID7  |

| 0x00X3<br>IDR3   | R<br>W | ID6   | ID5  | ID4  | ID3      | ID2      | ID1  | ID0  | RTR  |

| 0x00X4<br>DSR0   | R<br>W | DB7   | DB6  | DB5  | DB4      | DB3      | DB2  | DB1  | DB0  |

| 0x00X5<br>DSR1   | R<br>W | DB7   | DB6  | DB5  | DB4      | DB3      | DB2  | DB1  | DB0  |

| 0x00X6<br>DSR2   | R<br>W | DB7   | DB6  | DB5  | DB4      | DB3      | DB2  | DB1  | DB0  |

| 0x00X7<br>DSR3   | R<br>W | DB7   | DB6  | DB5  | DB4      | DB3      | DB2  | DB1  | DB0  |

| 0x00X8<br>DSR4   | R<br>W | DB7   | DB6  | DB5  | DB4      | DB3      | DB2  | DB1  | DB0  |

| 0x00X9<br>DSR5   | R<br>W | DB7   | DB6  | DB5  | DB4      | DB3      | DB2  | DB1  | DB0  |

| 0x00XA<br>DSR6   | R<br>W | DB7   | DB6  | DB5  | DB4      | DB3      | DB2  | DB1  | DB0  |

| 0x00XB<br>DSR7   | R<br>W | DB7   | DB6  | DB5  | DB4      | DB3      | DB2  | DB1  | DB0  |

| 0x00XC<br>DLR    | R<br>W |       |      |      |          | DLC3     | DLC2 | DLC1 | DLC0 |

### Figure 13-23. Receive/Transmit Message Buffer — Extended Identifier Mapping

#### Scalable Controller Area Network (S12MSCANV2)

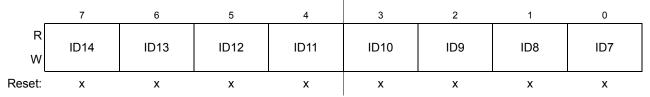

Module Base + 0x00X2

Figure 13-27. Identifier Register 2 (IDR2) — Extended Identifier Mapping

| Table 13-28 | 3. IDR2 Register | Field Descriptions - | – Extended |

|-------------|------------------|----------------------|------------|

|-------------|------------------|----------------------|------------|

| Field           | Description                                                                                                                                                                                                                                                                                                  |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7-0<br>ID[14:7] | <b>Extended Format Identifier</b> — The identifiers consist of 29 bits (ID[28:0]) for the extended format. ID28 is the most significant bit and is transmitted first on the CAN bus during the arbitration procedure. The priority of an identifier is defined to be highest for the smallest binary number. |  |

#### Module Base + 0x00X3

| _      | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| R<br>W | ID6 | ID5 | ID4 | ID3 | ID2 | ID1 | ID0 | RTR |

| Reset: | х   | х   | х   | х   | х   | х   | х   | X   |

Figure 13-28. Identifier Register 3 (IDR3) — Extended Identifier Mapping

### Table 13-29. IDR3 Register Field Descriptions — Extended

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-1<br>ID[6:0] | <b>Extended Format Identifier</b> — The identifiers consist of 29 bits (ID[28:0]) for the extended format. ID28 is the most significant bit and is transmitted first on the CAN bus during the arbitration procedure. The priority of an identifier is defined to be highest for the smallest binary number.                                                                                                                      |

| 0<br>RTR       | <ul> <li>Remote Transmission Request — This flag reflects the status of the remote transmission request bit in the CAN frame. In the case of a receive buffer, it indicates the status of the received frame and supports the transmission of an answering frame in software. In the case of a transmit buffer, this flag defines the setting of the RTR bit to be sent.</li> <li>0 Data frame</li> <li>1 Remote frame</li> </ul> |

#### Supply Voltage Sensor (BATSV3)

The comparator outputs BVLC and BVHC are forced to zero if the comparator is disabled (configuration bit BSUSE is cleared). If the software disables the comparator during a high or low Voltage condition (BVHC or BVLC active), then an additional interrupt is generated. To avoid this behavior the software must disable the interrupt generation before disabling the comparator.

The BATS interrupt vector is named in Table 14-6. Vector addresses and interrupt priorities are defined at MCU level.

The module internal interrupt sources are combined into one module interrupt signal.

Table 14-6. BATSV3 Interrupt Sources

| Module Interrupt Source | Module Internal Interrupt Source             | Local Enable |

|-------------------------|----------------------------------------------|--------------|

| BATSV3 Interrupt (BATI) | BATS Voltage Low Condition Interrupt (BVLI)  | BVLIE = 1    |

|                         | BATS Voltage High Condition Interrupt (BVHI) | BVHIE = 1    |

### 14.4.2.1 BATS Voltage Low Condition Interrupt (BVLI)

To use the Voltage Low Interrupt the Level Sensing must be enabled (BSUSE =1).

If measured when

a)  $V_{LBI1}$  selected with BVLS[1:0] = 0x0

$V_{measure} < V_{LBI1_A}$  (falling edge) or  $V_{measure} < V_{LBI1_D}$  (rising edge)

or when

b) V<sub>LBI2</sub> selected with BVLS[1:0] = 0x1 at pin VSUP

V<sub>measure</sub> < V<sub>LBI2</sub> A (falling edge) or V<sub>measure</sub> < V<sub>LBI2</sub> D (rising edge)

or when

c) V<sub>LBI3</sub> selected with BVLS[1:0] = 0x2 V<sub>measure</sub> < V<sub>LBI3\_A</sub> (falling edge) or V<sub>measure</sub> < V<sub>LBI3\_D</sub> (rising edge)

or when

d) V<sub>LBI4</sub> selected with BVLS[1:0] = 0x3

V<sub>measure</sub> < V<sub>LBI4\_A</sub> (falling edge) or V<sub>measure</sub> < V<sub>LBI4\_D</sub> (rising edge)

then BVLC is set. BVLC status bit indicates that a low voltage at pin VSUP is present. The Low Voltage Interrupt flag (BVLIF) is set to 1 when the Voltage Low Condition (BVLC) changes state. The Interrupt flag BVLIF can only be cleared by writing a 1. If the interrupt is enabled by bit BVLIE the module requests an interrupt to MCU (BATI).

### 14.4.2.2 BATS Voltage High Condition Interrupt (BVHI)

To use the Voltage High Interrupt the Level Sensing must be enabled (BSUSE=1).

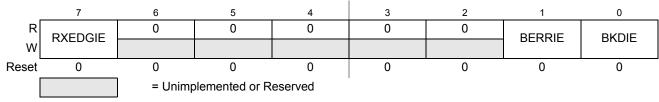

#### Serial Communication Interface (S12SCIV6)

### Write: Anytime, if AMAP = 1

| Field        | Description                                                                                                                                                                                                                                                                                                                                                             |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>RXEDGIF | Receive Input Active Edge Interrupt Flag — RXEDGIF is asserted, if an active edge (falling if RXPOL = 0, rising if RXPOL = 1) on the RXD input occurs. RXEDGIF bit is cleared by writing a "1" to it.<br>0 No active receive on the receive input has occurred<br>1 An active edge on the receive input has occurred                                                    |

| 2<br>BERRV   | <b>Bit Error Value</b> — BERRV reflects the state of the RXD input when the bit error detect circuitry is enabled and a mismatch to the expected value happened. The value is only meaningful, if BERRIF = 1.<br>0 A low input was sampled, when a high was expected<br>1 A high input reassembled, when a low was expected                                             |

| 1<br>BERRIF  | <b>Bit Error Interrupt Flag</b> — BERRIF is asserted, when the bit error detect circuitry is enabled and if the value sampled at the RXD input does not match the transmitted value. If the BERRIE interrupt enable bit is set an interrupt will be generated. The BERRIF bit is cleared by writing a "1" to it.<br>0 No mismatch detected<br>1 A mismatch has occurred |

| 0<br>BKDIF   | <ul> <li>Break Detect Interrupt Flag — BKDIF is asserted, if the break detect circuitry is enabled and a break signal is received. If the BKDIE interrupt enable bit is set an interrupt will be generated. The BKDIF bit is cleared by writing a "1" to it.</li> <li>0 No break signal was received</li> <li>1 A break signal was received</li> </ul>                  |

#### Table 18-5. SCIASR1 Field Descriptions

# 18.3.2.4 SCI Alternative Control Register 1 (SCIACR1)

Module Base + 0x0001

### Figure 18-7. SCI Alternative Control Register 1 (SCIACR1)

Read: Anytime, if AMAP = 1

Write: Anytime, if AMAP = 1

#### Table 18-6. SCIACR1 Field Descriptions

| Field | Description                                                                                                                                                                                                                                                          |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>Receive Input Active Edge Interrupt Enable — RXEDGIE enables the receive input active edge interrupt flag, RXEDGIF, to generate interrupt requests.</li> <li>0 RXEDGIF interrupt requests disabled</li> <li>1 RXEDGIF interrupt requests enabled</li> </ul> |

# 18.4.4 Baud Rate Generation

A 16-bit modulus counter in the two baud rate generator derives the baud rate for both the receiver and the transmitter. The value from 0 to 65535 written to the SBR15:SBR0 bits determines the baud rate. The value from 0 to 4095 written to the SBR15:SBR4 bits determines the baud rate clock with SBR3:SBR0 for fine adjust. The SBR bits are in the SCI baud rate registers (SCIBDH and SCIBDL) for both transmit and receive baud generator. The baud rate clock is synchronized with the bus clock and drives the receiver. The baud rate clock divided by 16 drives the transmitter. The receiver has an acquisition rate of 16 samples per bit time.

Baud rate generation is subject to one source of error:

• Integer division of the bus clock may not give the exact target frequency.

Table 18-16 lists some examples of achieving target baud rates with a bus clock frequency of 25 MHz.

### When IREN = 0 then,

SCI baud rate = SCI bus clock / (SCIBR[15:0])

| Bits<br>SBR[15:0] | Receiver <sup>1</sup><br>Clock (Hz) | Transmitter <sup>2</sup><br>Clock (Hz) | Target<br>Baud Rate | Error<br>(%) |

|-------------------|-------------------------------------|----------------------------------------|---------------------|--------------|

| 109               | 3669724.8                           | 229,357.8                              | 230,400             | .452         |

| 217               | 1843318.0                           | 115,207.4                              | 115,200             | .006         |

| 651               | 614439.3                            | 38,402.5                               | 38,400              | .006         |

| 1302              | 307219.7                            | 19,201.2                               | 19,200              | .006         |

| 2604              | 153,609.8                           | 9600.6                                 | 9,600               | .006         |

| 5208              | 76,804.9                            | 4800.3                                 | 4,800               | .006         |

| 10417             | 38,398.8                            | 2399.9                                 | 2,400               | .003         |

| 20833             | 19,200.3                            | 1200.02                                | 1,200               | .00          |

| 41667             | 9599.9                              | 600.0                                  | 600                 | .00          |

| 65535             | 6103.6                              | 381.5                                  |                     |              |

<sup>1</sup> 16x faster then baud rate

<sup>2</sup> divide 1/16 form transmit baud generator

#### Flash Module (S12ZFTMRZ)

block can support. Right after reset the Flash will be configured to run with the maximum amount of wait-states enabled; if the user application is setup to run at a slower frequency the control bits FCNFG[WSTAT] (see Section 22.3.2.5) can be configured by the user to disable the generation of wait-states, so it does not impose a performance penalty to the system if the read timing of the S12Z core is setup to be within the margins of the Flash block. For a definition of the frequency values where wait-states can be disabled please refer to the device electrical parameters.

The following sequence must be followed when the transition from a higher frequency to a lower frequency is going to happen:

- Flash resets with wait-states enabled;

- system frequency must be configured to the lower target;

- user writes to FNCNF[WSTAT] to disable wait-states;

- user reads the value of FPSTAT[WSTATACK], the new wait-state configuration will be effective when it reads as 1;

- user must re-write FCLKDIV to set a new value based on the lower frequency.

The following sequence must be followed on the contrary direction, going from a lower frequency to a higher frequency:

- user writes to FCNFG[WSTAT] to enable wait-states;

- user reads the value of FPSTAT[WSTATACK], the new wait-state configuration will be effective when it reads as 1;

- user must re-write FCLKDIV to set a new value based on the higher frequency;

- system frequency must be set to the upper target.

### CAUTION

If the application is going to require the frequency setup to change, the value to be loaded on register FCLKDIV will have to be updated according to the new frequency value. In this scenario the application must take care to avoid locking the value of the FCLKDIV register: bit FDIVLCK must not be set if the value to be loaded on FDIV is going to be re-written, otherwise a reset is going to be required. Please refer to Section 22.3.2.1, "Flash Clock Divider Register (FCLKDIV) and Section 22.4.5.1, "Writing the FCLKDIV Register.

### 22.4.4 Internal NVM resource

IFR is an internal NVM resource readable by CPU. The IFR fields are shown in Table 22-4.

The NVM Resource Area global address map is shown in Table 22-5.

### 22.4.5 Flash Command Operations

Flash command operations are used to modify Flash memory contents.

The next sections describe:

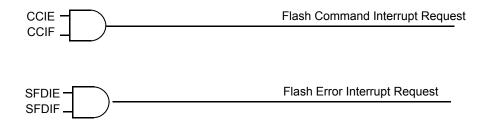

### 22.4.8 Interrupts

The Flash module can generate an interrupt when a Flash command operation has completed or when a Flash command operation has detected an ECC fault.

| Interrupt Source                   | Interrupt Flag              | Local Enable                | Global (CCR)<br>Mask |

|------------------------------------|-----------------------------|-----------------------------|----------------------|

| Flash Command Complete             | CCIF<br>(FSTAT register)    | CCIE<br>(FCNFG register)    | l Bit                |

| ECC Single Bit Fault on Flash Read | SFDIF<br>(FERSTAT register) | SFDIE<br>(FERCNFG register) | l Bit                |

Table 22-70. Flash Interrupt Sources

### NOTE

Vector addresses and their relative interrupt priority are determined at the MCU level.

### 22.4.8.1 Description of Flash Interrupt Operation

The Flash module uses the CCIF flag in combination with the CCIE interrupt enable bit to generate the Flash command interrupt request. The Flash module uses the SFDIF flag in combination with the SFDIE interrupt enable bits to generate the Flash error interrupt request. For a detailed description of the register bits involved, refer to Section 22.3.2.5, "Flash Configuration Register (FCNFG)", Section 22.3.2.6, "Flash Error Configuration Register (FERCNFG)", Section 22.3.2.6, "Flash Status Register (FSTAT)", and Section 22.3.2.8, "Flash Error Status Register (FERSTAT)".

The logic used for generating the Flash module interrupts is shown in Figure 22-31.

Figure 22-31. Flash Module Interrupts Implementation

### 22.4.9 Wait Mode

The Flash module is not affected if the MCU enters wait mode. The Flash module can recover the MCU from wait via the CCIF interrupt (see Section 22.4.8, "Interrupts").

| Num  | Characteristic                                                                                                                                                                                                                                         | Symbol                                 | Min                         | Typical                  | Мах                         | Unit    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-----------------------------|--------------------------|-----------------------------|---------|

| VDDX | =3.3V, VREG5VEN = 1'b0, ZVL(A)128/96/64 only                                                                                                                                                                                                           | <u> </u>                               |                             | <u> </u>                 |                             |         |

| 6a   | Output Voltage $V_{DDX}$ , with external PNP<br>Full Performance Mode $V_{SUP} > 5.5V^1$<br>Full Performance Mode $V_{SUP} > 5.5V^4$<br>Full Performance Mode $3.5V \le V_{SUP} \le 5.5V$<br>Reduced Performance Mode (stopmode)<br>$V_{SUP} > = 3.5V$ | V <sub>DDX</sub>                       | 3.2<br>3.23<br>3.13<br>2.2  | 3.3<br>3.3<br>-<br>3.3   | 3.39<br>3.36<br>3.39<br>3.6 | v       |

| 6b   | Output Voltage $V_{DDX}$ , without PNP<br>Full Performance Mode $V_{SUP} > 5.5V^1$<br>Full Performance Mode $V_{SUP} > 5.5V^4$<br>Full Performance Mode $3.5V \le V_{SUP} \le 5.5V$<br>Reduced Performance Mode (stopmode)<br>$V_{SUP} > = 3.5V$       | V <sub>DDX</sub>                       | 3.18<br>3.21<br>3.13<br>2.2 | 3.28<br>3.28<br>-<br>3.3 | 3.37<br>3.35<br>3.37<br>3.6 | v       |

| 7    | Load Current $V_{DDX}^{2,3}$ without external PNP<br>Full Performance Mode $V_{SUP} > 5.5V$<br>Full Performance Mode $3.5V \le V_{SUP} \le 5.5V$<br>Reduced Performance Mode (stopmode)                                                                | I <sub>DDX</sub>                       | 0<br>0<br>0                 |                          | 70<br>25<br>5               | mA      |

|      |                                                                                                                                                                                                                                                        |                                        |                             |                          |                             |         |

| 8    | Short Circuit $V_{DDX}$ fall back current $V_{DDX} \leq 0.5V$                                                                                                                                                                                          | I <sub>DDX</sub>                       | —                           | 100                      | —                           | mA      |

| 9    | Low Voltage Interrupt Assert Level <sup>5</sup><br>Low Voltage Interrupt Deassert Level                                                                                                                                                                | V <sub>LVIA</sub><br>V <sub>LVID</sub> | 4.04<br>4.19                | 4.23<br>4.38             | 4.40<br>4.49                | V       |

| 10a  | V <sub>DDX</sub> Low Voltage Reset deassert <sup>6</sup>                                                                                                                                                                                               | V <sub>LVRXD</sub>                     | _                           | —                        | 3.13                        | V       |

| 10b  | V <sub>DDX</sub> Low Voltage Reset assert                                                                                                                                                                                                              | V <sub>LVRXA</sub>                     | 2.95                        | 3.02                     |                             | V       |

| 11   | Trimmed ACLK output frequency <sup>7</sup>                                                                                                                                                                                                             | f <sub>ACLK</sub>                      | —                           | 20                       | —                           | KHz     |

| 12   | Trimmed ACLK internal clock $\Delta f / f_{nominal}^{8}$                                                                                                                                                                                               | df <sub>ACLK</sub>                     | - 6%                        | —                        | + 6%                        | —       |

| 13   | The first period after enabling the counter by APIFE might be reduced by API start up delay                                                                                                                                                            | t <sub>sdel</sub>                      | —                           | —                        | 100                         | μS      |

| 14   | Temperature Sensor Slope                                                                                                                                                                                                                               | dV <sub>HT</sub>                       | 5.05                        | 5.25                     | 5.45                        | mV/ºC   |

| 15   | Temperature Sensor Output Voltage (Tj=150°C)                                                                                                                                                                                                           | V <sub>HT</sub>                        | _                           | 2.4                      | —                           | V       |

| 16   | High Temperature Interrupt Assert <sup>9</sup><br>High Temperature Interrupt Deassert                                                                                                                                                                  | T <sub>HTIA</sub><br>T <sub>HTID</sub> | 120<br>110                  | 132<br>122               | 144<br>134                  | °C<br>℃ |

| 17   | Bandgap output voltage                                                                                                                                                                                                                                 | V <sub>BG</sub>                        | 1.14                        | 1.20                     | 1.28                        | V       |

| 18   | $V_{BG}$ voltage variation over input voltage $V_{SUP}$ 3.5V $\leq$ $V_{SUP}$ $\leq$ 18V, $T_{J}$ = 125°C                                                                                                                                              | $\Delta_{VBGV}$                        | -5                          |                          | 5                           | mV      |

#### Table B-1. Voltage Regulator Electrical Characteristics

# Appendix I ACMP Electrical Specifications

This section describe the electrical characteristics of the analog comparator module.

# I.1 Maximum Ratings

#### Table I-1. Maximum Ratings of the analog comparator - ACMP

Characteristics noted under conditions  $3.20V \le V_{DDA} \le 5.15V$ ,  $-40^{\circ}C \le T_J \le 175^{\circ}C^1$  unless otherwise noted. Typical values noted reflect the approximate parameter mean at  $T_A = 25^{\circ}C^2$  under nominal conditions unless otherwise noted.

| Num | Ratings                                                                                                             | Symbol                 | Min  | Тур | Max          | Unit |

|-----|---------------------------------------------------------------------------------------------------------------------|------------------------|------|-----|--------------|------|

| 1   | Max Rating (relative to supply)                                                                                     | V <sub>ACMP_MAX</sub>  | -0.3 | _   | VDDA<br>+0.3 | V    |

|     | Max Rating (absolute)<br>V <sub>ACMP_0</sub><br>V <sub>ACMP_1</sub><br>V <sub>acmpi_0</sub><br>V <sub>acmpi_1</sub> | V <sub>ACMP_MAXA</sub> | -0.3 | _   | 6            | V    |

<sup>1</sup> T<sub>J</sub>: Junction Temperature

<sup>2</sup>  $T_A$ : Ambient Temperature

# **I.2** Static Electrical Characteristics

#### Table I-2. Static Electrical Characteristics of the analog comparator - ACMP

Characteristics noted under conditions  $3.20V \le V_{DDA} \le 5.15V$ ,  $-40^{\circ}C \le T_J \le 175^{\circ}C^1$  unless otherwise noted. Typical values noted reflect the approximate parameter mean at  $T_A = 25^{\circ}C^2$  under nominal conditions unless otherwise noted.

| Num | Ratings                                                                                                                                                                                                                                                                                                     | Symbol                                         | Min            | Тур         | Max         | Unit           |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|----------------|-------------|-------------|----------------|

| 2   | Supply Current of ACMP $T_J \le 150^{\circ}C$<br>• Module disabled<br>• Module enabled $\Delta V_{in} > 5^*V_{hyst}$                                                                                                                                                                                        | I <sub>ACMP_off</sub><br>I <sub>ACMP_run</sub> | -<br>80        | -           | 3<br>180    | μΑ<br>μΑ       |

| 3   | Supply Current of ACMP 150°C $<$ T <sub>J</sub> $\leq$ 175°C<br>• Module disabled<br>• Module enabled $\Delta V_{in}$ > 5*V <sub>hyst</sub>                                                                                                                                                                 | I <sub>ACMP_off</sub><br>I <sub>ACMP_run</sub> | -<br>80        | -           | 5<br>180    | μΑ<br>μΑ       |

| 4   | $\begin{array}{l} \mbox{Pad Input Current in } V_{ACMP\_in} \mbox{ range} \\ \bullet \ -40^\circ C \leq T_J \leq 80^\circ C \\ \bullet \ -40^\circ C \leq T_J \leq 150^\circ C \\ \bullet \ -40^\circ C \leq T_J \leq 175^\circ C \\ \end{array}$ $\label{eq:For 0V < V_{pad\_in} < V_{DDA} \\ \end{array}$ | I <sub>ACMP_pad_in</sub>                       | -1<br>-2<br>-3 | -<br>-<br>- | 1<br>2<br>3 | μΑ<br>μΑ<br>μΑ |

| 5   | Input Offset<br>・ -40°C ≤ T <sub>J</sub> ≤ 175°C                                                                                                                                                                                                                                                            | V <sub>ACMP_offset</sub>                       | -25            | 0           | 25          | mV             |

#### **PIM Electrical Specifications**

<sup>4</sup> The structure of the HVI pins does not include diode structures shown in Figure A-1 that inject current when the input voltage goes outside the supply-ground range. Thus the HVI pin current injection is limited to below 200uA within the absolute maximum pin voltage range. However if the HVI impedance converter bypass is enabled, then even currents in this range can corrupt ADC results from simultaneous conversions on other channels. This can be prevented by disabling the bypass, either by clearing the PTAENLx or PTABYPLx bit. Similarly when the ADC is converting a HVI pin voltage then the impedance converter bypass must be disabled to ensure that current injection on PADx pins does not impact the HVI ADC conversion result.

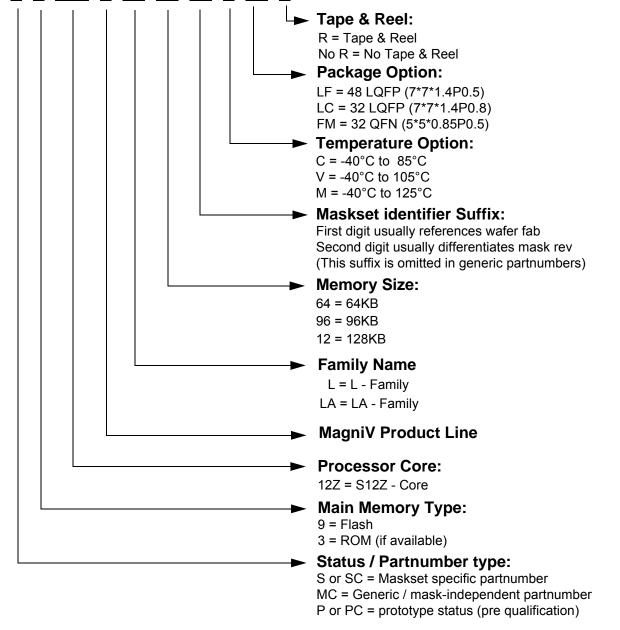

#### NOTE

Not every combination is offered. Table 1-2 lists available derivatives. The mask identifier suffix and the Tape & Reel suffix are always both omitted from the partnumber which is actually marked on the device.

```

<u>S 9 12Z V LA 12 F0 M LF R</u>

```

#### How to Reach Us:

Home Page:

nxp.com

Web Support

nxp.com/support

Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX, EMBRACE, GREENCHIP, HITAG, I2C BUS, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorIQ, QorIQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, and UMEMS are trademarks of NXP B.V. All other product or service names are the property of their respective owners. ARM, AMBA, ARM Powered, Artisan, Cortex, Jazelle, Keil, SecurCore, Thumb, TrustZone, and µVision are registered trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. ARM7, ARM9, ARM11, big.LITTLE, CoreLink, CoreSight, DesignStart, Mali, mbed, NEON, POP, Sensinode, Socrates, ULINK and Versatile are trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org

© 2016 NXP B.V.