Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | S12Z                                                                    |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SCI, SPI, UART/USART                    |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 19                                                                      |

| Program Memory Size        | 32KB (32K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 128 x 8                                                                 |

| RAM Size                   | 1K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 5.5V ~ 18V                                                              |

| Data Converters            | A/D 6x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount, Wettable Flank                                           |

| Package / Case             | 32-VFQFN Exposed Pad                                                    |

| Supplier Device Package    | 32-HVQFN (5x5)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12zvls3f0mfm |

**Device Overview MC9S12ZVL-Family**

#### 1.7.2.13.3 AMPM Input Pin

This analog input pin is used as input signal for the operational amplifiers negative input pin when the according mode is selected in DACCTL register bits DACM[2:0].

# **1.7.2.14 PGA Signals**

# 1.7.2.14.1 PGA\_IN0 / PGA\_IN1 — Programmable Gain Amplifier Inputs

PGA\_IN0 and PGA\_IN1 are the inputs of the Programmable Gain Amplifier.

# 1.7.2.14.2 PGA\_REF1 — Programmable Gain Amplifier Reference Inputs

PGA\_REF1 is the reference voltage the input of the Programmable Gain Amplifier.

# 1.7.2.15 VRH, VRL — ADC Reference Signals

VRH and VRL are the reference voltage input pins for the analog-to-digital converter.

# 1.7.2.16 **SPI0 Signals**

# 1.7.2.16.1 SS0 Signal

This signal is associated with the slave select SS functionality of the serial peripheral interface SPIO.

# 1.7.2.16.2 SCK0 Signal

This signal is associated with the serial clock SCK functionality of the serial peripheral interface SPIO.

#### 1.7.2.16.3 MISO0 Signal

This signal is associated with the MISO functionality of the serial peripheral interface SPI0. This signal acts as master input during master mode or as slave output during slave mode.

#### 1.7.2.16.4 MOSI0 Signal

This signal is associated with the MOSI functionality of the serial peripheral interface SPI0. This signal acts as master output during master mode or as slave input during slave mode

# 1.7.2.17 **SCI**[1:0] Signals

# 1.7.2.17.1 RXD[1:0] Signals

These signals are associated with the receive functionality of the serial communication interfaces (SCI[1:0]).

#### Port Integration Module (\$12ZVLPIMV2)

**Table 2-21. Port P Over-Current Interrupt Enable Register (continued)**

| Field       | Description                                                                                                                                                                                         |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3<br>OCIEP3 | Over-Current Interrupt Enable — This bit enables or disables the over-current interrupt on PP3.  1 PP3 over-current interrupt enabled 0 PP3 over-current interrupt disabled (interrupt flag masked) |

| 1<br>OCIEP1 | Over-Current Interrupt Enable — This bit enables or disables the over-current interrupt on PP1. 1 PP1 over-current interrupt enabled 0 PP1 over-current interrupt disabled (interrupt flag masked)  |

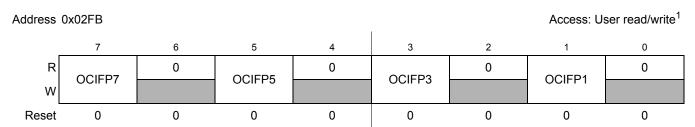

#### 2.3.4.3 Port P Over-Current Interrupt Flag Register (OCIFP)

Figure 2-25. Port P Over-Current Interrupt Flag Register

Write: Anytime, write 1 to clear

Table 2-22. Port P Over-Current Interrupt Flag Register

| Field       | Description                                                                                                                                                                                                                                                                             |  |  |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7<br>OCIFP7 | Over-Current Interrupt Flag — This flag asserts if an over-current condition is detected on EVDD1 (Section 2.4.4.3, "Over-Current Interrupt"). Writing a logic "1' to the corresponding bit clears the flag. 1 EVDD1 over-current event occurred 0 No EVDD1 over-current event occurred |  |  |  |  |

| 5<br>OCIFP5 | Over-Current Interrupt Flag — This flag asserts if an over-current condition is detected on PP5 (Section 2.4.4.3, "Over-Current Interrupt"). Writing a logic "1" to the corresponding bit clears the flag.  1 PP5 over-current event occurred 0 No PP5 over-current event occurred      |  |  |  |  |

| 3<br>OCIFP3 | Over-Current Interrupt Flag — This flag asserts if an over-current condition is detected on PP3 (Section 2.4.4.3, "Over-Current Interrupt"). Writing a logic "1' to the corresponding bit clears the flag.  1 PP3 over-current event occurred  0 No PP3 over-current event occurred     |  |  |  |  |

| 1<br>OCIFP1 | Over-Current Interrupt Flag — This flag asserts if an over-current condition is detected on PP1 (Section 2.4.4.3, "Over-Current Interrupt"). Writing a logic "1' to the corresponding bit clears the flag.  1 PP1 over-current event occurred  0 No PP1 over-current event occurred     |  |  |  |  |

MC912ZVL Family Reference Manual, Rev. 2.41 94 **NXP Semiconductors**

Read: Anytime

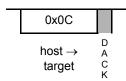

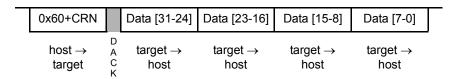

# 5.4.4.8 **GO\_UNTIL**

This command is used to exit active BDM and begin (or resume) execution of application code. The CPU pipeline is flushed and refilled before normal instruction execution resumes. Prefetching begins at the current address in the PC. If any register (such as the PC) is altered by a BDC command whilst in BDM, the updated value is used when prefetching resumes.

After resuming application code execution, if ACK is enabled, the BDC awaits a return to active BDM before driving an ACK pulse. timeouts do not apply when awaiting a GO\_UNTIL command ACK.

If a GO\_UNTIL is not acknowledged then a SYNC command must be issued to end the pending GO\_UNTIL.

If a GO\_UNTIL command is issued whilst BDM is inactive, an illegal command response is returned and the ILLCMD bit is set.

If ACK handshaking is disabled, the GO\_UNTIL command is identical to the GO command.

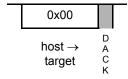

#### 5.4.4.9 NOP

NOP performs no operation and may be used as a null command where required.

#### 5.4.4.10 READ Rn

#### Read CPU register Active Background

This command reads the selected CPU registers and returns the 32-bit result. Accesses to CPU registers are always 32-bits wide, regardless of implemented register width. Bytes that are not implemented return zero. The register is addressed through the CPU register number (CRN). See Section 5.4.5.1, "BDC

S12Z DebugLite (S12ZDBGV3)

# 7.3.2.15 Debug Comparator D Address Register (DBGDAH, DBGDAM, DBGDAL)

Address: 0x0145. DBGDAH 20 19 18 17 16 R DBGDA[23:16] W Reset 0 0 0 0 0 0 0 0 Address: 0x0146, DBGDAM 15 14 13 11 10 9 8 R DBGDA[15:8] W 0 0 0 0 0 0 Reset Address: 0x0147, DBGDAL R DBGDA[7:0] W 0 0 0 0 0 0 0 0 Reset

Figure 7-18. Debug Comparator D Address Register

Read: Anytime.

Write: If DBG not armed.

Table 7-26. DBGDAH, DBGDAM, DBGDAL Field Descriptions

| Field                     | Description                                                                                                                                                                                                                                                              |  |  |  |  |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 23–16<br>DBGDA<br>[23:16] | Comparator Address Bits [23:16]— These comparator address bits control whether the comparator compares the address bus bits [23:16] to a logic one or logic zero.  O Compare corresponding address bit to a logic zero  Compare corresponding address bit to a logic one |  |  |  |  |

| 15–0<br>DBGDA<br>[15:0]   | Comparator Address Bits[15:0]— These comparator address bits control whether the comparator compares the address bus bits [15:0] to a logic one or logic zero.  O Compare corresponding address bit to a logic zero  Compare corresponding address bit to a logic one    |  |  |  |  |

# 7.4 Functional Description

This section provides a complete functional description of the DBG module.

# 7.4.1 DBG Operation

The DBG module operation is enabled by setting ARM in DBGC1. When armed it can be used to generate breakpoints to the CPU. The DBG module is made up of comparators, control logic, and the state sequencer, Figure 7-1.

The comparators monitor the bus activity of the CPU. Comparators can be configured to monitor opcode addresses (effectively the PC address) or data accesses. Comparators can be configured during data

# 9.4.6.3 PLL Bypassed External Mode (PBE)

In this mode, the Bus Clock is based on the external oscillator clock. The reference clock for the PLL is based on the external oscillator.

The clock sources for COP and RTI can be based on the internal reference clock generator or on the external oscillator clock or the RC-Oscillator (ACLK).

This mode can be entered from default mode PEI by performing the following steps:

- 1. Make sure the PLL configuration is valid.

- 2. Enable the external Oscillator (OSCE bit)

- 3. Wait for the oscillator to start-up and the PLL being locked (LOCK = 1) and (UPOSC =1)

- 4. Clear all flags in the CPMUIFLG register to be able to detect any status bit change.

- 5. Optionally status interrupts can be enabled (CPMUINT register).

- 6. Select the Oscillator clock as source of the Bus clock (PLLSEL=0)

Loosing PLL lock status (LOCK=0) means loosing the oscillator status information as well (UPOSC=0).

The impact of loosing the oscillator status (UPOSC=0) in PBE mode is as follows:

- PLLSEL is set automatically and the Bus clock is switched back to the PLL clock.

- The PLLCLK is derived from the VCO clock (with its actual frequency) divided by four until the PLL locks again.

NOTEApplication software needs to be prepared to deal with the impact of loosing the oscillator status at any time.

When using the oscillator clock as system clock (write PLLSEL = 0) it is highly recommended to enable the oscillator clock monitor reset feature (write OMRE = 1 in CPMUOSC2 register). If the oscillator monitor reset feature is disabled (OMRE = 0) and the oscillator clock is used as system clock, the system might stall in case of loss of oscillation.

#### 9.5 Resets

#### 9.5.1 General

All reset sources are listed in Table 9-34. There is only one reset vector for all these reset sources. Refer to MCU specification for reset vector address.

Reset Source

Local Enable

Power-On Reset (POR)

None

Low Voltage Reset (LVR)

None

External pin RESET

None

PLL Clock Monitor Reset

None

Table 9-34. Reset Summary

MC912ZVL Family Reference Manual, Rev. 2.41

Analog-to-Digital Converter (ADC12B\_LBA)

# 10.4 Signal Description

This section lists all inputs to the ADC12B\_LBA block.

# 10.4.1 Detailed Signal Descriptions

# 10.4.1.1 ANx (x = n,..., 2, 1, 0)

This pin serves as the analog input Channel x. The maximum input channel number is n. Please refer to the device reference manual for the maximum number of input channels.

# 10.4.1.2 VRH\_0, VRH\_1, VRH\_2, VRL\_0, VRL\_1

VRH\_0/1/2 are the high reference voltages, VRL0/1 are the low reference voltages for a ADC conversion selectable on a conversion command basis. Please refer to the device overview information for availability and connectivity of these pins.

VRH\_2 is only available on ADC12B\_LBA V3.

VRL\_1 is only available on ADC12B\_LBA V1 and V2.

See also Table 10-2.

# 10.4.1.3 VDDA, VSSA

These pins are the power supplies for the analog circuitry of the ADC12B\_LBA block.

# Table 10-10. ADCFLWCTL Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>SEQA | Conversion Sequence Abort Event — This bit indicates that a conversion sequence abort event is in progress. When this bit is set the ongoing conversion sequence and current CSL will be aborted at the next conversion boundary. This bit gets cleared when the ongoing conversion sequence is aborted and ADC is idle. This bit can only be set if bit ADC_EN is set. This bit is cleared if bit ADC_EN is clear. Data Bus Control:                         |

|           | This bit can be controlled via the data bus if access control is configured accordingly via ACC_CFG[1:0]. Writing a value of 1'b0 does not clear the flag.                                                                                                                                                                                                                                                                                                    |

|           | Writing a one to this bit does not clear it but causes an overrun if the bit has already been set. See Section 10.6.3.2.6, "Conversion flow control in case of conversion sequence control bit overrun scenarios for more details.                                                                                                                                                                                                                            |

|           | Internal Interface Control:  This bit can be controlled via the internal interface Signal "Seq_Abort" if access control is configured accordingly via ACC_CFG[1:0]. After being set an additional request via the internal interface Signal "Seq_Abort" causes an overrun. See also conversion flow control in case of overrun situations.  General:                                                                                                          |

|           | In both conversion flow control modes (Restart Mode and Trigger Mode) when bit RSTA gets set automatically bit SEQA gets set when the ADC has not reached one of the following scenarios:  - A Sequence Abort request is about to be executed or has been executed.  - "End Of List" command type has been executed or is about to be executed In case bit SEQA is set automatically the Restart error flag RSTA_EIF is set to indicate an unexpected Restart |

|           | Request.  O No conversion sequence abort request.  Conversion sequence abort request.                                                                                                                                                                                                                                                                                                                                                                         |

| 6<br>TRIG | Conversion Sequence Trigger Bit — This bit starts a conversion sequence if set and no conversion or conversion sequence is ongoing. This bit is cleared when the first conversion of a sequence starts to sample. This bit can only be set if bit ADC_EN is set. This bit is cleared if bit ADC_EN is clear.  Data Bus Control:                                                                                                                               |

|           | This bit can be controlled via the data bus if access control is configured accordingly via ACC_CFG[1:0]. Writing a value of 1'b0 does not clear the flag.  After being set this bit can not be cleared by writing a value of 1'b1 instead the error flag TRIG_EIF is set. See also Section 10.6.3.2.6, "Conversion flow control in case of conversion sequence control bit overrun scenarios for more details.                                               |

|           | Internal Interface Control: This bit can be controlled via the internal interface Signal "Trigger" if access control is configured accordingly via ACC_CFG[1:0]. After being set an additional request via internal interface Signal "Trigger" causes the flag TRIG_EIF to be set.  No conversion sequence trigger.  Trigger to start conversion sequence.                                                                                                    |

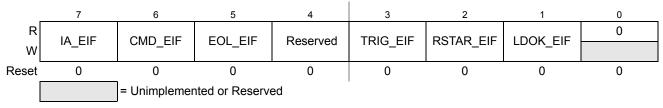

# 10.5.2.9 ADC Error Interrupt Flag Register (ADCEIF)

If one of the following error flags is set the ADC ceases operation:

- IA EIF

- CMD EIF

- EOL\_EIF

- TRIG EIF

In order to make the ADC operational again an ADC Soft-Reset must be issued which clears above listed error interrupt flags.

The error interrupt flags RSTAR\_EIF and LDOK\_EIF do not cause the ADC to cease operation. If set the ADC continues operation. Each of the two bits can be cleared by writing a value of 1'b1. Both bits are also cleared if an ADC Soft-Reset is issued.

All bits are cleared if bit ADC\_EN is clear. Writing any flag with value 1'b0 does not clear a flag. Writing any flag with value 1'b1 does not set the flag.

Module Base + 0x0008

Figure 10-12. ADC Error Interrupt Flag Register (ADCEIF)

Read: Anytime

#### Write:

- Bits RSTAR\_EIF and LDOK\_EIF are writable anytime

- Bits IA EIF, CMD EIF, EOL EIF and TRIG EIF are not writable

# **Table 10-14. ADCEIF Field Descriptions**

| Field        | Description                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7<br>IA_EIF  | Illegal Access Error Interrupt Flag — This flag indicates that storing the conversion result caused an illegal access error or conversion command loading from outside system RAM or NVM area occurred.  The ADC ceases operation if this error flag is set (issue of type severe).  No illegal access error occurred.  An illegal access error occurred.            |  |  |  |  |

| 6<br>CMD_EIF | Command Value Error Interrupt Flag — This flag indicates that an invalid command is loaded (Any command that contains reserved bit settings) or illegal format setting selected (reserved SRES[2:0] bit settings).  The ADC ceases operation if this error flag is set (issue of type severe).  Valid conversion command loaded.  Invalid conversion command loaded. |  |  |  |  |

| 5<br>EOL_EIF | <ul> <li>"End Of List" Error Interrupt Flag — This flag indicates a missing "End Of List" command type in current executed CSL.</li> <li>The ADC ceases operation if this error flag is set (issue of type severe).</li> <li>No "End Of List" error.</li> <li>"End Of List" command type missing in current executed CSL.</li> </ul>                                 |  |  |  |  |

#### MC912ZVL Family Reference Manual, Rev. 2.41

If signal Restart is asserted before signal LoadOK is set the conversion starts from top of currently active CSL at the next Trigger Event (no exchange of CSL list).

If signal Restart is asserted after or simultaneously with signal LoadOK the conversion starts from top of the other CSL at the next Trigger Event (CSL is switched) if CSL is configured for double buffer mode.

#### **Sequence Abort Event**

Internal Interface Signal: Seq Abort Corresponding Bit Name: SEQA

- Function:

Abort any possible ongoing conversion at next conversion boundary and abort current conversion sequence and active CSL

- Requested by:

- Positive edge of internal interface signal Seq\_Abort

- Write Access via data bus to set control bit SEQA

- When finished:

This bit gets cleared when an ongoing conversion is finished and the result is stored and/or an ongoing conversion sequence is aborted and current active CSL is aborted (ADC idle, RVL done)

- Mandatory Requirement:

- In all ADC conversion flow control modes bit SEQA can only be set if:

- \* ADC not idle (a conversion or conversion sequence is ongoing)

- \* ADC idle but RVL done condition not reached

The RVL done condition is not reached if:

- \* An "End Of List" command type has not been executed

- \* A Sequence Abort Event has not been executed (bit SEQA not already set)

- In all ADC conversion flow control modes a Sequence Abort Event can be issued at any time

- In ADC conversion flow control mode "Restart Mode" after a conversion sequence abort request has been executed it is mandatory to set bit RSTA. If a Trigger Event occurs before a Restart Event is executed (bit RSTA set and cleared by hardware), bit TRIG is set, error flag TRIG EIF is set, and the ADC can only be continued by a Soft-Reset. After the Restart Event the ADC accepts new Trigger Events (bit TRIG set) and begins conversion from top of the currently active CSL.

- In ADC conversion flow control mode "Restart Mode" after a Sequence Abort Event has been executed, a Restart Event causes only the RSTA bit being set. The ADC executes a Restart Event only.

- In both conversion flow control modes ("Restart Mode" and "Trigger Mode") when conversion flow control bit RSTA gets set automatically bit SEQA gets set when the ADC has not reached one of the following scenarios:

- \* An "End Of List" command type has been executed or is about to be executed

- \* A Sequence Abort request is about to be executed or has been executed.

In case bit SEQA is set automatically the Restart error flag RSTA\_EIF is set to indicate an unexpected Restart Request.

Analog-to-Digital Converter (ADC12B\_LBA)

#### 10.7 Resets

At reset the ADC12B\_LBA is disabled and in a power down state. The reset state of each individual bit is listed within Section 10.5.2, "Register Descriptions" which details the registers and their bit-fields.

# 10.8 Interrupts

The ADC supports three types of interrupts:

- Conversion Interrupt

- Sequence Abort Interrupt

- Error and Conversion Flow Control Issue Interrupt

Each of the interrupt types is associated with individual interrupt enable bits and interrupt flags.

# **10.8.1** ADC Conversion Interrupt

The ADC provides one conversion interrupt associated to 16 interrupt enable bits with dedicated interrupt flags. The 16 interrupt flags consist of:

- 15 conversion interrupt flags which can be associated to any conversion completion.

- One additional interrupt flag which is fixed to the "End Of List" conversion command type within the active CSL.

The association of the conversion number with the interrupt flag number is done in the conversion command.

# 10.8.2 ADC Sequence Abort Done Interrupt

The ADC provides one sequence abort done interrupt associated with the sequence abort request for conversion flow control. Hence, there is only one dedicated interrupt flag and interrupt enable bit for conversion sequence abort and it occurs when the sequence abort is done.

# **Chapter 12 Programmable Gain Amplifier (PGAV1)**

# 12.1 Revision History

**Table 12-1. Revision History Table**

| Rev. No.<br>(Item No.) | Data     | Sections<br>Affected | Substantial Change(s)                                 |  |  |  |

|------------------------|----------|----------------------|-------------------------------------------------------|--|--|--|

| 1.0                    | 05-May15 | Figure 12-8          | updated Figure 12-8                                   |  |  |  |

| 1.1                    | 13-May15 | Figure 12-2          | correct read values of reserved registers Figure 12-2 |  |  |  |

# **Glossary**

Table 12-2. Terminology

| Term | Meaning                     |  |

|------|-----------------------------|--|

| PGA  | Programmable Gain Amplifier |  |

# 12.2 Introduction

The PGA module is programmable gain amplifier. Figure 12-1 shows the block diagram. Please refer to device specification for the mapping and connectivity of the PGA module pins.

#### 12.2.1 Features

The PGA will be operated from the analog 5V power domain VDDA.

- Amplification of analog input signal with selectable gain of 10x, 20x, 40x, 80x

- Typical current consumption 1mA

- Offset compensation

- Internal VDDA / 2 reference voltage generation or external signal as reference voltage (see top level connections)

- Amplifier output connected to ADC

# 12.2.2 Modes of Operation

The PGA module behaves as follows in the system power modes:

1. CPU run mode

The functionality of the PGA module is available.

Table 13-25. Message Buffer Organization

| Offset<br>Address | Register                                              | Access |  |  |

|-------------------|-------------------------------------------------------|--------|--|--|

| 0x00X0            | IDR0 — Identifier Register 0                          | R/W    |  |  |

| 0x00X1            | 0x00X1 IDR1 — Identifier Register 1                   |        |  |  |

| 0x00X2            | IDR2 — Identifier Register 2                          | R/W    |  |  |

| 0x00X3            | IDR3 — Identifier Register 3                          | R/W    |  |  |

| 0x00X4            | DSR0 — Data Segment Register 0                        | R/W    |  |  |

| 0x00X5            | DSR1 — Data Segment Register 1                        | R/W    |  |  |

| 0x00X6            | DSR2 — Data Segment Register 2                        | R/W    |  |  |

| 0x00X7            | DSR3 — Data Segment Register 3                        | R/W    |  |  |

| 0x00X8            | DSR4 — Data Segment Register 4                        | R/W    |  |  |

| 0x00X9            | DSR5 — Data Segment Register 5                        | R/W    |  |  |

| 0x00XA            | DSR6 — Data Segment Register 6                        | R/W    |  |  |

| 0x00XB            | DSR7 — Data Segment Register 7                        | R/W    |  |  |

| 0x00XC            | DLR — Data Length Register                            | R/W    |  |  |

| 0x00XD            | TBPR — Transmit Buffer Priority Register <sup>1</sup> | R/W    |  |  |

| 0x00XE            | TSRH — Time Stamp Register (High Byte)                | R      |  |  |

| 0x00XF            | TSRL — Time Stamp Register (Low Byte)                 | R      |  |  |

<sup>&</sup>lt;sup>1</sup> Not applicable for receive buffers

Figure 13-23 shows the common 13-byte data structure of receive and transmit buffers for extended identifiers. The mapping of standard identifiers into the IDR registers is shown in Figure 13-24.

All bits of the receive and transmit buffers are 'x' out of reset because of RAM-based implementation<sup>1</sup>. All reserved or unused bits of the receive and transmit buffers always read 'x'.

MC912ZVL Family Reference Manual, Rev. 2.41

<sup>1.</sup> Exception: The transmit buffer priority registers are 0 out of reset.

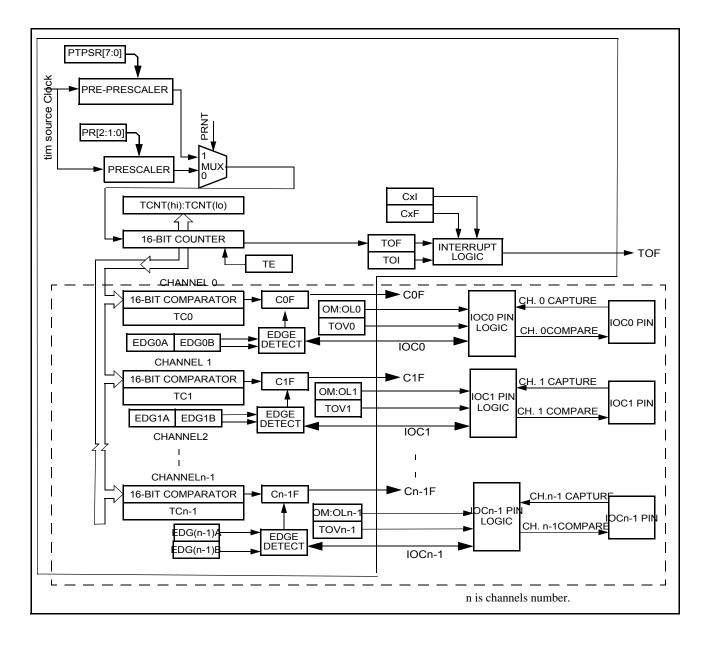

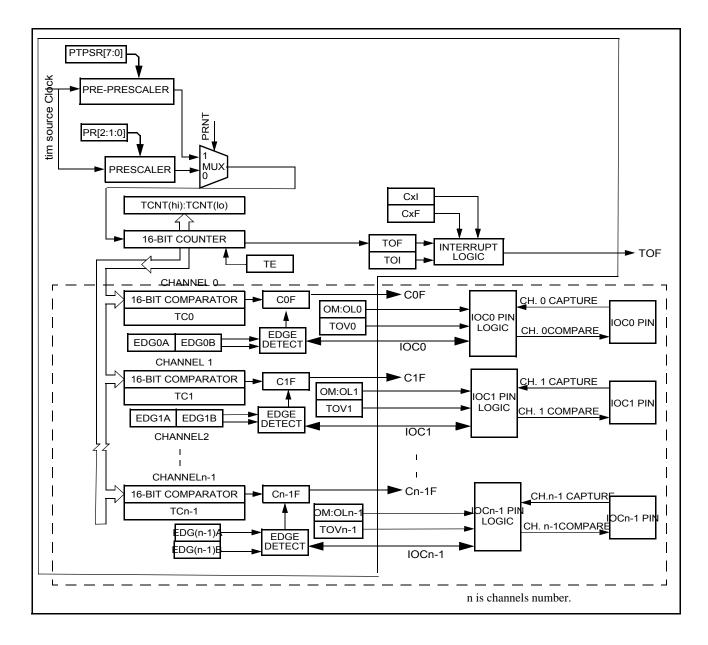

Figure 15-22. Detailed Timer Block Diagram

#### 15.4.1 Prescaler

The prescaler divides the Bus clock by 1, 2, 4, 8, 16, 32, 64 or 128. The prescaler select bits, PR[2:0], select the prescaler divisor. PR[2:0] are in timer system control register 2 (TSCR2).

The prescaler divides the Bus clock by a prescalar value. Prescaler select bits PR[2:0] of in timer system control register 2 (TSCR2) are set to define a prescalar value that generates a divide by 1, 2, 4, 8, 16, 32, 64 and 128 when the PRNT bit in TSCR1 is disabled.

MC912ZVL Family Reference Manual, Rev. 2.41

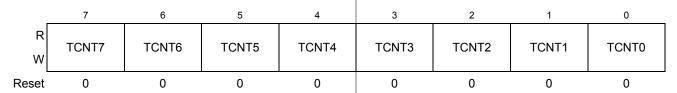

#### Timer Module (TIM16B2CV3)

Module Base + 0x0005

Figure 16-7. Timer Count Register Low (TCNTL)

The 16-bit main timer is an up counter.

A full access for the counter register should take place in one clock cycle. A separate read/write for high byte and low byte will give a different result than accessing them as a word.

Read: Anytime

Write: Has no meaning or effect in the normal mode; only writable in special modes.

The period of the first count after a write to the TCNT registers may be a different size because the write is not synchronized with the prescaler clock.

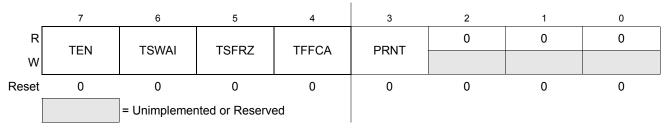

# 16.3.2.4 Timer System Control Register 1 (TSCR1)

Module Base + 0x0006

Figure 16-8. Timer System Control Register 1 (TSCR1)

Read: Anytime Write: Anytime

Table 16-4. TSCR1 Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                            |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | Timer Enable  0 Disables the main timer, including the counter. Can be used for reducing power consumption.  1 Allows the timer to function normally.  If for any reason the timer is not active, there is no ÷64 clock for the pulse accumulator because the ÷64 is generated by the timer prescaler. |

| 6<br>TSWAI | Timer Module Stops While in Wait  O Allows the timer module to continue running during wait.  Disables the timer module when the MCU is in the wait mode. Timer interrupts cannot be used to get the MCU out of wait.  TSWAI also affects pulse accumulator.                                           |

MC912ZVL Family Reference Manual, Rev. 2.41

Figure 16-22. Detailed Timer Block Diagram

#### 16.4.1 Prescaler

The prescaler divides the Bus clock by 1, 2, 4, 8, 16, 32, 64 or 128. The prescaler select bits, PR[2:0], select the prescaler divisor. PR[2:0] are in timer system control register 2 (TSCR2).

The prescaler divides the Bus clock by a prescalar value. Prescaler select bits PR[2:0] of in timer system control register 2 (TSCR2) are set to define a prescalar value that generates a divide by 1, 2, 4, 8, 16, 32, 64 and 128 when the PRNT bit in TSCR1 is disabled.

MC912ZVL Family Reference Manual, Rev. 2.41

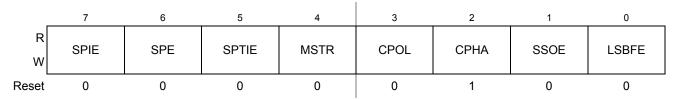

Figure 19-2. SPI Register Summary

# 19.3.2 Register Descriptions

This section consists of register descriptions in address order. Each description includes a standard register diagram with an associated figure number. Details of register bit and field function follow the register diagrams, in bit order.

# 19.3.2.1 SPI Control Register 1 (SPICR1)

Module Base +0x0000

Figure 19-3. SPI Control Register 1 (SPICR1)

Read: Anytime Write: Anytime

**Table 19-2. SPICR1 Field Descriptions**

| Field      | Description                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7<br>SPIE  | SPI Interrupt Enable Bit — This bit enables SPI interrupt requests, if SPIF or MODF status flag is set.  0 SPI interrupts disabled.  1 SPI interrupts enabled.                                                                                                                                                              |  |  |  |  |

| 6<br>SPE   | SPI System Enable Bit — This bit enables the SPI system and dedicates the SPI port pins to SPI system functions. If SPE is cleared, SPI is disabled and forced into idle state, status bits in SPISR register are reset. 0 SPI disabled (lower power consumption). 1 SPI enabled, port pins are dedicated to SPI functions. |  |  |  |  |

| 5<br>SPTIE | SPI Transmit Interrupt Enable — This bit enables SPI interrupt requests, if SPTEF flag is set.  0 SPTEF interrupt disabled.  1 SPTEF interrupt enabled.                                                                                                                                                                     |  |  |  |  |

| 4<br>MSTR  | SPI Master/Slave Mode Select Bit — This bit selects whether the SPI operates in master or slave mode.  Switching the SPI from master to slave or vice versa forces the SPI system into idle state.  O SPI is in slave mode.  1 SPI is in master mode.                                                                       |  |  |  |  |

621

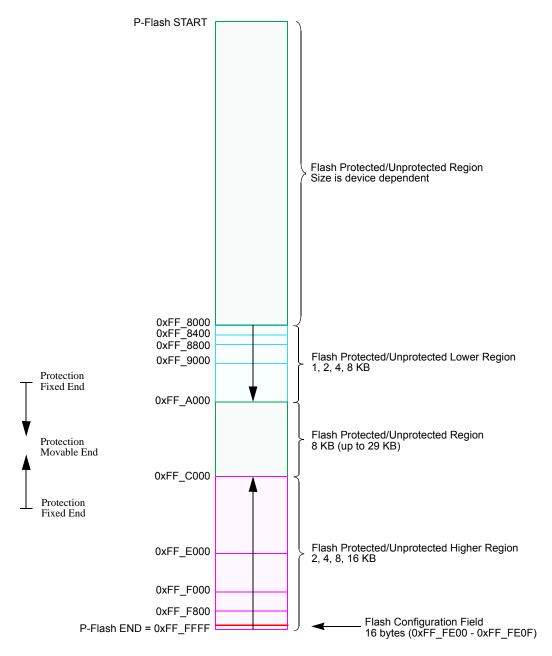

Figure 22-2. P-Flash Memory Map With Protection Alignment

**PGA Electrical Specifications**

# O.6 0x0380-0x039F FTMRZ (continued)

| Address | Name     | 7             | 6      | 5      | 4      | 3      | 2      | 1     | 0     |

|---------|----------|---------------|--------|--------|--------|--------|--------|-------|-------|

| 0x0394  | FCCOB4HI | R<br>W CCOB15 | CCOB14 | CCOB13 | CCOB12 | CCOB11 | CCOB10 | ССОВ9 | CCOB8 |

| 0x0395  | FCCOB4LO | R<br>W CCOB7  | CCOB6  | CCOB5  | CCOB4  | ССОВ3  | CCOB2  | CCOB1 | ССОВ0 |

| 0x0396  | FCCOB5HI | R<br>W CCOB15 | CCOB14 | CCOB13 | CCOB12 | CCOB11 | CCOB10 | ССОВ9 | CCOB8 |

| 0x0397  | FCCOB5LO | R<br>W CCOB7  | CCOB6  | CCOB5  | CCOB4  | CCOB3  | CCOB2  | CCOB1 | ССОВ0 |

# O.7 0x03C0-0x03CF SRAM\_ECC\_32D7P

| Address            | Name     |        | D:4.7         | _ |   |   |   |   |       |        |  |

|--------------------|----------|--------|---------------|---|---|---|---|---|-------|--------|--|

|                    |          |        | Bit 7         | 6 | 5 | 4 | 3 | 2 | 1     | Bit 0  |  |

| 0x03C0             | ECCSTAT  | R<br>W | 0             | 0 | 0 | 0 | 0 | 0 | 0     | RDY    |  |

| 0x03C1             | ECCIE    | R<br>W | 0             | 0 | 0 | 0 | 0 | 0 | 0     | SBEEIE |  |

| 0x03C2             | ECCIF    | R<br>W | 0             | 0 | 0 | 0 | 0 | 0 | 0     | SBEEIF |  |

| 0x03C3 -<br>0x03C6 | Reserved | R<br>W | 0             | 0 | 0 | 0 | 0 | 0 | 0     | 0      |  |

| 0x03C7             | ECCDPTRH | R<br>W | DPTR[23:16]   |   |   |   |   |   |       |        |  |

| 0x03C8             | ECCDPTRM | R<br>W | DPTR[15:8]    |   |   |   |   |   |       |        |  |

| 0x03C9             | ECCDPTRL | R<br>W | DPTR[7:1]     |   |   |   |   |   |       |        |  |

| 0x03CA -<br>0x03CB | Reserved | R<br>W | 0             | 0 | 0 | 0 | 0 | 0 | 0     | 0      |  |

| 0x03CC             | ECCDDH   | R<br>W | DDATA[15:8]   |   |   |   |   |   |       |        |  |

| 0x03CD             | ECCDDL   | R<br>W | DDATA[7:0]    |   |   |   |   |   |       |        |  |

| 0x03CE             | ECCDE    | R<br>W | 0 0 DECC[5:0] |   |   |   |   |   |       |        |  |

| 0x03CF             | ECCDCMD  | R<br>W | ECCDRR        | 0 | 0 | 0 | 0 | 0 | ECCDW | ECCDR  |  |

# O.15 0x06C0-0x06DF CPMU (continued)

| Address | Name            |   | Bit 7   | 6 | 5 | 4 | 3 | 2 | 1      | Bit 0  |

|---------|-----------------|---|---------|---|---|---|---|---|--------|--------|

| 0x06DD  | CPMU<br>VREGCTL | R | VREG5VE | 0 | 0 | 0 | 0 | 0 | EXTXON | INTXON |

|         |                 | W | N       |   |   |   |   |   | EXTAGN | INTXON |

| 0x06DE  | CPMU            | R | 0       | 0 | 0 | 0 | 0 | 0 | 0      | 0      |

|         | RESERVED1<br>E  | W |         |   |   |   |   |   |        |        |

| 0x06DF  | CPMU            | R | 0       | 0 | 0 | 0 | 0 | 0 | 0      | 0      |

|         | RESERVED1<br>F  | W |         |   |   |   |   |   |        |        |