# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | S12Z                                                                     |

| Core Size                  | 16-Bit                                                                   |

| Speed                      | 32MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SCI, SPI, UART/USART                     |

| Peripherals                | LVD, POR, PWM, WDT                                                       |

| Number of I/O              | 19                                                                       |

| Program Memory Size        | 32KB (32K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 1K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 5.5V ~ 18V                                                               |

| Data Converters            | A/D 6x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount, Wettable Flank                                            |

| Package / Case             | 32-VFQFN Exposed Pad                                                     |

| Supplier Device Package    | 32-HVQFN (5x5)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12zvls3f0mfmr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Revision History**

| Date              | Revision<br>Level | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28 September 2013 | 0.14              | <ul> <li>Updated Chapter 1, "Device Overview MC9S12ZVL-Family"</li> <li>Updated Chapter 10, "Analog-to-Digital Converter (ADC12B_LBA)"</li> <li>Updated Chapter 18, "Serial Communication Interface (S12SCIV6)"</li> <li>Updated Chapter 19, "Serial Peripheral Interface (S12SPIV5)"</li> <li>Updated Chapter 21, "LIN Physical Layer (S12LINPHYV2)""</li> <li>Updated Appendix A, "MCU Electrical Specifications"</li> <li>Updated Appendix O, "Detailed Register Address Map"</li> <li>Updated Appendix N, "Ordering Information"</li> </ul>                                                                                                             |

| 28 November 2013  | 0.15              | <ul> <li>Updated Chapter 1, "Device Overview MC9S12ZVL-Family"</li> <li>Updated Chapter 8, "ECC Generation Module (SRAM_ECCV2)"</li> <li>Updated Chapter 10, "Analog-to-Digital Converter (ADC12B_LBA)"</li> <li>Updated MC9S12ZVL"</li> <li>Updated Chapter 19, "Serial Peripheral Interface (S12SPIV5)"</li> <li>Updated Chapter 21, "LIN Physical Layer (S12LINPHYV2)""</li> <li>Updated Appendix A, "MCU Electrical Specifications"</li> </ul>                                                                                                                                                                                                          |

| 17 September 2014 | 1.00              | <ul> <li>Updated Chapter 1, "Device Overview MC9S12ZVL-Family"</li> <li>Updated Chapter 5, "Background Debug Controller (S12ZBDCV2)"</li> <li>Updated Chapter 7, "S12Z DebugLite (S12ZDBGV3)"</li> <li>Updated Chapter 22, "Flash Module (S12ZFTMRZ)"</li> <li>Updated Chapter 21, "LIN Physical Layer (S12LINPHYV2)""</li> <li>Updated Appendix A, "MCU Electrical Specifications"</li> <li>Updated Appendix O, "Detailed Register Address Map</li> <li>Updated Appendix M, "Package Information</li> </ul>                                                                                                                                                |

| 16 October 2014   | 1.01              | Updated Appendix A, "MCU Electrical Specifications"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 11 December 2014  | 2.00              | Initial version including ZVL128<br>• Updated Chapter 1, "Device Overview MC9S12ZVL-Family"<br>• Updated Chapter 2, "Port Integration Module (S12ZVLPIMV2)"<br>• Added Chapter 3, "5V Analog Comparator (ACMPV2)"<br>• Updated Chapter 7, "S12Z DebugLite (S12ZDBGV3)"<br>• Updated Chapter 10, "Analog-to-Digital Converter (ADC12B_LBA)"<br>• Added Chapter 11, "Digital Analog Converter (DAC_8B5V_V2)"<br>• Added Chapter 12, "Programmable Gain Amplifier (PGAV1)"<br>• Added Chapter 13, "Scalable Controller Area Network (S12MSCANV2)"<br>• Updated Chapter 22, "Flash Module (S12ZFTMRZ)"<br>• Updated Appendix O, "Detailed Register Address Map" |

| 05 May 2015       | 2.00 Draft D      | <ul> <li>Updated Chapter 1, "Device Overview MC9S12ZVL-Family"</li> <li>Added new version of Chapter 8, "ECC Generation Module<br/>(SRAM_ECCV2)"</li> <li>Added new version of Chapter 9, "S12 Clock, Reset and Power<br/>Management Unit (S12CPMU_UHV)"</li> <li>Added new version of Chapter 12, "Programmable Gain Amplifier<br/>(PGAV1)</li> <li>added VL128 specific parameter (3.3V VDDX mode, Supply Current<br/>Table) to Appendix A, "MCU Electrical Specifications</li> </ul>                                                                                                                                                                     |

## Chapter 14 Supply Voltage Sensor (BATSV3)

| 14.1 | Introduction                       | 429 |

|------|------------------------------------|-----|

|      | 14.1.1 Features                    | 429 |

|      | 14.1.2 Modes of Operation          | 429 |

|      | 14.1.3 Block Diagram               | 430 |

| 14.2 | External Signal Description        | 430 |

|      | 14.2.1 VSUP — Voltage Supply Pin   | 430 |

| 14.3 | Memory Map and Register Definition | 431 |

|      | 14.3.1 Register Summary            | 431 |

|      | 14.3.2 Register Descriptions       | 431 |

| 14.4 | Functional Description             | 435 |

|      | 14.4.1 General                     | 435 |

|      | 14.4.2 Interrupts                  | 435 |

## Chapter 15 Timer Module (TIM16B6CV3)

| 15.1 | Introduction                                                      |  |

|------|-------------------------------------------------------------------|--|

|      | 15.1.1 Features                                                   |  |

|      | 15.1.2 Modes of Operation                                         |  |

|      | 15.1.3 Block Diagrams                                             |  |

| 15.2 | External Signal Description                                       |  |

|      | 15.2.1 IOC5 - IOC0 — Input Capture and Output Compare Channel 5-0 |  |

| 15.3 | Memory Map and Register Definition                                |  |

|      | 15.3.1 Module Memory Map                                          |  |

|      | 15.3.2 Register Descriptions                                      |  |

| 15.4 | Functional Description                                            |  |

|      | 15.4.1 Prescaler                                                  |  |

|      | 15.4.2 Input Capture                                              |  |

|      | 15.4.3 Output Compare                                             |  |

| 15.5 | Resets                                                            |  |

| 15.6 | Interrupts                                                        |  |

|      | 15.6.1 Channel [5:0] Interrupt (C[5:0]F)                          |  |

|      | 15.6.2 Timer Overflow Interrupt (TOF)                             |  |

## Chapter 16 Timer Module (TIM16B2CV3)

| 16.1 | Introduction                                                      | 457 |

|------|-------------------------------------------------------------------|-----|

|      | 16.1.1 Features                                                   | 457 |

|      | 16.1.2 Modes of Operation                                         | 458 |

|      | 16.1.3 Block Diagrams                                             | 458 |

| 16.2 | External Signal Description                                       | 459 |

|      | 16.2.1 IOC1 - IOC0 — Input Capture and Output Compare Channel 1-0 | 459 |

| 16.3 | Memory Map and Register Definition                                | 459 |

- Instructions and Addressing modes optimized for C-Programming & Compiler

- MAC unit 32bit += 32bit\*32bit

- Hardware divider

- Single cycle multi-bit shifts (Barrel shifter)

- Special instructions for fixed point math

- Unimplemented opcode traps

- Unprogrammed byte value (0xFF) defaults to SWI instruction

## 1.4.1.1 Background Debug Controller (BDC)

- Background debug controller (BDC) with single-wire interface

- Non-intrusive memory access commands

- Supports in-circuit programming of on-chip nonvolatile memory

## 1.4.1.2 Debugger (DBG)

- Three comparators (A, B and D)

- Comparator A compares the full address bus and full 32-bit data bus

- Comparators B and D compare the full address bus only

- Each comparator can be configured to monitor PC addresses or addresses of data accesses

- Each comparator can select either read or write access cycles

- Comparator matches can force state sequencer state transitions

- Three comparator modes

- Simple address/data comparator match mode

- Inside address range mode, Addmin  $\leq$  Address  $\leq$  Addmax

- Outside address range match mode, Address < Addmin or Address > Addmax

- State sequencer control

- State transitions forced by comparator matches

- State transitions forced by software write to TRIG

- State transitions forced by an external event

- The following types of breakpoints

- CPU breakpoint entering active BDM on breakpoint (BDM)

- CPU breakpoint executing SWI on breakpoint (SWI)

## 1.4.2 Embedded Memory

## 1.4.2.1 Memory Access Integrity

- Illegal address detection

- ECC support on embedded NVM and system RAM

## 1.7.2.24 BDC and Debug Signals

## 1.7.2.24.1 BKGD — Background Debug signal

The BKGD signal is used as a pseudo-open-drain signal for the background debug communication. The BKGD signal has an internal pull-up device.

## 1.7.2.24.2 DBGEEV — External Event Input

This signal is the DBG external event input. It is input only. Within the DBG module, it allows an external event to force a state sequencer transition. A falling edge at the external event signal constitutes an event. Rising edges have no effect. The maximum frequency of events is half the internal core bus frequency.

## 1.7.2.25 CAN0 Signals

## 1.7.2.25.1 RXCAN0 Signal

This signal is associated with the receive functionality of the scalable controller area network controller (MSCAN0).

## 1.7.2.25.2 TXCAN0 Signal

This signal is associated with the transmit functionality of the scalable controller area network controller (MSCAN0).

## 1.7.2.26 LIN Physical Layer Signals

## 1.7.2.26.1 LIN

This pad is connected to the single-wire LIN data bus.

## 1.7.2.26.2 LPTXD

This is the LIN physical layer transmitter input signal.

## 1.7.2.26.3 LPRXD

This is the LIN physical layer receiver output signal.

## 1.7.2.26.4 LPDR1

This is the LIN LP0DR1 register bit, visible at the designated pin for debug purposes.

## 1.7.2.27 BCTL

BCTL is the ballast connection for the on chip voltage regulator. It provides the base current of an external PNP transistor of the VDDX and VDDA supplies.

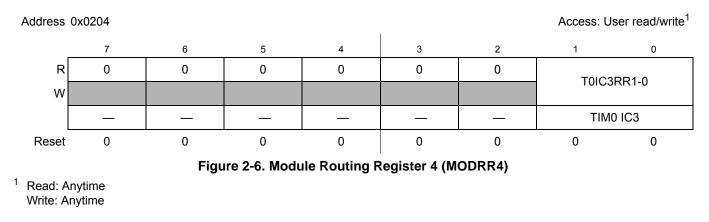

## 2.3.2.5 Module Routing Register 4 (MODRR4)

#### Table 2-7. MODRR4 Routing Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                        |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-0<br>T0IC3RR1-0 | Module Routing Register — TIM0 IC3 routingOne out of four different sources can be selected as input to timer channel 3.11 TIM0 input capture channel 3 is connected to ACLK10 TIM0 input capture channel 3 is connected to RXD101 TIM0 input capture channel 3 is connected to RXD000 TIM0 input capture channel 3 is connected to pin selected by MODRR2[T0C3RR] |

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>OVRUN  | <ul> <li>Overrun Flag — Indicates unexpected host activity before command completion.<br/>This occurs if a new command is received before the current command completion.<br/>With ACK enabled this also occurs if the host drives the BKGD pin low whilst a target ACK pulse is pending<br/>To protect internal resources from misinterpreted BDC accesses following an overrun, internal accesses are<br/>suppressed until a SYNC clears this bit.<br/>A SYNC clears the bit.</li> <li>No overrun detected.</li> <li>Overrun detected when issuing a BDC command.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3<br>NORESP | <ul> <li>No Response Flag — Indicates that the BDC internal action or data access did not complete. This occurs in the following scenarios:</li> <li>a) If no free cycle for an access is found within 512 core clock cycles. This could typically happen if a code loop without free cycles is executing with ACK enabled and STEAL clear.</li> <li>b) With ACK disabled or STEAL set, when an internal access is not complete before the host starts data/BDCCSRL retrieval or an internal write access is not complete before the host starts the next BDC command.</li> <li>c) Attempted internal memory or SYNC_PC accesses during STOP mode set NORESP if BDCCIS is clear. In the above cases, on setting NORESP, the BDC aborts the access if permitted. (For devices supporting EWAIT, BDC external accesses with EWAIT assertions, prevent a command from being aborted until EWAIT is deasserted).</li> <li>d) If a BACKGROUND command is issued whilst the device is in wait mode the NORESP bit is set but the command is not aborted. The active BDM request is completed when the device leaves wait mode. Furthermore subsequent CPU register access commands during wait mode set the NORESP bit, should it have been cleared.</li> <li>e) If a command is issued whilst awaiting return from Wait mode. This can happen when using STEP1 to step over a CPU WAI instruction, if the CPU has not returned from Wait mode regardless of the BDMACT state.</li> <li>When NORESP is set a value of 0xEE is returned for each data byte associated with the current access. Writing a "1" to this bit, clears the bit.</li> <li>Internal action or data access did not complete.</li> </ul> |

| 2<br>RDINV  | <ul> <li>Read Data Invalid Flag — Indicates invalid read data due to an ECC error during a BDC initiated read access. The access returns the actual data read from the location. Writing a "1" to this bit, clears the bit.</li> <li>0 No invalid read data detected.</li> <li>1 Invalid data returned during a BDC read access.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1<br>ILLACC | Illegal Access Flag — Indicates an attempted illegal access. This is set in the following cases:         When the attempted access addresses unimplemented memory         When the access attempts to write to the flash array         When a CPU register access is attempted with an invalid CRN (Section 5.4.5.1, "BDC Access Of CPU Registers).         Illegal accesses return a value of 0xEE for each data byte         Writing a "1" to this bit, clears the bit.         0 No illegal access detected.         1 Illegal BDC access detected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

#### Interrupt (S12ZINTV0)

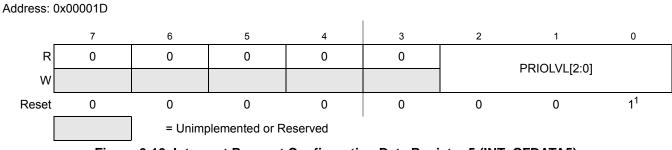

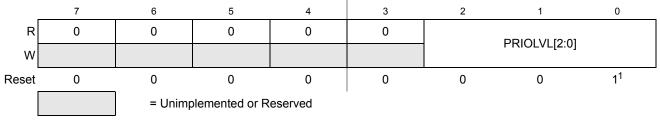

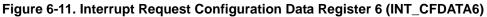

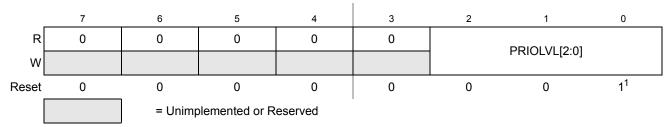

Figure 6-10. Interrupt Request Configuration Data Register 5 (INT\_CFDATA5)

<sup>1</sup> Please refer to the notes following the PRIOLVL[2:0] description below.

#### Address: 0x00001E

<sup>1</sup> Please refer to the notes following the PRIOLVL[2:0] description below.

#### Address: 0x00001F

#### Figure 6-12. Interrupt Request Configuration Data Register 7 (INT\_CFDATA7)

<sup>1</sup> Please refer to the notes following the PRIOLVL[2:0] description below.

#### Read: Anytime

Write: Anytime

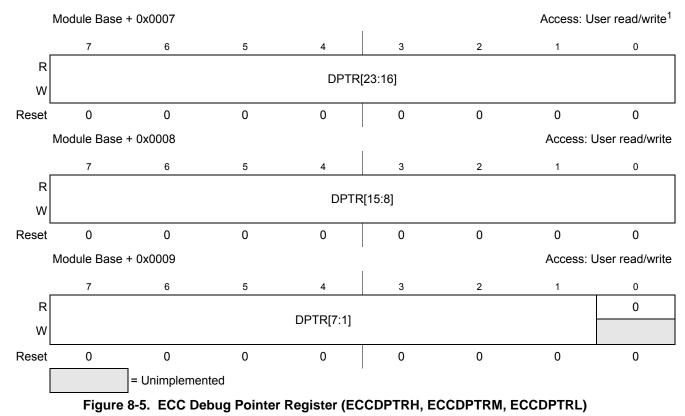

# 8.2.2.4 ECC Debug Pointer Register (ECCDPTRH, ECCDPTRM, ECCDPTRL)

<sup>1</sup> Read: Anytime Write: Anytime

#### Table 8-5. ECCDPTR Register Field Descriptions

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DPTR<br>[23:0] | <b>ECC Debug Pointer</b> — This register contains the system memory address which will be used for a debug access. Address bits not relevant for SRAM address space are not writeable, so the software should read back the pointer value to make sure the register contains the intended memory address. It is possible to write an address value to this register which points outside the system memory. There is no additional monitoring of the register content; therefore, the software must make sure that the address value points to the system memory space. |

| Address<br>Offset | Register<br>Name      |        | Bit 7    | 6       | 5           | 4       | 3       | 2       | 1      | Bit 0  |

|-------------------|-----------------------|--------|----------|---------|-------------|---------|---------|---------|--------|--------|

| 0x000E            | RESERVED              | R      | 0        | 0       | 0           | 0       | 0       | 0       | 0      | 0      |

| OXOOOL            | CPMUTEST1             | W      |          |         |             |         |         |         |        |        |

| 0x000F            | CPMU                  | R      | 0        | 0       | 0           | 0       | 0       | 0       | 0      | 0      |

|                   | ARMCOP                | W      | Bit 7    | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0  |

| 0x0010            | CPMU<br>HTCTL         | R<br>W | 0        | 0       | VSEL        | 0       | HTE     | HTDS    | HTIE   | HTIF   |

| 0x0011            | CPMU<br>LVCTL         | R<br>W | 0        | 0       | 0           | 0       | 0       | LVDS    | LVIE   | LVIF   |

| 0x0012            | CPMU<br>APICTL        | R<br>W | APICLK   | 0       | 0           | APIES   | APIEA   | APIFE   | APIE   | APIF   |

| 0x0013            | CPMUACLKTR            | R<br>W | ACLKTR5  | ACLKTR4 | ACLKTR3     | ACLKTR2 | ACLKTR1 | ACLKTR0 | 0      | 0      |

| 0x0014            | CPMUAPIRH             | R<br>W | APIR15   | APIR14  | APIR13      | APIR12  | APIR11  | APIR10  | APIR9  | APIR8  |

| 0x0015            | CPMUAPIRL             | R<br>W | APIR7    | APIR6   | APIR5       | APIR4   | APIR3   | APIR2   | APIR1  | APIR0  |

| 0x0016            | RESERVED              | R      | 0        | 0       | 0           | 0       | 0       | 0       | 0      | 0      |

| 0,0010            | V                     |        |          |         |             |         |         |         |        |        |

| 0x0017            | CPMUHTTR              | R<br>W | HTOE     | 0       | 0           | 0       | HTTR3   | HTTR2   | HTTR1  | HTTR0  |

| 0x0018            | CPMU<br>IRCTRIMH      | R<br>W |          |         | FCTRIM[4:0] |         |         | 0       | IRCTRI | M[9:8] |

| 0x0019            | CPMU<br>IRCTRIML      | R<br>W |          |         |             | IRCTRI  | M[7:0]  |         |        |        |

| 0x001A            | CPMUOSC               | R<br>W | OSCE     | 0       | Reserved    | 0       | 0       | 0       | 0      | 0      |

|                   |                       | R      | 0        | 0       | 0           | 0       | 0       | 0       | 0      |        |

| 0x001B            | CPMUPROT              | W      |          | 0       | 0           | 0       | 0       | 0       | 0      | PROT   |

| 0x001C            | RESERVED<br>CPMUTEST2 | R<br>W | 0        | 0       | 0           | 0       | 0       | 0       | 0      | 0      |

| 0x001D            | CPMU<br>VREGCTL       | R<br>W | VREG5VEN | 0       | 0           | 0       | 0       | 0       | EXTXON | INTXON |

| 0x001E            | CPMUOSC2              | R      | 0        | 0       | 0           | 0       | 0       | 0       | OMRE   | OSCMOD |

| UXUUTE            |                       | W      |          |         |             |         |         |         |        |        |

| 0x001F            | RESERVED              | R<br>W | 0        | 0       | 0           | 0       | 0       | 0       | 0      | 0      |

= Unimplemented or Reserved

Figure 9-3. CPMU Register Summary

S12 Clock, Reset and Power Management Unit (S12CPMU\_UHV)

## 9.3.2.10 S12CPMU\_UHV PLL Control Register (CPMUPLL)

This register controls the PLL functionality.

Module Base + 0x000A

|       | 7 | 6 | 5   | 4     | 3 | 2 | 1 | 0 |

|-------|---|---|-----|-------|---|---|---|---|

| R     | 0 | 0 |     | FM0   | 0 | 0 | 0 | 0 |

| W     |   |   | FM1 | FIVIU |   |   |   |   |

| Reset | 0 | 0 | 0   | 0     | 0 | 0 | 0 | 0 |

#### Figure 9-13. S12CPMU\_UHV PLL Control Register (CPMUPLL)

Read: Anytime

Write: Anytime if PROT=0 (CPMUPROT register) and PLLSEL=1 (CPMUCLKS register). Else write has no effect.

#### NOTE

Write to this register clears the LOCK and UPOSC status bits.

#### NOTE

Care should be taken to ensure that the bus frequency does not exceed the specified maximum when frequency modulation is enabled.

#### Table 9-9. CPMUPLL Field Descriptions

| Field            | Description                                                                                                                                                                                                                   |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5, 4<br>FM1, FM0 | PLL <b>Frequency Modulation Enable Bits</b> — FM1 and FM0 enable frequency modulation on the VCOCLK. This is to reduce noise emission. The modulation frequency is f <sub>ref</sub> divided by 16. See Table 9-10 for coding. |

#### Table 9-10. FM Amplitude selection

| FM1 | FM0 | FM Amplitude /<br>f <sub>VCO</sub> Variation |

|-----|-----|----------------------------------------------|

| 0   | 0   | FM off                                       |

| 0   | 1   | ±1%                                          |

| 1   | 0   | ±2%                                          |

| 1   | 1   | ±4%                                          |

S12 Clock, Reset and Power Management Unit (S12CPMU\_UHV)

## 9.5.4 PLL Clock Monitor Reset

In case of loss of PLL clock oscillation or the PLL clock frequency is below the failure assert frequency  $f_{PMFA}$  (see device electrical characteristics for values), the S12CPMU\_UHV generates a PLL Clock Monitor Reset. In Full Stop Mode the PLL and the PLL clock monitor are disabled.

## 9.5.5 Computer Operating Properly Watchdog (COP) Reset

The COP (free running watchdog timer) enables the user to check that a program is running and sequencing properly. When the COP is being used, software is responsible for keeping the COP from timing out. If the COP times out it is an indication that the software is no longer being executed in the intended sequence; thus COP reset is generated.

The clock source for the COP is either ACLK, IRCCLK or OSCCLK depending on the setting of the COPOSCSEL0 and COPOSCSEL1 bit.

Depending on the COP configuration there might be a significant latency time until COP is active again after exit from Stop Mode due to clock domain crossing synchronization. This latency time occurs if COP clock source is ACLK and the CSAD bit is set (please refer to CSAD bit description for details)

Table 9-35 gives an overview of the COP condition (run, static) in Stop Mode depending on legal configuration and status bit settings:

| COPOSCSEL1 | CSAD | PSTP | PCE | COPOSCSEL0 | OSCE | UPOSC | COP counter behavior in Stop Mode<br>(clock source) |  |

|------------|------|------|-----|------------|------|-------|-----------------------------------------------------|--|

| 1          | 0    | x    | x   | x          | x    | x     | Run (ACLK)                                          |  |

| 1          | 1    | x    | x   | x          | x    | x     | Static (ACLK)                                       |  |

| 0          | x    | 1    | 1   | 1          | 1    | 1     | Run (OSCCLK)                                        |  |

| 0          | ×    | 1    | 1   | 0          | 0    | x     | Static (IRCCLK)                                     |  |

| 0          | ×    | 1    | 1   | 0          | 1    | x     | Static (IRCCLK)                                     |  |

| 0          | x    | 1    | 0   | 0          | x    | x     | Static (IRCCLK)                                     |  |

| 0          | x    | 1    | 0   | 1          | 1    | 1     | Static (OSCCLK)                                     |  |

| 0          | х    | 0    | 1   | 1          | 1    | 1     | Static (OSCCLK)                                     |  |

| 0          | х    | 0    | 1   | 0          | 1    | x     | Static (IRCCLK)                                     |  |

| 0          | х    | 0    | 1   | 0          | 0    | 0     | Static (IRCCLK)                                     |  |

| 0          | х    | 0    | 0   | 1          | 1    | 1     | Satic (OSCCLK)                                      |  |

| 0          | х    | 0    | 0   | 0          | 1    | 1     | Static (IRCCLK)                                     |  |

| 0          | х    | 0    | 0   | 0          | 1    | 0     | Static (IRCCLK)                                     |  |

| 0          | х    | 0    | 0   | 0          | 0    | 0     | Static (IRCCLK)                                     |  |

Table 9-35. COP condition (run, static) in Stop Mode

# Chapter 10 Analog-to-Digital Converter (ADC12B\_LBA)

| Revision<br>Number | Revision<br>Date | Sections Affected                                                              | Description of Changes                                                                                                                             |

|--------------------|------------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| V1.37              | 19. Apr 2013     | -                                                                              | Updates from review of reference manual to fix typos etc.                                                                                          |

| V1.38              | 30. Apr 2013     | 10.5.2.13/10-314                                                               | Provided more detailed information regarding captured information in bits RIDX_IMD[5:0] for different scenarios of Sequence Abort Event execution. |

| V1.39              | 02. Jul 2013     | 10.5.2.6/10-303                                                                | Update of: Timing considerations for Restart Mode                                                                                                  |

|                    |                  |                                                                                |                                                                                                                                                    |

| V1.40              | 02. Oct 2013     | entire document                                                                | Updated formatting and wording correction for entire document (for technical publications).                                                        |

| V2.00              | 14. Oct. 2014    | 10.3/10-287,<br>10.5.2.15/10-316,<br>10.5.2.17/10-321,<br>Figure 10-2./10-291, | Added option bits to conversion command for top level SoC specific feature/function implementation option.                                         |

| V3.00              | 27. Feb. 2015    | 10.5.2.16/10-319,<br>10.1/10-285                                               | Changed ADCCMD_1 VRH_SEL, VRL_SEL<br>Single document for all versions (V1,V2,V3)                                                                   |

| V3.01              | 15. Oct 2015     | 10.5.2.16/10-319                                                               | Added clarification: CMD_EIF not set for internal channels                                                                                         |

#### Table 10-1. Revision History

## 10.1 Differences ADC12B\_LBA V1 vs V2 vs V3

#### NOTE

Device reference manuals specify which module version is integrated on the device. Some reference manuals support families of devices, with device dependent module versions. This chapter describes the superset. The feature differences are listed in Table 10-2.

| Table 10-2. | Comparison | of ADC12B | _LBA Module Versions | ; |

|-------------|------------|-----------|----------------------|---|

|             |            |           |                      |   |

| Feature                                                                                | V1  | V2  | V3  |

|----------------------------------------------------------------------------------------|-----|-----|-----|

| ADC Command Register 0 (ADCCMD_0),<br>ADC Command Register 2 (ADCCMD_2): OPT[3:0] bits | No  | Yes | Yes |

| ADC Command Register 1 (ADCCMD_1):VRH_SEL[1:0]                                         | No  | No  | Yes |

| ADC Command Register 1 (ADCCMD_1):VRH_SEL,VRL_SEL                                      | Yes | Yes | No  |

The MSCAN facilitates a sophisticated message storage system which addresses the requirements of a broad range of network applications.

## 13.4.2.1 Message Transmit Background

Modern application layer software is built upon two fundamental assumptions:

- Any CAN node is able to send out a stream of scheduled messages without releasing the CAN bus between the two messages. Such nodes arbitrate for the CAN bus immediately after sending the previous message and only release the CAN bus in case of lost arbitration.

- The internal message queue within any CAN node is organized such that the highest priority message is sent out first, if more than one message is ready to be sent.

The behavior described in the bullets above cannot be achieved with a single transmit buffer. That buffer must be reloaded immediately after the previous message is sent. This loading process lasts a finite amount of time and must be completed within the inter-frame sequence (IFS) to be able to send an uninterrupted stream of messages. Even if this is feasible for limited CAN bus speeds, it requires that the CPU reacts with short latencies to the transmit interrupt.

A double buffer scheme de-couples the reloading of the transmit buffer from the actual message sending and, therefore, reduces the reactiveness requirements of the CPU. Problems can arise if the sending of a message is finished while the CPU re-loads the second buffer. No buffer would then be ready for transmission, and the CAN bus would be released.

At least three transmit buffers are required to meet the first of the above requirements under all circumstances. The MSCAN has three transmit buffers.

The second requirement calls for some sort of internal prioritization which the MSCAN implements with the "local priority" concept described in Section 13.4.2.2, "Transmit Structures."

## 13.4.2.2 Transmit Structures

The MSCAN triple transmit buffer scheme optimizes real-time performance by allowing multiple messages to be set up in advance. The three buffers are arranged as shown in Figure 13-38.

All three buffers have a 13-byte data structure similar to the outline of the receive buffers (see Section 13.3.3, "Programmer's Model of Message Storage"). An additional Transmit Buffer Priority Register (TBPR) contains an 8-bit local priority field (PRIO) (see Section 13.3.3.4, "Transmit Buffer Priority Register (TBPR)"). The remaining two bytes are used for time stamping of a message, if required (see Section 13.3.3.5, "Time Stamp Register (TSRH–TSRL)").

To transmit a message, the CPU must identify an available transmit buffer, which is indicated by a set transmitter buffer empty (TXEx) flag (see Section 13.3.2.7, "MSCAN Transmitter Flag Register (CANTFLG)"). If a transmit buffer is available, the CPU must set a pointer to this buffer by writing to the CANTBSEL register (see Section 13.3.2.11, "MSCAN Transmit Buffer Selection Register (CANTBSEL)"). This makes the respective buffer accessible within the CANTXFG address space (see Section 13.3.3, "Programmer's Model of Message Storage"). The algorithmic feature associated with the CANTBSEL register simplifies the transmit buffer selection. In addition, this scheme makes the handler

The Prescaler can be calculated as follows depending on logical value of the PTPS[7:0] and PRNT bit: PRNT = 1 : Prescaler = PTPS[7:0] + 1

| PTPS7 | PTPS6 | PTPS5 | PTPS4 | PTPS3 | PTPS2 | PTPS1 | PTPS0 | Prescale<br>Factor |

|-------|-------|-------|-------|-------|-------|-------|-------|--------------------|

| 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1                  |

| 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 2                  |

| 0     | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 3                  |

| 0     | 0     | 0     | 0     | 0     | 0     | 1     | 1     | 4                  |

| -     | -     | -     | -     | -     | -     | -     | -     | -                  |

| -     | -     | -     | -     | -     | -     | -     | -     | -                  |

| -     | -     | -     | -     | -     | -     | -     | -     | -                  |

| 0     | 0     | 0     | 1     | 0     | 0     | 1     | 1     | 20                 |

| 0     | 0     | 0     | 1     | 0     | 1     | 0     | 0     | 21                 |

| 0     | 0     | 0     | 1     | 0     | 1     | 0     | 1     | 22                 |

| -     | -     | -     | -     | -     | -     | -     | -     | -                  |

| -     | -     | -     | -     | -     | -     | -     | -     | -                  |

| -     | -     | -     | -     | -     | -     | -     | -     | -                  |

| 1     | 1     | 1     | 1     | 1     | 1     | 0     | 0     | 253                |

| 1     | 1     | 1     | 1     | 1     | 1     | 0     | 1     | 254                |

| 1     | 1     | 1     | 1     | 1     | 1     | 1     | 0     | 255                |

| 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 256                |

Table 15-17. Precision Timer Prescaler Selection Examples when PRNT = 1

## 15.4 Functional Description

This section provides a complete functional description of the timer TIM16B6CV3 block. Please refer to the detailed timer block diagram in Figure 15-22 as necessary.

#### Timer Module (TIM16B2CV3)

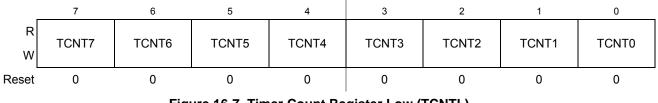

Module Base + 0x0005

Figure 16-7. Timer Count Register Low (TCNTL)

The 16-bit main timer is an up counter.

A full access for the counter register should take place in one clock cycle. A separate read/write for high byte and low byte will give a different result than accessing them as a word.

Read: Anytime

Write: Has no meaning or effect in the normal mode; only writable in special modes .

The period of the first count after a write to the TCNT registers may be a different size because the write is not synchronized with the prescaler clock.

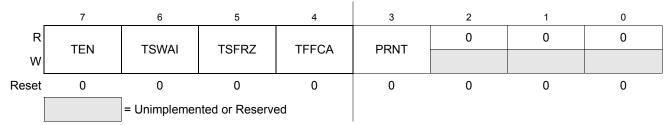

## 16.3.2.4 Timer System Control Register 1 (TSCR1)

Module Base + 0x0006

Figure 16-8. Timer System Control Register 1 (TSCR1)

Read: Anytime

Write: Anytime

#### Table 16-4. TSCR1 Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                    |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TEN   | <ul> <li>Timer Enable</li> <li>Disables the main timer, including the counter. Can be used for reducing power consumption.</li> <li>Allows the timer to function normally.</li> <li>If for any reason the timer is not active, there is no ÷64 clock for the pulse accumulator because the ÷64 is generated by the timer prescaler.</li> </ul> |

| 6<br>TSWAI | <ul> <li>Timer Module Stops While in Wait</li> <li>Allows the timer module to continue running during wait.</li> <li>Disables the timer module when the MCU is in the wait mode. Timer interrupts cannot be used to get the MCU out of wait.</li> <li>TSWAI also affects pulse accumulator.</li> </ul>                                         |

| Field             | Description                                                                                                                                                                                             |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–6<br>KEYEN[1:0] | <b>Backdoor Key Security Enable Bits</b> — The KEYEN[1:0] bits define the enabling of backdoor key access to the Flash module as shown in Table 22-9.                                                   |

| 5–2<br>RNV[5:2]   | <b>Reserved Nonvolatile Bits</b> — The RNV bits should remain in the erased state for future enhancements.                                                                                              |

| 1–0<br>SEC[1:0]   | <b>Flash Security Bits</b> — The SEC[1:0] bits define the security state of the MCU as shown in Table 22-10. If the Flash module is unsecured using backdoor key access, the SEC bits are forced to 10. |

#### Table 22-8. FSEC Field Descriptions

| KEYEN[1:0] | Status of Backdoor Key Access |

|------------|-------------------------------|

| 00         | DISABLED                      |

| 01         | DISABLED <sup>1</sup>         |

| 10         | ENABLED                       |

| 11         | DISABLED                      |

#### Table 22-9. Flash KEYEN States

Preferred KEYEN state to disable backdoor key access.

#### Table 22-10. Flash Security States

| SEC[1:0] | Status of Security   |

|----------|----------------------|

| 00       | SECURED              |

| 01       | SECURED <sup>1</sup> |

| 10       | UNSECURED            |

| 11       | SECURED              |

<sup>1</sup> Preferred SEC state to set MCU to secured state.

The security function in the Flash module is described in Section 22.5.

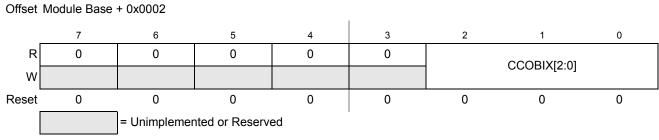

## 22.3.2.3 Flash CCOB Index Register (FCCOBIX)

The FCCOBIX register is used to indicate the amount of parameters loaded into the FCCOB registers for Flash memory operations.

Figure 22-7. FCCOB Index Register (FCCOBIX)

CCOBIX bits are readable and writable while remaining bits read 0 and are not writable.

Flash Module (S12ZFTMRZ)

Upon clearing CCIF to launch the Verify Backdoor Access Key command, the Memory Controller will check the FSEC KEYEN bits to verify that this command is enabled. If not enabled, the Memory Controller sets the ACCERR bit in the FSTAT register and terminates. If the command is enabled, the Memory Controller compares the key provided in FCCOB to the backdoor comparison key in the Flash configuration field with Key 0 compared to 0xFF\_FE00, etc. If the backdoor keys match, security will be released. If the backdoor keys do not match, security is not released and all future attempts to execute the Verify Backdoor Access Key command are aborted (set ACCERR) until a reset occurs. The CCIF flag is set after the Verify Backdoor Access Key operation has completed.

| Register | Error Bit | Error Condition                                                                          |  |  |

|----------|-----------|------------------------------------------------------------------------------------------|--|--|

|          |           | Set if CCOBIX[2:0] != 100 at command launch                                              |  |  |

|          |           | Set if an incorrect backdoor key is supplied                                             |  |  |

|          | ACCERR    | Set if backdoor key access has not been enabled (KEYEN[1:0] != 10, see Section 22.3.2.2) |  |  |

| FSTAT    |           | Set if the backdoor key has mismatched since the last reset                              |  |  |

|          | FPVIOL    | None                                                                                     |  |  |

|          | MGSTAT1   | None                                                                                     |  |  |

|          | MGSTAT0   | None                                                                                     |  |  |

Table 22-54. Verify Backdoor Access Key Command Error Handling

## 22.4.7.12 Set User Margin Level Command

The Set User Margin Level command causes the Memory Controller to set the margin level for future read operations of the P-Flash or EEPROM block.

| Register | FCCOB Parameters                              |  |  |  |

|----------|-----------------------------------------------|--|--|--|

| FCCOB0   | 0x0D Global address [23:16] to ident          |  |  |  |

| FCCOB1   | Global address [15:0] to identify Flash block |  |  |  |

| FCCOB2   | Margin level setting.                         |  |  |  |

Upon clearing CCIF to launch the Set User Margin Level command, the Memory Controller will set the user margin level for the targeted block and then set the CCIF flag.

## NOTE

When the EEPROM block is targeted, the EEPROM user margin levels are applied only to the EEPROM reads. However, when the P-Flash block is targeted, the P-Flash user margin levels are applied to both P-Flash and EEPROM reads. It is not possible to apply user margin levels to the P-Flash block only.

Valid margin level settings for the Set User Margin Level command are defined in Table 22-56.

## NOTE

When the EEPROM block is targeted, the EEPROM field margin levels are applied only to the EEPROM reads. However, when the P-Flash block is targeted, the P-Flash field margin levels are applied to both P-Flash and EEPROM reads. It is not possible to apply field margin levels to the P-Flash block only.

Valid margin level settings for the Set Field Margin Level command are defined in Table 22-59.

| FCCOB2 | Level Description                 |  |  |

|--------|-----------------------------------|--|--|

| 0x0000 | Return to Normal Level            |  |  |

| 0x0001 | User Margin-1 Level <sup>1</sup>  |  |  |

| 0x0002 | User Margin-0 Level <sup>2</sup>  |  |  |

| 0x0003 | Field Margin-1 Level <sup>1</sup> |  |  |

| 0x0004 | Field Margin-0 Level <sup>2</sup> |  |  |

<sup>1</sup> Read margin to the erased state

<sup>2</sup> Read margin to the programmed state

#### Table 22-60. Set Field Margin Level Command Error Handling

| Register | Error Bit | Error Condition                                                     |  |  |  |  |

|----------|-----------|---------------------------------------------------------------------|--|--|--|--|

| FSTAT    | ACCERR    | Set if CCOBIX[2:0] != 010 at command launch                         |  |  |  |  |

|          |           | Set if command not available in current mode (see Table 22-28)      |  |  |  |  |

|          |           | Set if an invalid global address [23:0] is supplied see Table 22-2) |  |  |  |  |

|          |           | Set if an invalid margin level setting is supplied                  |  |  |  |  |

|          | FPVIOL    | None                                                                |  |  |  |  |

|          | MGSTAT1   | None                                                                |  |  |  |  |

|          | MGSTAT0   | None                                                                |  |  |  |  |

#### CAUTION

Field margin levels must only be used during verify of the initial factory programming.

#### NOTE

Field margin levels can be used to check that Flash memory contents have adequate margin for data retention at the normal level setting. If unexpected results are encountered when checking Flash memory contents at field margin levels, the Flash memory contents should be erased and reprogrammed.

| Protection Update<br>Selection code [1:0] | Protection register selection                                                                                                        |  |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|

| bit 1                                     | Update EEPROM protection<br>0 - keep unchanged (do not update)<br>1 - update EEPROM protection with new DFPROT value loaded on FCCOB |  |

| Table 22-68 | . Protection | Override | selection | description |

|-------------|--------------|----------|-----------|-------------|

|-------------|--------------|----------|-----------|-------------|

If the comparison key successfully matches the key programmed in the Flash Configuration Field the Protection Override command will preserve the current values of registers FPROT and DFPROT stored in an internal area and will override these registers as selected by the Protection Update Selection field with the value(s) loaded on FCCOB parameters. The new values loaded into FPROT and/or DFPROT can reconfigure protection without any restriction (by increasing, decreasing or disabling protection limits). If the command executes successfully the FPSTAT FPOVRD bit will set.

If the comparison key does not match the key programmed in the Flash Configuration Field, or if the key loaded on FCCOB is 16'hFFFF, the value of registers FPROT and DFPROT will be restored to their original contents before executing the Protection Override command and the FPSTAT FPOVRD bit will be cleared. If the contents of the Protection Override Comparison Key in the Flash Configuration Field is left in the erased state (i.e. 16'hFFFF) the Protection Override feature is permanently disabled. If the command execution is flagged as an error (ACCERR being set for incorrect command launch) the values of FPROT and DFPROT will not be modified.

The Protection Override command can be called multiple times and every time it is launched it will preserve the current values of registers FPROT and DFPROT in a single-entry buffer to be restored later; when the Protection Override command is launched to restore FPROT and DFPROT these registers will assume the values they had before executing the Protection Override command on the last time. If contents of FPROT and/or DFPROT registers were modified by direct register writes while protection is overridden these modifications will be lost. Running Protection Override command to restore the contents of registers FPROT and DFPROT will not force them to the reset values.

| Register | Error Bit | Error Condition                                                                                                                                                                                                                               |  |  |  |  |

|----------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|          | ACCERR    | Set if CCOBIX[2:0] != (001, 010 or 011) at command launch.                                                                                                                                                                                    |  |  |  |  |

|          |           | Set if command not available in current mode (see Table 22-28).                                                                                                                                                                               |  |  |  |  |

|          |           | Set if protection is supposed to be restored (if key does not match or is invalid) and Protection Override command was not run previously (bit FPSTAT FPOVRD is 0) so there are no previous valid values of FPROT and DFPROT to be re-loaded. |  |  |  |  |

| FSTAT    |           | Set if Protection Update Selection[1:0] = 00 (in case of CCOBIX[2:0] = 010 or 011)                                                                                                                                                            |  |  |  |  |

|          |           | Set if Protection Update Selection[1:0] = 00, CCOBIX[2:0] = 001 and a valid comparison key is loaded as a command parameter.                                                                                                                  |  |  |  |  |

|          | FPVIOL    | None                                                                                                                                                                                                                                          |  |  |  |  |

|          | MGSTAT1   | None                                                                                                                                                                                                                                          |  |  |  |  |

|          | MGSTAT0   | None                                                                                                                                                                                                                                          |  |  |  |  |

Table 22-69. Protection Override Command Error Handling

# Appendix H PGA Electrical Specifications

This section describe the electrical characteristics of the PGA module.

## H.1 Static Electrical Characteristics

Table H-1. Static Electrical Characteristics - PGA

| Supply | Supply voltage 4.85V $\leq$ V_DDA $\leq$ 5.15 V, -40°C < T_J < 150°C |                             |       |     |                        |      |  |

|--------|----------------------------------------------------------------------|-----------------------------|-------|-----|------------------------|------|--|

| Num    | Ratings                                                              | Symbol                      | Min   | Тур | Max                    | Unit |  |

| 1      | Settling time                                                        | t <sub>PGA_settling</sub>   |       | 5   | 10                     | us   |  |

| 2      | Common mode voltage input range                                      | V <sub>CM</sub>             | 1.5   |     | V <sub>DDA</sub> - 1.5 | V    |  |

| 3      | DC Gain Error for<br>gain A <sub>PGA</sub>                           | E <sub>A</sub>              | -2.5  |     | 1.0                    | %    |  |

| 4      | Initial input offset                                                 | V <sub>initial_offset</sub> | -10.0 |     | 10.0                   | mV   |  |

| 5      | Input offset difference<br>to offset at room<br>temperature          | V <sub>var_offset</sub>     | -2    | -   | 2                      | mV   |  |

| 6      | Current consumption                                                  | I <sub>PGA</sub>            |       | 1   |                        | mA   |  |

| 7      | Supply voltage                                                       | V <sub>DDA</sub>            | 4.5   | 5.0 | 5.5                    | V    |  |

| 8      | output voltage range                                                 | V <sub>OUT</sub>            | 0.5   |     | V <sub>DDA</sub> -0.5  | V    |  |