Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | S12Z                                                                    |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SCI, SPI, UART/USART                    |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 19                                                                      |

| Program Memory Size        | 32KB (32K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 128 x 8                                                                 |

| RAM Size                   | 1K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 5.5V ~ 18V                                                              |

| Data Converters            | A/D 6x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount, Wettable Flank                                           |

| Package / Case             | 32-VFQFN Exposed Pad                                                    |

| Supplier Device Package    | 32-HVQFN (5x5)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12zvls3f0vfm |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| External | I Signal Description                                                                                           | 181                                                                                                                 |

|----------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| 7.2.1    | External Event Input                                                                                           | 181                                                                                                                 |

| Memory   | Map and Registers                                                                                              | 182                                                                                                                 |

| 7.3.1    | Module Memory Map                                                                                              | 182                                                                                                                 |

| 7.3.2    | Register Descriptions                                                                                          | 184                                                                                                                 |

| Function | nal Description                                                                                                | 196                                                                                                                 |

| 7.4.1    | DBG Operation                                                                                                  | 196                                                                                                                 |

| 7.4.2    | Comparator Modes                                                                                               | 197                                                                                                                 |

| 7.4.3    | Events                                                                                                         | 200                                                                                                                 |

| 7.4.4    | State Sequence Control                                                                                         | 202                                                                                                                 |

| 7.4.5    | Breakpoints                                                                                                    | 202                                                                                                                 |

| Applica  | tion Information                                                                                               | 204                                                                                                                 |

| 7.5.1    | Avoiding Unintended Breakpoint Re-triggering                                                                   | 204                                                                                                                 |

| 7.5.2    | Breakpoints from other S12Z sources                                                                            | 204                                                                                                                 |

|          | 7.2.1<br>Memory<br>7.3.1<br>7.3.2<br>Function<br>7.4.1<br>7.4.2<br>7.4.3<br>7.4.4<br>7.4.5<br>Applica<br>7.5.1 | 7.4.4State Sequence Control7.4.5BreakpointsApplication Information7.5.1Avoiding Unintended Breakpoint Re-triggering |

## Chapter 8 ECC Generation Module (SRAM\_ECCV2)

| 8.1 | Introduc | xtion                           |   | 05 |

|-----|----------|---------------------------------|---|----|

|     | 8.1.1    | Features                        |   | 05 |

| 8.2 | Memory   | / Map and Register Definition   |   | 06 |

|     | 8.2.1    | Register Summary                |   | 06 |

|     | 8.2.2    | Register Descriptions           |   | 08 |

| 8.3 | Function | nal Description                 |   | 12 |

|     | 8.3.1    | Aligned Memory Write Access     |   | 13 |

|     | 8.3.2    | Non-aligned Memory Write Access |   | 13 |

|     | 8.3.3    | Memory Read Access              |   | 14 |

|     | 8.3.4    | Memory Initialization           |   | 14 |

|     | 8.3.5    | Interrupt Handling              | 2 | 14 |

|     | 8.3.6    | ECC Algorithm                   | 2 | 15 |

|     | 8.3.7    | ECC Debug Behavior              | 2 | 15 |

|     |          |                                 |   |    |

# Chapter 9

# S12 Clock, Reset and Power Management Unit (S12CPMU\_UHV)

| 9.1 | Introdu  | ction                                        |  |

|-----|----------|----------------------------------------------|--|

|     | 9.1.1    | Features                                     |  |

|     | 9.1.2    | Modes of Operation                           |  |

|     | 9.1.3    | S12CPMU_UHV Block Diagram                    |  |

| 9.2 | Signal I | Description                                  |  |

|     | 9.2.1    | RESET                                        |  |

|     | 9.2.2    | EXTAL and XTAL                               |  |

|     | 9.2.3    | VSUP — Regulator Power Input Pin             |  |

|     | 9.2.4    | VDDA, VSSA — Regulator Reference Supply Pins |  |

|     | 9.2.5    | VDDX, VSSX — Pad Supply Pins                 |  |

|     | 9.2.6    | BCTL — Base Control Pin for external PNP     |  |

|     |          |                                              |  |

#### Device Overview MC9S12ZVL-Family

This byte can be erased and programmed like any other Flash location. Two bits of this byte are used for security (SEC[1:0]). The contents of this byte are copied into the Flash security register (FSEC) during a reset sequence.

The meaning of the security bits SEC[1:0] is shown in Table 1-10. For security reasons, the state of device security is controlled by two bits. To put the device in unsecured mode, these bits must be programmed to SEC[1:0] = `10`. All other combinations put the device in a secured mode. The recommended value to put the device in secured state is the inverse of the unsecured state, i.e. SEC[1:0] = `01`.

| SEC[1:0] | Security State |

|----------|----------------|

| 00       | 1 (secured)    |

| 01       | 1 (secured)    |

| 10       | 0 (unsecured)  |

| 11       | 1 (secured)    |

| Table | 1-10. | Security | Bits |

|-------|-------|----------|------|

|       |       | 00000    |      |

#### NOTE

Please refer to the Flash block description for more security byte details.

## **1.11.3** Operation of the Secured Microcontroller

By securing the device, unauthorized access to the EEPROM and Flash memory contents is prevented. Secured operation has the following effects on the microcontroller:

### 1.11.3.1 Normal Single Chip Mode (NS)

- Background debug controller (BDC) operation is completely disabled.

- Execution of Flash and EEPROM commands is restricted (described in flash block description).

## 1.11.3.2 Special Single Chip Mode (SS)

- Background debug controller (BDC) commands are restricted

- Execution of Flash and EEPROM commands is restricted (described in flash block description).

In special single chip mode the device is in active BDM after reset. In special single chip mode on a secure device, only the BDC mass erase and BDC control and status register commands are possible. BDC access to memory mapped resources is disabled. The BDC can only be used to erase the EEPROM and Flash memory without giving access to their contents.

## 1.11.4 Unsecuring the Microcontroller

Unsecuring the microcontroller can be done using three different methods:

- 1. Backdoor key access

- 2. Reprogramming the security bits

- 3. Complete memory erase

# 1.12 Resets and Interrupts

## 1.12.1 Resets

Table 1-11. lists all reset sources and the vector locations. Resets are explained in detail in the Chapter 9, "S12 Clock, Reset and Power Management Unit (S12CPMU\_UHV)".

| Vector Address | Reset Source            | CCR<br>Mask | Local Enable                                                |

|----------------|-------------------------|-------------|-------------------------------------------------------------|

| 0xFFFFFC       | Power-On Reset (POR)    | None        | None                                                        |

|                | Low Voltage Reset (LVR) | None        | None                                                        |

|                | External pin RESET      | None        | None                                                        |

|                | Clock monitor reset     | None        | OSCE Bit in CPMUOSC and<br>OMRE Bit in CPMUOSC2<br>register |

|                | COP watchdog reset      | None        | CR[2:0] in CPMUCOP register                                 |

Table 1-11. Reset Sources and Vector Locations

## 1.12.2 Interrupt Vectors

Table 1-12 lists all interrupt sources and vectors in the default order of priority. The interrupt module description provides an interrupt vector base register (IVBR) to relocate the vectors.

Table 1-12. Interrupt Vector Locations (Sheet 1 of 4)

| Vector Address <sup>1</sup> | Interrupt Source                            | CCR<br>Mask | Local Enable   | Wake up<br>from STOP | Wake up<br>from WAIT |

|-----------------------------|---------------------------------------------|-------------|----------------|----------------------|----------------------|

| Vector base + 0x1F8         | Unimplemented page1 op-code trap<br>(SPARE) | None        | None           | -                    | -                    |

| Vector base + 0x1F4         | Unimplemented page2 op-code trap<br>(TRAP)  | None        | None           | -                    | -                    |

| Vector base + 0x1F0         | Software interrupt instruction (SWI)        | None        | None           | -                    | -                    |

| Vector base + 0x1EC         | System call interrupt instruction<br>(SYS)  | None        | None           | -                    | -                    |

| Vector base + 0x1E8         | Machine exception                           | None        | None           | -                    | -                    |

| Vector base + 0x1E4         | Reserved                                    |             |                |                      |                      |

| Vector base + 0x1E0         |                                             |             | Reserved       |                      |                      |

| Vector base + 0x1DC         | Spurious interrupt                          | _           | None           | -                    | -                    |

| Vector base + 0x1D8         | XIRQ interrupt request                      | X bit       | None           | Yes                  | Yes                  |

| Vector base + 0x1D4         | IRQ interrupt request                       | l bit       | IRQCR(IRQEN)   | Yes                  | Yes                  |

| Vector base + 0x1D0         | RTI time-out interrupt                      | l bit       | CPMUINT (RTIE) | See CPMU section     | Yes                  |

### NOTE

The term stop mode (STOP) is limited to voltage regulator operating in reduced performance mode (RPM). Refer to "Low Power Modes" section in device overview.

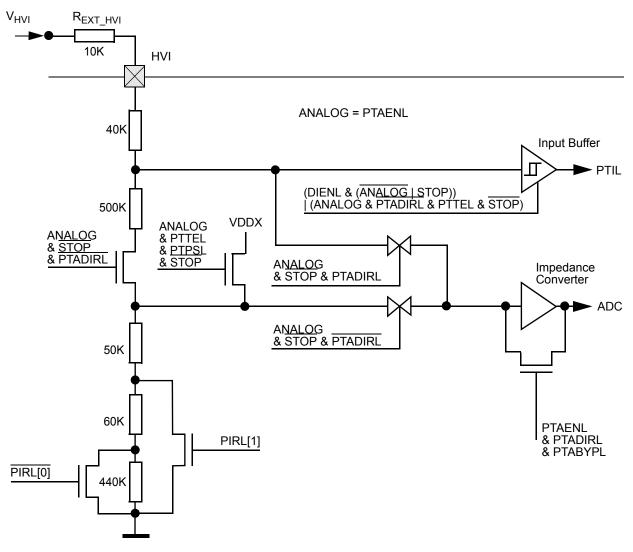

Figure 2-32. HVI Block Diagram

Voltages up to  $V_{HVI}$  can be applied to the HVI pin. Internal voltage dividers scale the input signals down to logic level. There are two modes, digital and analog, where these signals can be processed.

## 2.4.5.1 Digital Mode Operation

In digital mode (PTAENL=0) the input buffer is enabled if DIENL=1. The synchronized pin input state determined at threshold level  $V_{TH HVI}$  can be read in register PTIL. Interrupt flag (PIFL) is set on input

accesses to mask out individual data bus bits and to use R/W access qualification in the comparison. Comparators can be configured to monitor a range of addresses.

When configured for data access comparisons, the match is generated if the address (and optionally data) of a data access matches the comparator value.

Configured for monitoring opcode addresses, the match is generated when the associated opcode reaches the execution stage of the instruction queue, but before execution of that opcode.

When a match with a comparator register value occurs, the associated control logic can force the state sequencer to another state (see Figure 7-19).

The state sequencer can transition freely between the states 1, 2 and 3. On transition to Final State, a breakpoint can be generated and the state sequencer returns to state0, disarming the DBG.

Independent of the comparators, state sequencer transitions can be forced by the external event input or by writing to the TRIG bit in the DBGC1 control register.

## 7.4.2 Comparator Modes

The DBG contains three comparators, A, B, and D. Each comparator compares the address stored in DBGXAH, DBGXAM, and DBGXAL with the PC (opcode addresses) or selected address bus (data accesses). Furthermore, comparator A can compare the data buses to values stored in DBGXD3-0 and allow data bit masking.

The comparators can monitor the buses for an exact address or an address range. The comparator configuration is controlled by the control register contents and the range control by the DBGC2 contents.

The comparator control register also allows the type of data access to be included in the comparison through the use of the RWE and RW bits. The RWE bit controls whether the access type is compared for the associated comparator and the RW bit selects either a read or write access for a valid match.

The INST bit in each comparator control register is used to determine the matching condition. By setting INST, the comparator matches opcode addresses, whereby the databus, data mask, RW and RWE bits are ignored. The comparator register must be loaded with the exact opcode address.

The comparator can be configured to match memory access addresses by clearing the INST bit.

Each comparator match can force a transition to another state sequencer state (see Section 7.4.3, "Events").

Once a successful comparator match has occurred, the condition that caused the original match is not verified again on subsequent matches. Thus if a particular data value is matched at a given address, this address may not contain that data value when a subsequent match occurs.

Match[0, 1, 3] map directly to Comparators [A, B, D] respectively, except in range modes (see Section 7.3.2.2, "Debug Control Register2 (DBGC2)"). Comparator priority rules are described in the event priority section (Section 7.4.3.4, "Event Priorities").

S12 Clock, Reset and Power Management Unit (S12CPMU\_UHV)

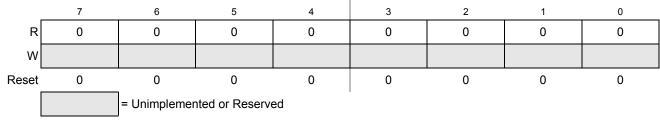

## 9.3.2.13 Reserved Register CPMUTEST0

### NOTE

This reserved register is designed for factory test purposes only, and is not intended for general user access. Writing to this register when in Special Mode can alter the S12CPMU\_UHV's functionality.

Module Base + 0x000D

### Figure 9-16. Reserved Register (CPMUTEST0)

Read: Anytime

Write: Only in Special Mode

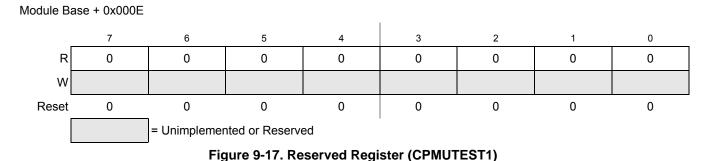

## 9.3.2.14 Reserved Register CPMUTEST1

NOTE

This reserved register is designed for factory test purposes only, and is not intended for general user access. Writing to this register when in Special Mode can alter the S12CPMU\_UHV's functionality.

Read: Anytime

Write: Only in Special Mode

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>RSTA | Restart Event (Restart from Top of Command Sequence List) — This bit indicates that a Restart Event is executed. The ADC loads the conversion command from top of the active Sequence Command List when no conversion or conversion sequence is ongoing. This bit is cleared when the first conversion command of the sequence from top of active Sequence Command List has been loaded into the ADCCMD register. This bit can only be set if bit ADC_EN is set. This bit is cleared if bit ADC_EN is clear. Data Bus Control: |

|           | This bit can be controlled via the data bus if access control is configured accordingly via ACC_CFG[1:0].<br>Writing a value of 1'b0 does not clear the flag.<br>Writing a one to this bit does not clear it but causes an overrun if the bit has already been set. See also<br>Section 10.6.3.2.6, "Conversion flow control in case of conversion sequence control bit overrun scenarios for<br>more details.                                                                                                                 |

|           | Internal Interface Control:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|           | This bit can be controlled via the internal interface Signal "Restart" if access control is configured accordingly via ACC_CFG[1:0]. After being set an additional request via internal interface Signal "Restart" causes an overrun. See conversion flow control in case of overrun situations for more details.                                                                                                                                                                                                              |

|           | General:<br>In conversion flow control mode "Trigger Mode" when bit RSTA gets set bit TRIG is set simultaneously if one of<br>the following has been executed:<br>- "End Of List" command type has been executed or is about to be executed                                                                                                                                                                                                                                                                                    |

|           | <ul> <li>Sequence Abort Event</li> <li>Continue with commands from active Sequence Command List.</li> <li>Restart from top of active Sequence Command List.</li> </ul>                                                                                                                                                                                                                                                                                                                                                         |

| 4<br>LDOK | Load OK for alternative Command Sequence List — This bit indicates if the preparation of the alternative<br>Sequence Command List is done and Command Sequence List must be swapped with the Restart Event. This<br>bit is cleared when bit RSTA is set (Restart Event executed) and the Command Sequence List got swapped.<br>This bit can only be set if bit ADC_EN is set.<br>This bit is cleared if bit ADC_EN is clear.<br>This bit is forced to zero if bit CSL_BMOD is clear.                                           |

|           | Data Bus Control:         This bit can be controlled via the data bus if access control is configured accordingly via ACC_CFG[1:0].         Writing a value of 1'b0 does not clear the flag.         To set bit LDOK the bits LDOK and RSTA must be written simultaneously.         After being set this bit can not be cleared by writing a value of 1'b1. See also Section 10.6.3.2.6, "Conversion flow control in case of conversion sequence control bit overrun scenarios for more details.                               |

|           | Internal Interface Control:<br>This bit can be controlled via the internal interface Signal "LoadOK" and "Restart" if access control is configured<br>accordingly via ACC_CFG[1:0]. With the assertion of Interface Signal "Restart" the interface Signal "LoadOK" is<br>evaluated and bit LDOK set accordingly (bit LDOK set if Interface Signal "LoadOK" asserted when Interface<br>Signal "Restart" asserts).<br>General:                                                                                                   |

|           | Only in "Restart Mode" if a Restart Event occurs without bit LDOK being set the error flag LDOK_EIF is set except<br>when the respective Restart Request occurred after or simultaneously with a Sequence Abort Request.<br>The LDOK_EIF error flag is also not set in "Restart Mode" if the first Restart Event occurs after:<br>- ADC got enabled<br>- Exit from Stop Mode<br>- ADC Soft-Reset                                                                                                                               |

|           | <ul><li>0 Load of alternative list done.</li><li>1 Load alternative list.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CH_SEL[5] | CH_SEL[4] | CH_SEL[3] | CH_SEL[2] | CH_SEL[1] | CH_SEL[0] | Analog Input Channel                                                                             |

|-----------|-----------|-----------|-----------|-----------|-----------|--------------------------------------------------------------------------------------------------|

| 0         | 0         | 0         | 0         | 0         | 0         | VRL_0/1 (V1, V2, see Table 10-2)<br>VRL_0 (V3, see Table 10-2)                                   |

| 0         | 0         | 0         | 0         | 0         | 1         | VRH_0/1 (V1, V2, see Table 10-2)<br>VRH_0/1/2 (V3, see Table 10-2)                               |

| 0         | 0         | 0         | 0         | 1         | 0         | (VRH_0/1 + VRL_0/1) / 2 (V1, V2, see Table 10-2)<br>(VRH_0/1/2 + VRL_0) / 2 (V3, see Table 10-2) |

| 0         | 0         | 0         | 0         | 1         | 1         | Reserved                                                                                         |

| 0         | 0         | 0         | 1         | 0         | 0         | Reserved                                                                                         |

| 0         | 0         | 0         | 1         | 0         | 1         | Reserved                                                                                         |

| 0         | 0         | 0         | 1         | 1         | 0         | Reserved                                                                                         |

| 0         | 0         | 0         | 1         | 1         | 1         | Reserved                                                                                         |

| 0         | 0         | 1         | 0         | 0         | 0         | Internal_0<br>(ADC temperature sense)                                                            |

| 0         | 0         | 1         | 0         | 0         | 1         | Internal_1                                                                                       |

| 0         | 0         | 1         | 0         | 1         | 0         | Internal_2                                                                                       |

| 0         | 0         | 1         | 0         | 1         | 1         | Internal_3                                                                                       |

| 0         | 0         | 1         | 1         | 0         | 0         | Internal_4                                                                                       |

| 0         | 0         | 1         | 1         | 0         | 1         | Internal_5                                                                                       |

| 0         | 0         | 1         | 1         | 1         | 0         | Internal_6                                                                                       |

| 0         | 0         | 1         | 1         | 1         | 1         | Internal_7                                                                                       |

| 0         | 1         | 0         | 0         | 0         | 0         | ANO                                                                                              |

| 0         | 1         | 0         | 0         | 0         | 1         | AN1                                                                                              |

| 0         | 1         | 0         | 0         | 1         | 0         | AN2                                                                                              |

| 0         | 1         | 0         | 0         | 1         | 1         | AN3                                                                                              |

| 0         | 1         | 0         | 1         | 0         | 0         | AN4                                                                                              |

| 0         | 1         | x         | x         | x         | x         | ANx                                                                                              |

| 1         | x         | x         | x         | x         | x         | Reserved                                                                                         |

Table 10-24. Analog Input Channel Select

### NOTE

ANx in Table 10-24 is the maximum number of implemented analog input channels on the device. Please refer to the device overview of the reference manual for details regarding number of analog input channels.

MC912ZVL Family Reference Manual, Rev. 2.41

Please note that there is always a pump phase of two ADC\_CLK cycles before the sample phase begins, hence glitches during the pump phase could impact the conversion accuracy for short sample times.

## 10.6.3 Digital Sub-Block

The digital sub-block contains a list-based programmer's model and the control logic for the analog sub-block circuits.

## 10.6.3.1 Analog-to-Digital (A/D) Machine

The A/D machine performs the analog-to-digital conversion. The resolution is program selectable to be either 8- or 10- or 12 bits. The A/D machine uses a successive approximation architecture. It functions by comparing the sampled and stored analog voltage with a series of binary coded discrete voltages.

By following a binary search algorithm, the A/D machine identifies the discrete voltage that is nearest to the sampled and stored voltage.

Only analog input signals within the potential range of VRL\_0/1 to VRH\_0/1/3 (availability of VRL\_1 and VRH\_2 see Table 10-2) (A/D reference potentials) will result in a non-railed digital output code.

## 10.6.3.2 Introduction of the Programmer's Model

The ADC\_LBA provides a programmer's model that uses a system memory list-based architecture for definition of the conversion command sequence and conversion result handling.

The Command Sequence List (CSL) and Result Value List (RVL) are implemented in double buffered manner and the buffer mode is user selectable for each list (bits CSL\_BMOD, RVL\_BMOD). The 32-bit wide conversion command is double buffered and the currently active command is visible in the ADC register map at ADCCMD register space.

- Function:

Start the first conversion of a conversion sequence which is defined in the active Command Sequence List

- Requested by:

- Positive edge of internal interface signal Trigger

- Write Access via data bus to set control bit TRIG

- When finished:

This bit is cleared by the ADC when the first conversion of the sequence is beginning to sample

- Mandatory Requirements:

- In all ADC conversion flow control modes bit TRIG is only set (Trigger Event executed) if the Trigger Event occurs while no conversion or conversion sequence is ongoing (ADC idle)

- In ADC conversion flow control mode "Restart Mode" with a Restart Event in progress it is not allowed that a Trigger Event occurs before the background command load phase has finished (Restart Event has been executed) else the error flag TRIG\_EIF is set

- In ADC conversion flow control mode "Trigger Mode" a Restart Event causes bit TRIG being set automatically. Bit TRIG is set when no conversion or conversion sequence is ongoing (ADC idle) and the RVL done condition is reached by one of the following:

\* A "End Of List" command type has been executed

\* A Sequence Abort Event is in progress or has been executed

The ADC executes the Restart Event followed by the Trigger Event.

- In ADC conversion flow control mode "Trigger Mode" a Restart Event and a simultaneous Trigger Event via internal interface or data bus causes the TRIG\_EIF bit being set and ADC cease operation.

• **Restart Event** (with current active CSL)

Internal Interface Signal: Restart

Corresponding Bit Name: RSTA

- Function:

- Go to top of active CSL (clear index register for CSL)

- Load one background command register and wait for Trigger (CSL offset register is not switched independent of bit CSL\_BMOD)

- Set error flag RSTA\_EIF when a Restart Request occurs before one of the following conditions was reached:

\* The "End Of List" command type has been executed

\* Depending on bit STR\_SEQA if the "End Of List" command type is about to be executed \* The current CSL has been aborted or is about to be aborted due to a Sequence Abort Request.

- Requested by:

- Positive edge of internal interface signal Restart

- Write Access via data bus to set control bit RSTA

# Chapter 11 Digital Analog Converter (DAC\_8B5V\_V2)

## 11.1 Revision History

### Table 11-1. Revision History Table

| 1.4 | 17-Nov10 | 11.2.2                      | Update the behavior of the DACU pin during stop mode                              |

|-----|----------|-----------------------------|-----------------------------------------------------------------------------------|

| 1.5 | 29-Aug13 | 11.2.2, 11.3                | added note about settling time<br>added link to DACM register inside section 11.3 |

| 2.0 | 30-Jan14 | 11.2.3, 11.4.2.1,<br>11.5.4 | added mode "Internal DAC only"                                                    |

| 2.1 | 13-May15 | Figure 11-5                 | correct read value of reserved register, Figure 11-5                              |

## Glossary

### Table 11-2. Terminology

| Term | Meaning                     |

|------|-----------------------------|

| DAC  | Digital to Analog Converter |

| VRL  | Low Reference Voltage       |

| VRH  | High Reference Voltage      |

| FVR  | Full Voltage Range          |

| SSC  | Special Single Chip         |

# 11.2 Introduction

The DAC\_8B5V module is a digital to analog converter. The converter works with a resolution of 8 bit and generates an output voltage between VRL and VRH.

The module consists of configuration registers and two analog functional units, a DAC resistor network and an operational amplifier.

The configuration registers provide all required control bits for the DAC resistor network and for the operational amplifier.

The DAC resistor network generates the desired analog output voltage. The unbuffered voltage from the DAC resistor network output can be routed to the external DACU pin. When enabled, the buffered voltage from the operational amplifier output is available on the external AMP pin.

The operational amplifier is also stand alone usable.

Figure 11-1 shows the block diagram of the DAC\_8B5V module.

## **13.3 Memory Map and Register Definition**

This section provides a detailed description of all registers accessible in the MSCAN.

## 13.3.1 Module Memory Map

Figure 13-3 gives an overview on all registers and their individual bits in the MSCAN memory map. The *register address* results from the addition of *base address* and *address offset*. The *base address* is determined at the MCU level and can be found in the MCU memory map description. The *address offset* is defined at the module level.

The MSCAN occupies 64 bytes in the memory space. The base address of the MSCAN module is determined at the MCU level when the MCU is defined. The register decode map is fixed and begins at the first address of the module address offset.

The detailed register descriptions follow in the order they appear in the register map.

## 15.1.2 Modes of Operation

Stop: Timer is off because clocks are stopped.

Freeze: Timer counter keeps on running, unless TSFRZ in TSCR1 is set to 1.

Wait: Counters keeps on running, unless TSWAI in TSCR1 is set to 1.

Normal: Timer counter keep on running, unless TEN in TSCR1 is cleared to 0.

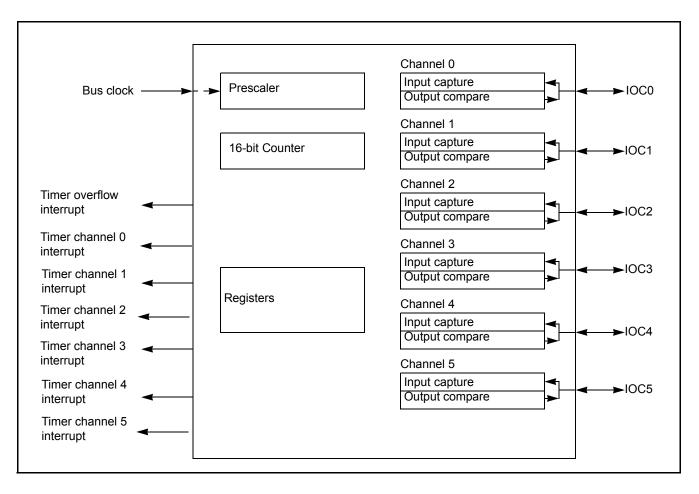

### 15.1.3 Block Diagrams

Figure 15-1. TIM16B6CV3 Block Diagram

# Chapter 16 Timer Module (TIM16B2CV3)

| V03.00 | Jan. 28, 2009 |                                                     | Initial version                                                                                                                                                                                                                                                                   |

|--------|---------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V03.01 | Aug. 26, 2009 | 16.1.2/16-458<br>16.3.2.2/16-461,<br>16.4.3/16-473  | <ul> <li>Correct typo: TSCR -&gt;TSCR1;</li> <li>Correct typo: ECTxxx-&gt;TIMxxx</li> <li>Add description, "a counter overflow when TTOV[7] is set", to be the condition of channel 7 override event.</li> <li>Phrase the description of OC7M to make it more explicit</li> </ul> |

| V03.02 | Apri,12,2010  | 16.3.2.6/16-464<br>16.3.2.9/16-466<br>16.4.3/16-473 | -update TCRE bit description                                                                                                                                                                                                                                                      |

| V03.03 | Jan,14,2013   |                                                     | -single source generate different channel guide                                                                                                                                                                                                                                   |

## 16.1 Introduction

The basic scalable timer consists of a 16-bit, software-programmable counter driven by a flexible programmable prescaler.

This timer can be used for many purposes, including input waveform measurements while simultaneously generating an output waveform.

This timer could contain up to 2 input capture/output compare channels. The input capture function is used to detect a selected transition edge and record the time. The output compare function is used for generating output signals or for timer software delays.

A full access for the counter registers or the input capture/output compare registers should take place in one clock cycle. Accessing high byte and low byte separately for all of these registers may not yield the same result as accessing them in one word.

## 16.1.1 Features

The TIM16B2CV3 includes these distinctive features:

- Up to 2 channels available. (refer to device specification for exact number)

- All channels have same input capture/output compare functionality.

- Clock prescaling.

- 16-bit counter.

The WAKE bit in SCI control register 1 (SCICR1) determines how the SCI is brought out of the standby state to process an incoming message. The WAKE bit enables either idle line wakeup or address mark wakeup.

### 18.4.6.6.1 Idle Input line Wakeup (WAKE = 0)

In this wakeup method, an idle condition on the RXD pin clears the RWU bit and wakes up the SCI. The initial frame or frames of every message contain addressing information. All receivers evaluate the addressing information, and receivers for which the message is addressed process the frames that follow. Any receiver for which a message is not addressed can set its RWU bit and return to the standby state. The RWU bit remains set and the receiver remains on standby until another idle character appears on the RXD pin.

Idle line wakeup requires that messages be separated by at least one idle character and that no message contains idle characters.

The idle character that wakes a receiver does not set the receiver idle bit, IDLE, or the receive data register full flag, RDRF.

The idle line type bit, ILT, determines whether the receiver begins counting logic 1s as idle character bits after the start bit or after the stop bit. ILT is in SCI control register 1 (SCICR1).

### 18.4.6.6.2 Address Mark Wakeup (WAKE = 1)

In this wakeup method, a logic 1 in the most significant bit (MSB) position of a frame clears the RWU bit and wakes up the SCI. The logic 1 in the MSB position marks a frame as an address frame that contains addressing information. All receivers evaluate the addressing information, and the receivers for which the message is addressed process the frames that follow. Any receiver for which a message is not addressed can set its RWU bit and return to the standby state. The RWU bit remains set and the receiver remains on standby until another address frame appears on the RXD pin.

The logic 1 MSB of an address frame clears the receiver's RWU bit before the stop bit is received and sets the RDRF flag.

Address mark wakeup allows messages to contain idle characters but requires that the MSB be reserved for use in address frames.

### NOTE

With the WAKE bit clear, setting the RWU bit after the RXD pin has been idle can cause the receiver to wake up immediately.

## 18.4.7 Single-Wire Operation

Normally, the SCI uses two pins for transmitting and receiving. In single-wire operation, the RXD pin is disconnected from the SCI. The SCI uses the TXD pin for both receiving and transmitting.

Serial Peripheral Interface (S12SPIV5)

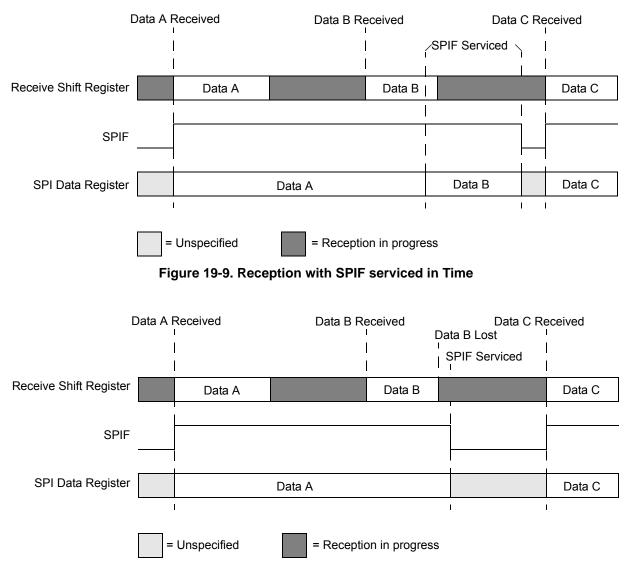

Figure 19-10. Reception with SPIF serviced too late

# 19.4 Functional Description

The SPI module allows a duplex, synchronous, serial communication between the MCU and peripheral devices. Software can poll the SPI status flags or SPI operation can be interrupt driven.

The SPI system is enabled by setting the SPI enable (SPE) bit in SPI control register 1. While SPE is set, the four associated SPI port pins are dedicated to the SPI function as:

- Slave select  $(\overline{SS})$

- Serial clock (SCK)

- Master out/slave in (MOSI)

- Master in/slave out (MISO)

| IBC2-0<br>(bin) | SCL Tap<br>(clocks) | SDA Tap<br>(clocks) |

|-----------------|---------------------|---------------------|

| 000             | 5                   | 1                   |

| 001             | 6                   | 1                   |

| 010             | 7                   | 2                   |

| 011             | 8                   | 2                   |

| 100             | 9                   | 3                   |

| 101             | 10                  | 3                   |

| 110             | 12                  | 4                   |

| 111             | 15                  | 4                   |

| Table 20-4. I-Bus | Tap and Prese | cale Values |

|-------------------|---------------|-------------|

|-------------------|---------------|-------------|

#### Table 20-5. Prescale Divider Encoding

| IBC5-3<br>(bin) | scl2start<br>(clocks) | scl2stop<br>(clocks) | scl2tap<br>(clocks) | tap2tap<br>(clocks) |

|-----------------|-----------------------|----------------------|---------------------|---------------------|

| 000             | 2                     | 7                    | 4                   | 1                   |

| 001             | 2                     | 7                    | 4                   | 2                   |

| 010             | 2                     | 9                    | 6                   | 4                   |

| 011             | 6                     | 9                    | 6                   | 8                   |

| 100             | 14                    | 17                   | 14                  | 16                  |

| 101             | 30                    | 33                   | 30                  | 32                  |

| 110             | 62                    | 65                   | 62                  | 64                  |

| 111             | 126                   | 129                  | 126                 | 128                 |

#### Table 20-6. Multiplier Factor

| IBC7-6 | MUL      |

|--------|----------|

| 00     | 01       |

| 01     | 02       |

| 10     | 04       |

| 11     | RESERVED |

The number of clocks from the falling edge of SCL to the first tap (Tap[1]) is defined by the values shown in the scl2tap column of Table 20-4, all subsequent tap points are separated by 2<sup>IBC5-3</sup> as shown in the tap2tap column in Table 20-5. The SCL Tap is used to generated the SCL period and the SDA Tap is used to determine the delay from the falling edge of SCL to SDA changing, the SDA hold time.

IBC7–6 defines the multiplier factor MUL. The values of MUL are shown in the Table 20-6.

#### LIN Physical Layer (S12LINPHYV2)

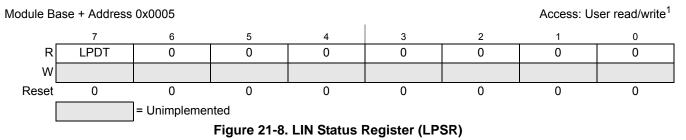

## 21.3.2.6 LIN Status Register (LPSR)

<sup>1</sup> Read: Anytime

Write: Never, writes to this register have no effect

#### Table 21-7. LPSR Field Description

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LPDT | <ul> <li>LIN Transmitter TxD-dominant timeout Status Bit — This read-only bit signals that the LPTxD pin is still dominant after a TxD-dominant timeout. As long as the LPTxD is dominant after the timeout the LIN transmitter is shut down and the LPTDIF is set again after attempting to clear it.</li> <li>If there was a TxD-dominant timeout, LPTxD has ceased to be dominant after the timeout.</li> <li>LPTxD is still dominant after a TxD-dominant timeout.</li> </ul> |

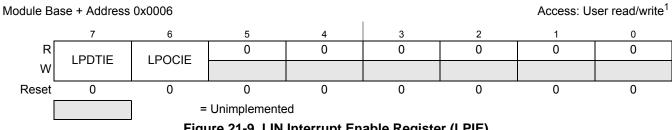

## 21.3.2.7 LIN Interrupt Enable Register (LPIE)

Figure 21-9. LIN Interrupt Enable Register (LPIE)

<sup>1</sup> Read: Anytime Write: Anytime

Flash Module (S12ZFTMRZ)

Upon clearing CCIF to launch the Verify Backdoor Access Key command, the Memory Controller will check the FSEC KEYEN bits to verify that this command is enabled. If not enabled, the Memory Controller sets the ACCERR bit in the FSTAT register and terminates. If the command is enabled, the Memory Controller compares the key provided in FCCOB to the backdoor comparison key in the Flash configuration field with Key 0 compared to 0xFF\_FE00, etc. If the backdoor keys match, security will be released. If the backdoor keys do not match, security is not released and all future attempts to execute the Verify Backdoor Access Key command are aborted (set ACCERR) until a reset occurs. The CCIF flag is set after the Verify Backdoor Access Key operation has completed.

| Register | Error Bit | Error Condition                                                                          |

|----------|-----------|------------------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] != 100 at command launch                                              |

|          |           | Set if an incorrect backdoor key is supplied                                             |

|          |           | Set if backdoor key access has not been enabled (KEYEN[1:0] != 10, see Section 22.3.2.2) |

| FSTAT    |           | Set if the backdoor key has mismatched since the last reset                              |

|          | FPVIOL    | None                                                                                     |

|          | MGSTAT1   | None                                                                                     |

|          | MGSTAT0   | None                                                                                     |

Table 22-54. Verify Backdoor Access Key Command Error Handling

## 22.4.7.12 Set User Margin Level Command

The Set User Margin Level command causes the Memory Controller to set the margin level for future read operations of the P-Flash or EEPROM block.

| Register | FCCOB Parameters                              |                                                   |  |  |

|----------|-----------------------------------------------|---------------------------------------------------|--|--|

| FCCOB0   | 0x0D                                          | Global address [23:16] to identify Flash<br>block |  |  |

| FCCOB1   | Global address [15:0] to identify Flash block |                                                   |  |  |

| FCCOB2   | Margin level setting.                         |                                                   |  |  |

Upon clearing CCIF to launch the Set User Margin Level command, the Memory Controller will set the user margin level for the targeted block and then set the CCIF flag.

### NOTE

When the EEPROM block is targeted, the EEPROM user margin levels are applied only to the EEPROM reads. However, when the P-Flash block is targeted, the P-Flash user margin levels are applied to both P-Flash and EEPROM reads. It is not possible to apply user margin levels to the P-Flash block only.

Valid margin level settings for the Set User Margin Level command are defined in Table 22-56.

# Appendix H PGA Electrical Specifications

This section describe the electrical characteristics of the PGA module.

# H.1 Static Electrical Characteristics

Table H-1. Static Electrical Characteristics - PGA

| Supply | Supply voltage 4.85V $\leq$ V_DDA $\leq$ 5.15 V, -40°C < T_J < 150°C |                             |       |     |                        |      |  |

|--------|----------------------------------------------------------------------|-----------------------------|-------|-----|------------------------|------|--|

| Num    | Ratings                                                              | Symbol                      | Min   | Тур | Max                    | Unit |  |

| 1      | Settling time                                                        | t <sub>PGA_settling</sub>   |       | 5   | 10                     | us   |  |

| 2      | Common mode voltage input range                                      | V <sub>CM</sub>             | 1.5   |     | V <sub>DDA</sub> - 1.5 | V    |  |

| 3      | DC Gain Error for<br>gain A <sub>PGA</sub>                           | E <sub>A</sub>              | -2.5  |     | 1.0                    | %    |  |

| 4      | Initial input offset                                                 | V <sub>initial_offset</sub> | -10.0 |     | 10.0                   | mV   |  |

| 5      | Input offset difference<br>to offset at room<br>temperature          | V <sub>var_offset</sub>     | -2    | -   | 2                      | mV   |  |

| 6      | Current consumption                                                  | I <sub>PGA</sub>            |       | 1   |                        | mA   |  |

| 7      | Supply voltage                                                       | V <sub>DDA</sub>            | 4.5   | 5.0 | 5.5                    | V    |  |

| 8      | output voltage range                                                 | V <sub>OUT</sub>            | 0.5   |     | V <sub>DDA</sub> -0.5  | V    |  |

MC912ZVL Family Reference Manual, Rev. 2.41