Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | S12Z                                                                     |

| Core Size                  | 16-Bit                                                                   |

| Speed                      | 32MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SCI, SPI, UART/USART                     |

| Peripherals                | LVD, POR, PWM, WDT                                                       |

| Number of I/O              | 19                                                                       |

| Program Memory Size        | 32KB (32K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 1K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 5.5V ~ 18V                                                               |

| Data Converters            | A/D 6x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount, Wettable Flank                                            |

| Package / Case             | 32-VFQFN Exposed Pad                                                     |

| Supplier Device Package    | 32-HVQFN (5x5)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12zvls3f0vfmr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Instructions and Addressing modes optimized for C-Programming & Compiler

- MAC unit 32bit += 32bit\*32bit

- Hardware divider

- Single cycle multi-bit shifts (Barrel shifter)

- Special instructions for fixed point math

- Unimplemented opcode traps

- Unprogrammed byte value (0xFF) defaults to SWI instruction

# 1.4.1.1 Background Debug Controller (BDC)

- Background debug controller (BDC) with single-wire interface

- Non-intrusive memory access commands

- Supports in-circuit programming of on-chip nonvolatile memory

# 1.4.1.2 Debugger (DBG)

- Three comparators (A, B and D)

- Comparator A compares the full address bus and full 32-bit data bus

- Comparators B and D compare the full address bus only

- Each comparator can be configured to monitor PC addresses or addresses of data accesses

- Each comparator can select either read or write access cycles

- Comparator matches can force state sequencer state transitions

- Three comparator modes

- Simple address/data comparator match mode

- Inside address range mode, Addmin  $\leq$  Address  $\leq$  Addmax

- Outside address range match mode, Address < Addmin or Address > Addmax

- State sequencer control

- State transitions forced by comparator matches

- State transitions forced by software write to TRIG

- State transitions forced by an external event

- The following types of breakpoints

- CPU breakpoint entering active BDM on breakpoint (BDM)

- CPU breakpoint executing SWI on breakpoint (SWI)

# 1.4.2 Embedded Memory

## 1.4.2.1 Memory Access Integrity

- Illegal address detection

- ECC support on embedded NVM and system RAM

#### Device Overview MC9S12ZVL-Family

This byte can be erased and programmed like any other Flash location. Two bits of this byte are used for security (SEC[1:0]). The contents of this byte are copied into the Flash security register (FSEC) during a reset sequence.

The meaning of the security bits SEC[1:0] is shown in Table 1-10. For security reasons, the state of device security is controlled by two bits. To put the device in unsecured mode, these bits must be programmed to SEC[1:0] = `10`. All other combinations put the device in a secured mode. The recommended value to put the device in secured state is the inverse of the unsecured state, i.e. SEC[1:0] = `01`.

| SEC[1:0] | Security State |

|----------|----------------|

| 00       | 1 (secured)    |

| 01       | 1 (secured)    |

| 10       | 0 (unsecured)  |

| 11       | 1 (secured)    |

| Table | 1-10. | Security | Bits |

|-------|-------|----------|------|

|       |       | 00000    |      |

#### NOTE

Please refer to the Flash block description for more security byte details.

# **1.11.3** Operation of the Secured Microcontroller

By securing the device, unauthorized access to the EEPROM and Flash memory contents is prevented. Secured operation has the following effects on the microcontroller:

# 1.11.3.1 Normal Single Chip Mode (NS)

- Background debug controller (BDC) operation is completely disabled.

- Execution of Flash and EEPROM commands is restricted (described in flash block description).

# 1.11.3.2 Special Single Chip Mode (SS)

- Background debug controller (BDC) commands are restricted

- Execution of Flash and EEPROM commands is restricted (described in flash block description).

In special single chip mode the device is in active BDM after reset. In special single chip mode on a secure device, only the BDC mass erase and BDC control and status register commands are possible. BDC access to memory mapped resources is disabled. The BDC can only be used to erase the EEPROM and Flash memory without giving access to their contents.

# 1.11.4 Unsecuring the Microcontroller

Unsecuring the microcontroller can be done using three different methods:

- 1. Backdoor key access

- 2. Reprogramming the security bits

- 3. Complete memory erase

#### Port Integration Module (S12ZVLPIMV2)

| Port | Pin | Pin Function<br>& Priority | I/O | Description                                              | Routing<br>Register Bit | Pin Function<br>after Reset |

|------|-----|----------------------------|-----|----------------------------------------------------------|-------------------------|-----------------------------|

| S    | PS3 | ECLK                       | 0   | Free-running clock                                       | —                       | GPIO                        |

|      |     | (IOC0_5)                   | I/O | TIM0 channel 5                                           | T0C5RR                  |                             |

|      |     | SS0                        | I/O | SPI0 slave select                                        | —                       |                             |

|      |     | PTS[3]/<br>KWS[3]          | I/O | General-purpose; with interrupt and key-wakeup           | —                       |                             |

|      | PS2 | DBGEEV                     | I   | DBG external event                                       | —                       |                             |

|      |     | TXCAN0                     | 0   | MSCAN0 transmit                                          | CAN0RR                  |                             |

|      |     | (IOC0_4)                   | I/O | TIM0 channel 4                                           | T0C4RR                  |                             |

|      |     | SCK0                       | I/O | SPI0 serial clock                                        | —                       |                             |

|      |     | PTS[2]/<br>KWS[2]          | I/O | General-purpose; with interrupt and key-wakeup           | —                       |                             |

|      | PS1 | (IOC0_3 <sup>2</sup> )     | I/O | TIM0 channel 3                                           | T0C3RR, T0IC3RR1-0      |                             |

|      |     | (TXD0)/<br>(LPDC0)         | 0   | SCI0 transmit/<br>LPTXD0 direct control by LP0DR[LP0DR1] | S0L0RR2-0               |                             |

|      |     | (PWM6)                     | 0   | PWM option 6                                             | PWM6RR                  |                             |

|      |     | MOSI0                      | I/O | SPI0 master out/slave in                                 | —                       |                             |

|      |     | PTS[1]/<br>KWS[1]          | I/O | General-purpose; with interrupt and key-wakeup           | _                       |                             |

|      | PS0 | RXCAN0                     | Ι   | MSCAN0 receive                                           | CAN0RR                  |                             |

|      |     | (IOC0_2)                   | I/O | TIM0 channel 2                                           | T0C2RR                  |                             |

|      |     | (RXD0)                     | I   | SCI0 receive                                             | S0L0RR2-0               |                             |

|      |     | (PWM4)                     | 0   | PWM option 4                                             | PWM4RR                  |                             |

|      |     | MISO0                      | I/O | SPI0 master in/slave out                                 | —                       |                             |

|      |     | PTS[0]/<br>KWS[0]          | I/O | General-purpose; with interrupt and key-wakeup           | _                       |                             |

| S0L0RR[2:0] | Description                                                                                   |

|-------------|-----------------------------------------------------------------------------------------------|

| 000         | Default setting:<br>SCI0 connects to LINPHY0, interface internal only                         |

| 001         | Direct control setting:<br>LP0DR[LPDR1] register bit controls LPTXD0, interface internal only |

| 100         | Probe setting:<br>SCI0 connects to LINPHY0, interface accessible on 2 external pins           |

| 110         | Conformance test setting:<br>Interface opened and all 4 signals routed externally             |

#### **Table 2-3. Preferred Interface Configurations**

## NOTE

For standalone usage of SCI0 on external pins set S0L0RR[2:0]=0b110 and disable LINPHY0 (LPCR[LPE]=0). This releases PT0 and PT1 to other associated functions and maintains TXD0 and RXD0 signals on PS1 and PS0, respectively, if no other function with higher priority takes precedence.

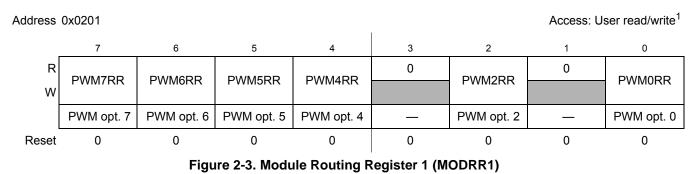

# 2.3.2.2 Module Routing Register 1 (MODRR1)

<sup>1</sup> Read: Anytime

Write: Once in normal, anytime in special mode

| Table 2-4. MODRR1 Routing Re | gister Field Descriptions |

|------------------------------|---------------------------|

|------------------------------|---------------------------|

| Field       | Description                                                                                      |  |  |  |  |  |

|-------------|--------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7<br>PWM7RR | Module Routing Register — PWM option 7 routing<br>1 PWM option 7 to PJ1<br>0 PWM option 7 to PP7 |  |  |  |  |  |

| 6<br>PWM6RR | Module Routing Register — PWM option 6 routing<br>1 PWM option 6 to PS1<br>0 PWM option 6 to PP6 |  |  |  |  |  |

| 5<br>PWM5RR | Module Routing Register — PWM option 5 routing<br>1 PWM option 5 to PJ0<br>0 PWM option 5 to PP5 |  |  |  |  |  |

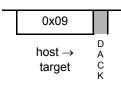

elapse between the consecutive ERASE\_FLASH commands then a timeout occurs, which forces a soft reset and initializes the sequence. The ERASE bit is cleared when the mass erase sequence has been completed. No ACK is driven.

During the mass erase operation, which takes many clock cycles, the command status is indicated by the ERASE bit in BDCCSR. Whilst a mass erase operation is ongoing, Always-available commands can be issued. This allows the status of the erase operation to be polled by reading BDCCSR to determine when the operation is finished.

The status of the flash array can be verified by subsequently reading the flash error flags to determine if the erase completed successfully.

ERASE\_FLASH can be aborted by a SYNC pulse forcing a soft reset.

# **NOTE: Device Bus Frequency Considerations**

The ERASE\_FLASH command requires the default device bus clock frequency after reset. Thus the bus clock frequency must not be changed following reset before issuing an ERASE\_FLASH command.

# 5.4.4.20 STEP1

Step1

Active Background

This command is used to step through application code. In active BDM this command executes the next CPU instruction in application code. If enabled an ACK is driven.

If a STEP1 command is issued and the CPU is not halted, the command is ignored.

Using STEP1 to step through a CPU WAI instruction is explained in Section 5.1.3.3.2, "Wait Mode.

# 5.4.5 BDC Access Of Internal Resources

Unsuccessful read accesses of internal resources return a value of 0xEE for each data byte. This enables a debugger to recognize a potential error, even if neither the ACK handshaking protocol nor a status command is currently being executed. The value of 0xEE is returned in the following cases.

- Illegal address access, whereby ILLACC is set

- Invalid READ\_SAME or DUMP\_MEM sequence

- Invalid READ\_Rn command (BDM inactive or CRN incorrect)

- Internal resource read with timeout, whereby NORESP is set

# Chapter 8 ECC Generation Module (SRAM\_ECCV2)

| Rev. No.<br>(Item No.) | Date      | Sections<br>Affected | Substantial Change(s)                                            |

|------------------------|-----------|----------------------|------------------------------------------------------------------|

| V01.00                 | 26-Jul11  | all                  | Initial version V1                                               |

| V02.00                 | 10-May-12 | all                  | Initial version V2, added support for max access width of 2 byte |

#### Table 8-1. Revision History Table

# 8.1 Introduction

The purpose of ECC logic is to detect and correct as much as possible memory data bit errors. These soft errors, mainly generated by alpha radiation, can occur randomly during operation. "Soft error" means that only the information inside the memory cell is corrupt; the memory cell itself is not damaged. A write access with correct data solves the issue. If the ECC algorithm is able to correct the data, then the system can use this corrected data without any issues. If the ECC algorithm is able to detect, but not correct the error, then the system is able to ignore the memory read data to avoid system malfunction.

The ECC value is calculated based on an aligned 2 byte memory data word. Depending on the device integration, the maximum supported access width can be 2 or 4 bytes. Please see the device overview section for the information about the maximum supported access width on the device.

In a system with a maximum access width of 2 bytes, a 2 byte access to a 2 byte aligned address is classed as an aligned access. If the system supports a 4-byte access width, then a 2-byte access to a 2 byte aligned address or a 4 byte access to a 4 byte aligned address are classed as aligned accesses. All other access types are classed as non-aligned accesses. A non-aligned write access requires a read-modify-write operation, for more details please see section The ECC algorithm is able to detect and correct single bit ECC errors. Double bit ECC errors will be detected but the system is not able to correct these errors. This kind of ECC code is called SECDED code. This ECC code requires 6 additional parity bits for each 2 byte data word.

# 8.1.1 Features

The SRAM\_ECC module provides the ECC logic for the system memory based on a SECDED algorithm. The SRAM\_ECC module includes the following features:

- SECDED ECC code

- Single bit error detection and correction per 2 byte data word

S12 Clock, Reset and Power Management Unit (S12CPMU\_UHV)

# 9.1.2 Modes of Operation

This subsection lists and briefly describes all operating modes supported by the S12CPMU\_UHV.

# 9.1.2.1 Run Mode

The voltage regulator is in Full Performance Mode (FPM).

## NOTE

The voltage regulator is active, providing the nominal supply voltages with full current sourcing capability (see also Appendix for VREG electrical parameters). The features ACLK clock source, Low Voltage Interrupt (LVI), Low Voltage Reset (LVR) and Power-On Reset (POR) are available.

The Phase Locked Loop (PLL) is on.

The Internal Reference Clock (IRC1M) is on.

The API is available.

- PLL Engaged Internal (PEI)

- This is the default mode after System Reset and Power-On Reset.

- The Bus Clock is based on the PLLCLK.

- After reset the PLL is configured for 50MHz VCOCLK operation.

- Post divider is 0x03, so PLLCLK is VCOCLK divided by 4, that is 12.5MHz and Bus Clock is 6.25MHz.

The PLL can be re-configured for other bus frequencies.

— The reference clock for the PLL (REFCLK) is based on internal reference clock IRC1M.

## • PLL Engaged External (PEE)

- The Bus Clock is based on the PLLCLK.

- This mode can be entered from default mode PEI by performing the following steps:

- Configure the PLL for desired bus frequency.

- Program the reference divider (REFDIV[3:0] bits) to divide down oscillator frequency if necessary.

- Enable the external oscillator (OSCE bit).

- Wait for oscillator to start up (UPOSC=1) and PLL to lock (LOCK=1).

#### • PLL Bypassed External (PBE)

- The Bus Clock is based on the Oscillator Clock (OSCCLK).

- The PLLCLK is always on to qualify the external oscillator clock. Therefore it is necessary to make sure a valid PLL configuration is used for the selected oscillator frequency.

- This mode can be entered from default mode PEI by performing the following steps:

- Make sure the PLL configuration is valid for the selected oscillator frequency.

| Address<br>Offset | Register<br>Name      |        | Bit 7    | 6       | 5           | 4       | 3       | 2       | 1            | Bit 0  |

|-------------------|-----------------------|--------|----------|---------|-------------|---------|---------|---------|--------------|--------|

| 0x000E            | RESERVED              | R      | 0        | 0       | 0           | 0       | 0       | 0       | 0            | 0      |

| OXOOOL            | CPMUTEST1             | W      |          |         |             |         |         |         |              |        |

| 0x000F            | CPMU                  | R      | 0        | 0       | 0           | 0       | 0       | 0       | 0            | 0      |

|                   | ARMCOP                | W      | Bit 7    | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2   | Bit 1        | Bit 0  |

| 0x0010            | CPMU<br>HTCTL         | R<br>W | 0        | 0       | VSEL        | 0       | HTE     | HTDS    | HTIE         | HTIF   |

| 0x0011            | CPMU<br>LVCTL         | R<br>W | 0        | 0       | 0           | 0       | 0       | LVDS    | LVIE         | LVIF   |

| 0x0012            | CPMU<br>APICTL        | R<br>W | APICLK   | 0       | 0           | APIES   | APIEA   | APIFE   | APIE         | APIF   |

| 0x0013            | CPMUACLKTR            | R<br>W | ACLKTR5  | ACLKTR4 | ACLKTR3     | ACLKTR2 | ACLKTR1 | ACLKTR0 | 0            | 0      |

| 0x0014            | CPMUAPIRH             | R<br>W | APIR15   | APIR14  | APIR13      | APIR12  | APIR11  | APIR10  | APIR9        | APIR8  |

| 0x0015            | CPMUAPIRL             | R<br>W | APIR7    | APIR6   | APIR5       | APIR4   | APIR3   | APIR2   | APIR1        | APIR0  |

| 0x0016            | RESERVED              | R      | 0        | 0       | 0           | 0       | 0       | 0       | 0            | 0      |

| 0,0010            |                       | W      |          |         |             |         |         |         |              |        |

| 0x0017            | CPMUHTTR              | R<br>W | HTOE     | 0       | 0           | 0       | HTTR3   | HTTR2   | HTTR1        | HTTR0  |

| 0x0018            | CPMU<br>IRCTRIMH      | R<br>W |          |         | FCTRIM[4:0] |         |         | 0       | IRCTRIM[9:8] |        |

| 0x0019            | CPMU<br>IRCTRIML      | R<br>W |          |         |             | IRCTRI  | M[7:0]  |         |              |        |

| 0x001A            | CPMUOSC               | R<br>W | OSCE     | 0       | Reserved    | 0       | 0       | 0       | 0            | 0      |

|                   |                       | R      | 0        | 0       | 0           | 0       | 0       | 0       | 0            |        |

| 0x001B            | CPMUPROT              | W      |          | 0       | 0           | 0       | 0       | 0       | 0            | PROT   |

| 0x001C            | RESERVED<br>CPMUTEST2 | R<br>W | 0        | 0       | 0           | 0       | 0       | 0       | 0            | 0      |

| 0x001D            | CPMU<br>VREGCTL       | R<br>W | VREG5VEN | 0       | 0           | 0       | 0       | 0       | EXTXON       | INTXON |

| 0x001E            | CPMUOSC2              | R      | 0        | 0       | 0           | 0       | 0       | 0       | OMRE         | OSCMOD |

|                   |                       | W      |          |         |             |         |         |         |              |        |

| 0x001F            | RESERVED              | R<br>W | 0        | 0       | 0           | 0       | 0       | 0       | 0            | 0      |

= Unimplemented or Reserved

Figure 9-3. CPMU Register Summary

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>RSTA | Restart Event (Restart from Top of Command Sequence List) — This bit indicates that a Restart Event is executed. The ADC loads the conversion command from top of the active Sequence Command List when no conversion or conversion sequence is ongoing. This bit is cleared when the first conversion command of the sequence from top of active Sequence Command List has been loaded into the ADCCMD register. This bit can only be set if bit ADC_EN is set. This bit is cleared if bit ADC_EN is clear. Data Bus Control: |

|           | This bit can be controlled via the data bus if access control is configured accordingly via ACC_CFG[1:0].<br>Writing a value of 1'b0 does not clear the flag.<br>Writing a one to this bit does not clear it but causes an overrun if the bit has already been set. See also<br>Section 10.6.3.2.6, "Conversion flow control in case of conversion sequence control bit overrun scenarios for<br>more details.                                                                                                                 |

|           | Internal Interface Control:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|           | This bit can be controlled via the internal interface Signal "Restart" if access control is configured accordingly via ACC_CFG[1:0]. After being set an additional request via internal interface Signal "Restart" causes an overrun. See conversion flow control in case of overrun situations for more details.                                                                                                                                                                                                              |

|           | General:<br>In conversion flow control mode "Trigger Mode" when bit RSTA gets set bit TRIG is set simultaneously if one of<br>the following has been executed:<br>- "End Of List" command type has been executed or is about to be executed                                                                                                                                                                                                                                                                                    |

|           | <ul> <li>Sequence Abort Event</li> <li>Continue with commands from active Sequence Command List.</li> <li>Restart from top of active Sequence Command List.</li> </ul>                                                                                                                                                                                                                                                                                                                                                         |

| 4<br>LDOK | Load OK for alternative Command Sequence List — This bit indicates if the preparation of the alternative<br>Sequence Command List is done and Command Sequence List must be swapped with the Restart Event. This<br>bit is cleared when bit RSTA is set (Restart Event executed) and the Command Sequence List got swapped.<br>This bit can only be set if bit ADC_EN is set.<br>This bit is cleared if bit ADC_EN is clear.<br>This bit is forced to zero if bit CSL_BMOD is clear.                                           |

|           | Data Bus Control:         This bit can be controlled via the data bus if access control is configured accordingly via ACC_CFG[1:0].         Writing a value of 1'b0 does not clear the flag.         To set bit LDOK the bits LDOK and RSTA must be written simultaneously.         After being set this bit can not be cleared by writing a value of 1'b1. See also Section 10.6.3.2.6, "Conversion flow control in case of conversion sequence control bit overrun scenarios for more details.                               |

|           | Internal Interface Control:<br>This bit can be controlled via the internal interface Signal "LoadOK" and "Restart" if access control is configured<br>accordingly via ACC_CFG[1:0]. With the assertion of Interface Signal "Restart" the interface Signal "LoadOK" is<br>evaluated and bit LDOK set accordingly (bit LDOK set if Interface Signal "LoadOK" asserted when Interface<br>Signal "Restart" asserts).<br>General:                                                                                                   |

|           | Only in "Restart Mode" if a Restart Event occurs without bit LDOK being set the error flag LDOK_EIF is set except<br>when the respective Restart Request occurred after or simultaneously with a Sequence Abort Request.<br>The LDOK_EIF error flag is also not set in "Restart Mode" if the first Restart Event occurs after:<br>- ADC got enabled<br>- Exit from Stop Mode<br>- ADC Soft-Reset                                                                                                                               |

|           | <ul><li>0 Load of alternative list done.</li><li>1 Load alternative list.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CH_SEL[5] | CH_SEL[4] | CH_SEL[3] | CH_SEL[2] | CH_SEL[1] | CH_SEL[0] | Analog Input Channel                                                                             |

|-----------|-----------|-----------|-----------|-----------|-----------|--------------------------------------------------------------------------------------------------|

| 0         | 0         | 0         | 0         | 0         | 0         | VRL_0/1 (V1, V2, see Table 10-2)<br>VRL_0 (V3, see Table 10-2)                                   |

| 0         | 0         | 0         | 0         | 0         | 1         | VRH_0/1 (V1, V2, see Table 10-2)<br>VRH_0/1/2 (V3, see Table 10-2)                               |

| 0         | 0         | 0         | 0         | 1         | 0         | (VRH_0/1 + VRL_0/1) / 2 (V1, V2, see Table 10-2)<br>(VRH_0/1/2 + VRL_0) / 2 (V3, see Table 10-2) |

| 0         | 0         | 0         | 0         | 1         | 1         | Reserved                                                                                         |

| 0         | 0         | 0         | 1         | 0         | 0         | Reserved                                                                                         |

| 0         | 0         | 0         | 1         | 0         | 1         | Reserved                                                                                         |

| 0         | 0         | 0         | 1         | 1         | 0         | Reserved                                                                                         |

| 0         | 0         | 0         | 1         | 1         | 1         | Reserved                                                                                         |

| 0         | 0         | 1         | 0         | 0         | 0         | Internal_0<br>(ADC temperature sense)                                                            |

| 0         | 0         | 1         | 0         | 0         | 1         | Internal_1                                                                                       |

| 0         | 0         | 1         | 0         | 1         | 0         | Internal_2                                                                                       |

| 0         | 0         | 1         | 0         | 1         | 1         | Internal_3                                                                                       |

| 0         | 0         | 1         | 1         | 0         | 0         | Internal_4                                                                                       |

| 0         | 0         | 1         | 1         | 0         | 1         | Internal_5                                                                                       |

| 0         | 0         | 1         | 1         | 1         | 0         | Internal_6                                                                                       |

| 0         | 0         | 1         | 1         | 1         | 1         | Internal_7                                                                                       |

| 0         | 1         | 0         | 0         | 0         | 0         | ANO                                                                                              |

| 0         | 1         | 0         | 0         | 0         | 1         | AN1                                                                                              |

| 0         | 1         | 0         | 0         | 1         | 0         | AN2                                                                                              |

| 0         | 1         | 0         | 0         | 1         | 1         | AN3                                                                                              |

| 0         | 1         | 0         | 1         | 0         | 0         | AN4                                                                                              |

| 0         | 1         | x         | x         | x         | x         | ANx                                                                                              |

| 1         | x         | x         | x         | x         | x         | Reserved                                                                                         |

Table 10-24. Analog Input Channel Select

## NOTE

ANx in Table 10-24 is the maximum number of implemented analog input channels on the device. Please refer to the device overview of the reference manual for details regarding number of analog input channels.

| Field                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>WUPIE <sup>1</sup> | Wake-Up Interrupt Enable0 No interrupt request is generated from this event.1 A wake-up event causes a Wake-Up interrupt request.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6<br>CSCIE              | <ul> <li>CAN Status Change Interrupt Enable</li> <li>0 No interrupt request is generated from this event.</li> <li>1 A CAN Status Change event causes an error interrupt request.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5-4<br>RSTATE[1:0<br>]  | <ul> <li>Receiver Status Change Enable — These RSTAT enable bits control the sensitivity level in which receiver state changes are causing CSCIF interrupts. Independent of the chosen sensitivity level the RSTAT flags continue to indicate the actual receiver state and are only updated if no CSCIF interrupt is pending.</li> <li>00 Do not generate any CSCIF interrupt caused by receiver state changes.</li> <li>01 Generate CSCIF interrupt only if the receiver enters or leaves "bus-off" state. Discard other receiver state changes for generating CSCIF interrupt.</li> <li>10 Generate CSCIF interrupt only if the receiver enters or leaves "RxErr" or "bus-off"<sup>2</sup> state. Discard other receiver state changes for generating CSCIF interrupt.</li> <li>11 Generate CSCIF interrupt on all state changes.</li> </ul>              |

| 3-2<br>TSTATE[1:0]      | <ul> <li>Transmitter Status Change Enable — These TSTAT enable bits control the sensitivity level in which transmitter state changes are causing CSCIF interrupts. Independent of the chosen sensitivity level, the TSTAT flags continue to indicate the actual transmitter state and are only updated if no CSCIF interrupt is pending.</li> <li>00 Do not generate any CSCIF interrupt caused by transmitter state changes.</li> <li>01 Generate CSCIF interrupt only if the transmitter enters or leaves "bus-off" state. Discard other transmitter state changes for generating CSCIF interrupt.</li> <li>10 Generate CSCIF interrupt only if the transmitter enters or leaves "TxErr" or "bus-off" state. Discard other transmitter state changes for generating CSCIF interrupt.</li> <li>11 Generate CSCIF interrupt on all state changes.</li> </ul> |

| 1<br>OVRIE              | Overrun Interrupt Enable         0       No interrupt request is generated from this event.         1       An overrun event causes an error interrupt request.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0<br>RXFIE              | <ul> <li>Receiver Full Interrupt Enable</li> <li>0 No interrupt request is generated from this event.</li> <li>1 A receive buffer full (successful message reception) event causes a receiver interrupt request.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

#### Table 13-12. CANRIER Register Field Descriptions

<sup>1</sup> WUPIE and WUPE (see Section 13.3.2.1, "MSCAN Control Register 0 (CANCTL0)") must both be enabled if the recovery mechanism from stop or wait is required.

<sup>2</sup> Bus-off state is only defined for transmitters by the CAN standard (see Bosch CAN 2.0A/B protocol specification). Because the only possible state change for the transmitter from bus-off to TxOK also forces the receiver to skip its current state to RxOK, the coding of the RXSTAT[1:0] flags define an additional bus-off state for the receiver (see Section 13.3.2.5, "MSCAN Receiver Flag Register (CANRFLG)").

# 13.3.2.7 MSCAN Transmitter Flag Register (CANTFLG)

The transmit buffer empty flags each have an associated interrupt enable bit in the CANTIER register.

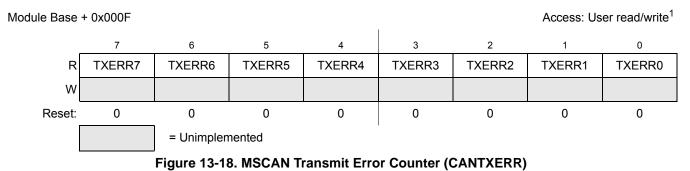

# 13.3.2.15 MSCAN Transmit Error Counter (CANTXERR)

This register reflects the status of the MSCAN transmit error counter.

Read: Only when in sleep mode (SLPRQ = 1 and SLPAK = 1) or initialization mode (INITRQ = 1 and INITAK = 1) Write: Unimplemented

#### NOTE

Reading this register when in any other mode other than sleep or initialization mode, may return an incorrect value. For MCUs with dual CPUs, this may result in a CPU fault condition.

## 13.3.2.16 MSCAN Identifier Acceptance Registers (CANIDAR0-7)

On reception, each message is written into the background receive buffer. The CPU is only signalled to read the message if it passes the criteria in the identifier acceptance and identifier mask registers (accepted); otherwise, the message is overwritten by the next message (dropped).

The acceptance registers of the MSCAN are applied on the IDR0–IDR3 registers (see Section 13.3.3.1, "Identifier Registers (IDR0–IDR3)") of incoming messages in a bit by bit manner (see Section 13.4.3, "Identifier Acceptance Filter").

For extended identifiers, all four acceptance and mask registers are applied. For standard identifiers, only the first two (CANIDAR0/1, CANIDMR0/1) are applied.

Module Base + 0x0010 to Module Base + 0x0013

Access: User read/write<sup>1</sup>

|        | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| R<br>W | AC7 | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

#### Figure 13-19. MSCAN Identifier Acceptance Registers (First Bank) — CANIDAR0–CANIDAR3

<sup>1</sup> Read: Anytime

Write: Anytime in initialization mode (INITRQ = 1 and INITAK = 1)

#### Pulse-Width Modulator (S12PWM8B8CV2)

In concatenated mode, writes to the 16-bit counter by using a 16-bit access or writes to either the low or high order byte of the counter will reset the 16-bit counter. Reads of the 16-bit counter must be made by 16-bit access to maintain data coherency.

Either left aligned or center aligned output mode can be used in concatenated mode and is controlled by the low order CAEx bit. The high order CAEx bit has no effect.

Table 17-13 is used to summarize which channels are used to set the various control bits when in 16-bit mode.

| CONxx | PWMEx | PPOLx | PCLKx | CAEx | PWMx<br>Output |

|-------|-------|-------|-------|------|----------------|

| CON67 | PWME7 | PPOL7 | PCLK7 | CAE7 | PWM7           |

| CON45 | PWME5 | PPOL5 | PCLK5 | CAE5 | PWM5           |

| CON23 | PWME3 | PPOL3 | PCLK3 | CAE3 | PWM3           |

| CON01 | PWME1 | PPOL1 | PCLK1 | CAE1 | PWM1           |

Table 17-13. 16-bit Concatenation Mode Summary

Note: Bits related to available channels have functional significance.

# 17.4.2.8 PWM Boundary Cases

Table 17-14 summarizes the boundary conditions for the PWM regardless of the output mode (left aligned or center aligned) and 8-bit (normal) or 16-bit (concatenation).

Table 17-14. PWM Boundary Cases

| PWMDTYx                     | PWMPERx                                    | PPOLx | PWMx Output |

|-----------------------------|--------------------------------------------|-------|-------------|

| \$00<br>(indicates no duty) | >\$00                                      | 1     | Always low  |

| \$00<br>(indicates no duty) | >\$00                                      | 0     | Always high |

| XX                          | \$00 <sup>1</sup><br>(indicates no period) | 1     | Always high |

| XX                          | \$00 <sup>1</sup><br>(indicates no period) | 0     | Always low  |

| >= PWMPERx                  | XX                                         | 1     | Always high |

| >= PWMPERx                  | XX                                         | 0     | Always low  |

Counter = \$00 and does not count.

# 17.5 Resets

The reset state of each individual bit is listed within the Section 17.3.2, "Register Descriptions" which details the registers and their bit-fields. All special functions or modes which are initialized during or just following reset are described within this section.

- The 8-bit up/down counter is configured as an up counter out of reset.

- All the channels are disabled and all the counters do not count.

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TDRE | <ul> <li>Transmit Data Register Empty Flag — TDRE is set when the transmit shift register receives a byte from the SCI data register. When TDRE is 1, the transmit data register (SCIDRH/L) is empty and can receive a new value to transmit.Clear TDRE by reading SCI status register 1 (SCISR1), with TDRE set and then writing to SCI data register low (SCIDRL).</li> <li>0 No byte transferred to transmit shift register</li> <li>1 Byte transferred to transmit shift register; transmit data register empty</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6<br>TC   | Transmit Complete Flag — TC is set low when there is a transmission in progress or when a preamble or break character is loaded. TC is set high when the TDRE flag is set and no data, preamble, or break character is being transmitted. When TC is set, the TXD pin becomes idle (logic 1). Clear TC by reading SCI status register 1 (SCISR1) with TC set and then writing to SCI data register low (SCIDRL). TC is cleared automatically when data, preamble, or break is queued and ready to be sent. TC is cleared in the event of a simultaneous set and clear of the TC flag (transmission not complete).<br>0 Transmission in progress<br>1 No transmission in progress                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5<br>RDRF | <ul> <li>Receive Data Register Full Flag — RDRF is set when the data in the receive shift register transfers to the SCI data register. Clear RDRF by reading SCI status register 1 (SCISR1) with RDRF set and then reading SCI data register low (SCIDRL).</li> <li>0 Data not available in SCI data register</li> <li>1 Received data available in SCI data register</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4<br>IDLE | <ul> <li>Idle Line Flag — IDLE is set when 10 consecutive logic 1s (if M = 0) or 11 consecutive logic 1s (if M = 1) appear on the receiver input. Once the IDLE flag is cleared, a valid frame must again set the RDRF flag before an idle condition can set the IDLE flag.Clear IDLE by reading SCI status register 1 (SCISR1) with IDLE set and then reading SCI data register low (SCIDRL).</li> <li>0 Receiver input is either active now or has never become active since the IDLE flag was last cleared 1 Receiver input has become idle</li> <li>Note: When the receiver wakeup bit (RWU) is set, an idle line condition does not set the IDLE flag.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3<br>OR   | <ul> <li>Overrun Flag — OR is set when software fails to read the SCI data register before the receive shift register receives the next frame. The OR bit is set immediately after the stop bit has been completely received for the second frame. The data in the shift register is lost, but the data already in the SCI data registers is not affected. Clear OR by reading SCI status register 1 (SCISR1) with OR set and then reading SCI data register low (SCIDRL).</li> <li>0 No overrun</li> <li>1 Overrun</li> <li>Note: OR flag may read back as set when RDRF flag is clear. This may happen if the following sequence of events occurs: <ol> <li>After the first frame is received, read status register SCISR1 (returns RDRF set and OR flag clear);</li> <li>Receive second frame without reading the first frame in the data register (the second frame is not received and OR flag is set);</li> <li>Read data register SCIDRL (returns RDRF clear and OR set).</li> </ol> </li> <li>Event 3 may be at exactly the same time as event 2 or any time after. When this happens, a dummy SCIDRL read following event 4 will be required to clear the OR flag if further frames are to be received.</li> </ul> |

| 2<br>NF   | <ul> <li>Noise Flag — NF is set when the SCI detects noise on the receiver input. NF bit is set during the same cycle as the RDRF flag but does not get set in the case of an overrun. Clear NF by reading SCI status register 1(SCISR1), and then reading SCI data register low (SCIDRL).</li> <li>0 No noise</li> <li>1 Noise</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

#### Table 18-11. SCISR1 Field Descriptions

| IIC       | <br> | <br>IBAL, TCF, IAAS | When either of IBAL, TCF or IAAS bits is set |

|-----------|------|---------------------|----------------------------------------------|

| Interrupt |      | bits in IBSR        | may cause an interrupt based on arbitration  |

|           |      | register            | lost, transfer complete or address detect    |

|           |      |                     | conditions                                   |

Internally there are three types of interrupts in IIC. The interrupt service routine can determine the interrupt type by reading the status register.

IIC Interrupt can be generated on

- 1. Arbitration lost condition (IBAL bit set)

- 2. Byte transfer condition (TCF bit set)

- 3. Address detect condition (IAAS bit set)

The IIC interrupt is enabled by the IBIE bit in the IIC control register. It must be cleared by writing 0 to the IBF bit in the interrupt service routine.

# 20.7 Application Information

# 20.7.1 IIC Programming Examples

# 20.7.1.1 Initialization Sequence

Reset will put the IIC bus control register to its default status. Before the interface can be used to transfer serial data, an initialization procedure must be carried out, as follows:

- 1. Update the frequency divider register (IBFD) and select the required division ratio to obtain SCL frequency from system clock.

- 2. Update the ADTYPE of IBCR2 to define the address length, 7 bits or 10 bits.

- 3. Update the IIC bus address register (IBAD) to define its slave address. If 10-bit address is applied IBCR2 should be updated to define the rest bits of address.

- 4. Set the IBEN bit of the IIC bus control register (IBCR) to enable the IIC interface system.

- 5. Modify the bits of the IIC bus control register (IBCR) to select master/slave mode, transmit/receive mode and interrupt enable or not.

- 6. If supported general call, the GCEN in IBCR2 should be asserted.

# 20.7.1.2 Generation of START

After completion of the initialization procedure, serial data can be transmitted by selecting the 'master transmitter' mode. If the device is connected to a multi-master bus system, the state of the IIC bus busy bit (IBB) must be tested to check whether the serial bus is free.

If the bus is free (IBB=0), the start condition and the first byte (the slave address) can be sent. The data written to the data register comprises the slave calling address and the LSB set to indicate the direction of transfer required from the slave.

The bus free time (i.e., the time between a STOP condition and the following START condition) is built into the hardware that generates the START cycle. Depending on the relative frequencies of the system

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                   |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>SFDIE | <ul> <li>Single Bit Fault Detect Interrupt Enable — The SFDIE bit controls interrupt generation when a single bit fault is detected during a Flash block read operation.</li> <li>0 SFDIF interrupt disabled whenever the SFDIF flag is set (see Section 22.3.2.8)</li> <li>1 An interrupt will be requested whenever the SFDIF flag is set (see Section 22.3.2.8)</li> </ul> |

#### Table 22-15. FERCNFG Field Descriptions

# 22.3.2.7 Flash Status Register (FSTAT)

The FSTAT register reports the operational status of the Flash module.

Offset Module Base + 0x0006

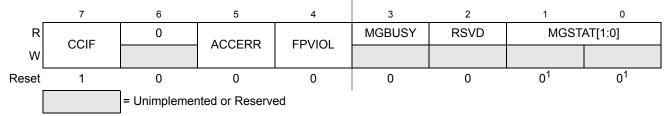

#### Figure 22-11. Flash Status Register (FSTAT)

<sup>1</sup> Reset value can deviate from the value shown if a double bit fault is detected during the reset sequence (see Section 22.6).

CCIF, ACCERR, and FPVIOL bits are readable and writable, MGBUSY and MGSTAT bits are readable but not writable, while remaining bits read 0 and are not writable.

Table 22-16. FSTAT Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CCIF   | <ul> <li>Command Complete Interrupt Flag — The CCIF flag indicates that a Flash command has completed. The CCIF flag is cleared by writing a 1 to CCIF to launch a command and CCIF will stay low until command completion or command violation.</li> <li>0 Flash command in progress</li> <li>1 Flash command has completed</li> </ul>                                                                                                                                                 |

| 5<br>ACCERR | <b>Flash Access Error Flag</b> — The ACCERR bit indicates an illegal access has occurred to the Flash memory caused by either a violation of the command write sequence (see Section 22.4.5.2) or issuing an illegal Flash command. While ACCERR is set, the CCIF flag cannot be cleared to launch a command. The ACCERR bit is cleared by writing a 1 to ACCERR. Writing a 0 to the ACCERR bit has no effect on ACCERR. 0 No access error detected 1 Access error detected             |

| 4<br>FPVIOL | <b>Flash Protection Violation Flag</b> —The FPVIOL bit indicates an attempt was made to program or erase an address in a protected area of P-Flash or EEPROM memory during a command write sequence. The FPVIOL bit is cleared by writing a 1 to FPVIOL. Writing a 0 to the FPVIOL bit has no effect on FPVIOL. While FPVIOL is set, it is not possible to launch a command or start a command write sequence.<br>0 No protection violation detected<br>1 Protection violation detected |

| 3<br>MGBUSY | <ul> <li>Memory Controller Busy Flag — The MGBUSY flag reflects the active state of the Memory Controller.</li> <li>0 Memory Controller is idle</li> <li>1 Memory Controller is busy executing a Flash command (CCIF = 0)</li> </ul>                                                                                                                                                                                                                                                    |

| Register | FCCOB Parameters                                            |  |  |

|----------|-------------------------------------------------------------|--|--|

| FCCOB0   | 0x11 Global address [23:16] to<br>identify the EEPROM block |  |  |

| FCCOB1   | Global address [15:0] of word to be programmed              |  |  |

| FCCOB2   | Word 0 program value                                        |  |  |

| FCCOB3   | Word 1 program value, if desired                            |  |  |

| FCCOB4   | Word 2 program value, if desired                            |  |  |

| FCCOB5   | Word 3 program value, if desired                            |  |  |

Table 22-63. Program EEPROM Command FCCOB Requirements

Upon clearing CCIF to launch the Program EEPROM command, the user-supplied words will be transferred to the Memory Controller and be programmed if the area is unprotected. The CCOBIX index value at Program EEPROM command launch determines how many words will be programmed in the EEPROM block. The CCIF flag is set when the operation has completed.

| Register | Error Bit         | Error Condition                                                                     |  |  |

|----------|-------------------|-------------------------------------------------------------------------------------|--|--|

|          |                   | Set if CCOBIX[2:0] < 010 at command launch                                          |  |  |

|          |                   | Set if CCOBIX[2:0] > 101 at command launch                                          |  |  |

|          | ACCERR            | Set if command not available in current mode (see Table 22-28)                      |  |  |

|          | ACCERR            | Set if an invalid global address [23:0] is supplied                                 |  |  |

| FSTAT    |                   | Set if a misaligned word address is supplied (global address [0] != 0)              |  |  |

|          |                   | Set if the requested group of words breaches the end of the EEPROM block            |  |  |

|          | FPVIOL<br>MGSTAT1 | Set if the selected area of the EEPROM memory is protected                          |  |  |

|          |                   | Set if any errors have been encountered during the verify operation                 |  |  |

|          | MGSTAT0           | Set if any non-correctable errors have been encountered during the verify operation |  |  |

## 22.4.7.16 Erase EEPROM Sector Command

The Erase EEPROM Sector operation will erase all addresses in a sector of the EEPROM block.

Table 22-65. Erase EEPROM Sector Command FCCOB Requirements

| Register | FCCOB                                                                                                          | Parameters                                         |  |

|----------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|

| FCCOB0   | 0x12                                                                                                           | Global address [23:16] to identify<br>EEPROM block |  |

| FCCOB1   | Global address [15:0] anywhere within the sector to be erased.<br>See Section 22.1.2.2 for EEPROM sector size. |                                                    |  |

| Protection Update<br>Selection code [1:0] | Protection register selection                                                                                                        |  |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|

| bit 1                                     | Update EEPROM protection<br>0 - keep unchanged (do not update)<br>1 - update EEPROM protection with new DFPROT value loaded on FCCOB |  |

| Table 22-68 | . Protection | Override | selection | description |

|-------------|--------------|----------|-----------|-------------|

|-------------|--------------|----------|-----------|-------------|

If the comparison key successfully matches the key programmed in the Flash Configuration Field the Protection Override command will preserve the current values of registers FPROT and DFPROT stored in an internal area and will override these registers as selected by the Protection Update Selection field with the value(s) loaded on FCCOB parameters. The new values loaded into FPROT and/or DFPROT can reconfigure protection without any restriction (by increasing, decreasing or disabling protection limits). If the command executes successfully the FPSTAT FPOVRD bit will set.

If the comparison key does not match the key programmed in the Flash Configuration Field, or if the key loaded on FCCOB is 16'hFFFF, the value of registers FPROT and DFPROT will be restored to their original contents before executing the Protection Override command and the FPSTAT FPOVRD bit will be cleared. If the contents of the Protection Override Comparison Key in the Flash Configuration Field is left in the erased state (i.e. 16'hFFFF) the Protection Override feature is permanently disabled. If the command execution is flagged as an error (ACCERR being set for incorrect command launch) the values of FPROT and DFPROT will not be modified.

The Protection Override command can be called multiple times and every time it is launched it will preserve the current values of registers FPROT and DFPROT in a single-entry buffer to be restored later; when the Protection Override command is launched to restore FPROT and DFPROT these registers will assume the values they had before executing the Protection Override command on the last time. If contents of FPROT and/or DFPROT registers were modified by direct register writes while protection is overridden these modifications will be lost. Running Protection Override command to restore the contents of registers FPROT and DFPROT will not force them to the reset values.

| Register | Error Bit | Error Condition                                                                                                                                                                                                                               |  |  |

|----------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| FSTAT    | ACCERR    | Set if CCOBIX[2:0] != (001, 010 or 011) at command launch.                                                                                                                                                                                    |  |  |

|          |           | Set if command not available in current mode (see Table 22-28).                                                                                                                                                                               |  |  |

|          |           | Set if protection is supposed to be restored (if key does not match or is invalid) and Protection Override command was not run previously (bit FPSTAT FPOVRD is 0) so there are no previous valid values of FPROT and DFPROT to be re-loaded. |  |  |

|          |           | Set if Protection Update Selection[1:0] = 00 (in case of CCOBIX[2:0] = 010 or 011)                                                                                                                                                            |  |  |

|          |           | Set if Protection Update Selection[1:0] = 00, CCOBIX[2:0] = 001 and a valid comparison key is loaded as a command parameter.                                                                                                                  |  |  |

|          | FPVIOL    | None                                                                                                                                                                                                                                          |  |  |

|          | MGSTAT1   | None                                                                                                                                                                                                                                          |  |  |

|          | MGSTAT0   | None                                                                                                                                                                                                                                          |  |  |

Table 22-69. Protection Override Command Error Handling

# **Appendix B CPMU Electrical Specifications (VREG, OSC, IRC, PLL)**

#### **VREG Electrical Specifications B.1**

# Table B-1. Voltage Regulator Electrical Characteristics

|       | $40^{\circ}C \le T_{J} \le 175^{\circ}C$ unless noted otherwise, $V_{DDA}$ and $V_{DDX}$ must be shorted on the application board.                                                                                                                                                                      |                  |                                     |                                  |                                      |      |  |  |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------|----------------------------------|--------------------------------------|------|--|--|--|

| Num   | Characteristic                                                                                                                                                                                                                                                                                          | Symbol           | Min                                 | Typical                          | Max                                  | Unit |  |  |  |

| 1     | Input Voltages                                                                                                                                                                                                                                                                                          | V <sub>SUP</sub> | 3.5                                 |                                  | 40                                   | V    |  |  |  |

| ZVL(S | 3)32/16/8 only                                                                                                                                                                                                                                                                                          |                  |                                     |                                  |                                      | -    |  |  |  |

| 2a    | Output Voltage $V_{DDX}$ , with external PNP<br>Full Performance Mode $V_{SUP} >=6V^1$<br>Full Performance Mode $5.5V \le V_{SUP} \le 6V$<br>Full Performance Mode $3.5V \le V_{SUP} \le 5.5V$<br>Reduced Performance Mode (stopmode)<br>$V_{SUP} > =3.5V$                                              | V <sub>DDX</sub> | 4.85<br>4.50<br>3.13<br>2.5         | 5.0<br>5.0<br>-<br>5.0           | 5.15<br>5.25<br>5.25<br>5.75         | V    |  |  |  |

| 2b    | Output Voltage $V_{DDX}$ , without external PNP<br>Full Performance Mode $V_{SUP} >=6V^1$<br>Full Performance Mode 5.5V <= $V_{SUP} <=6V$<br>Full Performance Mode 3.5V <= $V_{SUP} <=5.5V$<br>Reduced Performance Mode (stopmode)<br>$V_{SUP} > =3.5V$                                                 | V <sub>DDX</sub> | 4.80<br>4.50<br>3.13<br>2.5         | 4.95<br>4.95<br>-<br>5.0         | 5.10<br>5.20<br>5.20<br>5.75         | V    |  |  |  |

| 3     | Load Current V <sub>DDX</sub> <sup>2,3</sup> without external PNP<br>Full Performance Mode V <sub>SUP</sub> > 6V<br>Full Performance Mode 3.5V <= V <sub>SUP</sub> <=6V<br>Reduced Performance Mode (stopmode)                                                                                          | I <sub>DDX</sub> | 0<br>0<br>0                         | -<br>-<br>-                      | 70<br>25<br>5                        | mA   |  |  |  |

| VDDX  | =5V, VREG5VEN = 1'b1, ZVL(A)128/96/64 only                                                                                                                                                                                                                                                              |                  |                                     |                                  |                                      |      |  |  |  |

| 4a    | Output Voltage $V_{DDX}$ , with external PNP<br>Full Performance Mode $V_{SUP} >=6V^1$<br>Full Performance Mode $V_{SUP} >=6V^4$<br>Full Performance Mode $5.5V \le V_{SUP} \le 6V$<br>Full Performance Mode $3.5V \le V_{SUP} \le 5.5V$<br>Reduced Performance Mode (stopmode)<br>$V_{SUP} > =3.5V$    | V <sub>DDX</sub> | 4.85<br>4.90<br>4.50<br>3.13<br>2.2 | 5.0<br>5.0<br>5.0<br>-<br>5.0    | 5.15<br>5.10<br>5.25<br>5.25<br>5.75 | V    |  |  |  |