Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | ARM® Cortex®-M4                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB          |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 37                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 16K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 11x12b; D/A 1x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-LQFP                                                               |

| Supplier Device Package    | 48-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f302c8t7 |

| 9 | Revi | sion his         | story                                       |

|---|------|------------------|---------------------------------------------|

| 8 | Orde | ering inf        | ormation                                    |

|   |      | 7.5.2            | Selecting the product temperature range     |

|   |      | 7.5.1            | Reference document                          |

|   | 7.5  | Therma           | al characteristics 132                      |

|   | 7.4  |                  | PN32 package information                    |

|   | 7.3  |                  | 8 package information                       |

|   | 7.2  |                  | 4 package information                       |

|   | 7.1  |                  | P49 package information                     |

| 7 |      | •                | ormation                                    |

|   |      | 0.0.20           | VBAI mornioring characteristics             |

|   |      | 6.3.23           | V <sub>BAT</sub> monitoring characteristics |

|   |      | 6.3.22           | Operational amplifier characteristics       |

|   |      | 6.3.20<br>6.3.21 | Comparator characteristics                  |

|   |      | 6.3.19           | DAC electrical specifications               |

|   |      | 6.3.18           | ADC characteristics                         |

|   |      | 6.3.17           | Communications interfaces                   |

|   |      | 6.3.16           | Timer characteristics                       |

|   |      | 6.3.15           | NRST pin characteristics                    |

|   |      | 6.3.14           | I/O port characteristics                    |

|   |      | 6.3.13           | I/O current injection characteristics       |

|   |      | 6.3.12           | Electrical sensitivity characteristics      |

|   |      | 6.3.11           | EMC characteristics                         |

|   |      | 6.3.10           | Memory characteristics                      |

|   |      | 6.3.9            | PLL characteristics81                       |

|   |      | 6.3.8            | Internal clock source characteristics       |

|   |      | 6.3.7            | External clock source characteristics       |

# List of figures

| Figure 1.  | DS9896 block diagram                                                             | 12  |

|------------|----------------------------------------------------------------------------------|-----|

| Figure 2.  | Clock tree                                                                       |     |

| Figure 3.  | Infrared transmitter                                                             | 30  |

| Figure 4.  | STM32F302x6/8 UFQFN32 pinout                                                     | 32  |

| Figure 5.  | STM32F302x6/8 LQFP48 pinout                                                      | 32  |

| Figure 6.  | STM32F302x6/8 LQFP64 pinout                                                      | 33  |

| Figure 7.  | STM32F302x6/8 WLCSP49 ballout                                                    | 34  |

| Figure 8.  | STM32F302x6/8 memory mapping                                                     | 49  |

| Figure 9.  | Pin loading conditions                                                           |     |

| Figure 10. | Pin input voltage                                                                |     |

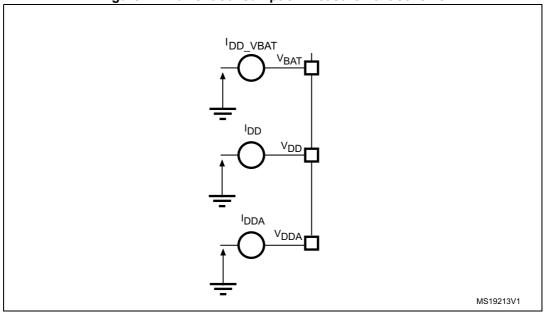

| Figure 11. | Power supply scheme                                                              |     |

| Figure 12. | Current consumption measurement scheme                                           |     |

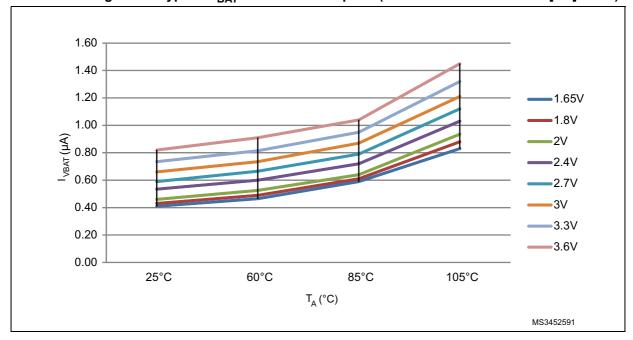

| Figure 13. | Typical V <sub>BAT</sub> current consumption (LSE and RTC ON/LSEDRV[1:0] = '00') |     |

| Figure 14. | High-speed external clock source AC timing diagram                               |     |

| Figure 15. | Low-speed external clock source AC timing diagram                                |     |

| Figure 16. | Typical application with an 8 MHz crystal                                        |     |

| Figure 17. | Typical application with a 32.768 kHz crystal                                    |     |

| Figure 18. | HSI oscillator accuracy characterization results for soldered parts              |     |

| Figure 19. | TC and TTa I/O input characteristics - CMOS port                                 |     |

| Figure 20. | TC and TTa I/O input characteristics - TTL port                                  |     |

| Figure 21. | Five volt tolerant (FT and FTf) I/O input characteristics - CMOS port            |     |

| Figure 22. | Five volt tolerant (FT and FTf) I/O input characteristics - TTL port             |     |

| Figure 23. | I/O AC characteristics definition                                                |     |

| Figure 24. | Recommended NRST pin protection                                                  |     |

| Figure 25. | SPI timing diagram - slave mode and CPHA = 0                                     |     |

| Figure 26. | SPI timing diagram - slave mode and CPHA = 1 <sup>(1)</sup>                      |     |

| Figure 27. | SPI timing diagram - master mode <sup>(1)</sup>                                  | 97  |

| Figure 28. | I <sup>2</sup> S slave timing diagram (Philips protocol) <sup>(1)</sup>          | 99  |

| Figure 29. | I <sup>2</sup> S master timing diagram (Philips protocol) <sup>(1)</sup>         | 99  |

| Figure 30. | USB timings: definition of data signal rise and fall time                        |     |

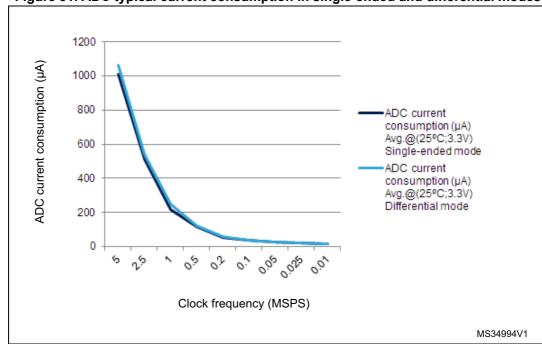

| Figure 31. | ADC typical current consumption in single-ended and differential modes           |     |

| Figure 32. | ADC accuracy characteristics                                                     |     |

| Figure 33. | Typical connection diagram using the ADC                                         |     |

| Figure 34. | 12-bit buffered /non-buffered DAC                                                |     |

| Figure 35. | Maximum V <sub>REFINT</sub> scaler startup time from power down                  | 113 |

| Figure 36. | OPAMP Voltage Noise versus Frequency                                             |     |

| Figure 37. | WLCSP49 - 49-pin, 3.417 x 3.151 mm, 0.4 mm pitch wafer level chip scale          |     |

| Ü          | package outline                                                                  | 119 |

| Figure 38. | WLCSP49 - 49-pin, 3.417 x 3.151 mm, 0.4 mm pitch wafer level chip scale          |     |

| Ü          | package recommended footprint                                                    | 120 |

| Figure 39. | WLCSP49 marking example (package top view)                                       |     |

| Figure 40. | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline                |     |

| Figure 41. | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package                        |     |

| <b>J</b>   | recommended footprint                                                            | 123 |

| Figure 42. | LQFP64 marking example (package top view)                                        | 124 |

| Figure 43. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline                  | 125 |

| Figure 44. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package                          |     |

| J          | recommended footprint                                                            | 127 |

## 3.4 Cyclic redundancy check calculation unit (CRC)

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code using a configurable generator polynomial value and size.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at linktime and stored at a given memory location.

## 3.5 Power management

## 3.5.1 Power supply schemes

- $V_{SS}$ ,  $V_{DD}$  = 2.0 to 3.6 V: external power supply for I/Os and the internal regulator. It is provided externally through  $V_{DD}$  pins.

- $V_{SSA}$ ,  $V_{DDA}$  = 2.0 to 3.6 V: external analog power supply for ADC, DAC, comparators, operational amplifier, reset blocks, RCs and PLL. The minimum voltage to be applied to  $V_{DDA}$  differs from one analog peripheral to another. *Table 2* provides the summary of the  $V_{DDA}$  ranges for analog peripherals. The  $V_{DDA}$  voltage level must always be greater than or equal to the  $V_{DD}$  voltage level and must be provided first.

| Analog peripheral | Minimum V <sub>DDA</sub> supply | Maximum V <sub>DDA</sub> supply |

|-------------------|---------------------------------|---------------------------------|

| ADC/COMP          | 2.0 V                           | 3.6 V                           |

| DAC/OPAMP         | 2.4 V                           | 3.6 V                           |

Table 2. External analog supply values for analog peripherals

V<sub>BAT</sub> = 1.65 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

#### 3.5.2 Power supply supervisor

The device has an integrated power-on reset (POR) and power-down reset (PDR) circuits. They are always active, and ensure proper operation above a threshold of 2 V. The device remains in reset mode when the monitored supply voltage is below a specified threshold, VPOR/PDR, without the need for an external reset circuit.

- The POR monitors only the V<sub>DD</sub> supply voltage. During the startup phase it is required that V<sub>DDA</sub> should arrive first and be greater than or equal to V<sub>DD</sub>.

- The PDR monitors both the V<sub>DD</sub> and V<sub>DDA</sub> supply voltages, however the V<sub>DDA</sub> power supply supervisor can be disabled (by programming a dedicated Option bit) to reduce the power consumption if the application design ensures that V<sub>DDA</sub> is higher than or equal to V<sub>DD</sub>.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}$  power supply and compares it to the VPVD threshold. An interrupt can be generated when  $V_{DD}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

Table 3. STM32F302x6/8 peripheral interconnect matrix

| Interconnect source                             | Interconnect destination | Interconnect action                                            |

|-------------------------------------------------|--------------------------|----------------------------------------------------------------|

|                                                 | TIMx                     | Timers synchronization or chaining                             |

| TIMx                                            | ADC1<br>DAC1             | Conversion triggers                                            |

|                                                 | DMA                      | Memory to memory transfer trigger                              |

|                                                 | Compx                    | Comparator output blanking                                     |

| COMPx                                           | TIMx                     | Timer input: OCREF_CLR input, input capture                    |

| ADC1                                            | TIM1                     | Timer triggered by analog watchdog                             |

| GPIO<br>RTCCLK<br>HSE/32<br>MC0                 | TIM16                    | Clock source used as input channel for HSI and LSI calibration |

| CSS<br>CPU (hard fault)<br>COMPx<br>PVD<br>GPIO | TIM1<br>TIM15, 16, 17    | Timer break                                                    |

|                                                 | TIMx                     | External trigger, timer break                                  |

| GPIO                                            | ADC1<br>DAC1             | Conversion external trigger                                    |

| DAC1                                            | COMPx                    | Comparator inverting input                                     |

Note: For more details about the interconnect actions, please refer to the corresponding sections in the STM32F302xx and STM32F302x6/8 reference manual RM0365.

|        | Table 12. STM32F302x6/8 pin definitions |        |        |                                             |          |               |       |                                                |                                      |  |

|--------|-----------------------------------------|--------|--------|---------------------------------------------|----------|---------------|-------|------------------------------------------------|--------------------------------------|--|

|        | Pin Nu                                  | umber  | •      |                                             |          |               |       |                                                |                                      |  |

| UQFN32 | WLCSP49                                 | LQFP48 | LQFP64 | Pin name<br>(function after reset)          | Pin type | I/O structure | Notes | Alternate<br>functions                         | Additional<br>functions              |  |

| -      | B6                                      | 1      | 1      | VBAT                                        | 8        | -             | -     | Backup po                                      | wer supply                           |  |

| -      | D5                                      | 2      | 2      | PC13 <sup>(1)</sup> TAMPER1<br>WKUP2 (PC13) | I/O      | TC            | (1)   | TIM1_CH1N                                      | WKUP2, RTC_TAMP1,<br>RTC_TS, RTC_OUT |  |

| -      | C7                                      | 3      | 3      | PC14 <sup>(1)</sup> OSC32_IN<br>(PC14)      | I/O      | TC            | (1)   | -                                              | OSC32_IN                             |  |

| -      | C6                                      | 4      | 4      | PC15 <sup>(1)</sup> OSC32_OUT<br>(PC14)     | I/O      | TC            | (1)   | -                                              | OSC32_OUT                            |  |

| 2      | D7                                      | 5      | 5      | PF0 OSC_IN (PF0)                            | I/O      | FTf           | -     | I2C2_SDA, SPI2_NSS/I2S2_WS,<br>TIM1_CH3N       | OSC_IN                               |  |

| 3      | D6                                      | 6      | 6      | PF1 OSC_OUT (PF1)                           | Ο        | FTf           | -     | I2C2_SCL, SPI2_SCK/I2S2_CK                     | OSC_OUT                              |  |

| 4      | E7                                      | 7      | 7      | NRST                                        | I/O      | RST           | -     | Device reset input/interna                     | I reset output (active low)          |  |

| -      | -                                       | -      | 8      | PC0                                         | I/O      | TTa           | -     | EVENTOUT, TIM1_CH1                             | ADC1_IN6                             |  |

| -      | -                                       | -      | 9      | PC1                                         | I/O      | TTa           | -     | EVENTOUT, TIM1_CH2                             | ADC1_IN7                             |  |

| -      | -                                       | -      | 10     | PC2                                         | I/O      | TTa           | -     | EVENTOUT, TIM1_CH3                             | ADC1_IN8                             |  |

| -      | -                                       | ı      | 11     | PC3                                         | I/O      | TTa           | -     | EVENTOUT, TIM1_CH4,<br>TIM1_BKIN2 ADC1_IN9     |                                      |  |

| 6      | E6                                      | 8      | 12     | VSSA/VREF-                                  | S        | -             | -     | Analog ground/Negat                            | ive reference voltage                |  |

| 5      | A6                                      | 9      | 13     | VDDA/VREF+                                  | S        | -             | -     | Analog power supply/Positive reference voltage |                                      |  |

DocID025147 Rev 6

|        | Pin Nu  | ımber  | •      |                                    |          |               |                                                                                          |                                                                                              |                         |

|--------|---------|--------|--------|------------------------------------|----------|---------------|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------|

| UQFN32 | WLCSP49 | LQFP48 | LQFP64 | Pin name<br>(function after reset) | Pin type | I/O structure |                                                                                          |                                                                                              | Additional<br>functions |

| -      | ,       | -      | 51     | PC10                               | I/O      | FT            | -                                                                                        | EVENTOUT, SPI3_SCK/I2S3_CK,<br>USART3_TX                                                     | -                       |

| -      | 1       | -      | 52     | PC11                               | I/O      | FT            | EVENTOUT, FT - SPI3_MISO/I2S3ext_SD, USART3_RX                                           |                                                                                              | -                       |

| -      | 1       | -      | 53     | PC12                               | I/O      | FT            | FT - EVENTOUT, SPI3_MOSI/I2S3_SD, USART3_CK                                              |                                                                                              | -                       |

| -      | -       | -      | 54     | PD2                                | I/O      | FT            | -                                                                                        | EVENTOUT                                                                                     | -                       |

| 26     | A3      | 39     | 55     | PB3                                | I/O      | FT            | -                                                                                        | JTDO-TRACESWO, TIM2_CH2,<br>TSC_G5_IO1, SPI3_SCK/I2S3_CK,<br>USART2_TX, EVENTOUT             | -                       |

| 27     | A4      | 40     | 56     | PB4                                | I/O      | FT            | -                                                                                        | JTRST, TIM16_CH1, TSC_G5_IO2,<br>SPI3_MISO/I2S3ext_SD,<br>USART2_RX, TIM17_BKIN,<br>EVENTOUT | -                       |

| 28     | B4      | 41     | 57     | PB5                                | I/O      | FT            | TIM16_BKIN, I2C1_SMBAI, FT - SPI3_MOSI/I2S3_SD, USART2_CK, I2C3_SDA, TIM17_CH1, EVENTOUT |                                                                                              | -                       |

| 29     | C4      | 42     | 58     | PB6                                | I/O      | FTf           | FTf - IZC1_SCL, USART1_TX, EVENTOUT                                                      |                                                                                              | -                       |

| 30     | D4      | 43     | 59     | PB7                                | I/O      | FTf           | FTf - I2C1_SDA, USART1_RX, EVENTOUT                                                      |                                                                                              | -                       |

Table 12. STM32F302x6/8 pin definitions (continued)

## 6.1.7 Current consumption measurement

Figure 12. Current consumption measurement scheme

# 6.3 Operating conditions

## 6.3.1 General operating conditions

Table 22. General operating conditions

| Symbol             | Parameter                                                         | Conditions                              | Min  | Max                   | Unit |  |  |  |

|--------------------|-------------------------------------------------------------------|-----------------------------------------|------|-----------------------|------|--|--|--|

| f <sub>HCLK</sub>  | Internal AHB clock frequency                                      | -                                       | 0    | 72                    |      |  |  |  |

| f <sub>PCLK1</sub> | Internal APB1 clock frequency                                     | -                                       | 0    | 36                    | MHz  |  |  |  |

| f <sub>PCLK2</sub> | Internal APB2 clock frequency                                     | -                                       | 0    | 72                    |      |  |  |  |

| V <sub>DD</sub>    | Standard operating voltage                                        | -                                       | 2    | 3.6                   | V    |  |  |  |

| V                  | Analog operating voltage (OPAMP and DAC not used)                 | Must have a potential                   | 2    | 3.6                   | V    |  |  |  |

| V <sub>DDA</sub>   | Analog operating voltage (OPAMP and DAC used)                     | equal to or higher than V <sub>DD</sub> | 2.4  | 3.6                   | V    |  |  |  |

| V <sub>BAT</sub>   | Backup operating voltage                                          | -                                       | 1.65 | 3.6                   | V    |  |  |  |

|                    |                                                                   | TC I/O                                  | -0.3 | V <sub>DD</sub> +0.3  |      |  |  |  |

|                    | I/O input voltage                                                 | TT I/O <sup>(1)</sup>                   | -0.3 | 3.6                   |      |  |  |  |

| V <sub>IN</sub>    |                                                                   | TTa I/O pins                            | -0.3 | V <sub>DDA</sub> +0.3 | V    |  |  |  |

|                    |                                                                   | FT and FTf I/O <sup>(1)</sup>           | -0.3 | 5.5                   |      |  |  |  |

|                    |                                                                   | воото                                   |      | 5.5                   |      |  |  |  |

|                    |                                                                   | LQFP64                                  |      | 444                   |      |  |  |  |

| D D                | Power dissipation at                                              | LQFP48                                  | -    | 364                   | \A/  |  |  |  |

| P <sub>D</sub>     | $T_A$ = 85 °C for suffix 6 or $T_A$ = 105 °C for suffix $7^{(2)}$ | WLCSP49                                 | -    | 408                   | mW   |  |  |  |

|                    |                                                                   | UFQFPN32                                | -    | 540                   |      |  |  |  |

|                    | Ambient temperature for 6                                         | Maximum power dissipation               | -40  | 85                    | °C   |  |  |  |

| т.                 | suffix version                                                    | Low power dissipation <sup>(3)</sup>    | -40  | 105                   | -    |  |  |  |

| ТА                 | Ambient temperature for 7 suffix version                          | Maximum power dissipation               | -40  | 105                   | °C   |  |  |  |

|                    | Suilla VEISIOII                                                   | Low power dissipation <sup>(3)</sup>    | -40  | 125                   |      |  |  |  |

| T.                 | lunction temperature range                                        | 6 suffix version                        | -40  | 105                   | °C   |  |  |  |

| TJ                 | Junction temperature range                                        | 7 suffix version                        | -40  | 125                   |      |  |  |  |

<sup>1.</sup> To sustain a voltage higher than  $V_{DD}$ +0.3 V, the internal pull-up/pull-down resistors must be disabled.

If T<sub>A</sub> is lower, higher P<sub>D</sub> values are allowed as long as T<sub>J</sub> does not exceed T<sub>Jmax</sub>. See *Table 82: Package thermal characteristics*.

<sup>3.</sup> In low power dissipation state,  $T_A$  can be extended to this range as long as  $T_J$  does not exceed  $T_{Jmax}$ . See *Table 82: Package thermal characteristics*

Table 29. Typical and maximum current consumption from the  $V_{\text{DDA}}$  supply

|                  |                      |                |                   | V <sub>DDA</sub> = 2.4 V |                                     |       |                    |     | V <sub>DDA</sub> = 3.6 V |        |                    |      |

|------------------|----------------------|----------------|-------------------|--------------------------|-------------------------------------|-------|--------------------|-----|--------------------------|--------|--------------------|------|

| Symbol           | Parameter            | Conditions (1) | f <sub>HCLK</sub> | f <sub>HCLK</sub>        | Max @ T <sub>A</sub> <sup>(2)</sup> |       |                    | Тур | М                        | ax @ T | A <sup>(2)</sup>   | Unit |

|                  |                      |                |                   | Тур                      | 25 °C                               | 85 °C | 105 °C             | тур | 25 °C                    | 85 °C  | 105 °C             |      |

|                  |                      |                | 72 MHz            | 231                      | 254 <sup>(3)</sup>                  | 266   | 271 <sup>(3)</sup> | 251 | 274 <sup>(3)</sup>       | 294    | 300 <sup>(3)</sup> |      |

|                  |                      |                | 64 MHz            | 203                      | 226                                 | 239   | 243                | 222 | 245                      | 261    | 266                |      |

|                  | Supply               |                | 48 MHz            | 153                      | 174                                 | 182   | 186                | 165 | 185                      | 198    | 203                |      |

|                  |                      | HSE bypass     | 32 MHz            | 105                      | 124                                 | 131   | 133                | 114 | 132                      | 141    | 143                |      |

|                  | current in           | ,,,,,,,,       | 24 MHz            | 82                       | 98                                  | 104   | 105                | 89  | 106                      | 111    | 113                |      |

| l                | Run mode,<br>code    | · .            | 8 MHz             | 3.1                      | 4.1                                 | 4.1   | 5.1                | 3.6 | 4.7                      | 5.2    | 5.5                | μΑ   |

| I <sub>DDA</sub> | executing            |                | 1 MHz             | 3.1                      | 4.1                                 | 4.1   | 5.1                | 3.6 | 4.7                      | 5.2    | 5.5                | μΑ   |

|                  | from Flash<br>or RAM |                | 64 MHz            | 270                      | 294                                 | 307   | 312                | 296 | 322                      | 338    | 343                |      |

|                  | OI KAWI              |                | 48 MHz            | 219                      | 242                                 | 253   | 257                | 240 | 263                      | 276    | 281                |      |

|                  |                      | HSI clock      | 32 MHz            | 171                      | 192                                 | 201   | 203                | 188 | 209                      | 219    | 222                |      |

|                  |                      |                | 24 MHz            | 148                      | 169                                 | 175   | 177                | 163 | 182                      | 190    | 193                |      |

|                  |                      |                | 8 MHz             | 69                       | 84                                  | 87    | 87                 | 79  | 92                       | 94     | 96                 |      |

Current consumption from the V<sub>DDA</sub> supply is independent of whether the peripherals are on or off. Furthermore when the PLL is off, I<sub>DDA</sub> is independent from the frequency.

Table 30. Typical and maximum  $\mathbf{V}_{\text{DD}}$  consumption in Stop and Standby modes

|                 |                               |                                                  | Typ $@V_{DD}(V_{DD}=V_{DDA})$ |       |       |       |       |       |                           |                           |                            |      |

|-----------------|-------------------------------|--------------------------------------------------|-------------------------------|-------|-------|-------|-------|-------|---------------------------|---------------------------|----------------------------|------|

| Symbol          | Parameter                     | Conditions                                       | 2.0 V                         | 2.4 V | 2.7 V | 3.0 V | 3.3 V | 3.6 V | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

|                 | O                             | Regulator in run mode, all oscillators OFF       | 16.92                         | 17.09 | 17.16 | 17.27 | 17.39 | 17.50 | 29.7                      | 359.1                     | 564.5                      |      |

| I <sub>DD</sub> | Stop mode                     | Regulator in low-power mode, all oscillators OFF | 5.29                          | 5.46  | 5.55  | 5.70  | 5.73  | 5.95  | 16.40                     | 267.1                     | 407.4                      | μA   |

| DD              | 1- 1- 7                       | LSI ON and IWDG ON                               | 0.80                          | 0.93  | 1.11  | 1.19  | 1.31  | 1.41  | ı                         | ı                         | ı                          |      |

|                 | current in<br>Standby<br>mode | LSI OFF and IWDG OFF                             | 0.63                          | 0.76  | 0.84  | 0.95  | 1.02  | 1.10  | 5.00                      | 6.30                      | 12.60                      |      |

<sup>1.</sup> Guaranteed by characterization results.

<sup>2.</sup> Guaranteed by characterization results.

<sup>3.</sup> Data based on characterization results and tested in production with code executing from RAM.

Figure 13. Typical V<sub>BAT</sub> current consumption (LSE and RTC ON/LSEDRV[1:0] = '00')

#### **Typical current consumption**

The MCU is placed under the following conditions:

- V<sub>DD</sub> = V<sub>DDA</sub> = 3.3 V

- All I/O pins available on each package are in analog input configuration

- The Flash access time is adjusted to f<sub>HCLK</sub> frequency (0 wait states from 0 to 24 MHz, 1 wait state from 24 to 48 MHz and 2 wait states from 48 MHz to 72 MHz), and Flash prefetch is ON

- When the peripherals are enabled,  $f_{APB1} = f_{AHB/2}$ ,  $f_{APB2} = f_{AHB}$

- PLL is used for frequencies greater than 8 MHz

- AHB prescaler of 2, 4, 8,16 and 64 is used for the frequencies 4 MHz, 2 MHz, 1 MHz, 500 kHz and 125 kHz respectively.

Table 33. Typical current consumption in Run mode, code with data processing running from Flash

|                                     |                                 |                                       |                   | Ту                     | /p                      |             |

|-------------------------------------|---------------------------------|---------------------------------------|-------------------|------------------------|-------------------------|-------------|

| Symbol                              | Parameter                       | Conditions                            | f <sub>HCLK</sub> | Peripherals<br>enabled | Peripherals<br>disabled | Unit        |

|                                     |                                 |                                       | 72 MHz            | 44.8                   | 24.9                    |             |

|                                     |                                 |                                       | 64 MHz            | 40.0                   | 22.4                    |             |

|                                     |                                 |                                       | 48 MHz            | 30.3                   | 17.1                    |             |

|                                     |                                 |                                       | 32 MHz            | 20.7                   | 11.9                    |             |

|                                     |                                 |                                       | 24 MHz            | 15.8                   | 9.2                     |             |

|                                     | Supply current in Run mode from |                                       | 16 MHz            | 10.9                   | 6.5                     | mA          |

| I <sub>DD</sub>                     | V <sub>DD</sub> supply          |                                       | 8 MHz             | 5.7                    | 3.55                    | IIIA        |

|                                     | 00 - 11 7                       |                                       | 4 MHz             | 3.43                   | 3.22                    | -<br>-<br>- |

|                                     |                                 | Running from HSE crystal clock 8 MHz, | 2 MHz             | 2.18                   | 1.53                    |             |

|                                     |                                 |                                       | 1 MHz             | 1.56                   | 1.19                    |             |

|                                     |                                 |                                       | 500 kHz           | 1.25                   | 0.96                    |             |

|                                     |                                 |                                       | 125 kHz           | 0.96                   | 0.84                    |             |

|                                     |                                 | code executing from                   | 72 MHz            | 237                    | 7.1                     |             |

|                                     |                                 | Flash                                 | 64 MHz            | 208                    | 8.3                     |             |

|                                     |                                 |                                       | 48 MHz            | 154                    | 154.3<br>105.0          |             |

|                                     |                                 |                                       | 32 MHz            | 105                    |                         |             |

|                                     |                                 |                                       | 24 MHz            | 81.3                   |                         | 1           |

| I <sub>DDA</sub> <sup>(1) (2)</sup> | Supply current in Run mode from |                                       | 16 MHz            | 57                     | <sup>7</sup> .8         |             |

| IDDA` / ` /                         | V <sub>DDA</sub> supply         |                                       | 8 MHz             | 1.1                    | 15                      | μA          |

|                                     | DDA FF 7                        |                                       | 4 MHz             | 1.1                    | 15                      |             |

|                                     |                                 |                                       | 2 MHz             | 1.1                    | 15                      |             |

|                                     |                                 |                                       | 1 MHz             | 1.1                    | 15                      |             |

|                                     |                                 |                                       | 500 kHz           | 1.1                    | 15                      |             |

|                                     |                                 |                                       | 125 kHz           | 1.1                    | 15                      |             |

<sup>1.</sup> V<sub>DDA</sub> supervisor is OFF.

<sup>2.</sup> When peripherals are enabled, the power consumption of the analog part of peripherals such as ADC, DAC, Comparators, OpAmp etc. is not included. Refer to the tables of characteristics in the subsequent sections.

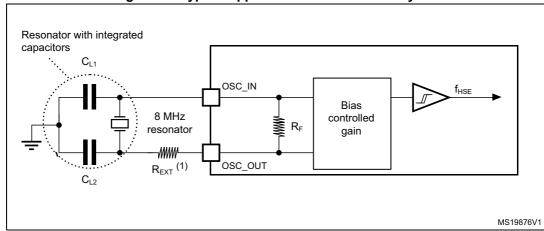

For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (Typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 16*).  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ .

Note:

For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

Figure 16. Typical application with an 8 MHz crystal

1.  $R_{\text{EXT}}$  value depends on the crystal characteristics.

| Table 62. I2S characteristics <sup>(1)</sup> | (continued) |

|----------------------------------------------|-------------|

|----------------------------------------------|-------------|

| Symbol                 | Parameter              | Conditions                             | Min | Max | Unit |

|------------------------|------------------------|----------------------------------------|-----|-----|------|

| t <sub>v(WS)</sub>     | WS valid time          | Master mode                            | -   | 20  |      |

| t <sub>h(WS)</sub>     | WS hold time           | Master mode                            | 2   | -   |      |

| t <sub>su(WS)</sub>    | WS setup time          | Slave mode                             | 0   | 0 - |      |

| t <sub>h(WS)</sub>     | WS hold time           | Slave mode                             | 4   | -   |      |

| t <sub>su(SD_MR)</sub> | Data input actus time  | Master receiver                        | 1   | -   |      |

| t <sub>su(SD_SR)</sub> | Data input setup time  | Slave receiver                         | 1   | -   |      |

| t <sub>h(SD_MR)</sub>  | Data input hold time   | Master receiver                        | 8   | -   | ns   |

| t <sub>h(SD_SR)</sub>  | Data input hold time   | Slave receiver                         | 2.5 | -   |      |

| t <sub>v(SD_ST)</sub>  |                        | Slave transmitter (after enable edge)  | -   | 50  |      |

| t <sub>v(SD_MT)</sub>  | Data output valid time | Master transmitter (after enable edge) | -   | 22  |      |

| t <sub>h(SD_ST)</sub>  |                        | Slave transmitter (after enable edge)  | 8   | -   |      |

| t <sub>h(SD_MT)</sub>  | Data output hold time  | Master transmitter (after enable edge) | 1   | -   |      |

<sup>1.</sup> Guaranteed by characterization results.

#### Note:

Refer to RM0365 Reference Manual I2S Section for more details about the sampling frequency (Fs), fMCK, fCK, DCK values reflect only the digital peripheral behavior, source clock precision might slightly change the values DCK depends mainly on ODD bit value. Digital contribution leads to a min of (I2SDIV/(2\*I2SDIV+ODD) and a max (I2SDIV+ODD)/(2\*I2SDIV+ODD) and Fs max supported for each mode/condition.

<sup>2. 256</sup>xFs maximum is 36 MHz (APB1 Maximum frequency)

*Figure 31* illustrates the ADC current consumption as per the clock frequency in single-ended and differential modes.

Figure 31. ADC typical current consumption in single-ended and differential modes

Table 67. Maximum ADC R<sub>AIN</sub> <sup>(1)</sup>

|            | Sampling                          | Sampling | R <sub>AIN</sub> max (kΩ)       |                  |                                  |  |

|------------|-----------------------------------|----------|---------------------------------|------------------|----------------------------------|--|

| Resolution | cycle @ time [ns] @ 72 MHz 72 MHz |          | Fast<br>channels <sup>(2)</sup> | Slow<br>channels | Other<br>channels <sup>(3)</sup> |  |

|            | 1.5                               | 20.83    | 0.018                           | NA               | NA                               |  |

|            | 2.5                               | 34.72    | 0.150                           | NA               | 0.022                            |  |

|            | 4.5                               | 62.50    | 0.470                           | 0.220            | 0.180                            |  |

| 12 bits    | 7.5                               | 104.17   | 0.820                           | 0.560            | 0.470                            |  |

| 12 Dits    | 19.5                              | 270.83   | 2.70                            | 1.80             | 1.50                             |  |

|            | 61.5                              | 854.17   | 8.20                            | 6.80             | 4.70                             |  |

|            | 181.5                             | 2520.83  | 22.0                            | 18.0             | 15.0                             |  |

|            | 601.5                             | 8354.17  | 82.0                            | 68.0             | 47.0                             |  |

Table 68. ADC accuracy - limited test conditions<sup>(1)(2)</sup>

| Symbol                         | Parameter                                      | Conditions                                                                                |                |                     |      | Тур  | Max<br>(3) | Unit                  |

|--------------------------------|------------------------------------------------|-------------------------------------------------------------------------------------------|----------------|---------------------|------|------|------------|-----------------------|

| Total<br>ET unadjuste<br>error |                                                | rror  tial ADC clock freq. ≤ 72 MHz Sampling freq. ≤ 5 Msps V <sub>DDA</sub> = 3.3 V 25°C | Cinala andad   | Fast channel 5.1 Ms | -    | ±4   | ±4.5       |                       |

|                                | unadjusted                                     |                                                                                           | Single ended   | Slow channel 4.8 Ms | -    | ±5.5 | ±6         | -<br>-<br>-<br>-<br>- |

|                                |                                                |                                                                                           | Differential - | Fast channel 5.1 Ms | -    | ±3.5 | ±4         |                       |

|                                |                                                |                                                                                           |                | Slow channel 4.8 Ms | -    | ±3.5 | ±4         |                       |

| EO                             |                                                |                                                                                           | Single ended   | Fast channel 5.1 Ms | -    | ±2   | ±2         |                       |

|                                | Offeet error                                   |                                                                                           |                | Slow channel 4.8 Ms | -    | ±1.5 | ±2         |                       |

|                                | Offset error                                   |                                                                                           | Differential   | Fast channel 5.1 Ms | -    | ±1.5 | ±2         |                       |

|                                |                                                |                                                                                           |                | Slow channel 4.8 Ms | -    | ±1.5 | ±2         |                       |

| EG                             |                                                |                                                                                           | Cinale anded   | Fast channel 5.1 Ms | -    | ±3   | ±4         |                       |

|                                | Gain error                                     |                                                                                           | Single ended   | Slow channel 4.8 Ms | -    | ±5   | ±5.5       |                       |

|                                |                                                |                                                                                           | Differential   | Fast channel 5.1 Ms | -    | ±3   | ±3         |                       |

|                                |                                                |                                                                                           |                | Slow channel 4.8 Ms | -    | ±3   | ±3.5       |                       |

| ED                             | Differential<br>linearity<br>error             |                                                                                           | Single ended   | Fast channel 5.1 Ms | -    | ±1   | ±1         |                       |

|                                |                                                |                                                                                           |                | Slow channel 4.8 Ms | -    | ±1   | ±1         |                       |

|                                |                                                |                                                                                           | Differential   | Fast channel 5.1 Ms | -    | ±1   | ±1         |                       |

|                                |                                                |                                                                                           |                | Slow channel 4.8 Ms | -    | ±1   | ±1         |                       |

| EL                             | Integral<br>linearity<br>error                 |                                                                                           | Single ended   | Fast channel 5.1 Ms | -    | ±1.5 | ±2         |                       |

|                                |                                                |                                                                                           |                | Slow channel 4.8 Ms | -    | ±2   | ±3         |                       |

|                                |                                                |                                                                                           | Differential   | Fast channel 5.1 Ms | -    | ±1.5 | ±1.5       |                       |

|                                |                                                |                                                                                           |                | Slow channel 4.8 Ms | -    | ±1.5 | ±2         |                       |

| ENOB (4)                       | Effective<br>number of<br>bits                 |                                                                                           | Single ended   | Fast channel 5.1 Ms | 10.8 | 10.8 | -          | - bit                 |

|                                |                                                |                                                                                           |                | Slow channel 4.8 Ms | 10.8 | 10.8 | 1          |                       |

|                                |                                                |                                                                                           | Differential   | Fast channel 5.1 Ms | 11.2 | 11.3 | -          |                       |

|                                |                                                |                                                                                           |                | Slow channel 4.8 Ms | 11.2 | 11.3 | -          |                       |

|                                | Signal-to-<br>noise and<br>distortion<br>ratio |                                                                                           | Single ended   | Fast channel 5.1 Ms | 66   | 67   | -          | - dB                  |

| SINAD                          |                                                |                                                                                           |                | Slow channel 4.8 Ms | 66   | 67   | -          |                       |

| (4)                            |                                                |                                                                                           | D:#: # # #     | Fast channel 5.1 Ms | 69   | 70   | -          |                       |

|                                |                                                |                                                                                           | Differential   | Slow channel 4.8 Ms | 69   | 70   | -          |                       |

| Table 77. WLCSP49 - 49-pin, 3.417 x 3.151 mm, 0.4 mm pitch wafer level chip scale |

|-----------------------------------------------------------------------------------|

| package mechanical data                                                           |

| Symbol            | millimeters |        |       | inches <sup>(1)</sup> |        |        |

|-------------------|-------------|--------|-------|-----------------------|--------|--------|

| Symbol            | Min         | Тур    | Max   | Min                   | Тур    | Max    |

| Α                 | 0.525       | 0.555  | 0.585 | 0.0207                | 0.0219 | 0.0230 |

| A1                | -           | 0.175  | -     | -                     | 0.0069 | -      |

| A2                | -           | 0.380  | -     | -                     | 0.0150 | -      |

| A3 <sup>(2)</sup> | -           | 0.025  | -     | -                     | 0.0010 | -      |

| b <sup>(3)</sup>  | 0.220       | 0.250  | 0.280 | 0.0087                | 0.0098 | 0.0110 |

| D                 | 3.382       | 3.417  | 3.452 | 0.1331                | 0.1345 | 0.1359 |

| E                 | 3.116       | 3.151  | 3.186 | 0.1227                | 0.1241 | 0.1254 |

| е                 | -           | 0.400  | -     | -                     | 0.0157 | -      |

| e1                | -           | 2.400  | -     | -                     | 0.0945 | -      |

| e2                | -           | 2.400  | -     | -                     | 0.0945 | -      |

| F                 | -           | 0.5085 | -     | -                     | 0.0200 | -      |

| G                 | -           | 0.3755 | -     | -                     | 0.0148 | -      |

| aaa               | -           | -      | 0.100 | -                     | -      | 0.0039 |

| bbb               | -           | -      | 0.100 | -                     | -      | 0.0039 |

| ccc               | -           | -      | 0.100 | -                     | -      | 0.0039 |

| ddd               | -           | -      | 0.050 | -                     | -      | 0.0020 |

| eee               | -           | -      | 0.050 | -                     | -      | 0.0020 |

- 1. Values in inches are converted from mm and rounded to 4 decimal digits.

- 2. Back side coating

- 3. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

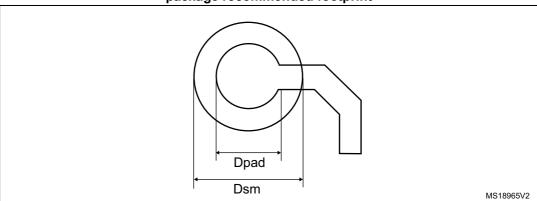

Figure 38. WLCSP49 - 49-pin, 3.417 x 3.151 mm, 0.4 mm pitch wafer level chip scale package recommended footprint

Table 78. WLCSP49 recommended PCB design rules (0.4 mm pitch)

| Dimension      | Recommended values                             |  |  |

|----------------|------------------------------------------------|--|--|

| Pitch          | 0.4                                            |  |  |

| Dpad           | 260 µm max. (circular)                         |  |  |

| ррац           | 220 µm recommended                             |  |  |

| Dsm            | 300 μm min. (for 260 μm diameter pad)          |  |  |

| PCB pad design | Non-solder mask defined via underbump allowed. |  |  |

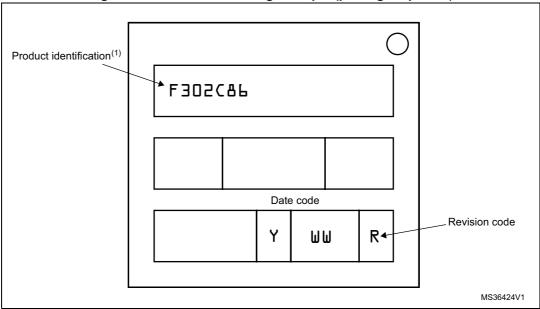

#### **Device marking**

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Figure 39. WLCSP49 marking example (package top view)

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

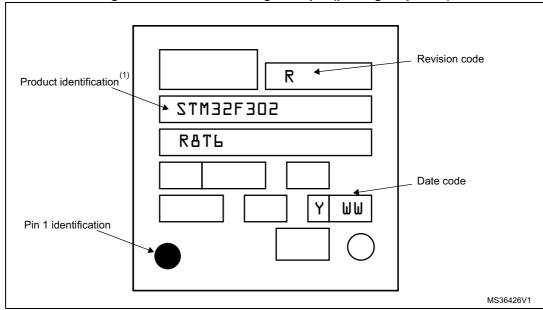

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Figure 42. LQFP64 marking example (package top view)

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

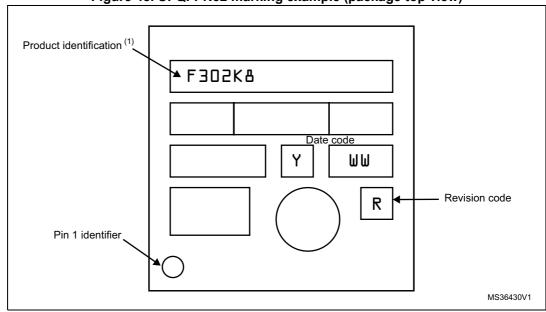

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Figure 48. UFQFPN32 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet

qualified and therefore not yet ready to be used in production and any consequences deriving from such

usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering

samples in production. ST Quality has to be contacted prior to any decision to use these Engineering

Samples to run qualification activity.

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics - All rights reserved