Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | ARM® Cortex®-M4                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB          |

| Peripherals                | DMA, I²S, POR, PWM, WDT                                               |

| Number of I/O              | 51                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 16K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 15x12b; D/A 1x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f302r8t7 |

# List of tables

| Table 1.  | STM32F302x6/8 device features and peripheral counts                                   | 11 |

|-----------|---------------------------------------------------------------------------------------|----|

| Table 2.  | External analog supply values for analog peripherals                                  |    |

| Table 3.  | STM32F302x6/8 peripheral interconnect matrix                                          | 16 |

| Table 4.  | Timer feature comparison                                                              | 22 |

| Table 5.  | Comparison of I2C analog and digital filters                                          |    |

| Table 6.  | STM32F302x6/8 I <sup>2</sup> C implementation                                         | 26 |

| Table 7.  | USART features                                                                        |    |

| Table 8.  | STM32F302x6/8 SPI/I2S implementation                                                  | 28 |

| Table 9.  | Capacitive sensing GPIOs available on STM32F302x6/8 devices                           | 29 |

| Table 10. | No. of capacitive sensing channels available on                                       |    |

|           | STM32F302x6/8 devices                                                                 | 29 |

| Table 11. | Legend/abbreviations used in the pinout table                                         | 35 |

| Table 12. | STM32F302x6/8 pin definitions                                                         | 36 |

| Table 13. | Alternate functions for Port A                                                        | 43 |

| Table 14. | Alternate functions for Port B                                                        | 45 |

| Table 15. | Alternate functions for Port C                                                        | 47 |

| Table 16. | Alternate functions for Port D                                                        | 48 |

| Table 17. | Alternate functions for Port F                                                        | 48 |

| Table 18. | STM32F302x6 STM32F302x8 peripheral register boundary                                  |    |

|           | addresses                                                                             | 50 |

| Table 19. | Voltage characteristics                                                               | 56 |

| Table 20. | Current characteristics                                                               | 57 |

| Table 21. | Thermal characteristics                                                               | 57 |

| Table 22. | General operating conditions                                                          | 58 |

| Table 23. | Operating conditions at power-up / power-down                                         | 59 |

| Table 24. | Embedded reset and power control block characteristics                                | 59 |

| Table 25. | Programmable voltage detector characteristics                                         | 60 |

| Table 26. | Embedded internal reference voltage                                                   | 61 |

| Table 27. | Internal reference voltage calibration values                                         | 61 |

| Table 28. | Typical and maximum current consumption from VDD supply at VDD = 3.6V                 | 62 |

| Table 29. | Typical and maximum current consumption from the V <sub>DDA</sub> supply              |    |

| Table 30. | Typical and maximum V <sub>DD</sub> consumption in Stop and Standby modes             | 64 |

| Table 31. | Typical and maximum V <sub>DDA</sub> consumption in Stop and Standby modes            | 65 |

| Table 32. | Typical and maximum current consumption from V <sub>BAT</sub> supply                  | 65 |

| Table 33. | Typical current consumption in Run mode, code with data processing running from Flash | 67 |

| Table 34. | Typical current consumption in Sleep mode, code running from Flash or RAM             |    |

| Table 35. | Switching output I/O current consumption                                              |    |

| Table 36. | Peripheral current consumption                                                        |    |

| Table 37. | Low-power mode wakeup timings                                                         |    |

| Table 38. | Wakeup time using USART                                                               |    |

| Table 39. | High-speed external user clock characteristics                                        |    |

| Table 40. | Low-speed external user clock characteristics                                         |    |

| Table 41. | HSE oscillator characteristics                                                        | 76 |

| Table 42. | LSE oscillator characteristics (f <sub>LSE</sub> = 32.768 kHz)                        | 78 |

| Table 43. | HSI oscillator characteristics                                                        | 80 |

| Table 44. | LSI oscillator characteristics                                                        |    |

| Table 45. | PLL characteristics                                                                   |    |

| Table 46. | Flash memory characteristics                                                          | 82 |

# List of figures

| Figure 1.  | DS9896 block diagram                                                             | 12  |

|------------|----------------------------------------------------------------------------------|-----|

| Figure 2.  | Clock tree                                                                       |     |

| Figure 3.  | Infrared transmitter                                                             | 30  |

| Figure 4.  | STM32F302x6/8 UFQFN32 pinout                                                     | 32  |

| Figure 5.  | STM32F302x6/8 LQFP48 pinout                                                      | 32  |

| Figure 6.  | STM32F302x6/8 LQFP64 pinout                                                      | 33  |

| Figure 7.  | STM32F302x6/8 WLCSP49 ballout                                                    | 34  |

| Figure 8.  | STM32F302x6/8 memory mapping                                                     | 49  |

| Figure 9.  | Pin loading conditions                                                           | 53  |

| Figure 10. | Pin input voltage                                                                |     |

| Figure 11. | Power supply scheme                                                              |     |

| Figure 12. | Current consumption measurement scheme                                           |     |

| Figure 13. | Typical V <sub>BAT</sub> current consumption (LSE and RTC ON/LSEDRV[1:0] = '00') | 66  |

| Figure 14. | High-speed external clock source AC timing diagram                               |     |

| Figure 15. | Low-speed external clock source AC timing diagram                                |     |

| Figure 16. | Typical application with an 8 MHz crystal                                        |     |

| Figure 17. | Typical application with a 32.768 kHz crystal                                    |     |

| Figure 18. | HSI oscillator accuracy characterization results for soldered parts              |     |

| Figure 19. | TC and TTa I/O input characteristics - CMOS port                                 |     |

| Figure 20. | TC and TTa I/O input characteristics - TTL port                                  |     |

| Figure 21. | Five volt tolerant (FT and FTf) I/O input characteristics - CMOS port            |     |

| Figure 22. | Five volt tolerant (FT and FTf) I/O input characteristics - TTL port             |     |

| Figure 23. | I/O AC characteristics definition                                                |     |

| Figure 24. | Recommended NRST pin protection                                                  |     |

| Figure 25. | SPI timing diagram - slave mode and CPHA = 0                                     |     |

| Figure 26. | SPI timing diagram - slave mode and CPHA = 1 <sup>(1)</sup>                      |     |

| Figure 27. | SPI timing diagram - master mode <sup>(1)</sup>                                  | 97  |

| Figure 28. | I <sup>2</sup> S slave timing diagram (Philips protocol) <sup>(1)</sup>          | 99  |

| Figure 29. | I <sup>2</sup> S master timing diagram (Philips protocol) <sup>(1)</sup>         | 99  |

| Figure 30. | USB timings: definition of data signal rise and fall time                        |     |

| Figure 31. | ADC typical current consumption in single-ended and differential modes           |     |

| Figure 32. | ADC accuracy characteristics                                                     |     |

| Figure 33. | Typical connection diagram using the ADC                                         |     |

| Figure 34. | 12-bit buffered /non-buffered DAC                                                |     |

| Figure 35. | Maximum V <sub>REFINT</sub> scaler startup time from power down                  | 113 |

| Figure 36. | OPAMP Voltage Noise versus Frequency                                             |     |

| Figure 37. | WLCSP49 - 49-pin, 3.417 x 3.151 mm, 0.4 mm pitch wafer level chip scale          |     |

| Ü          | package outline                                                                  | 119 |

| Figure 38. | WLCSP49 - 49-pin, 3.417 x 3.151 mm, 0.4 mm pitch wafer level chip scale          |     |

| J          | package recommended footprint                                                    | 120 |

| Figure 39. | WLCSP49 marking example (package top view)                                       |     |

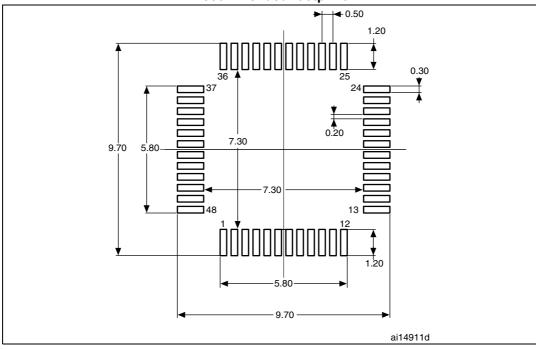

| Figure 40. | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline                |     |

| Figure 41. | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package                        |     |

| <b>J</b>   | recommended footprint                                                            | 123 |

| Figure 42. | LQFP64 marking example (package top view)                                        | 124 |

| Figure 43. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline                  | 125 |

| Figure 44. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package                          |     |

| ū          | recommended footprint                                                            | 127 |

# List of figures

### STM32F302x6 STM32F302x8

| Figure 45. | LQFP48 marking example (package top view)                               | 128 |

|------------|-------------------------------------------------------------------------|-----|

| Figure 46. | UFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch ultra thin fine pitch quad flat |     |

|            | package outline                                                         | 129 |

| Figure 47. | UFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch ultra thin fine pitch quad flat |     |

|            | package recommended footprint                                           | 130 |

| Figure 48. | UFQFPN32 marking example (package top view)                             | 131 |

8/138 DocID025147 Rev 6

#### 3.11 Fast analog-to-digital converter (ADC)

An analog-to-digital converter, with selectable resolution between 12 and 6 bit, is embedded in the STM32F302x6/8 family devices. The ADC has up to 15 external channels performing conversions in single-shot or scan modes. Channels can be configured to be either singleended input or differential input. In scan mode, automatic conversion is performed on a selected group of analog inputs.

Additional logic functions embedded in the ADC interface allow:

- Simultaneous sample and hold

- Single-shunt phase current reading techniques.

The ADC can be served by the DMA controller.

Three analog watchdogs are available. The analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

The events generated by the general-purpose timers (TIMx) and the advanced-control timer (TIM1) can be internally connected to the ADC start trigger and injection trigger, respectively, to allow the application to synchronize A/D conversion and timers.

#### 3.11.1 Temperature sensor

The temperature sensor (TS) generates a voltage V<sub>SENSE</sub> that varies linearly with temperature.

The temperature sensor is internally connected to the ADC1 IN16 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode.

#### 3.11.2 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference (V<sub>REFINT</sub>) provides a stable (bandgap) voltage output for the ADC and Comparators. V<sub>REFINT</sub> is internally connected to the ADC1\_IN18 input channel. The precise voltage of V<sub>REFINT</sub> is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode.

20/138 DocID025147 Rev 6

### 3.24 Development support

### 3.24.1 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP Interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target.

The JTAG TMS and TCK pins are shared respectively with SWDIO and SWCLK and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

|        | Table 12. STM32F302x6/8 pin definitions |        |        |                                             |          |               |       |                                                |                                      |

|--------|-----------------------------------------|--------|--------|---------------------------------------------|----------|---------------|-------|------------------------------------------------|--------------------------------------|

|        | Pin Nu                                  | umber  | •      |                                             |          |               |       |                                                |                                      |

| UQFN32 | WLCSP49                                 | LQFP48 | LQFP64 | Pin name<br>(function after reset)          | Pin type | I/O structure | Notes | Alternate<br>functions                         | Additional<br>functions              |

| -      | B6                                      | 1      | 1      | VBAT                                        | 8        | -             | -     | Backup po                                      | wer supply                           |

| -      | D5                                      | 2      | 2      | PC13 <sup>(1)</sup> TAMPER1<br>WKUP2 (PC13) | I/O      | TC            | (1)   | TIM1_CH1N                                      | WKUP2, RTC_TAMP1,<br>RTC_TS, RTC_OUT |

| -      | C7                                      | 3      | 3      | PC14 <sup>(1)</sup> OSC32_IN<br>(PC14)      | I/O      | TC            | (1)   | -                                              | OSC32_IN                             |

| -      | C6                                      | 4      | 4      | PC15 <sup>(1)</sup> OSC32_OUT<br>(PC14)     | I/O      | TC            | (1)   | -                                              | OSC32_OUT                            |

| 2      | D7                                      | 5      | 5      | PF0 OSC_IN (PF0)                            | I/O      | FTf           | -     | I2C2_SDA, SPI2_NSS/I2S2_WS,<br>TIM1_CH3N       | OSC_IN                               |

| 3      | D6                                      | 6      | 6      | PF1 OSC_OUT (PF1)                           | Ο        | FTf           | -     | I2C2_SCL, SPI2_SCK/I2S2_CK                     | OSC_OUT                              |

| 4      | E7                                      | 7      | 7      | NRST                                        | I/O      | RST           | -     | Device reset input/interna                     | I reset output (active low)          |

| -      | -                                       | -      | 8      | PC0                                         | I/O      | TTa           | -     | EVENTOUT, TIM1_CH1                             | ADC1_IN6                             |

| -      | -                                       | -      | 9      | PC1                                         | I/O      | TTa           | -     | EVENTOUT, TIM1_CH2                             | ADC1_IN7                             |

| -      | -                                       | -      | 10     | PC2                                         | I/O      | TTa           | -     | EVENTOUT, TIM1_CH3                             | ADC1_IN8                             |

| -      | -                                       | ı      | 11     | PC3                                         | I/O      | TTa           | -     | EVENTOUT, TIM1_CH4,<br>TIM1_BKIN2              | ADC1_IN9                             |

| 6      | E6                                      | 8      | 12     | VSSA/VREF-                                  | S        | -             | -     | Analog ground/Negative reference voltage       |                                      |

| 5      | A6                                      | 9      | 13     | VDDA/VREF+                                  | S        | -             | -     | Analog power supply/Positive reference voltage |                                      |

DocID025147 Rev 6

|        | Pin Nu  | umber  | •      |                                    |          |               |                                                                            |                                                                                                          |                         |

|--------|---------|--------|--------|------------------------------------|----------|---------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------|

| UQFN32 | WLCSP49 | LQFP48 | LQFP64 | Pin name<br>(function after reset) | Pin type | I/O structure | Notes                                                                      | Alternate<br>functions                                                                                   | Additional<br>functions |

| -      | F1      | 27     | 35     | PB14                               | I/O      | ТТа           | -                                                                          | TIM15_CH1, TSC_G6_IO4,<br>SPI2_MISO/I2S2ext_SD,<br>TIM1_CH2N, USART3_RTS_DE,<br>EVENTOUT                 | OPAMP2_VINP             |

| -      | E1      | 28     | 36     | PB15                               | I/O      | ТТа           | RTC_REFIN, TIM15_CH2, - TIM15_CH1N, TIM1_CH3N, SPI2_MOSI/I2S2_SD, EVENTOUT |                                                                                                          | COMP6_INM               |

| -      | 1       | -      | 37     | PC6                                | I/O      | FT            | -                                                                          | EVENTOUT, I2S2_MCK,<br>COMP6_OUT                                                                         | -                       |

| -      | 1       | -      | 38     | PC7                                | I/O      | FT            | -                                                                          | EVENTOUT, I2S3_MCK                                                                                       | -                       |

| -      | 1       | -      | 39     | PC8                                | I/O      | FT            | -                                                                          | EVENTOUT                                                                                                 | -                       |

| -      | ı       | -      | 40     | PC9                                | I/O      | FTf           | -                                                                          | EVENTOUT, I2C3_SDA, I2SCKIN                                                                              | -                       |

| 18     | D1      | 29     | 41     | PA8                                | I/O      | FT            | -                                                                          | MCO, I2C3_SCL, I2C2_SMBAL,<br>I2S2_MCK, TIM1_CH1,<br>USART1_CK, EVENTOUT                                 | -                       |

| 19     | D2      | 30     | 42     | PA9                                | I/O      | FTf           | -                                                                          | I2C3_SMBAL, TSC_G4_IO1,<br>I2C2_SCL, I2S3_MCK, TIM1_CH2,<br>USART1_TX, TIM15_BKIN,<br>TIM2_CH3, EVENTOUT | -                       |

Table 12. STM32F302x6/8 pin definitions (continued)

#### I/O system current consumption

The current consumption of the I/O system has two components: static and dynamic.

#### I/O static current consumption

All the I/Os used as inputs with pull-up generate current consumption when the pin is externally held low. The value of this current consumption can be simply computed by using the pull-up/pull-down resistors values given in *Table 53: I/O static characteristics*.

For the output pins, any external pull-down or external load must also be considered to estimate the current consumption.

Additional I/O current consumption is due to I/Os configured as inputs if an intermediate voltage level is externally applied. This current consumption is caused by the input Schmitt trigger circuits used to discriminate the input value. Unless this specific configuration is required by the application, this supply current consumption can be avoided by configuring these I/Os in analog mode. This is notably the case of ADC input pins which should be configured as analog inputs.

#### Caution:

Any floating input pin can also settle to an intermediate voltage level or switch inadvertently, as a result of external electromagnetic noise. To avoid current consumption related to floating pins, they must either be configured in analog mode, or forced internally to a definite digital value. This can be done either by using pull-up/down resistors or by configuring the pins in output mode.

#### I/O dynamic current consumption

In addition to the internal peripheral current consumption (see *Table 36: Peripheral current consumption*), the I/Os used by an application also contribute to the current consumption. When an I/O pin switches, it uses the current from the MCU supply voltage to supply the I/O pin circuitry and to charge/discharge the capacitive load (internal or external) connected to the pin:

$$I_{SW} = V_{DD} \times f_{SW} \times C$$

where

$I_{SW}$  is the current sunk by a switching I/O to charge/discharge the capacitive load  $V_{DD}$  is the MCU supply voltage

f<sub>SW</sub> is the I/O switching frequency

C is the total capacitance seen by the I/O pin:  $C = C_{INT} + C_{EXT} + C_{S}$

The test pin is configured in push-pull output mode and is toggled by software at a fixed frequency.

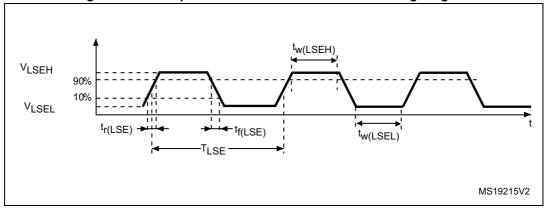

### Low-speed external user clock generated from an external source

In bypass mode the LSE oscillator is switched off and the input pin is a standard GPIO. The external clock signal has to respect the I/O characteristics in *Section 6.3.14*. However, the recommended clock input waveform is shown in *Figure 15*

Table 40. Low-speed external user clock characteristics

| Symbol                                                                 | Parameter                                           | Conditions | Min                | Тур    | Max                | Unit        |

|------------------------------------------------------------------------|-----------------------------------------------------|------------|--------------------|--------|--------------------|-------------|

| f <sub>LSE_ext</sub>                                                   | User External clock source frequency <sup>(1)</sup> |            | -                  | 32.768 | 1000               | kHz         |

| V <sub>LSEH</sub>                                                      | OSC32_IN input pin high level voltage               |            | 0.7V <sub>DD</sub> | -      | $V_{DD}$           | <b>&gt;</b> |

| V <sub>LSEL</sub>                                                      | OSC32_IN input pin low level voltage                | -          | V <sub>SS</sub>    | ı      | 0.3V <sub>DD</sub> | V           |

| $\begin{matrix} t_{\text{w(LSEH)}} \\ t_{\text{w(LSEL)}} \end{matrix}$ | OSC32_IN high or low time <sup>(1)</sup>            |            | 450                | ı      | ı                  | ns          |

| $\begin{array}{c} t_{r(\text{LSE})} \\ t_{f(\text{LSE})} \end{array}$  | OSC32_IN rise or fall time <sup>(1)</sup>           |            | -                  | -      | 50                 | 110         |

<sup>1.</sup> Guaranteed by design.

Figure 15. Low-speed external clock source AC timing diagram

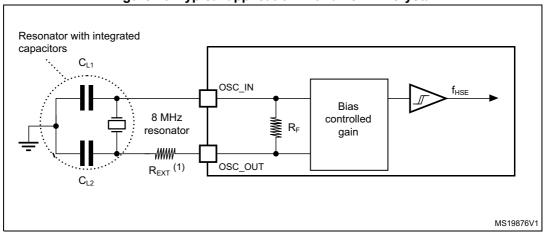

For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (Typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 16*).  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ .

Note:

For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

Figure 16. Typical application with an 8 MHz crystal

1.  $R_{\text{EXT}}$  value depends on the crystal characteristics.

### Low-speed internal (LSI) RC oscillator

Table 44. LSI oscillator characteristics<sup>(1)</sup>

| Symbol                              | Parameter                                                            | Min | Тур  | Max | Unit |

|-------------------------------------|----------------------------------------------------------------------|-----|------|-----|------|

| f <sub>LSI</sub>                    | f <sub>LSI</sub> Frequency                                           |     | 40   | 50  | kHz  |

| t <sub>su(LSI)</sub> <sup>(2)</sup> | LSI oscillator startup time                                          |     | -    | 85  | μs   |

| I <sub>DD(LSI)</sub> <sup>(2)</sup> | I <sub>DD(LSI)</sub> <sup>(2)</sup> LSI oscillator power consumption |     | 0.75 | 1.2 | μΑ   |

<sup>1.</sup>  $V_{DDA}$  = 3.3 V,  $T_A$  = -40 to 105 °C unless otherwise specified.

#### 6.3.9 PLL characteristics

The parameters given in *Table 45* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 22*.

Table 45. PLL characteristics

| Symbol               | Parameter                      |                   | Unit |                    |       |

|----------------------|--------------------------------|-------------------|------|--------------------|-------|

| Symbol               | Farameter                      | Min               | Тур  | Max                | Oilit |

| f                    | PLL input clock <sup>(1)</sup> | 1 <sup>(2)</sup>  | -    | 24 <sup>(2)</sup>  | MHz   |

| f <sub>PLL_IN</sub>  | PLL input clock duty cycle     | 40 <sup>(2)</sup> | -    | 60 <sup>(2)</sup>  | %     |

| f <sub>PLL_OUT</sub> | PLL multiplier output clock    | 16 <sup>(2)</sup> | -    | 72                 | MHz   |

| t <sub>LOCK</sub>    | PLL lock time                  | -                 | -    | 200 <sup>(2)</sup> | μs    |

| Jitter               | Cycle-to-cycle jitter          | -                 | -    | 300 <sup>(2)</sup> | ps    |

Take care of using the appropriate multiplier factors so as to have PLL input clock values compatible with the range defined by f<sub>PLL\_OUT</sub>.

<sup>2.</sup> Guaranteed by design.

<sup>2.</sup> Guaranteed by design.

#### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latch-up standard.

Table 51. Electrical sensitivities

| Symbol | Parameter             | Conditions                                     | Class     |

|--------|-----------------------|------------------------------------------------|-----------|

| LU     | Static latch-up class | T <sub>A</sub> = +105 °C conforming to JESD78A | 2 level A |

### 6.3.13 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard, 3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (higher than 5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of  $-5 \,\mu\text{A}/+0 \,\mu\text{A}$  range), or other functional failure (for example reset occurrence or oscillator frequency deviation).

The test results are given in *Table 52*

Table 52. I/O current injection susceptibility

|                  |                                                                                                                                                                                                                | Functional s       |                    |      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|------|

| Symbol           | Description                                                                                                                                                                                                    | Negative injection | Positive injection | Unit |

|                  | Injected current on BOOT0                                                                                                                                                                                      | -0                 | NA                 |      |

|                  | Injected current on PC0 pin (TTa pin)                                                                                                                                                                          | -0                 | +5                 |      |

| I <sub>INJ</sub> | Injected current PC0, PC1, PC2, PC3, PA0, PA1, PA2, PA3, PA4, PA6, PA7, PC4, PB0, PB10, PB11, PB13 with induced leakage current on other pins from this group less than -100 $\mu$ A or more than +100 $\mu$ A | -5                 | +5                 | mA   |

|                  | Injected current on any other TT, FT and FTf pins                                                                                                                                                              | -5                 | NA                 |      |

|                  | Injected current on all other TC, TTa and RESET pins                                                                                                                                                           | -5                 | +5                 |      |

Note:

It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

| Table 62. I2S characteristics <sup>(1)</sup> | (continued) |

|----------------------------------------------|-------------|

|----------------------------------------------|-------------|

| Symbol                 | Parameter              | Conditions                             | Min | Max | Unit |

|------------------------|------------------------|----------------------------------------|-----|-----|------|

| t <sub>v(WS)</sub>     | WS valid time          | Master mode                            | -   | 20  |      |

| t <sub>h(WS)</sub>     | WS hold time           | Master mode                            | 2   | -   |      |

| t <sub>su(WS)</sub>    | WS setup time          | Slave mode                             | 0   | -   |      |

| t <sub>h(WS)</sub>     | WS hold time           | Slave mode                             | 4   | -   |      |

| t <sub>su(SD_MR)</sub> | Data input actus time  | Master receiver                        | 1   | -   |      |

| t <sub>su(SD_SR)</sub> | Data input setup time  | Slave receiver                         | 1   | -   |      |

| t <sub>h(SD_MR)</sub>  | Data input hold time   | Master receiver                        | 8   | -   | ns   |

| t <sub>h(SD_SR)</sub>  | Data input hold time   | Slave receiver                         | 2.5 | -   |      |

| t <sub>v(SD_ST)</sub>  |                        | Slave transmitter (after enable edge)  | -   | 50  |      |

| t <sub>v(SD_MT)</sub>  | Data output valid time | Master transmitter (after enable edge) | -   | 22  |      |

| t <sub>h(SD_ST)</sub>  |                        | Slave transmitter (after enable edge)  | 8   | -   |      |

| t <sub>h(SD_MT)</sub>  | Data output hold time  | Master transmitter (after enable edge) | 1   | -   |      |

<sup>1.</sup> Guaranteed by characterization results.

#### Note:

Refer to RM0365 Reference Manual I2S Section for more details about the sampling frequency (Fs), fMCK, fCK, DCK values reflect only the digital peripheral behavior, source clock precision might slightly change the values DCK depends mainly on ODD bit value. Digital contribution leads to a min of (I2SDIV/(2\*I2SDIV+ODD) and a max (I2SDIV+ODD)/(2\*I2SDIV+ODD) and Fs max supported for each mode/condition.

98/138 DocID025147 Rev 6

<sup>2. 256</sup>xFs maximum is 36 MHz (APB1 Maximum frequency)

Table 65. USB: Full-speed electrical characteristics<sup>(1)</sup> (continued)

| Symbol                                 | Parameter                       | Conditions                     | Min | Тур | Max | Unit |

|----------------------------------------|---------------------------------|--------------------------------|-----|-----|-----|------|

| t <sub>rfm</sub>                       | Rise/ fall time matching        | t <sub>r</sub> /t <sub>f</sub> | 90  | -   | 110 | %    |

| V <sub>CRS</sub>                       | Output signal crossover voltage |                                | 1.3 | -   | 2.0 | V    |

| Output driver Impedance <sup>(3)</sup> | Z <sub>DRV</sub>                | driving high and low           | 28  | 40  | 44  | Ω    |

- 1. Guaranteed by design.

- Measured from 10% to 90% of the data signal. For more detailed informations, please refer to USB Specification Chapter 7 (version 2.0).

- 3. No external termination series resistors are required on USB\_DP (D+) and USB\_DM (D-), the matching impedance is already included in the embedded driver.

#### CAN (controller area network) interface

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (CAN TX and CAN RX).

### 6.3.18 ADC characteristics

Unless otherwise specified, the parameters given in *Table 66* to *Table 68* are guaranteed by design, with conditions summarized in *Table 22*.

**Table 66. ADC characteristics**

| Symbol                           | Parameter                                       | Conditions                                        | Min    | Тур    | Max       | Unit               |

|----------------------------------|-------------------------------------------------|---------------------------------------------------|--------|--------|-----------|--------------------|

| $V_{DDA}$                        | Analog supply voltage for ADC                   | -                                                 | 2      | -      | 3.6       | V                  |

|                                  | ADC current consumption (see <i>Figure 31</i> ) | Single-ended mode,<br>5 MSPS                      | -      | 1011.3 | 1172.0    | μΑ                 |

| I <sub>DDA</sub>                 |                                                 | Single-ended mode,<br>1 MSPS                      | -      | 214.7  | 322.3     |                    |

|                                  |                                                 | Single-ended mode,<br>200 KSPS                    | -      | 54.7   | 81.1      |                    |

|                                  |                                                 | Differential mode, 5 MSPS                         | -      | 1061.5 | 1243.6    |                    |

|                                  |                                                 | Differential mode, 1 MSPS                         | -      | 246.6  | 337.6     |                    |

|                                  |                                                 | Differential mode,<br>200 KSPS                    | -      | 56.4   | 83.0      |                    |

| f <sub>ADC</sub>                 | ADC clock frequency                             | -                                                 | 0.14   | -      | 72        | MHz                |

|                                  | Sampling rate                                   | Resolution = 12 bits,<br>Fast Channel             | 0.01   | -      | 5.14      | — MSPS             |

| f <sub>S</sub> <sup>(1)</sup>    |                                                 | Resolution = 10 bits,<br>Fast Channel             | 0.012  | -      | 6         |                    |

| 'S'                              |                                                 | Resolution = 8 bits,<br>Fast Channel              | 0.014  | -      | 7.2       |                    |

|                                  |                                                 | Resolution = 6 bits,<br>Fast Channel              | 0.0175 | -      | 9         |                    |

| f <sub>TRIG</sub> <sup>(1)</sup> | External trigger frequency                      | f <sub>ADC</sub> = 72 MHz<br>Resolution = 12 bits | -      | -      | 5.14      | MHz                |

|                                  |                                                 | Resolution = 12 bits                              | -      | -      | 14        | 1/f <sub>AD0</sub> |

| V <sub>AIN</sub>                 | Conversion voltage range                        | -                                                 | 0      | -      | $V_{DDA}$ | V                  |

| R <sub>AIN</sub> <sup>(1)</sup>  | External input impedance                        | -                                                 | -      | -      | 100       | kΩ                 |

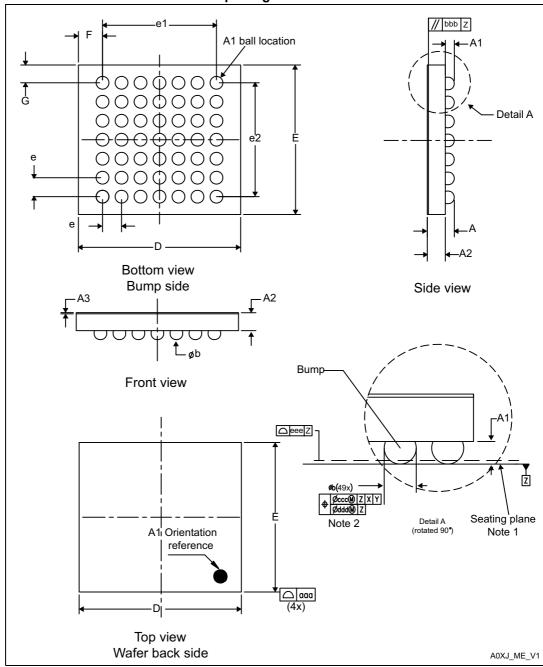

## 7.1 WLCSP49 package information

Figure 37. WLCSP49 - 49-pin, 3.417 x 3.151 mm, 0.4 mm pitch wafer level chip scale package outline

1. Drawing is not to scale.

Table 78. WLCSP49 recommended PCB design rules (0.4 mm pitch)

| Dimension      | Recommended values                             |  |

|----------------|------------------------------------------------|--|

| Pitch          | 0.4                                            |  |

| Dpad           | 260 μm max. (circular)                         |  |

| ррац           | 220 µm recommended                             |  |

| Dsm            | 300 μm min. (for 260 μm diameter pad)          |  |

| PCB pad design | Non-solder mask defined via underbump allowed. |  |

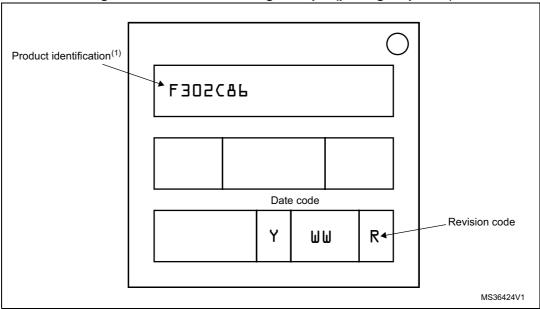

#### **Device marking**

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Figure 39. WLCSP49 marking example (package top view)

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

Figure 44. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

#### 7.5 Thermal characteristics

The maximum chip junction temperature (T<sub>J</sub>max) must never exceed the values given in Table 22: General operating conditions.

The maximum chip-junction temperature, T<sub>J</sub> max, in degrees Celsius, may be calculated using the following equation:

$$T_J \max = T_A \max + (P_D \max x \Theta_{JA})$$

#### Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{IA}$  is the package junction-to-ambient thermal resistance, in ° C/W,

- $P_D$  max is the sum of  $P_{INT}$  max and  $P_{I/O}$  max ( $P_D$  max =  $P_{INT}$  max +  $P_{I/O}$ max),

- $P_{INT}$  max is the product of  $I_{DD}$  and  $V_{DD}$ , expressed in Watts. This is the maximum chip internal power.

$P_{I\!/O}$  max represents the maximum power dissipation on output pins where:

$$P_{I/O} \max = \sum (V_{OL} \times I_{OL}) + \sum ((V_{DD} - V_{OH}) \times I_{OH}),$$

taking into account the actual  $V_{OL}$  /  $I_{OL}$  and  $V_{OH}$  /  $I_{OH}$  of the I/Os at low and high level in the application.

| Symbol            | Parameter                                                              | Value | Unit |  |

|-------------------|------------------------------------------------------------------------|-------|------|--|

| $\Theta_{\sf JA}$ | Thermal resistance junction-ambient LQFP64 - 10 × 10 mm / 0.5 mm pitch | 45    |      |  |

|                   | Thermal resistance junction-ambient LQFP48 - 7 × 7 mm                  | 55    | °C/W |  |

|                   | Thermal resistance junction-ambient WCSP49 - 3.4 x 3.4 mm              | 49    | C/VV |  |

|                   | Thermal resistance junction-ambient UFQFN32 - 5 x 5 mm                 | 37    |      |  |

Table 82. Package thermal characteristics

#### 7.5.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org

DocID025147 Rev 6 132/138

# 8 Ordering information

Table 83. Ordering information scheme STM32 Example: 302 8 Т 6 XXX **Device family** STM32 = ARM<sup>®</sup>-based 32-bit microcontroller **Product type** F = general-purpose **Device subfamily** 302 = STM32F302xx, 2.0 to 3.6 V operating voltage Pin count K = 32 pinsC = 48 or 49 pins R = 64 pinsFlash memory size 6 = 32 Kbytes of Flash memory 8 = 64 Kbytes of Flash memory **Package** T = LQFP Y= WLCSP U= UFQFPN Temperature range 6 = Industrial temperature range, -40 to 85 °C 7 = Industrial temperature range, -40 to 105 °C **Options**

xxx = programmed parts

TR = tape and reel