Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusActiveCore ProcessorARM® Cortex®-M4Core Size32-Bit Single-CoreSpeed72MHz |  |

|----------------------------------------------------------------------------------------|--|

| Core Size 32-Bit Single-Core                                                           |  |

|                                                                                        |  |

| Speed 72MHz                                                                            |  |

|                                                                                        |  |

| Connectivity CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB              |  |

| Peripherals DMA, I <sup>2</sup> S, POR, PWM, WDT                                       |  |

| Number of I/O 51                                                                       |  |

| Program Memory Size 512KB (512K x 8)                                                   |  |

| Program Memory Type FLASH                                                              |  |

| EEPROM Size -                                                                          |  |

| RAM Size 64K x 8                                                                       |  |

| Voltage - Supply (Vcc/Vdd) 2V ~ 3.6V                                                   |  |

| Data ConvertersA/D 16x12b; D/A 1x12b                                                   |  |

| Oscillator Type Internal                                                               |  |

| Operating Temperature -40°C ~ 105°C (TA)                                               |  |

| Mounting Type Surface Mount                                                            |  |

| Package / Case 64-LQFP                                                                 |  |

| Supplier Device Package64-LQFP (10x10)                                                 |  |

| Purchase URL https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f302ret7tr   |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.8 General-purpose inputs/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions. All GPIOs are high current capable except for analog inputs.

The I/Os alternate function configuration can be locked if needed following a specific sequence in order to avoid spurious writing to the I/Os registers.

Fast I/O handling allows I/O toggling up to 36 MHz.

# 3.9 Direct memory access (DMA)

The flexible general-purpose DMA is able to manage memory-to-memory, peripheral-tomemory and memory-to-peripheral transfers. The DMA controller supports circular buffer management, avoiding the generation of interrupts when the controller reaches the end of the buffer.

Each of the 7 DMA channels is connected to dedicated hardware DMA requests, with software trigger support for each channel. Configuration is done by software and transfer sizes between source and destination are independent.

The DMA can be used with the main peripherals: SPI, I<sup>2</sup>C, USART, timers, DAC and ADC.

# 3.10 Interrupts and events

### 3.10.1 Nested vectored interrupt controller (NVIC)

The STM32F302x6/8 devices embed a nested vectored interrupt controller (NVIC) able to handle up to 60 maskable interrupt channels and 16 priority levels.

The NVIC benefits are the following:

- Closely coupled NVIC gives low latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Closely coupled NVIC core interface

- Allows early processing of interrupts

- Processing of late arriving higher priority interrupts

- Support for tail chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

The NVIC hardware block provides flexible interrupt management features with minimal interrupt latency.

# 3.11 Fast analog-to-digital converter (ADC)

An analog-to-digital converter, with selectable resolution between 12 and 6 bit, is embedded in the STM32F302x6/8 family devices. The ADC has up to 15 external channels performing conversions in single-shot or scan modes. Channels can be configured to be either singleended input or differential input. In scan mode, automatic conversion is performed on a selected group of analog inputs.

Additional logic functions embedded in the ADC interface allow:

- Simultaneous sample and hold

- Single-shunt phase current reading techniques.

The ADC can be served by the DMA controller.

Three analog watchdogs are available. The analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

The events generated by the general-purpose timers (TIMx) and the advanced-control timer (TIM1) can be internally connected to the ADC start trigger and injection trigger, respectively, to allow the application to synchronize A/D conversion and timers.

### 3.11.1 Temperature sensor

The temperature sensor (TS) generates a voltage  $\mathsf{V}_{\mathsf{SENSE}}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC1\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode.

# 3.11.2 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference ( $V_{REFINT}$ ) provides a stable (bandgap) voltage output for the ADC and Comparators.  $V_{REFINT}$  is internally connected to the ADC1\_IN18 input channel. The precise voltage of  $V_{REFINT}$  is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode.

## 3.11.3 V<sub>BAT</sub> battery voltage monitoring

This embedded hardware feature allows the application to measure the V<sub>BAT</sub> battery voltage using the internal ADC channel ADC1\_IN17. As the V<sub>BAT</sub> voltage may be higher than V<sub>DDA</sub>, and thus outside the ADC input range, the V<sub>BAT</sub> pin is internally connected to a bridge divider by 2. As a consequence, the converted digital value is half the V<sub>BAT</sub> voltage.

# 3.12 Digital-to-analog converter (DAC)

One 12-bit buffered DAC channel (DAC1\_OUT1) can be used to convert digital signals into analog voltage signal outputs. The chosen design structure is composed of integrated resistor strings and an amplifier in inverting configuration.

This digital interface supports the following features:

- One DAC output channel

- 8-bit or 12-bit monotonic output

- Left or right data alignment in 12-bit mode

- Synchronized update capability

- Noise-wave generation

- Triangular-wave generation

- DMA capability

- External triggers for conversion

# 3.13 Operational amplifier (OPAMP)

The STM32F302x6/8 devices embed one operational amplifier with external or internal follower routing and PGA capability (or even amplifier and filter capability with external components). When the operational amplifier is selected, an external ADC channel is used to enable output measurement.

The operational amplifier features:

- 8.2 MHz bandwidth

- 0.5 mA output capability

- Rail-to-rail input/output

- In PGA mode, the gain can be programmed to be 2, 4, 8 or 16.

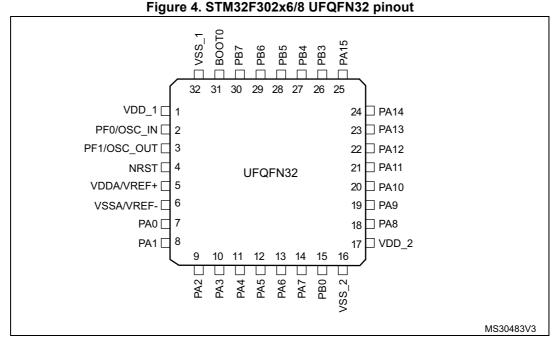

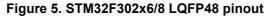

# 4 Pinouts and pin description

1. The above figure shows the package top view.

1. The above figure shows the package top view.

DocID025147 Rev 6

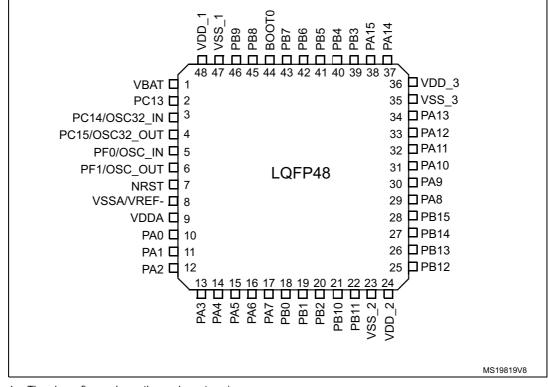

Figure 7. STM32F302x6/8 WLCSP49 ballout

1. The above figure shows the package top view.

2. NC: Not connected.

| 1 | S       |

|---|---------|

|   | õ       |

|   | 1       |

|   | <u></u> |

|   | õ       |

| D   |

|-----|

| č   |

| D   |

| )25 |

| 51  |

| 7   |

| Re  |

| Š   |

| o   |

|        | Table 12. STM32F302x6/8 pin definitions (continued)         Pin Number |        |        |                                    |          |               |       |                                                                                |                                      |  |  |  |  |

|--------|------------------------------------------------------------------------|--------|--------|------------------------------------|----------|---------------|-------|--------------------------------------------------------------------------------|--------------------------------------|--|--|--|--|

| UQFN32 | WLCSP49                                                                | LQFP48 | LQFP64 | Pin name<br>(function after reset) | Pin type | I/O structure | Notes | Alternate<br>functions                                                         | Additional<br>functions              |  |  |  |  |

| -      | -                                                                      | -      | 24     | PC4                                | I/O      | TT            | -     | EVENTOUT, TIM1_ETR,<br>USART1_TX                                               |                                      |  |  |  |  |

| -      | -                                                                      | -      | 25     | PC5                                | I/O      | TTa           | -     | EVENTOUT, TIM15_BKIN,<br>TSC_G3_IO1, USART1_RX                                 | OPAMP2_VINM                          |  |  |  |  |

| 15     | G5                                                                     | 18     | 26     | PB0                                | I/O      | TTa           | -     | TSC_G3_IO2, TIM1_CH2N,<br>EVENTOUT                                             | ADC1_IN11, COMP4_INP,<br>OPAMP2_VINP |  |  |  |  |

| -      | G4                                                                     | 19     | 27     | PB1                                | I/O      | TTa           | -     | TSC_G3_IO3, TIM1_CH3N,<br>COMP4_OUT, EVENTOUT                                  | ADC1_IN12                            |  |  |  |  |

| -      | G3                                                                     | 20     | 28     | PB2                                | I/O      | TTa           | -     | TSC_G3_IO4, EVENTOUT                                                           | COMP4_INM                            |  |  |  |  |

| -      | E3                                                                     | 21     | 29     | PB10                               | I/O      | TT            | -     | TIM2_CH3, TSC_SYNC,<br>USART3_TX, EVENTOUT                                     |                                      |  |  |  |  |

| -      | G2                                                                     | 22     | 30     | PB11                               | I/O      | TTa           | -     | TIM2_CH4, TSC_G6_IO1,<br>USART3_RX, EVENTOUT                                   | ADC1_IN14, COMP6_INP                 |  |  |  |  |

| 16     | D3                                                                     | 23     | 31     | VSS_2                              | S        | -             | -     | Digital                                                                        | ground                               |  |  |  |  |

| 17     | B2                                                                     | 24     | 32     | VDD_2                              | S        | -             | -     | Digital pov                                                                    | wer supply                           |  |  |  |  |

| -      | E2                                                                     | 25     | 33     | PB12                               | I/O      | TT            | -     | TSC_G6_IO2, I2C2_SMBAL,<br>SPI2_NSS/I2S2_WS, TIM1_BKIN,<br>USART3_CK, EVENTOUT |                                      |  |  |  |  |

| -      | G1                                                                     | 26     | 34     | PB13                               | I/O      | ТТа           | -     | TSC_G6_IO3, SPI2_SCK/I2S2_CK,<br>TIM1_CH1N, USART3_CTS,<br>EVENTOUT            | ADC1_IN13                            |  |  |  |  |

5

DocID025147 Rev 6

45/138

| r                     | 1                     |                                  |                      |                | Та                             | ble 14. A                        | Alternate                             | functior                             | ns for Po                        | rt B           | -              |      |               |      |      |              |

|-----------------------|-----------------------|----------------------------------|----------------------|----------------|--------------------------------|----------------------------------|---------------------------------------|--------------------------------------|----------------------------------|----------------|----------------|------|---------------|------|------|--------------|

|                       | AF0                   | AF1                              | AF2                  | AF3            | AF4                            | AF5                              | AF6                                   | AF7                                  | AF8                              | AF9            | AF10           | AF11 | AF12          | AF13 | AF14 | AF15         |

| Port &<br>pin<br>name | SYS_AF                | TIM2/TIM15/TIM16<br>/TIM17/EVENT | I2C3/TIM1/TIM2/TIM15 | I2C3/TIM15/TSC | I2C1/I2C2/TIM1/<br>TIM16/TIM17 | SPI2/I2S2/<br>SPI3/I2S3/Infrared | SPI2/I2S2/SPI3/<br>I2S3/TIM1/Infrared | USART1/USART2/USART3/<br>CAN/GPCOMP6 | I2C3/GPCOMP2<br>/GPCOMP4/GPCOMP6 | CAN/TIM1/TIM15 | TIM2/TIM17     | TIM1 | TIM1          |      | 1    | EVENT        |

| PB0                   | -                     | -                                | -                    | TSC<br>_G3_IO2 | -                              | -                                | TIM1<br>_CH2N                         | -                                    | -                                | -              | -              | -    | -             | -    | -    | EVENT<br>OUT |

| PB1                   | -                     | -                                | -                    | TSC<br>_G3_IO3 | -                              | -                                | TIM1<br>_CH3N                         | -                                    | COMP4_<br>OUT                    | -              | -              | -    | -             | -    | -    | EVENT<br>OUT |

| PB2                   |                       |                                  |                      | TSC<br>_G3_IO4 | -                              | -                                | -                                     | -                                    | -                                | -              | -              | -    | -             | -    | -    | EVENT<br>OUT |

| PB3                   | JTDO-<br>TRACE<br>SWO | TIM2<br>_CH2                     | -                    | TSC<br>_G5_IO1 | -                              | -                                | SPI3_SC<br>K/I2S3_<br>CK              | USART2<br>_TX                        | -                                | -              | -              | -    | -             | -    | -    | EVENT<br>OUT |

| PB4                   | JTRST                 | TIM16<br>_CH1                    | -                    | TSC<br>_G5_IO2 | -                              | -                                | SPI3_MI<br>SO/I2S3<br>_SD             | USART2<br>_RX                        | -                                | -              | TIM17<br>_BKIN | -    | -             | -    | -    | EVENT<br>OUT |

| PB5                   | -                     | TIM16<br>_BKIN                   | -                    | -              | I2C1<br>_SMBAI                 | -                                | SPI3<br>_MOSI/<br>I2S3ext_<br>SD      | USART2<br>_CK                        | I2C3<br>_SDA                     | -              | TIM17<br>_CH1  | -    | -             | -    | -    | EVENT<br>OUT |

| PB6                   | -                     | TIM16<br>_CH1N                   | -                    | TSC<br>_G5_IO3 | I2C1<br>_SCL                   | -                                | -                                     | USART1<br>_TX                        | -                                | -              | -              | -    | -             | -    | -    | EVENT<br>OUT |

| PB7                   | -                     | TIM17<br>_CH1N                   | -                    | TSC<br>_G5_IO4 | l2C1<br>_SDA                   | -                                | -                                     | USART1<br>_RX                        | -                                | -              | -              | -    | -             | -    | -    | EVENT<br>OUT |

| PB8                   | -                     | TIM16<br>_CH1                    | -                    | TSC<br>_SYNC   | I2C1<br>_SCL                   | -                                | -                                     | USART3<br>_RX                        | -                                | CAN<br>_RX     | -              | -    | TIM1<br>_BKIN | -    | -    | EVENT<br>OUT |

STM32F302x6 STM32F302x8

Pinouts and pin description

|   |                       |        |                                      | Table 1                  | 6. Alternate fund | ctions for Port D              | )                                    |                                           |                                              |

|---|-----------------------|--------|--------------------------------------|--------------------------|-------------------|--------------------------------|--------------------------------------|-------------------------------------------|----------------------------------------------|

| Ĩ |                       | AF0    | AF1                                  | AF2                      | AF3               | AF4                            | AF5                                  | AF6                                       | AF7                                          |

|   | Port &<br>pin<br>name | SYS_AF | TIM2/TIM15/<br>TIM16/TIM17/<br>EVENT | I2C3/TIM1/TIM2/<br>TIM15 | I2C3/TIM15/TSC    | I2C1/I2C2/TIM1/<br>TIM16/TIM17 | SPI2/I2S2/<br>SPI3/I2S3/<br>Infrared | SPI2/I2S2/SPI3/<br>I2S3/TIM1/<br>Infrared | USART1/<br>USART2/<br>USART3/CAN/<br>GPCOMP6 |

|   | PD2                   | -      | EVENTOUT                             | -                        | -                 | -                              | _                                    | -                                         | -                                            |

Table 17. Alternate functions for Port F

| Dout 9                | AF0 AF1 |                                      | AF2                      | AF3            | AF4                            | AF5                                  | AF6                                       | AF7                                      |  |

|-----------------------|---------|--------------------------------------|--------------------------|----------------|--------------------------------|--------------------------------------|-------------------------------------------|------------------------------------------|--|

| Port &<br>pin<br>name | SYS_AF  | TIM2/TIM15/<br>TIM16/TIM17/<br>EVENT | I2C3/TIM1/TIM2/<br>TIM15 | I2C3/TIM15/TSC | I2C1/I2C2/TIM1/<br>TIM16/TIM17 | SPI2/I2S2/<br>SPI3/I2S3/<br>Infrared | SPI2/I2S2/SPI3/<br>I2S3/TIM1/<br>Infrared | USART1/USAR<br>T2/USART3/<br>CAN/GPCOMP6 |  |

| PF0                   | -       | -                                    | -                        | -              | I2C2_SDA                       | SPI2_NSS/<br>I2S2_WS                 | TIM1_CH3N                                 | -                                        |  |

| PF1                   | -       | -                                    | -                        | -              | I2C2_SCL                       | SPI2_SCK/<br>I2S2_CK                 | -                                         | -                                        |  |

DocID025147 Rev 6

STM32F302x6 STM32F302x8

Pinouts and pin description

48/138

57

# 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 19: Voltage characteristics*, *Table 20: Current characteristics*, and *Table 21: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                            | Ratings                                                                    | Min                                    | Max                   | Unit |

|-----------------------------------|----------------------------------------------------------------------------|----------------------------------------|-----------------------|------|

| V <sub>DD</sub> -V <sub>SS</sub>  | External main supply voltage (including $V_{DDA,}$ $V_{BAT}$ and $V_{DD})$ | -0.3                                   | 4.0                   | V    |

| V <sub>DD</sub> –V <sub>DDA</sub> | Allowed voltage difference for $V_{DD} > V_{DDA}$                          | -                                      | 0.4                   | V    |

|                                   | Input voltage on FT and FTf pins                                           | V <sub>SS</sub> –0.3                   | V <sub>DD</sub> + 4.0 |      |

|                                   | Input voltage on TTa and TT pins                                           | V <sub>SS</sub> –0.3                   |                       |      |

| V <sub>IN</sub> <sup>(2)</sup>    | Input voltage on any other pin                                             | V <sub>SS</sub> -0.3                   | 4.0                   | V    |

|                                   | Input voltage on Boot0 pin                                                 | 0                                      | 9                     |      |

| $ \Delta V_{DDx} $                | Variations between different V <sub>DD</sub> power pins                    | -                                      | 50                    | mV   |

| V <sub>SSX</sub> –V <sub>SS</sub> | Variations between all the different ground pins <sup>(3)</sup>            | -                                      | 50                    | 111V |

| V <sub>ESD(HBM)</sub>             | Electrostatic discharge voltage (human body model)                         | see Section 6.3.<br>sensitivity charac |                       | V    |

| Table 19. Voltag | ge characteristics <sup>(1)</sup> |

|------------------|-----------------------------------|

|------------------|-----------------------------------|

All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range. The following relationship must be respected between V<sub>DDA</sub> and V<sub>DD</sub>: V<sub>DDA</sub> must power on before or at the same time as V<sub>DD</sub> in the power up sequence. V<sub>DDA</sub> must be greater than or equal to V<sub>DD</sub>.

2. V<sub>IN</sub> maximum must always be respected. Refer to *Table 20: Current characteristics* for the maximum allowed injected current values.

3. Include V<sub>REF-</sub> pin.

|                  |                      |                   |                   |     | V <sub>DDA</sub>   | = 2.4 V             |                    |     | V <sub>DDA</sub>   | = 3.6 \ | /                  |                |    |    |    |

|------------------|----------------------|-------------------|-------------------|-----|--------------------|---------------------|--------------------|-----|--------------------|---------|--------------------|----------------|----|----|----|

| Symbol           | Parameter            | Conditions<br>(1) | f <sub>HCLK</sub> | Тур | М                  | ax @ T <sub>A</sub> | (2)                | Тур | м                  | Unit    |                    |                |    |    |    |

|                  |                      |                   |                   | тур | 25 °C              | 85 °C               | 105 °C             | קני | 25 °C              | 85 °C   | 105 °C             |                |    |    |    |

|                  |                      |                   | 72 MHz            | 231 | 254 <sup>(3)</sup> | 266                 | 271 <sup>(3)</sup> | 251 | 274 <sup>(3)</sup> | 294     | 300 <sup>(3)</sup> |                |    |    |    |

|                  |                      | 64 MHz            | 203               | 226 | 239                | 243                 | 222                | 245 | 261                | 266     |                    |                |    |    |    |

|                  | Supply current in    | in                | 48 MHz            | 153 | 174                | 182                 | 186                | 165 | 185                | 198     | 203                | -<br>-<br>- μΑ |    |    |    |

|                  |                      |                   | 32 MHz            | 105 | 124                | 131                 | 133                | 114 | 132                | 141     | 143                |                |    |    |    |

|                  |                      |                   | 24 MHz            | 82  | 98                 | 104                 | 105                | 89  | 106                | 111     | 113                |                |    |    |    |

|                  | Run mode,<br>code    |                   | 8 MHz             | 3.1 | 4.1                | 4.1                 | 5.1                | 3.6 | 4.7                | 5.2     | 5.5                |                |    |    |    |

| I <sub>DDA</sub> | executing            |                   | 1 MHz             | 3.1 | 4.1                | 4.1                 | 5.1                | 3.6 | 4.7                | 5.2     | 5.5                |                |    |    |    |

|                  | from Flash<br>or RAM |                   | 64 MHz            | 270 | 294                | 307                 | 312                | 296 | 322                | 338     | 343                |                |    |    |    |

|                  | UI RAIVI             |                   | 48 MHz            | 219 | 242                | 253                 | 257                | 240 | 263                | 276     | 281                |                |    |    |    |

|                  |                      | HSI clock         | 32 MHz            | 171 | 192                | 201                 | 203                | 188 | 209                | 219     | 222                | 1              |    |    |    |

|                  |                      |                   | 24 MHz            | 148 | 169                | 175                 | 177                | 163 | 182                | 190     | 193                |                |    |    |    |

|                  |                      |                   |                   |     |                    |                     | 8 MHz              | 69  | 84                 | 87      | 87                 | 79             | 92 | 94 | 96 |

Table 29. Typical and maximum current consumption from the  $V_{\text{DDA}}$  supply

1. Current consumption from the  $V_{DDA}$  supply is independent of whether the peripherals are on or off. Furthermore when the PLL is off,  $I_{DDA}$  is independent from the frequency.

2. Guaranteed by characterization results.

3. Data based on characterization results and tested in production with code executing from RAM.

|                 |                                   | Conditions                                       |       | Тур ( | @V <sub>DD</sub> ( | (V <sub>DD</sub> =\ |       |       |                           |                           |                            |      |  |

|-----------------|-----------------------------------|--------------------------------------------------|-------|-------|--------------------|---------------------|-------|-------|---------------------------|---------------------------|----------------------------|------|--|

| Symbol          | Parameter                         |                                                  | 2.0 V | 2.4 V | 2.7 V              | 3.0 V               | 3.3 V | 3.6 V | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |  |

|                 | Supply<br>current in<br>Stop mode | Regulator in run mode,<br>all oscillators OFF    | 16.92 | 17.09 | 17.16              | 17.27               | 17.39 | 17.50 | 29.7                      | 359.1                     | 564.5                      | _    |  |

|                 |                                   | Regulator in low-power mode, all oscillators OFF | 5.29  | 5.46  | 5.55               | 5.70                | 5.73  | 5.95  | 16.40                     | 267.1                     | 407.4                      |      |  |

| I <sub>DD</sub> | Supply                            | LSI ON and IWDG ON                               | 0.80  | 0.93  | 1.11               | 1.19                | 1.31  | 1.41  | -                         | -                         | -                          | . I  |  |

| c<br>S          | current in<br>Standby<br>mode     | LSI OFF and IWDG OFF                             | 0.63  | 0.76  | 0.84               | 0.95                | 1.02  | 1.10  | 5.00                      | 6.30                      | 12.60                      |      |  |

### Table 30. Typical and maximum $V_{\text{DD}}$ consumption in Stop and Standby modes

1. Guaranteed by characterization results.

### **On-chip peripheral current consumption**

The MCU is placed under the following conditions:

- all I/O pins are in analog input configuration

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- ambient operating temperature at 25°C and  $V_{DD} = V_{DDA} = 3.3$  V.

| Davishand                  | Typical consumption <sup>(1)</sup> |        |

|----------------------------|------------------------------------|--------|

| Peripheral                 | I <sub>DD</sub>                    |        |

| BusMatrix <sup>(2)</sup>   | 11.3                               |        |

| DMA1                       | 6.7                                |        |

| CRC                        | 2.0                                |        |

| GPIOA                      | 8.5                                |        |

| GPIOB                      | 8.3                                |        |

| GPIOC                      | 8.6                                |        |

| GPIOD                      | 1.5                                |        |

| GPIOF                      | 1.0                                |        |

| TSC                        | 4.7                                |        |

| ADC1                       | 15.9                               |        |

| APB2-Bridge <sup>(3)</sup> | 2.7                                |        |

| SYSCFG                     | 3.2                                |        |

| TIM1                       | 27.6                               |        |

| USART1                     | 21.0                               |        |

| TIM15                      | 14.3                               |        |

| TIM16                      | 10.1                               |        |

| TIM17                      | 10.4                               | μA/MHz |

| APB1-Bridge <sup>(3)</sup> | 5.8                                |        |

| TIM2                       | 40.7                               |        |

| TIM6                       | 7.4                                |        |

| WWDG                       | 4.6                                |        |

| SPI2                       | 35.2                               |        |

| SPI3                       | 34.2                               |        |

| USART2                     | 13.9                               |        |

| USART3                     | 13.1                               |        |

| I2C1                       | 9.4                                |        |

| I2C2                       | 9.4                                |        |

| USB                        | 17.4                               |        |

| CAN                        | 28.8                               |        |

| PWR                        | 4.5                                |        |

| DAC                        | 8.3                                |        |

| I2C3                       | 10.5                               |        |

### Table 36. Peripheral current consumption

The power consumption of the analog part (I<sub>DDA</sub>) of peripherals such as ADC, DAC, Comparators, OpAmp etc. is not included. Refer to the tables of characteristics in the subsequent sections.

2. BusMatrix is automatically active when at least one master is ON (CPU or DMA1).

3. The APBx bridge is automatically active when at least one peripheral is ON on the same bus.

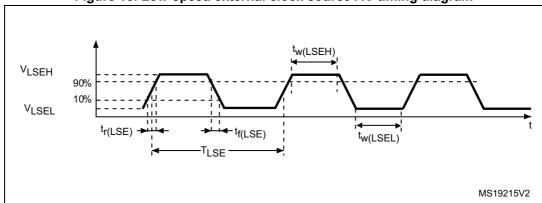

### Low-speed external user clock generated from an external source

In bypass mode the LSE oscillator is switched off and the input pin is a standard GPIO. The external clock signal has to respect the I/O characteristics in *Section 6.3.14*. However, the recommended clock input waveform is shown in *Figure 15*

| Symbol                                       | Parameter                                           | Conditions | Min                | Тур    | Max                | Unit |

|----------------------------------------------|-----------------------------------------------------|------------|--------------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                         | User External clock source frequency <sup>(1)</sup> |            | -                  | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                            | OSC32_IN input pin high level voltage               |            | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | V    |

| V <sub>LSEL</sub>                            | OSC32_IN input pin low level voltage                |            |                    | -      | 0.3V <sub>DD</sub> | v    |

| t <sub>w(LSEH)</sub><br>t <sub>w(LSEL)</sub> | OSC32_IN high or low time <sup>(1)</sup>            |            | 450                | -      | -                  | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub>   | OSC32_IN rise or fall time <sup>(1)</sup>           |            | -                  | -      | 50                 | 10   |

Table 40. Low-speed external user clock characteristics

1. Guaranteed by design.

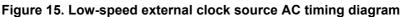

For C<sub>L1</sub> and C<sub>L2</sub>, it is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (Typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 16*). C<sub>L1</sub> and C<sub>L2</sub> are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of C<sub>L1</sub> and C<sub>L2</sub>. PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing C<sub>L1</sub> and C<sub>L2</sub>.

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

1. R<sub>EXT</sub> value depends on the crystal characteristics.

### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on design simulation results obtained with typical external components specified in *Table 42*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol              | Parameter                      | Conditions <sup>(1)</sup>                        | Min <sup>(2)</sup> | Тур | Max <sup>(2)</sup> | Unit  |  |

|---------------------|--------------------------------|--------------------------------------------------|--------------------|-----|--------------------|-------|--|

| I <sub>DD</sub>     | LSE current consumption        | LSEDRV[1:0]=00<br>lower driving capability       | -                  | 0.5 | 0.9                | .9    |  |

|                     |                                | LSEDRV[1:0]=10<br>medium low driving capability  | -                  | -   | 1                  |       |  |

|                     |                                | LSEDRV[1:0]=01<br>medium high driving capability | -                  | -   | 1.3                | μA    |  |

|                     |                                | LSEDRV[1:0]=11<br>higher driving capability      | -                  | -   | 1.6                |       |  |

| 9 <sub>m</sub>      | Oscillator<br>transconductance | LSEDRV[1:0]=00<br>lower driving capability       | 5                  | ;   |                    |       |  |

|                     |                                | LSEDRV[1:0]=10 8 -                               |                    | -   | -                  | μA/V  |  |

|                     |                                | LSEDRV[1:0]=01<br>medium high driving capability | 15                 | -   | -                  | - µAV |  |

|                     |                                | LSEDRV[1:0]=11<br>higher driving capability      | 25                 | -   | -                  |       |  |

| $t_{SU(LSE)}^{(3)}$ | Startup time                   | V <sub>DD</sub> is stabilized                    | -                  | 2   | -                  | S     |  |

### Table 42. LSE oscillator characteristics (f<sub>LSE</sub> = 32.768 kHz)

1. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

2. Guaranteed by design.

3. t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer.

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

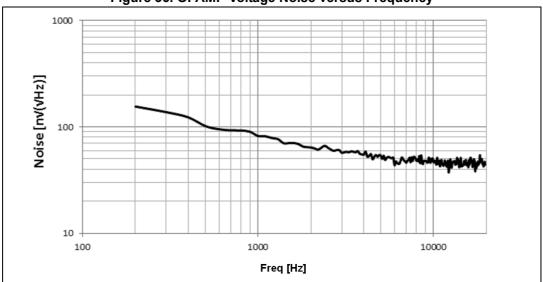

Figure 36. OPAMP Voltage Noise versus Frequency

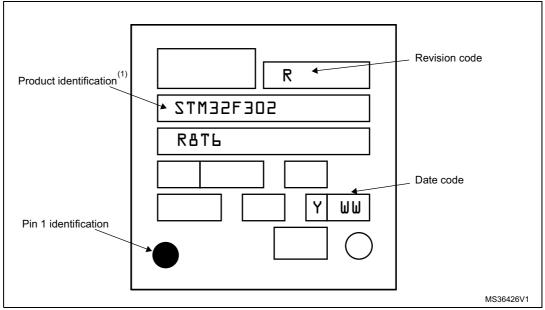

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

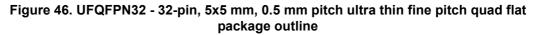

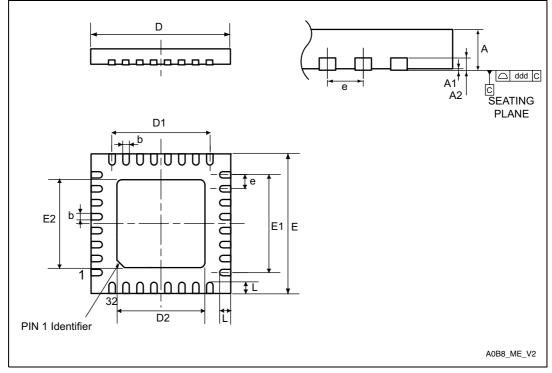

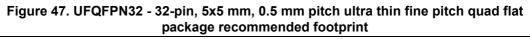

# 7.4 UFQFPN32 package information

1. Drawing is not to scale.

- 2. All leads/pads should also be soldered to the PCB to improve the lead/pad solder joint life.

- 3. There is an exposed die pad on the underside of the UFQFPN package. This pad is used for the device ground and must be connected. It is referred to as pin 0 in Table: Pin definitions.

|        | millimeters                             |       |       | inches <sup>(1)</sup> |        |        |  |

|--------|-----------------------------------------|-------|-------|-----------------------|--------|--------|--|

| Symbol | 111111111111111111111111111111111111111 |       |       |                       |        |        |  |

|        | Min                                     | Тур   | Мах   | Min                   | Тур    | Max    |  |

| A      | 0.500                                   | 0.550 | 0.600 | 0.0197                | 0.0217 | 0.0236 |  |

| A1     | 0.000                                   | 0.020 | 0.050 | 0.0000                | 0.0008 | 0.0020 |  |

| A3     | -                                       | 0.152 | -     | -                     | 0.0060 | -      |  |

| b      | 0.180                                   | 0.230 | 0.280 | 0.0071                | 0.0091 | 0.0110 |  |

| D      | 4.900                                   | 5.000 | 5.100 | 0.1929                | 0.1969 | 0.2008 |  |

| D1     | 3.400                                   | 3.500 | 3.600 | 0.1339                | 0.1378 | 0.1417 |  |

| D2     | 3.400                                   | 3.500 | 3.600 | 0.1339                | 0.1378 | 0.1417 |  |

| E      | 4.900                                   | 5.000 | 5.100 | 0.1929                | 0.1969 | 0.2008 |  |

| E1     | 3.400                                   | 3.500 | 3.600 | 0.1339                | 0.1378 | 0.1417 |  |

| E2     | 3.400                                   | 3.500 | 3.600 | 0.1339                | 0.1378 | 0.1417 |  |

| е      | -                                       | 0.500 | -     | -                     | 0.0197 | -      |  |

| L      | 0.300                                   | 0.400 | 0.500 | 0.0118                | 0.0157 | 0.0197 |  |

| ddd    | -                                       | -     | 0.080 | -                     | -      | 0.0031 |  |

# Table 81. UFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch ultra thin fine pitch quad flatpackage mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved

DocID025147 Rev 6