Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Obsolete                                                                            |

|----------------------------|-------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                  |

| Speed                      | 50MHz                                                                               |

| Connectivity               | I²C, IrDA, LINbus, SPI, UART/USART                                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                               |

| Number of I/O              | 24                                                                                  |

| Program Memory Size        | 32KB (32K x 8)                                                                      |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | 4K x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                         |

| Data Converters            | A/D 8x12b                                                                           |

| Oscillator Type            | Internal                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 32-WFQFN Exposed Pad                                                                |

| Supplier Device Package    | -                                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/m058zbn |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Up to two sets of UART device

- Programmable baud-rate generator

- Buffered receiver and transmitter, each with 15 bytes FIFO

- Optional flow control function (CTS and RTS)

- Supports IrDA(SIR) function

- Supports RS485 function

- Supports LIN function

- SPI

- Up to two sets of SPI device.

- Supports master/slave mode

- Full duplex synchronous serial data transfer

- Provide 3 wire function

- Variable length of transfer data from 1 to 32 bits

- MSB or LSB first data transfer

- Rx latching data can be either at rising edge or at falling edge of serial clock

- Tx sending data can be either at rising edge or at falling edge of serial clock

- Supports Byte suspend mode in 32-bit transmission

- I<sup>2</sup>C

- Supports master/slave mode

- Bidirectional data transfer between masters and slaves

- Multi-master bus (no central master).

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus

- Serial clock synchronization allows devices with different bit rates to communicate via one serial bus.

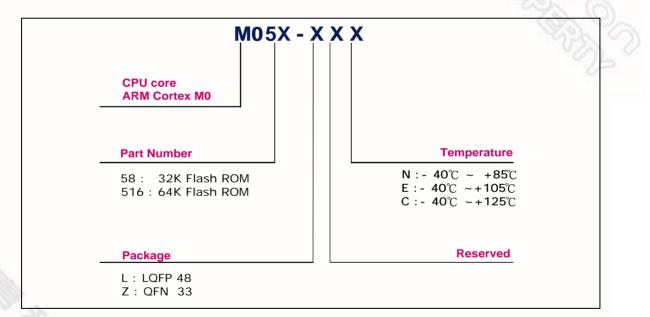

### **4 SELECTION TABLE**

NuMicro M051<sup>™</sup> Series Selection Guide

| Part number | APROM | RAM | Data<br>Flash | LDROM | I/O | Timer    | Con<br>UART | nectivi<br>SPI | ity<br>I2C | СОМР | PWM | ADC      | EBI | ISP<br>ICP | Package |

|-------------|-------|-----|---------------|-------|-----|----------|-------------|----------------|------------|------|-----|----------|-----|------------|---------|

|             |       |     |               |       |     |          | UARI        | 381            | 120        |      |     |          |     |            |         |

| M058LBN     | 32KB  | 4KB | 4KB           | 4KB   | 40  | 4x32-bit | 2           | 2              | 1          | 2    | 8   | 8X12-bit | v   | v          | LQFP48  |

| M058ZBN     | 32KB  | 4KB | 4KB           | 4KB   | 24  | 4x32-bit | 2           | 1              | 1          | 2    | 5   | 8X12-bit |     | v          | QFN33   |

| M0516LBN    | 64KB  | 4KB | 4KB           | 4KB   | 40  | 4x32-bit | 2           | 2              | 1          | 2    | 8   | 8X12-bit | v   | v          | LQFP48  |

| M0516ZBN    | 64KB  | 4KB | 4KB           | 4KB   | 24  | 4x32-bit | 2           | 1              | 1          | 2    | 5   | 8X12-bit |     | v          | QFN33   |

Table 4-1 NuMicro™ M051 Series Product Selection Guide

Figure 4-1 NuMicro<sup>™</sup> Naming Rule

Publication Release Date: Mar. 19, 2012 Revision V1.01

- 14 -

| Pin n | umber  | Symbol | Altern              | ate Funct | ion  | Type <sup>[1]</sup> | Description                                                                                                                                        |

|-------|--------|--------|---------------------|-----------|------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| QFN33 | LQFP48 | Symbol | 1                   | 2         | 3    | Type                | Description                                                                                                                                        |

| 16    | 23     | P2.4   | PWM4 <sup>[2]</sup> | AD12      |      | D,<br>I/O           | The CPO1 pin is the output of Comparator1.                                                                                                         |

| 17    | 25     | P2.5   | PWM5 <sup>[2]</sup> | AD13      |      | D,<br>I/O           | AP OF                                                                                                                                              |

| 18    | 26     | P2.6   | PWM6 <sup>[2]</sup> | AD14      | CPO1 | D,<br>I/O           | E. C.                                                                                                                                              |

| NC    | 27     | P2.7   | PWM7 <sup>[2]</sup> | AD15      |      | D,<br>I/O           | 20.                                                                                                                                                |

| 3     | 5      | P3.0   | RXD <sup>[2]</sup>  |           | CPN1 | I/O                 | <b>PORT3:</b> Port 3 is an 8-bit four mode output pin and two mode input. Its multifunction pins are                                               |

| 5     | 7      | P3.1   | TXD <sup>[2]</sup>  |           | CPP1 | I/O                 | for RXD, TXD, INTO, INT1, T0, T1, WR,                                                                                                              |

| 6     | 8      | P3.2   | INT0                | STADC     | TOEX | I/O                 | and RD.<br>The RXD/TXD pins are for UART0 function                                                                                                 |

| NC    | 9      | P3.3   | INT1                | MCLK      | T1EX | I/O                 | used.<br>The SDA/SCK pins are for I <sup>2</sup> C function used.<br>MCLK: EBI clock output pin.                                                   |

| 7     | 10     | P3.4   | T0                  | SDA       |      | I/O                 | CKO: HCLK clock output                                                                                                                             |

| 8     | 11     | P3.5   | T1                  | SCL       |      | I/O                 | The STADC pin is for ADC external trigger input.                                                                                                   |

| 9     | 13     | P3.6   | WR                  | ско       | CPO0 | I/O                 | The CPN1/CPP1 pins are for Comparator1 negative/positive inputs.<br>The CPO0 pin is the output of Comparator0.                                     |

| NC    | 14     | P3.7   | RD                  |           |      | I/O                 | The T0/T1 pins are for Timer0/1 external even<br>counter input.<br>The T0EX/T1EX pins are for external<br>capture/reset trigger input of Timer0/1. |

| NC    | 24     | P4.0   | PWM0 <sup>[2]</sup> |           | T2EX | I/O                 | <b>PORT4:</b> Port 4 is an 8-bit four mode output pin and two mode input. Its multifunction pins are                                               |

| NC    | 36     | P4.1   | PWM1 <sup>[2]</sup> |           | T3EX | I/O                 | for /CS, ALE, ICE_CLK and ICE_DAT.                                                                                                                 |

| NC    | 48     | P4.2   | PWM2 <sup>[2]</sup> |           |      | I/O                 | CS for EBI (External Bus Interface) used.<br>ALE (Address Latch Enable) is used to enable                                                          |

| NC    | 12     | P4.3   | PWM3 <sup>[2]</sup> |           |      | I/O                 | the address latch that separates the address from the data on Port 0 and Port 2.                                                                   |

### **6 FUNCTIONAL DESCRIPTION**

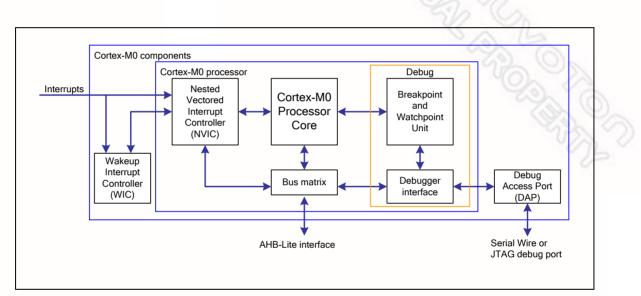

### 6.1 ARM® Cortex<sup>™</sup>-M0 Core

The Cortex<sup>™</sup>-M0 processor is a configurable, multistage, 32-bit RISC processor. It has an AMBA AHB-Lite interface and includes an NVIC component. It also has optional hardware debug functionality. The processor can execute Thumb code and is compatible with other Cortex-M profile processor. The profile supports two modes -Thread and Handler modes. Handler mode is entered as a result of an exception. An exception return can only be issued in Handler mode. Thread mode is entered on Reset, and can be entered as a result of an exception return. Figure 6-1 shows the functional controller of processor.

Figure 6-1 Functional Block Diagram

The implemented device provides:

### A low gate count processor the features:

- The ARMv6-M Thumb<sup>®</sup> instruction set.

- Thumb-2 technology.

- ARMv6-M compliant 24-bit SysTick timer.

- A 32-bit hardware multiplier.

- The system interface supports little-endian data accesses.

- The ability to have deterministic, fixed-latency, interrupt handling.

Publication Release Date: Mar. 19, 2012

- 21 -

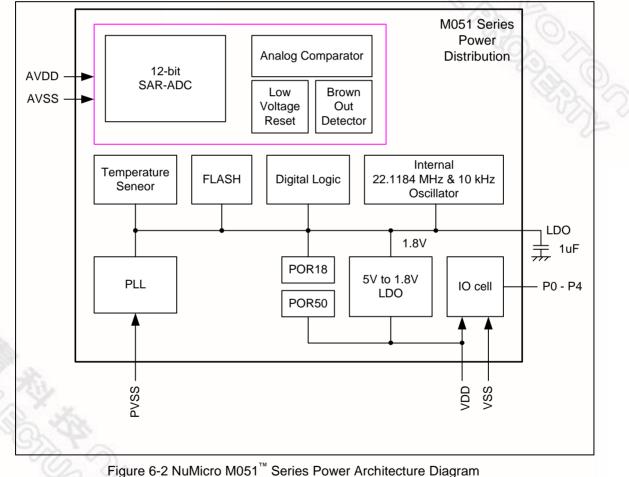

#### 6.2.3 System Power Architecture

In this device, the power architecture is divided into three segments.

- Analog power from AV<sub>DD</sub> and AV<sub>SS</sub> provides the power for analog module operation.

- Digital power from  $V_{DD}$  and  $V_{SS}$  supplies the power to the internal regulator which provides a fixed 1.8V power for digital operation and I/O pins.

The outputs of internal voltage regulator, which is LDO, require an external capacitor which should be located close to the corresponding pin. The Figure 6-2 shows the power architecture of this device.

Publication Release Date: Mar. 19, 2012 Revision V1.01

- 24 -

| M052/54/58/                       | ′516                                                                        | -        |                                      |                            |           |

|-----------------------------------|-----------------------------------------------------------------------------|----------|--------------------------------------|----------------------------|-----------|

| 4 GB                              | OxFFFF_FFF                                                                  |          |                                      |                            |           |

| Reserved                          | 1                                                                           |          | System Control                       |                            |           |

|                                   | 0xE000_F000                                                                 | -        | System Timer Control                 | 0xE000_E000                | SCS_BA    |

| System Control                    | 0xE000_EFFF                                                                 |          |                                      |                            |           |

| System control                    | 0xE000_E000                                                                 | <b>▲</b> |                                      |                            |           |

|                                   | 0xE000_E00F                                                                 |          |                                      |                            |           |

| Reserved                          | I                                                                           |          |                                      |                            |           |

|                                   | 0x6002_0000                                                                 |          |                                      |                            |           |

| EBI                               | 0x6001_FFFF                                                                 |          |                                      |                            |           |

| LDI                               | 0x6000_0000                                                                 |          |                                      |                            |           |

|                                   | 0x5FFF_FFF                                                                  |          |                                      |                            |           |

| Reserved                          | 1                                                                           |          |                                      |                            |           |

|                                   | 0x5020_0000                                                                 |          | AHB peripherals                      |                            |           |

| АНВ                               | 0x501F_FFFF                                                                 |          | EBI Control                          | 0x5001_0000                | EBI_CTL_I |

| АПЬ                               | 0x5000_0000                                                                 |          | FMC                                  | 0x5000_C000                | FLASH_BA  |

|                                   | 0x4FFF_FFFF                                                                 |          | GPIO Control                         | 0x5000_4000                | GPIO_BA   |

| Deserved                          |                                                                             |          | Interrupt Multiplexer Control        | 0x5000_0300                | INT_BA    |

| Reserved                          |                                                                             |          | Clock Control                        | 0x5000_0200                | CLK_BA    |

|                                   | 0x4020_0000                                                                 |          | System Global Control                | 0x5000_0000                | GCR_BA    |

|                                   | 0x401F_FFFF                                                                 |          | •                                    | •                          |           |

| АРВ                               | I                                                                           |          |                                      |                            |           |

| 1 GB                              | 0x4000_0000                                                                 | _        |                                      |                            |           |

|                                   | 0x3FFF_FFF                                                                  |          |                                      |                            |           |

| Reserved                          |                                                                             |          | APB peripherals                      |                            |           |

|                                   |                                                                             |          | UART1 Control                        | 0x4015_0000                | UART1_BA  |

|                                   | 0x2000_1000                                                                 |          | PWM4/5/6/7 Control                   | 0x4014_0000                | PWMB_BA   |

|                                   | 0x2000_0FFF                                                                 |          | Timer2/Timer3 Control                | 0x4011_0000                | TMR23_B/  |

| 4 KB SRAM                         |                                                                             |          | ADC Control                          | 0x400E_0000                | ADC_BA    |

| (M052/M054/M058/M                 | 10516)                                                                      |          | COMP control                         | 0x400D_0000                | ACMP_BA   |

|                                   |                                                                             | Ľ        | UARTO Control                        | 0x4005_0000                | UARTO_B   |

|                                   | 0x2000_0000                                                                 | -        | PWM0/1/2/3 Control                   | 0x4004_0000                | PWMA_BA   |

| 0.5 GB                            |                                                                             |          | SPI1 Control                         | 0x4003_4000                | SPI1_BA   |

| 0.5 GB                            | 0x1FFF_FFF                                                                  |          |                                      | 0,4002,0000                | SPI0_BA   |

| 0.5 GB                            |                                                                             |          | SPI0 Control                         | 0x4003_0000                |           |

|                                   | 0x1FFF_FFFF                                                                 |          | I2C Control                          | 0x4002_0000                | I2C_BA    |

|                                   |                                                                             |          |                                      |                            | TMR01_BA  |

|                                   | 0x1FFF_FFF                                                                  | -        | I2C Control                          | 0x4002_0000                |           |

| Reserved                          | 0x1FFF_FFF<br> <br>0x0001_0000<br>(M0516) 0x0000_FFFF                       | -        | I2C Control<br>Timer0/Timer1 Control | 0x4002_0000<br>0x4001_0000 | TMR01_BA  |

| Reserved<br>64 KB on-chip Flash ( | 0x1FFF_FFF<br> <br>0x0001_0000<br>(M0516) 0x0000_FFFF<br>(M058) 0x0000_7FFF |          | I2C Control<br>Timer0/Timer1 Control | 0x4002_0000<br>0x4001_0000 | TMR01_BA  |

### 6.2.5 Whole System Memory Mapping Table

### 6.2.6 System Timer (SysTick)

The Cortex-M0 includes an integrated system timer, SysTick. SysTick provides a simple, 24-bit

Publication Release Date: Mar. 19, 2012 Revision V1.01

- 27 -

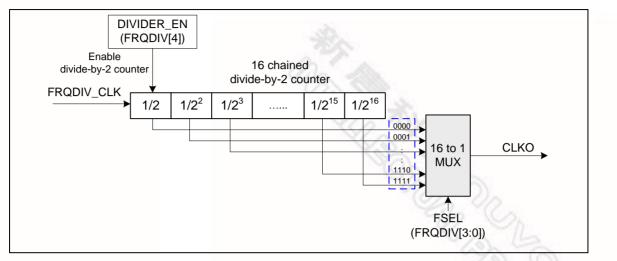

Figure 6-9 Block Diagram of Frequency Divider

Figure 6-12 Quasi-bidirectional I/O Mode

#### 6.5.2 Features

The I<sup>2</sup>C bus uses two wires (SDA and SCL) to transfer information between devices connected to the bus. The main features of the bus are:

- Support Master and Slave mode

- Bidirectional data transfer between masters and slaves

- Multi-master bus (no central master)

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus

- Serial clock synchronization allows devices with different bit rates to communicate via one serial bus

- Serial clock synchronization can be used as a handshake mechanism to suspend and resume serial transfer

- Built-in a 14-bit time-out counter will request the I<sup>2</sup>C interrupt if the I<sup>2</sup>C bus hangs up and timer-out counter overflows.

- External pull-up are needed for high output

- Programmable clocks allow versatile rate control

- Supports 7-bit addressing mode

- I<sup>2</sup>C-bus controllers support multiple address recognition (Four slave address with mask option)

### 6.6 **PWM Generator and Capture Timer**

#### 6.6.1 Overview

NuMicro M051<sup>™</sup> series has 2 sets of PWM group supports 4 sets of PWM Generators which can be configured as 8 independent PWM outputs, PWM0~PWM7, or as 4 complementary PWM pairs, (PWM0, PWM1), (PWM2, PWM3), (PWM4, PWM5) and (PWM6, PWM7) with 4 programmable dead-zone generators.

Each PWM Generator has one 8-bit prescaler, one clock divider with 5 divided frequencies (1, 1/2, 1/4, 1/8, 1/16), two PWM Timers including two clock selectors, two 16-bit PWM downcounters for PWM period control, two 16-bit comparators for PWM duty control and one deadzone generator. The 4 sets of PWM Generators provide eight independent PWM interrupt flags which are set by hardware when the corresponding PWM period down counter reaches zero. Each PWM interrupt source with its corresponding enable bit can cause CPU to request PWM interrupt. The PWM generators can be configured as one-shot mode to produce only one PWM cycle signal or auto-reload mode to output PWM waveform continuously.

When PCR.DZEN01 is set, PWM0 and PWM1 perform complementary PWM paired function; the paired PWM timing, period, duty and dead-time are determined by PWM0 timer and Dead-zone generator 0. Similarly, the complementary PWM pairs of (PWM2, PWM3), (PWM4, PWM5) and (PWM6, PWM7) are controlled by PWM2, PWM4 and PWM6 timers and Dead-zone generator 2, 4 and 6, respectively. Refer to figures bellowed for the architecture of PWM Timers.

When the 16-bit period down counter reaches zero, the interrupt request is generated. If PWMtimer is set as auto-reload mode, when the down counter reaches zero, it is reloaded with PWM Counter Register (CNRx) automatically then start decreasing, repeatedly. If the PWM-timer is set as one-shot mode, the down counter will stop and generate one interrupt request when it reaches zero.

The value of PWM counter comparator is used for pulse high width modulation. The counter control logic changes the output to high level when down-counter value matches the value of compare register.

The alternate feature of the PWM-timer is digital input Capture function. If Capture function is enabled the PWM output pin is switched as capture input mode. The Capture0 and PWM0 share one timer which is included in PWM 0; and the Capture1 and PWM1 share PWM1 timer, and etc. Therefore user must setup the PWM-timer before enable Capture feature. After capture feature is enabled, the capture always latched PWM-counter to Capture Rising Latch Register (CRLR) when input channel has a rising transition and latched PWM-counter to Capture Falling Latch Register (CFLR) when input channel has a falling transition. Capture channel 0 interrupt is programmable by setting CCR0.CRL\_IE0[1] (Rising latch Interrupt enable) and CCR0.CFL IE0[2]] (Falling latch Interrupt enable) to decide the condition of interrupt occur. Capture channel 1 has the same feature by setting CCR0.CRL IE1[17] and CCR0.CFL IE1[18]. And capture channel 0 to channel 3 on each group have the same feature by setting the corresponding control bits in CCR0 and CCR2. For each group, whenever Capture issues Interrupt 0/1/2/3, the PWM counter 0/1/2/3 will be reload at this moment.

The maximum captured frequency that PWM can capture is confined by the capture interrupt latency. When capture interrupt occurred, software will do at least three steps, they are: Read

### 6.7 Serial Peripheral Interface (SPI)

#### 6.7.1 Overview

The Serial Peripheral Interface (SPI) is a synchronous serial data communication protocol which operates in full duplex mode. Devices communicate in master/slave mode with 4-wire bi-direction interface. NuMicro M051<sup>™</sup> series contains up to two sets of SPI controller performing a serial-to-parallel conversion on data received from a peripheral device, and a parallel-to-serial conversion on data transmitted to a peripheral device. Each set of SPI controller can be set as a master, it also can be configured as a slave device controlled by an off-chip master device. This controller supports a variable serial clock for special application.

### 6.7.2 Features

- Up to two sets of SPI controller

- Support master or slave mode operation

- Configurable bit length up to 32-bit of a transfer word and configurable word numbers up to 2 of a transaction, so the maximum bit length is 64-bit for each data transfer

- Provide burst mode operation, transmit/receive can be transferred up to two times word transaction in one transfer

- Support MSB or LSB first transfer

- Support byte reorder function

- Support byte or word suspend mode

- Support two programmable serial clock frequencies in master mode

- Support three wire, no slave select signal, bi-direction interface

- The SPI clock rate can be configured to equal the system clock rate

Publication Release Date: Mar. 19, 2012 Revision V1.01

- 44 -

### 6.9 Watchdog Timer (WDT)

#### 6.9.1 Overview

The purpose of Watchdog Timer is to perform a system reset when system runs into an unknown state. This prevents system from hanging for an infinite period of time. Besides, this Watchdog Timer supports another function to wakeup chip from power down mode. The watchdog timer includes an 18-bit free running counter with programmable time-out intervals. Table 6-2 show the watchdog timeout interval selection and Figure 6.9-1 shows the timing of watchdog interrupt signal and reset signal.

Setting WTE (WDTCR [7]) enables the watchdog timer and the WDT counter starts counting up. When the counter reaches the selected time-out interval, Watchdog timer interrupt flag WTIF will be set immediately to request a WDT interrupt if the watchdog timer interrupt enable bit WTIE is set, in the meanwhile, a specified delay time (1024 \* T<sub>WDT</sub>) follows the time-out event. User must set WTR (WDTCR [0]) (Watchdog timer reset) high to reset the 18-bit WDT counter to avoid chip from Watchdog timer reset before the delay time expires. WTR bit is cleared automatically by hardware after WDT counter is reset. There are eight time-out intervals with specific delay time which are selected by Watchdog timer interval select bits WTIS (WDTCR [10:8]). If the WDT counter has not been cleared after the specific delay time expires, the watchdog timer will set Watchdog Timer Reset Flag (WTRF) high and reset chip. This reset will last 63 WDT clocks (T<sub>RST</sub>) then chip restarts executing program from reset vector (0x0000 0000). WTRF will not be cleared by Watchdog reset. User may poll WTFR by software to recognize the reset source. WDT also provides wakeup function. When chip is powered down and the Watchdog Timer Wake-up Function Enable bit (WDTR[4]) is set, if the WDT counter reaches the specific time interval defined by WTIS (WDTCR [10:8]), the chip is waken up from power down state. First example, if WTIS is set as 000, the specific time interval for chip to wake up from power down state is 2<sup>4</sup> \*  $T_{WDT}$ . When power down command is set by software, then, chip enters power down state. After  $2^4 * T_{WDT}$  time is elapsed, chip is waken up from power down state. Second example, if WTIS (WDTCR [10:8]) is set as 111, the specific time interval for chip to wake up from power down state is  $2^{18} * T_{WDT}$ . If power down command is set by software, then, chip enters power down state. After  $2^{18} * T_{WDT}$  time is elapsed, chip is waken up from power down state. Notice if WTRE (WDTCR [1]) is set to 1, after chip is waken up, software should chip the Watchdog Timer counter by setting WTR(WDTCR [0]) to 1 as soon as possible. Otherwise, if the Watchdog Timer counter is not cleared by setting WTR (WDTCR [0]) to 1 before time starting from waking up to software clearing Watchdog Timer counter is over 1024 \*  $T_{WDT}$ , the chip is reset by Watchdog Timer.

| WTIS | Timeout Interval Selection         | Interrupt Period        | WTR Timeout Interval (WDT_CLK=                |

|------|------------------------------------|-------------------------|-----------------------------------------------|

|      |                                    |                         | MIN. T <sub>WTR</sub> ~ MAX. T <sub>WTR</sub> |

| 000  | 2 <sup>4</sup> * T <sub>WDT</sub>  | 1024 * T <sub>WDT</sub> | 1.6 ms ~ 104 ms                               |

| 001  | 2 <sup>6</sup> * T <sub>WDT</sub>  | 1024 * T <sub>WDT</sub> | 6.4 ms ~ 108.8 ms                             |

| 010  | 2 <sup>8</sup> * T <sub>WDT</sub>  | 1024 * T <sub>WDT</sub> | 25.6 ms ~ 128 ms                              |

| 011  | 2 <sup>10</sup> * T <sub>WDT</sub> | 1024 * T <sub>WDT</sub> | 102.4 ms ~ 204.8 ms                           |

| 100  | 2 <sup>12</sup> * T <sub>WDT</sub> | 1024 * T <sub>WDT</sub> | 409.6 ms ~ 512 ms                             |

| 101  | 2 <sup>14</sup> * T <sub>WDT</sub> | 1024 * T <sub>WDT</sub> | 1.6384 s ~ 1.7408 s                           |

|      | 0, 1                               |                         | Publication Release Date: Mar                 |

|      |                                    | - 46 -                  | Revis                                         |

|           | System clo  | ock = 22.1184MHz                      |        |

|-----------|-------------|---------------------------------------|--------|

| Baud rate | Mode0       | Mode1                                 | Mode2  |

| 921600    | Not support | A=0,B=11                              | A=22   |

| 460800    | A=1         | A=1,B=15<br>A=2,B=11                  | A=46   |

| 230400    | A=4         | A=4,B=15<br>A=6,B=11                  | A=94   |

| 115200    | A=10        | A=10,B=15<br>A=14,B=11                | A=190  |

| 57600     | A=22        | A=22,B=15<br>A=30,B=11                | A=382  |

| 38400     | A=34        | A=62,B=8<br>A=46,B=11<br>A=34,B=15    | A=574  |

| 19200     | A=70        | A=126,B=8<br>A=94,B=11<br>A=70,B=15   | A=1150 |

| 9600      | A=142       | A=254,B=8<br>A=190,B=11<br>A=142,B=15 | A=2302 |

| 4800      | A=286       | A=510,B=8<br>A=382,B=11<br>A=286,B=15 | A=4606 |

Table 6-4 UART Baud Rate Setting Table

The UART0 and UART1 controllers support auto-flow control function that uses two low-level signals, /CTS (clear-to-send) and /RTS (request-to-send), to control the flow of data transfer between the UART and external devices (ex: Modem). When auto-flow is enabled, the UART is not allowed to receive data until the UART asserts /RTS to external device. When the number of bytes in the RX FIFO equals the value of RTS\_TRI\_LEV (UA\_FCR [19:16]), the /RTS is deasserted. The UART sends data out when UART controller detects /CTS is asserted from external device. If the valid asserted /CTS is not detected, the UART controller will not send data out.

The UART controllers also provides Serial IrDA (SIR, Serial Infrared) function (User must set UA\_FUN\_SEL [1:0] = '10' to enable IrDA function). The SIR specification defines a short-range infrared asynchronous serial transmission mode with one start bit, 8 data bits, and 1 stop bit. The maximum data rate is 115.2 Kbps (half duplex). The IrDA SIR block contains an IrDA SIR Protocol encoder/decoder. The IrDA SIR protocol is half-duplex only. So it cannot transmit and receive data at the same time. The IrDA SIR physical layer specifies a minimum 10ms transfer delay between transmission and reception. This delay feature must be implemented by software.

Publication Release Date: Mar. 19, 2012 Revision V1.01

- 49 -

# ηυνοΤοη

### 8 ELECTRICAL CHARACTERISTICS

### 8.1 Absolute Maximum Ratings

| SYMBOL                                    | PARAMETER                        | MIN                  | МАХ                  | UNIT |

|-------------------------------------------|----------------------------------|----------------------|----------------------|------|

| DC Power Supply                           | V <sub>DD</sub> –V <sub>SS</sub> | -0.3                 | +7.0                 | V    |

| Input Voltage                             | VIN                              | V <sub>SS</sub> -0.3 | V <sub>DD</sub> +0.3 | V    |

| Oscillator Frequency                      | 1/t <sub>CLCL</sub>              | 4                    | 24                   | MHz  |

| Operating Temperature                     | TA                               | -40                  | +85                  | °C   |

| Storage Temperature                       | TST                              | -55                  | +150                 | °C   |

| Maximum Current into $V_{DD}$             |                                  | -                    | 120                  | mA   |

| Maximum Current out of $V_{SS}$           |                                  |                      | 120                  | mA   |

| Maximum Current sunk by a I/O pin         |                                  |                      | 35                   | mA   |

| Maximum Current sourced by a I/O pin      |                                  |                      | 35                   | mA   |

| Maximum Current sunk by total I/O pins    |                                  |                      | 100                  | mA   |

| Maximum Current sourced by total I/O pins |                                  |                      | 100                  | mA   |

Note: Exposure to conditions beyond those listed under absolute maximum ratings may adversely affects the lift and reliability of the device.

### 8.3 AC Electrical Characteristics

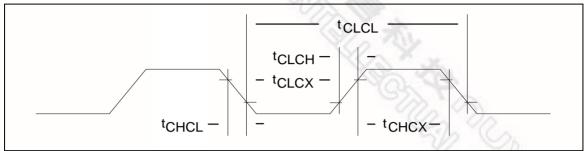

### 8.3.1 External Crystal

Note: Duty cycle is 50%.

| PARAMETER       | SYMBOL            | MIN. | TYP. | MAX. | UNITS | CONDITION |

|-----------------|-------------------|------|------|------|-------|-----------|

| Clock High Time | t <sub>CHCX</sub> | 20   | -    | -    | nS    | NON CO    |

| Clock Low Time  | t <sub>CLCX</sub> | 20   | -    | -    | nS    | 0.97      |

| Clock Rise Time | t <sub>CLCH</sub> | -    | -    | 10   | nS    | 122       |

| Clock Fall Time | t <sub>CHCL</sub> | -    | -    | 10   | nS    | -0        |

### 8.3.2 External Oscillator

|       | RAMETER         | CONDITION                    | MIN. | TYP. | MAX. | UNIT |

|-------|-----------------|------------------------------|------|------|------|------|

| Input | clock frequency | External crystal             | 4    | 12   | 24   | MHz  |

| Te    | emperature      | -                            | -40  | -    | 85   | °C   |

|       | V <sub>DD</sub> | -                            | 2.5  | 5    | 5.5  | V    |

| Ope   | rating current  | 12 MHz@ V <sub>DD</sub> = 5V | -    | 1    | -    | mA   |

#### **Analog Characteristics** 8.4

#### 8.4.1 **Specification of 12-bit SARADC**

| 12               | Bit                            |

|------------------|--------------------------------|

| 26.0             |                                |

| Vin Un           | LSB                            |

|                  | LSB                            |

| +5               | LSB                            |

| -6               | G.                             |

| Guaranteed       | 505                            |

| 16               | MHz                            |

| -                | Clock                          |

| 760              | K SPS                          |

| -                | V                              |

| 5.5              | V                              |

| -                | mA                             |

| -                | mA                             |

| AV <sub>DD</sub> | V                              |

|                  | pF                             |

|                  | -<br>760<br>-<br>5.5<br>-<br>- |

| RAMETER        | MIN  | түр 🖉 | МАХ  | UNIT | NOTE                   |

|----------------|------|-------|------|------|------------------------|

| Input Voltage  | 2.5  | 5     | 5.5  | V    | $V_{DD}$ input voltage |

| Output Voltage | -10% | 1.8   | +10% | V    | LDO output voltage     |

| Temperature    | -40  | 25    | 85   | °C   | 2                      |

| С              | -    | 1u    | -    | E.   | Resr=10hm              |

### 8.4.2 Specification of LDO & Power management

Note:

1. It is recommended a 100nF bypass capacitor is connected between  $V_{DD}$  and the closest  $V_{SS}$  pin of the device.

2. For ensuring power stability, a 1uF or higher capacitor must be connected between LDO pin and the closest  $V_{SS}$  pin of the device.

| Quiescent current Vin>reset voltage | 34 | 1 | - | nA |

|-------------------------------------|----|---|---|----|

|-------------------------------------|----|---|---|----|

### 8.4.6 Specification of Temperature Sensor

| PARAMETER                     | CONDITIONS | MIN.  | TYP.  | MAX.  | UNIT  |

|-------------------------------|------------|-------|-------|-------|-------|

| Supply voltage <sup>[1]</sup> | - Ka       | 1.62  | 1.8   | 1.98  | V     |

| Temperature                   | X          | -40   |       | 85    | °C    |

| Gain                          |            | -1.72 | -1.76 | -1.80 | mV/°C |

| Offset                        | Temp=0 ℃   | 717   | 725   | 733   | mV    |

Note[1]: Internal operation voltage comes from LDO.

### 8.4.7 Specification of Comparator

| CONDITION                          | MIN. | TYP.                                                                                                                                             | MAX.                                                                                                                                                                                    | UNIT                                                                                                                                                                                                                                                  |

|------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -                                  | -40  | 25                                                                                                                                               | 85                                                                                                                                                                                      | °C                                                                                                                                                                                                                                                    |

| -                                  | 2.4  |                                                                                                                                                  | 5.5<br>80                                                                                                                                                                               | V<br>uA                                                                                                                                                                                                                                               |

| -                                  | -    |                                                                                                                                                  |                                                                                                                                                                                         |                                                                                                                                                                                                                                                       |

| -                                  |      | 10                                                                                                                                               | 20                                                                                                                                                                                      | mV                                                                                                                                                                                                                                                    |

| -                                  | 0.1  | -                                                                                                                                                | V <sub>DD</sub> -0.1                                                                                                                                                                    | V                                                                                                                                                                                                                                                     |

| -                                  | 0.1  | -                                                                                                                                                | V <sub>DD</sub> -0.1                                                                                                                                                                    | V                                                                                                                                                                                                                                                     |

| -                                  | -    | 70                                                                                                                                               | -                                                                                                                                                                                       | dB                                                                                                                                                                                                                                                    |

| @VCM=1.2 V and<br>VDIFF=0.1 V      | -    | 200                                                                                                                                              | -                                                                                                                                                                                       | ns                                                                                                                                                                                                                                                    |

| @VCM=0.2 V ~ V <sub>DD</sub> -0.2V | -    | ±10                                                                                                                                              | -                                                                                                                                                                                       | mV                                                                                                                                                                                                                                                    |

| @CINP=1.3 V<br>CINN=1.2 V          | -    | -                                                                                                                                                | 2                                                                                                                                                                                       | us                                                                                                                                                                                                                                                    |

|                                    |      |                                                                                                                                                  |                                                                                                                                                                                         |                                                                                                                                                                                                                                                       |

|                                    |      | - -40   - 2.4   - -   - -   - 0.1   - 0.1   - 0.1   - -   @VCM=1.2 V and<br>VDIFF=0.1 V -   @VCM=0.2 V ~ V <sub>DD</sub> -0.2V -   @CINP=1.3 V - | - -40 25   - 2.4 3   - - 40   - - 40   - - 40   - 0.1 -   - 0.1 -   - 0.1 -   - 0.1 -   - 0.1 -   @VCM=1.2 V and<br>VDIFF=0.1 V - 200   @VCM=0.2 V ~ V_DD -0.2V - ±10   @CINP=1.3 V - - | - -40 25 85   - 2.4 3 5.5   - - 40 80   - - 40 80   - - 40 80   - 0.1 - $V_{DD}$ -0.1   - 0.1 - $V_{DD}$ -0.1   - 0.1 - $V_{DD}$ -0.1   - - 0.1 -   @VCM=1.2 V and<br>VDIFF=0.1 V - 200 -   @VCM=0.2 V ~ V_{DD}-0.2V - $\pm 10$ -   @CINP=1.3 V - - 2 |

### 8.5 Flash DC Electrical Characteristics

| SYMBOL             | PARAMETER             | CONDITIONS | MIN.   | TYP. | MAX. | UNIT<br>cycles <sup>[1]</sup> |

|--------------------|-----------------------|------------|--------|------|------|-------------------------------|

| N <sub>endu</sub>  | Endurance             | No.        | 100000 |      |      |                               |

| T <sub>ret</sub>   | Retention time        | Temp=85 ℃  | 10     | 0    |      | year                          |

| T <sub>erase</sub> | Page erase time       |            | 19     | 20   | 21   | ms                            |

| T <sub>mess</sub>  | Mess erase time       |            | 30     | 40   | 50   | ms                            |

| T <sub>prog</sub>  | Program time          |            | 38     | 40   | 42   | us                            |

| V <sub>DD</sub>    | Supply voltage        |            | 1.62   | 1.8  | 1.98 | V <sup>[2]</sup>              |

| I <sub>dd1</sub>   | Read current          |            |        |      | 0.25 | mA                            |

| I <sub>dd2</sub>   | Program/Erase current |            |        |      | 7    | mA                            |

| I <sub>pd</sub>    | Power down current    |            |        | 1    | 20   | uA                            |

1. Number of program/erase cycles.

2. V<sub>DD</sub> is source from chip LDO output voltage.

3. Guaranteed by design, not test in production.

### **10 REVISION HISTORY**

| VERSION | DATE          | PAGE  | DESCRIPTION                                   |  |

|---------|---------------|-------|-----------------------------------------------|--|

| V1.0    | Oct 20, 2011  | -     | Initial issued                                |  |

| V1.01   | Mar. 19, 2012 | 8.3.4 | Updated the Center Frequency of 22Mhz RC spec |  |