Welcome to **E-XFL.COM**

Understanding <u>Embedded - DSP (Digital Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

# Applications of <u>Embedded - DSP (Digital Signal Processors)</u>

| Dataila                 |                                                                                |

|-------------------------|--------------------------------------------------------------------------------|

| Details                 |                                                                                |

| Product Status          | Obsolete                                                                       |

| Туре                    | SC3850 Dual Core                                                               |

| Interface               | Ethernet, I <sup>2</sup> C, PCI, RGMII, Serial RapidIO, SGMII, SPI, UART/USART |

| Clock Rate              | 1GHz                                                                           |

| Non-Volatile Memory     | ROM (96kB)                                                                     |

| On-Chip RAM             | 576kB                                                                          |

| Voltage - I/O           | 2.50V                                                                          |

| Voltage - Core          | 1.00V                                                                          |

| Operating Temperature   | -40°C ~ 105°C (TJ)                                                             |

| Mounting Type           | Surface Mount                                                                  |

| Package / Case          | 783-BBGA, FCBGA                                                                |

| Supplier Device Package | 783-FCPBGA (29x29)                                                             |

| Purchase URL            | https://www.e-xfl.com/product-detail/nxp-semiconductors/msc8152tvt1000b        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

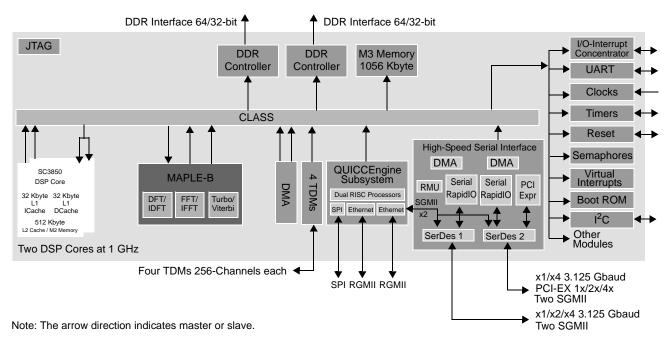

Figure 1. MSC8152 Block Diagram

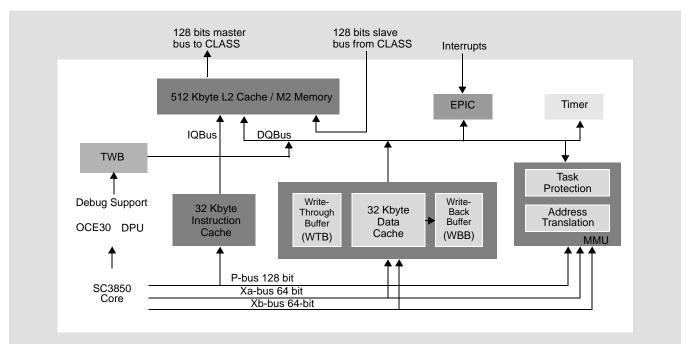

Figure 2. StarCore SC3850 DSP Subsystem Block Diagram

Table 1. Signal List by Ball Number (continued)

| Ball Number | Signal Name <sup>1,2</sup>   | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|------------------------------|------------------------|--------------------|

| G7          | M2CKE0                       | 0                      | GVDD2              |

| G8          | M2A11                        | 0                      | GVDD2              |

| G9          | M2A7                         | 0                      | GVDD2              |

| G10         | M2CK2                        | 0                      | GVDD2              |

| G11         | M2APAR_OUT                   | 0                      | GVDD2              |

| G12         | M2ODT1                       | 0                      | GVDD2              |

| G13         | M2APAR_IN                    | I                      | GVDD2              |

| G14         | M2DQ43                       | I/O                    | GVDD2              |

| G15         | M2DM5                        | 0                      | GVDD2              |

| G16         | M2DQ44                       | I/O                    | GVDD2              |

| G17         | M2DQ40                       | I/O                    | GVDD2              |

| G18         | M2DQ59                       | I/O                    | GVDD2              |

| G19         | M2DM7                        | 0                      | GVDD2              |

| G20         | M2DQ60                       | I/O                    | GVDD2              |

| G21         | Reserved                     | NC                     | _                  |

| G22         | Reserved                     | NC                     | _                  |

| G23         | SXPVSS1                      | Ground                 | N/A                |

| G24         | SXPVDD1                      | Power                  | N/A                |

| G25         | SR1_IMP_CAL_TX               | I                      | SXCVDD1            |

| G26         | SXCVSS1                      | Ground                 | N/A                |

| G27         | Reserved                     | NC                     | _                  |

| G28         | Reserved                     | NC                     | _                  |

| H1          | GVDD2                        | Power                  | N/A                |

| H2          | VSS                          | Ground                 | N/A                |

| H3          | M2DQ18                       | I/O                    | GVDD2              |

| H4          | GVDD2                        | Power                  | N/A                |

| H5          | VSS                          | Ground                 | N/A                |

| H6          | M2DQ20                       | I/O                    | GVDD2              |

| H7          | GVDD2                        | Power                  | N/A                |

| H8          | VSS                          | Ground                 | N/A                |

| H9          | M2A15                        | 0                      | GVDD2              |

| H10         | M2CK2                        | 0                      | GVDD2              |

| H11         | M2MDIC0                      | I/O                    | GVDD2              |

| H12         | M2VREF                       | I                      | GVDD2              |

| H13         | M2MDIC1                      | I/O                    | GVDD2              |

| H14         | M2DQ46                       | 1/0                    | GVDD2              |

| H15         | M2DQ47                       | I/O                    | GVDD2              |

| H16         | M2DQ45                       | I/O                    | GVDD2              |

| H17         | M2DQ41                       | I/O                    | GVDD2              |

| H18         | M2DQ62                       | I/O                    | GVDD2              |

| H19         | M2DQ63                       | 1/0                    | GVDD2              |

| H20         | M2DQ61                       | 1/0                    | GVDD2              |

| H21         | Reserved                     | NC                     |                    |

| H22         | Reserved                     | NC NC                  |                    |

| H23         | SR1_TXD3/SG2_TX <sup>4</sup> | 0                      | SXPVDD1            |

| H24         | SR1_TXD3/SG2_TX <sup>4</sup> | 0                      | SXPVDD1            |

Table 1. Signal List by Ball Number (continued)

| Ball Number | Signal Name <sup>1,2</sup>   | Pin Type <sup>10</sup> | Power Rail<br>Name |  |

|-------------|------------------------------|------------------------|--------------------|--|

| H25         | SXCVSS1                      | Ground                 | N/A                |  |

| H26         | SXCVDD1                      | Power                  | N/A                |  |

| H27         | SR1_RXD3/SG2_RX <sup>4</sup> | I                      | SXCVDD1            |  |

| H28         | SR1_RXD3/SG2_RX <sup>4</sup> | I                      | SXCVDD1            |  |

| J1          | M2DQS1                       | I/O                    | GVDD2              |  |

| J2          | M2DQS1                       | I/O                    | GVDD2              |  |

| J3          | M2DQ10                       | I/O                    | GVDD2              |  |

| J4          | M2DQ11                       | I/O                    | GVDD2              |  |

| J5          | M2DQ14                       | I/O                    | GVDD2              |  |

| J6          | M2DQ23                       | I/O                    | GVDD2              |  |

| J7          | M2ODT0                       | 0                      | GVDD2              |  |

| J8          | M2A12                        | 0                      | GVDD2              |  |

| J9          | M2A14                        | 0                      | GVDD2              |  |

| J10         | VSS                          | Ground                 | N/A                |  |

| J11         | GVDD2                        | Power                  | N/A                |  |

| J12         | VSS                          | Ground                 | N/A                |  |

| J13         | GVDD2                        | Power                  | N/A                |  |

| J14         | VSS                          | Ground                 | N/A                |  |

| J15         | GVDD2                        | Power                  | N/A                |  |

| J16         | VSS                          | Ground                 | N/A                |  |

| J17         | GVDD2                        | Power                  | N/A                |  |

| J18         | VSS                          | Ground                 | N/A                |  |

| J19         | GVDD2                        | Power                  | N/A                |  |

| J20         | Reserved                     | NC NC                  |                    |  |

| J21         | Reserved                     | NC NC                  | _                  |  |

| J22         | Reserved                     | NC NC                  | _                  |  |

| J23         | SXPVDD1                      | Power                  | N/A                |  |

| J24         | SXPVSS1                      | Ground                 | N/A                |  |

| J25         | SXCVDD1                      | Power                  | N/A                |  |

| J26         | SXCVSS1                      | Ground                 | N/A                |  |

| J27         | SXCVDD1                      | Power                  | N/A                |  |

| J28         | SXCVSS1                      | Ground                 | N/A                |  |

| K1          | VSS                          | Ground                 | N/A                |  |

| K2          | GVDD2                        | Power                  | N/A                |  |

| K3          | M2DM1                        | O                      | GVDD2              |  |

| K4          | VSS                          | Ground                 | N/A                |  |

| K5          | GVDD2                        | Power                  | N/A<br>N/A         |  |

| K6          | M2DQ0                        | I/O                    | GVDD2              |  |

|             |                              |                        |                    |  |

| K7          | VSS<br>GVDD2                 | Ground                 | N/A                |  |

| K8          |                              | Power                  | N/A                |  |

| K9          | M2DQ5                        | 1/0                    | GVDD2              |  |

| K10         | VSS                          | Ground                 | N/A                |  |

| K11         | VDD                          | Power                  | N/A                |  |

| K12         | VSS                          | Ground                 | N/A                |  |

| K13         | VDD                          | Power                  | N/A                |  |

Table 1. Signal List by Ball Number (continued)

| Ball Number | Signal Name <sup>1,2</sup>           | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|--------------------------------------|------------------------|--------------------|

| K15         | VDD                                  | Power                  | N/A                |

| K16         | VSS                                  | Ground                 | N/A                |

| K17         | VSS                                  | Ground                 | N/A                |

| K18         | VSS                                  | Ground                 | N/A                |

| K19         | VDD                                  | Power                  | N/A                |

| K20         | Reserved                             | NC                     | _                  |

| K21         | Reserved                             | NC                     | _                  |

| K22         | Reserved                             | NC                     | _                  |

| K23         | SXPVDD2                              | Power                  | N/A                |

| K24         | SXPVSS2                              | Ground                 | N/A                |

| K25         | SXCVDD2                              | Power                  | N/A                |

| K26         | SXCVSS2                              | Ground                 | N/A                |

| K27         | SXCVDD2                              | Power                  | N/A                |

| K28         | SXCVSS2                              | Ground                 | N/A                |

| L1          | M2DQ9                                | I/O                    | GVDD2              |

| L2          | M2DQ12                               | I/O                    | GVDD2              |

| L3          | M2DQ13                               | I/O                    | GVDD2              |

| L4          | M2DQS0                               | I/O                    | GVDD2              |

| L5          | M2DQS0                               | I/O                    | GVDD2              |

| L6          | M2DM0                                | 0                      | GVDD2              |

| L7          | M2DQ3                                | I/O                    | GVDD2              |

| L8          | M2DQ2                                | I/O                    | GVDD2              |

| L9          | M2DQ4                                | I/O                    | GVDD2              |

| L10         | VDD                                  | Power                  | N/A                |

| L11         | VSS                                  | Ground                 | N/A                |

| L12         | M3VDD                                | Power                  | N/A                |

| L13         | VSS                                  | Ground                 | N/A                |

| L14         | VSS                                  | Ground                 | N/A                |

| L15         | VSS                                  | Ground                 | N/A                |

| L16         | VSS                                  | Ground                 | N/A                |

| L17         | VSS                                  | Ground                 | N/A                |

| L18         | VDD                                  | Power                  | N/A                |

| L19         | VSS                                  | Ground                 | N/A                |

| L20         | Reserved                             | NC NC                  | _                  |

| L21         | Reserved                             | NC NC                  | _                  |

| L22         | Reserved                             | NC                     | _                  |

| L23         | SR2_TXD3/PE_TXD3/SG2_TX <sup>4</sup> | 0                      | SXPVDD2            |

| L24         | SR2_TXD3/PE_TXD3/SG2_TX <sup>4</sup> | 0                      | SXPVDD2            |

| L25         | SXCVSS2                              | Ground                 | N/A                |

| L26         | SXCVDD2                              | Power                  | N/A                |

| L27         | SR2_RXD3/PE_RXD3/SG2_RX <sup>4</sup> | I                      | SXCVDD2            |

| L28         | SR2_RXD3/PE_RXD3/SG2_RX <sup>4</sup> | <u>'</u>               | SXCVDD2            |

| M1          | M2DQ8                                | 1/0                    | GVDD2              |

| M2          | VSS                                  | Ground                 | N/A                |

| M3          | GVDD2                                | Power                  | N/A                |

| M4          | M2DQ15                               | I/O                    | GVDD2              |

Table 1. Signal List by Ball Number (continued)

| Ball Number | Signal Name <sup>1,2</sup> | Pin Type <sup>10</sup> | Power Rail<br>Name |  |

|-------------|----------------------------|------------------------|--------------------|--|

| M5          | M2DQ1                      | I/O                    | GVDD2              |  |

| M6          | VSS                        | Ground                 | N/.A               |  |

| M7          | GVDD2                      | Power                  | N/A                |  |

| M8          | M2DQ7                      | I/O                    | GVDD2              |  |

| M9          | M2DQ6                      | I/O                    | GVDD2              |  |

| M10         | VSS                        | Ground                 | N/A                |  |

| M11         | VDD                        | Power                  | N/A                |  |

| M12         | VSS                        | Ground                 | N/A                |  |

| M13         | VDD                        | Power                  | N/A                |  |

| M14         | VSS                        | Ground                 | N/A                |  |

| M15         | VSS                        | Ground                 | N/A                |  |

| M16         | VSS                        | Ground                 | N/A                |  |

| M17         | VSS                        | Ground                 | N/A                |  |

| M18         | VSS                        | Ground                 | N/A                |  |

| M19         | VDD                        | Power                  | N/A                |  |

| M20         | Reserved                   | NC                     | _                  |  |

| M21         | Reserved                   | NC                     |                    |  |

| M22         | Reserved                   | NC                     | _                  |  |

| M23         | SXPVSS2                    | Ground                 | N/A                |  |

| M24         | SXPVDD2                    | Power                  | N/A                |  |

| M25         | SR2_IMP_CAL_TX             | 1                      | SXCVDD2            |  |

| M26         | SXCVSS2                    | Ground                 | N/A                |  |

| M27         | Reserved                   | NC                     |                    |  |

| M28         | Reserved                   | NC                     | _                  |  |

| N1          | VSS                        | Ground                 | N/A                |  |

| N2          | TRST <sup>7</sup>          | I                      | QVDD               |  |

| N3          | PORESET <sup>7</sup>       | · ·                    | QVDD               |  |

| N4          | VSS                        | Ground                 | N/A                |  |

| N5          | TMS <sup>7</sup>           | I                      | QVDD               |  |

| N6          | CLKOUT                     | 0                      | QVDD               |  |

| N7          | VSS                        | Ground                 | N/A                |  |

| N8          | VSS                        | Ground                 | N/A                |  |

| N9          | VSS                        | Ground                 | N/A                |  |

| N10         | VDD                        | Power                  | N/A<br>N/A         |  |

| N11         | VSS                        | Ground                 | N/A<br>N/A         |  |

| N12         | M3VDD                      | Power                  | N/A<br>N/A         |  |

| N13         | VSS                        | Ground                 | N/A                |  |

| N14         | VSS                        |                        | t                  |  |

|             |                            | Ground<br>Ground       | N/A                |  |

| N15         | VSS                        |                        | N/A                |  |

| N16         | VDD                        | Power                  | N/A                |  |

| N17         | VSS                        | Ground                 | N/A                |  |

| N18         | VDD                        | Power                  | N/A                |  |

| N19         | VSS                        | Ground                 | N/A                |  |

| N20         | Reserved                   | NC P                   | —<br>N/A           |  |

| N21         | SXPVDD2                    | Power                  | N/A                |  |

Table 1. Signal List by Ball Number (continued)

| Ball Number | Signal Name <sup>1,2</sup>           | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|--------------------------------------|------------------------|--------------------|

| N23         | SR2_TXD2/PE_TXD2/SG1_TX <sup>4</sup> | 0                      | SXPVDD2            |

| N24         | SR2_TXD2/PE_TXD2/SG1_TX <sup>4</sup> | 0                      | SXPVDD2            |

| N25         | SXCVDD2                              | Power                  | N/A                |

| N26         | SXCVSS2                              | Ground                 | N/A                |

| N27         | SR2_RXD2/PE_RXD2/SG1_RX <sup>4</sup> | 1                      | SXCVDD2            |

| N28         | SR2_RXD2/PE_RXD2/SG1_RX <sup>4</sup> | 1                      | SXCVDD2            |

| P1          | CLKIN                                | I                      | QVDD               |

| P2          | EE0                                  | I                      | QVDD               |

| P3          | QVDD                                 | Power                  | N/A                |

| P4          | VSS                                  | Ground                 | N/A                |

| P5          | STOP_BS                              | I                      | QVDD               |

| P6          | QVDD                                 | Power                  | N/A                |

| P7          | VSS                                  | Ground                 | N/A                |

| P8          | PLL0_AVDD <sup>9</sup>               | Power                  | VDD                |

| P9          | PLL2_AVDD <sup>9</sup>               | Power                  | VDD                |

| P10         | VSS                                  | Ground                 | N/A                |

| P11         | VDD                                  | Power                  | N/A                |

| P12         | VSS                                  | Ground                 | N/A                |

| P13         | VDD                                  | Power                  | N/A                |

| P14         | VSS                                  | Ground                 | N/A                |

| P15         | MVDD                                 | Power                  | N/A                |

| P16         | VSS                                  | Ground                 | N/A                |

| P17         | MVDD                                 | Power                  | N/A                |

| P18         | VSS                                  | Ground                 | N/A                |

| P19         | VDD                                  | Power                  | N/A                |

| P20         | Reserved                             | NC                     | _                  |

| P21         | Reserved                             | NC                     | _                  |

| P22         | Reserved                             | NC                     | _                  |

| P23         | SXPVDD2                              | Power                  | N/A                |

| P24         | SXPVSS2                              | Ground                 | N/A                |

| P25         | SR2_PLL_AGND <sup>9</sup>            | Ground                 | SXCVSS2            |

| P26         | SR2_PLL_AVDD <sup>9</sup>            | Power                  | SXCVDD2            |

| P27         | SXCVSS2                              | Ground                 | N/A                |

| P28         | SXCVDD2                              | Power                  | N/A                |

| R1          | VSS                                  | Ground                 | N/A                |

| R2          | NMI                                  | I                      | QVDD               |

| R3          | NMI_OUT <sup>6</sup>                 | 0                      | QVDD               |

| R4          | HRESET <sup>6,7</sup>                | I/O                    | QVDD               |

| R5          | INT_OUT <sup>6</sup>                 | 0                      | QVDD               |

| R6          | EE1                                  | 0                      | QVDD               |

| R7          | VSS                                  | Ground                 | N/A                |

| R8          | PLL1_AVDD <sup>9</sup>               | Power                  | VDD                |

| R9          | VSS                                  | Ground                 | N/A                |

| R10         | VDD                                  | Power                  | N/A                |

| R11         | VSS                                  | Non-user               | N/A                |

| R12         | VDD                                  | Power                  | N/A                |

Table 1. Signal List by Ball Number (continued)

| Ball Number | Signal Name <sup>1,2</sup>          | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|-------------------------------------|------------------------|--------------------|

| AB1         | M1DQS2                              | I/O                    | GVDD1              |

| AB2         | M1DQS2                              | I/O                    | GVDD1              |

| AB3         | M1DQ19                              | I/O                    | GVDD1              |

| AB4         | M1DM2                               | 0                      | GVDD1              |

| AB5         | M1DQ21                              | I/O                    | GVDD1              |

| AB6         | M1DQ22                              | I/O                    | GVDD1              |

| AB7         | M1CKE0                              | 0                      | GVDD1              |

| AB8         | M1A11                               | 0                      | GVDD1              |

| AB9         | M1A7                                | 0                      | GVDD1              |

| AB10        | M1CK2                               | 0                      | GVDD1              |

| AB11        | M1APAR_OUT                          | 0                      | GVDD1              |

| AB12        | M1ODT1                              | 0                      | GVDD1              |

| AB13        | M1APAR_IN                           | I                      | GVDD1              |

| AB14        | M1DQ43                              | I/O                    | GVDD1              |

| AB15        | M1DM5                               | 0                      | GVDD1              |

| AB16        | M1DQ44                              | I/O                    | GVDD1              |

| AB17        | M1DQ40                              | I/O                    | GVDD1              |

| AB18        | M1DQ59                              | I/O                    | GVDD1              |

| AB19        | M1DM7                               | 0                      | GVDD1              |

| AB20        | M1DQ60                              | I/O                    | GVDD1              |

| AB21        | VSS                                 | Ground                 | N/A                |

| AB22        | GPIO31/I2C_SDA <sup>5,8</sup>       | I/O                    | NVDD               |

| AB23        | GPIO27/TMR4/RCW_SRC0 <sup>5,8</sup> | I/O                    | NVDD               |

| AB24        | GPIO25/TMR2/RCW_SRC1 <sup>5,8</sup> | I/O                    | NVDD               |

| AB25        | GPIO24/TMR1/RCW_SRC2 <sup>5,8</sup> | I/O                    | NVDD               |

| AB26        | GPIO10/IRQ10/RC10 <sup>5,8</sup>    | I/O                    | NVDD               |

| AB27        | GPIO5/IRQ5/RC5 <sup>5,8</sup>       | I/O                    | NVDD               |

| AB28        | GPIO0/IRQ0/RC0 <sup>5,8</sup>       | I/O                    | NVDD               |

| AC1         | VSS                                 | Ground                 | N/A                |

| AC2         | GVDD1                               | Power                  | N/A                |

| AC3         | M1DQ16                              | I/O                    | GVDD1              |

| AC4         | VSS                                 | Ground                 | N/A                |

| AC5         | GVDD1                               | Power                  | N/A                |

| AC6         | M1DQ17                              | I/O                    | GVDD1              |

| AC7         | VSS                                 | Ground                 | N/A                |

| AC8         | GVDD1                               | Power                  | N/A                |

| AC9         | M1BA2                               | 0                      | GVDD1              |

| AC10        | VSS                                 | Ground                 | N/A                |

| AC11        | GVDD1                               | Power                  | N/A                |

| AC12        | M1A4                                | 0                      | GVDD1              |

| AC13        | VSS                                 | Ground                 | N/A                |

| AC14        | GVDD1                               | Power                  | N/A                |

| AC15        | M1DQ42                              | I/O                    | GVDD1              |

| AC16        | VSS                                 | Ground                 | N/A                |

| AC17        | GVDD1                               | Power                  | N/A                |

| AC18        | M1DQ58                              | I/O                    | GVDD1              |

27

#### 2.5.1.2 DDR3 (1.5V) SDRAM DC Electrical Characteristics

Table 7 provides the recommended operating conditions for the DDR SDRAM controller when interfacing to DDR3 SDRAM.

At recommended operating conditions (see Table 3) with  $V_{DDDDR} = 1.5 \text{ V}$ .

Table 7. DDR3 SDRAM Interface DC Electrical Characteristics

| Parameter/Condition   | Symbol            | Min                       | Max                       | Unit | Notes |

|-----------------------|-------------------|---------------------------|---------------------------|------|-------|

| I/O reference voltage | MV <sub>REF</sub> | 0.49 × V <sub>DDDDR</sub> | 0.51 × V <sub>DDDDR</sub> | V    | 2,3,4 |

| Input high voltage    | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.100 | $V_{DDDDR}$               | V    | 5     |

| Input low voltage     | V <sub>IL</sub>   | GND                       | MV <sub>REF</sub> - 0.100 | V    | 5     |

| I/O leakage current   | I <sub>OZ</sub>   | -50                       | 50                        | μА   | 6     |

Notes:

- V<sub>DDDDR</sub> is expected to be within 50 mV of the DRAM V<sub>DD</sub> at all times. The DRAM and memory controller can use the same or different sources.

- $MV_{REF}$  is expected to be equal to  $0.5 \times V_{DDDDR}$ , and to track  $V_{DDDDR}$  DC variations as measured at the receiver. Peak-to-peak noise on  $MV_{REF}$  may not exceed ±1% of the DC value.

- 3. V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal to  $MV_{REF}$  with a minimum value of  $MV_{REF} - 0.4$  and a maximum value of  $MV_{REF} + 0.04$  V.  $V_{TT}$  should track variations in the DC-level of MV<sub>REF</sub>.

- The voltage regulator for MV  $_{\mbox{\scriptsize REF}}$  must be  $\underline{\mbox{able}}$  to supply up to 250  $\mu\mbox{\scriptsize A}.$

- Input capacitance load for DQ, DQS, and DQS signals are available in the IBIS models.

- Output leakage is measured with all outputs are disabled,  $0 \text{ V} \leq V_{OUT} \leq V_{DDDDR}$ .

#### 2.5.1.3 DDR2/DDR3 SDRAM Capacitance

Table 8 provides the DDR controller interface capacitance for DDR2 and DDR3 memory.

At recommended operating conditions (see Table 3) with V<sub>DDDDR</sub> = 1.8 V for DDR2 memory or V<sub>DDDDR</sub> = 1.5 V for Note: DDR3 memory.

Table 8. DDR2/DDR3 SDRAM Capacitance

| Parameter                                               | Symbol           | Min | Max | Unit |

|---------------------------------------------------------|------------------|-----|-----|------|

| I/O capacitance: DQ, DQS, DQS                           | C <sub>IO</sub>  | 6   | 8   | pF   |

| Delta I/O capacitance: DQ, DQS, DQS                     | C <sub>DIO</sub> | _   | 0.5 | pF   |

| Note: Guaranteed by FAB process and micro-construction. |                  |     |     |      |

#### Table 14. Serial RapidIO Receiver DC Specifications

| Parameter                      | Symbol          | Min | Typical | Max  | Units | Notes |

|--------------------------------|-----------------|-----|---------|------|-------|-------|

| Differential input voltage     | V <sub>IN</sub> | 200 | _       | 1600 | mVp-p | 1     |

| Notes: 1. Measured at receiver |                 |     |         |      |       |       |

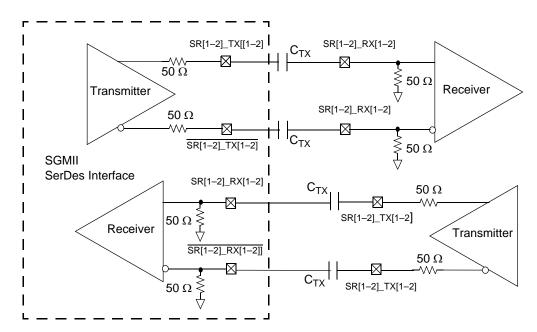

### 2.5.3.4 DC-Level Requirements for SGMII Configurations

**Note:** Specifications are valid at the recommended operating conditions listed in Table 3

Table 15 describes the SGMII SerDes transmitter AC-coupled DC electrical characteristics. Transmitter DC characteristics are measured at the transmitter outputs  $(SR[1-2]_TX[n])$  and  $\overline{SR[1-2]_TX[n]}$  as shown in Figure 10.

Table 15. SGMII DC Transmitter Electrical Characteristics

| Parameter                               | Symbol          | Min                                       | Тур | Max                                       | Unit | Notes  |

|-----------------------------------------|-----------------|-------------------------------------------|-----|-------------------------------------------|------|--------|

| Output high voltage                     | V <sub>OH</sub> | _                                         | _   | $XV_{DD\_SRDS-Typ}/2 +  V_{OD} _{-max}/2$ | mV   | 1      |

| Output low voltage                      | V <sub>OL</sub> | $XV_{DD\_SRDS-Typ}/2 -  V_{OD} _{-max}/2$ | _   | _                                         | mV   | 1      |

| Output differential                     | V <sub>OD</sub> | 323                                       | 500 | 725                                       | mV   | 2,3,4  |

| voltage (XV <sub>DD-Typ</sub> at 1.0 V) |                 | 296                                       | 459 | 665                                       |      | 2,3,5  |

| 1.0 V)                                  |                 | 269                                       | 417 | 604                                       |      | 2,3,6  |

|                                         |                 | 243                                       | 376 | 545                                       |      | 2,3,7  |

|                                         |                 | 215                                       | 333 | 483                                       |      | 2,3,8  |

|                                         |                 | 189                                       | 292 | 424                                       |      | 2,3,9  |

|                                         |                 | 162                                       | 250 | 362                                       |      | 2,3,10 |

| Output impedance (single-ended)         | R <sub>O</sub>  | 40                                        | 50  | 60                                        | Ω    | _      |

Notes:

- 1. This does not align to DC-coupled SGMII.  $XV_{DD SRDS2-Tvp} = 1.1 \text{ V}$ .

- 2. The |V<sub>OD</sub>| value shown in the table assumes full multitude by setting srd\_smit\_lvl as 000 and the following transmit equalization setting in the XMITEQAB (for lanes A and B) or XMITEQEF (for lanes E and F) bit field of Control Register:

- The MSB (bit 0) of the above bit field is set to zero (selecting the full V<sub>DD-DIFF-p-p</sub> amplitude which is power up default);

- The LSB (bit [1–3]) of the above bit field is set based on the equalization settings listed in notes 4 through 10.

- 3. The  $|V_{OD}|$  value shown in the Typ column is based on the condition of  $XV_{DD\_SRDS2-Typ} = 1.0 \text{ V}$ , no common mode offset variation ( $V_{OS} = 500 \text{mV}$ ), SerDes transmitter is terminated with  $100-\Omega$  differential load between

- 4. Equalization setting: 1.0x: 0000.

- Equalization setting: 1.09x: 1000.

- 6. Equalization setting: 1.2x: 0100.

- 7. Equalization setting: 1.33x: 1100.

- **8.** Equalization setting: 1.5x: 0010.

- 9. Equalization setting: 1.71x: 1010.

- 10. Equalization setting: 2.0x: 0110.

- 11.  $|V_{OD}| = |V_{SR[1-2]}|_{TX_D} V_{\overline{SR[1-2]}}|_{TX_D}|_{TX_D}$  is also referred to as output differential peak voltage.  $V_{TX-DIFF_{D-D}} = 2^*|V_{OD}|$

37

## 2.6 AC Timing Characteristics

This section describes the AC timing characteristics for the MSC8152.

### 2.6.1 DDR SDRAM AC Timing Specifications

This section describes the AC electrical characteristics for the DDR SDRAM interface.

### 2.6.1.1 DDR SDRAM Input AC Timing Specifications

Table 18 provides the input AC timing specifications for the DDR SDRAM when  $V_{DDDDR}$  (typ) = 1.8 V.

Table 18. DDR2 SDRAM Input AC Timing Specifications for 1.8 V Interface

| Parameter                                                                   | Symbol          | Min                      | Max                      | Unit |

|-----------------------------------------------------------------------------|-----------------|--------------------------|--------------------------|------|

| AC input low voltage                                                        | V <sub>IL</sub> | _                        | MV <sub>REF</sub> - 0.20 | V    |

| AC input high voltage                                                       | V <sub>IH</sub> | MV <sub>REF</sub> + 0.20 | _                        | V    |

| Note: At recommended operating conditions with $V_{DDDDR}$ of 1.8 $\pm$ 5%. |                 |                          |                          |      |

Table 19 provides the input AC timing specifications for the DDR SDRAM when V<sub>DDDDR</sub> (typ) = 1.5 V.

Table 19. DDR3 SDRAM Input AC Timing Specifications for 1.5 V Interface

| Parameter                                                                   | Symbol          | Min                       | Max                       | Unit |

|-----------------------------------------------------------------------------|-----------------|---------------------------|---------------------------|------|

| AC input low voltage                                                        | V <sub>IL</sub> | _                         | MV <sub>REF</sub> – 0.175 | V    |

| AC input high voltage                                                       | V <sub>IH</sub> | MV <sub>REF</sub> + 0.175 | _                         | V    |

| Note: At recommended operating conditions with $V_{DDDDR}$ of 1.5 $\pm$ 5%. |                 |                           |                           |      |

Table 20 provides the input AC timing specifications for the DDR SDRAM interface.

#### Table 20. DDR SDRAM Input AC Timing Specifications

| Parameter                             | Symbol              | Min          | Max | Unit | Notes |

|---------------------------------------|---------------------|--------------|-----|------|-------|

| Controller Skew for MDQS—MDQ/MECC/MDM | t <sub>CISKEW</sub> |              |     |      | 1, 2  |

| 800 MHz data rate                     | 5.5                 | -200         | 200 | ps   |       |

| 667 MHz data rate                     |                     | -240         | 240 | ps   |       |

| Tolerated Skew for MDQS—MDQ/MECC/MDM  | t <sub>DISKEW</sub> |              |     |      | 2, 3  |

| 800 MHz data rate                     |                     | -425         | 425 | ps   |       |

| 667 MHz data rate                     |                     | <b>–</b> 510 | 510 | ps   |       |

Notes:

- t<sub>CISKEW</sub> represents the total amount of skew consumed by the controller between MDQS[n] and any corresponding bit that is captured with MDQS[n]. Subtract this value from the total timing budget.

- 2. At recommended operating conditions with  $V_{DDDDR}$  (1.8 V or 1.5 V)  $\pm$  5%

- 3. The amount of skew that can be tolerated from MDQS to a corresponding MDQ signal is called t<sub>DISKEW</sub>. This can be determined by the following equation: t<sub>DISKEW</sub> = ±(T ÷ 4 abs(t<sub>CISKEW</sub>)) where T is the clock period and abs(t<sub>CISKEW</sub>) is the absolute value of t<sub>CISKEW</sub>.

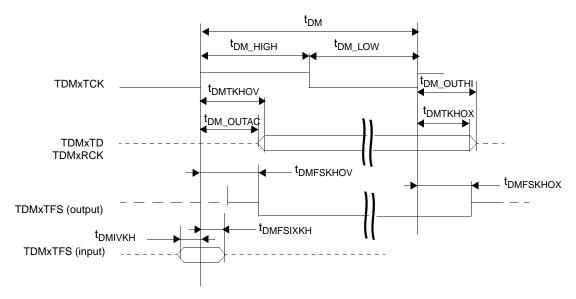

Figure 21 shows the TDM transmit signal timing.

Figure 21. TDM Transmit Signals

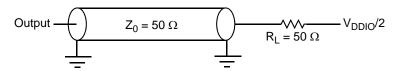

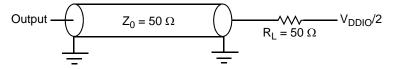

Figure 22 provides the AC test load for the TDM/SI.

Figure 22. TDM AC Test Load

### 2.6.4 Timers AC Timing Specifications

Table 32 lists the timer input AC timing specifications.

**Table 32. Timers Input AC Timing Specifications**

| Characteristics                                                                                                           |                                                                                                                       |  | Symbol             | Minimum | Unit | Notes |

|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--|--------------------|---------|------|-------|

| Timers inputs—minimum pulse width                                                                                         |                                                                                                                       |  | T <sub>TIWID</sub> | 8       | ns   | 1, 2  |

| Notes: 1. The maximum allowed frequency of timer outputs is 125 MHz. Configure the timer modules appropriately.           |                                                                                                                       |  |                    |         |      |       |

| 2. Timer inputs and outputs are asynchronous to any visible clock. Timer outputs should be synchronized before use by any |                                                                                                                       |  |                    |         |      |       |

|                                                                                                                           | external synchronous logic. Timer inputs are required to be valid for at least triving as to ensure proper operation. |  |                    |         |      |       |

**Note:** For recommended operating conditions, see Table 3.

Figure 23 shows the AC test load for the timers.

Figure 23. Timer AC Test Load

### 2.6.5.2 RGMII AC Timing Specifications

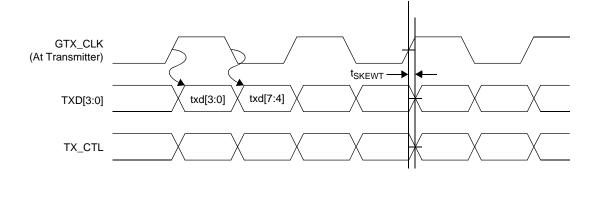

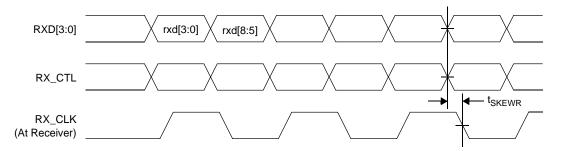

Table 34 presents the RGMII AC timing specifications for applications requiring an on-board delayed clock.

Table 34. RGMII at 1 Gbps<sup>2</sup> with On-Board Delay<sup>3</sup> AC Timing Specifications

| Parameter/Condition                                     | Symbol             | Min | Тур | Max | Unit |

|---------------------------------------------------------|--------------------|-----|-----|-----|------|

| Data to clock output skew (at transmitter) <sup>4</sup> | t <sub>SKEWT</sub> | 0.5 |     | 0.5 | ns   |

| Data to clock input skew (at receiver) 4                | t <sub>SKEWR</sub> | 1   | _   | 2.6 | ns   |

**Notes:** 1. At recommended operating conditions with  $V_{DDIO}$  of 2.5 V  $\pm$  5%.

- 2. RGMII at 100 Mbps support is guaranteed by design.

- **3.** Program GCR4 as 0x00000000.

- 4. This implies that PC board design requires clocks to be routed such that an additional trace delay of greater than 1.5 ns and less than 2.0 ns is added to the associated clock signal.

Table 35 presents the RGMII AC timing specification for applications required non-delayed clock on board.

Table 35. RGMII at 1 Gbps<sup>2</sup> with No On-Board Delay<sup>3</sup> AC Timing Specifications

| Parameter/Condition                                     | Symbol             | Min  | Тур | Max  | Unit |

|---------------------------------------------------------|--------------------|------|-----|------|------|

| Data to clock output skew (at transmitter) <sup>4</sup> | t <sub>SKEWT</sub> | -2.6 | _   | -1.0 | ns   |

| Data to clock input skew (at receiver) <sup>4</sup>     | t <sub>SKEWR</sub> | -0.5 |     | 0.5  | ns   |

**Notes:** 1. At recommended operating conditions with  $V_{DDIO}$  of 2.5 V  $\pm$  5%.

- 2. RGMII at 100 Mbps support is guaranteed by design.

- 3. GCR4 should be programmed as 0x000CC330.

- 4. This implies that PC board design requires clocks to be routed with no additional trace delay

Figure 25 shows the RGMII AC timing and multiplexing diagrams.

Figure 25. RGMII AC Timing and Multiplexing

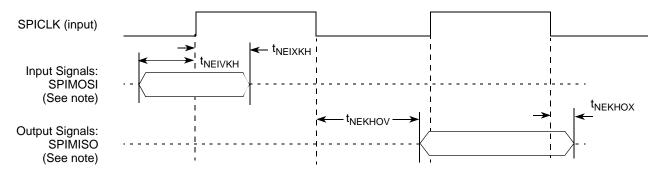

### 2.6.6 SPI Timing

Table 36 lists the SPI input and output AC timing specifications.

Table 36. SPI AC Timing Specifications

| Parameter                                                | Symbol <sup>1</sup> | Min | Max | Unit | Note |

|----------------------------------------------------------|---------------------|-----|-----|------|------|

| SPI outputs valid—Master mode (internal clock) delay     | t <sub>NIKHOV</sub> |     | 6   | ns   | 2    |

| SPI outputs hold—Master mode (internal clock) delay      | t <sub>NIKHOX</sub> | 0.5 | _   | ns   | 2    |

| SPI outputs valid—Slave mode (external clock) delay      | t <sub>NEKHOV</sub> | _   | 12  | ns   | 2    |

| SPI outputs hold—Slave mode (external clock) delay       | t <sub>NEKHOX</sub> | 2   | _   | ns   | 2    |

| SPI inputs—Master mode (internal clock) input setup time | t <sub>NIIVKH</sub> | 12  | _   | ns   | _    |

| SPI inputs—Master mode (internal clock) input hold time  | t <sub>NIIXKH</sub> | 0   | _   | ns   | _    |

| SPI inputs—Slave mode (external clock) input setup time  | t <sub>NEIVKH</sub> | 4   | _   | ns   | _    |

| SPI inputs—Slave mode (external clock) input hold time   | t <sub>NEIXKH</sub> | 2   | _   | ns   | _    |

Notes:

1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>NIKHOX</sub> symbolizes the internal timing (NI) for the time SPICLK clock reference (K) goes to the high state (H) until outputs (O) are invalid (X).

Output specifications are measured from the 50% level of the rising edge of SPICLK to the 50% level of the signal. Timings are measured at the pin.

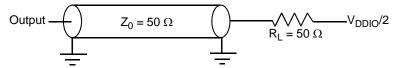

Figure 26 provides the AC test load for the SPI.

Figure 26. SPI AC Test Load

Figure 27 and Figure 28 represent the AC timings from Table 36. Note that although the specifications generally reference the rising edge of the clock, these AC timing diagrams also apply when the falling edge is the active edge.

Figure 27 shows the SPI timings in slave mode (external clock).

Note: measured with SPMODE[CI] = 0, SPMODE[CP] = 0

Figure 27. SPI AC Timing in Slave Mode (External Clock)

Figure 28 shows the SPI timings in master mode (internal clock).

## 2.6.7 Asynchronous Signal Timing

Table 35 lists the asynchronous signal timing specifications.

Table 37. Signal Timing

| Characteristics                                              | Symbol           | Туре         | Min                   |  |  |

|--------------------------------------------------------------|------------------|--------------|-----------------------|--|--|

| Input                                                        | t <sub>IN</sub>  | Asynchronous | One CLKIN cycle       |  |  |

| Output                                                       | t <sub>OUT</sub> | Asynchronous | Application dependent |  |  |

| Note: Input value relevant for EE0, IRQ[15–0], and NMI only. |                  |              |                       |  |  |

The following interfaces use the specified asynchronous signals:

GPIO. Signals GPIO[31–0], when used as GPIO signals, that is, when the alternate multiplexed special functions are not selected.

**Note:** When used as a general purpose input (GPI), the input signal should be driven until it is acknowledged by the MSC8152 device, that is, when the expected input value is read from the GPIO data register.

- EE port. Signals EE0, EE1.

- Boot function. Signal STOP\_BS.

- *I*<sup>2</sup>*C interface*. Signals I2C\_SCL and I2C\_SDA.

- Interrupt inputs. Signals  $\overline{IRQ[15-0]}$  and  $\overline{NMI}$ .

- Interrupt outputs. Signals INT\_OUT and NMI\_OUT (minimum pulse width is 32 ns).

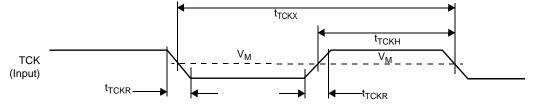

### 2.6.8 JTAG Signals

Table 38 lists the JTAG timing specifications shown in Figure 29 through Figure 32.

**Table 38. JTAG Timing**

| Characteristics                                                                                         | Symbol              | All frequencies |      | Unit |  |

|---------------------------------------------------------------------------------------------------------|---------------------|-----------------|------|------|--|

| Cital acteristics                                                                                       |                     | Min             | Max  | Onit |  |

| TCK cycle time                                                                                          | t <sub>TCKX</sub>   | 36.0            | _    | ns   |  |

| TCK clock high phase measured at V <sub>M</sub> = V <sub>DDIO</sub> /2                                  | t <sub>TCKH</sub>   | 15.0            | _    | ns   |  |

| Boundary scan input data setup time                                                                     | t <sub>BSVKH</sub>  | 0.0             |      | ns   |  |

| Boundary scan input data hold time                                                                      | t <sub>BSXKH</sub>  | 15.0            | _    | ns   |  |

| TCK fall to output data valid                                                                           | t <sub>TCKHOV</sub> | _               | 20.0 | ns   |  |

| TCK fall to output high impedance                                                                       | t <sub>TCKHOZ</sub> | _               | 24.0 | ns   |  |

| TMS, TDI data setup time                                                                                | t <sub>TDIVKH</sub> | 0.0             |      | ns   |  |

| TMS, TDI data hold time                                                                                 |                     | 5.0             |      | ns   |  |

| TCK fall to TDO data valid                                                                              |                     | _               | 10.0 | ns   |  |

| TCK fall to TDO high impedance                                                                          |                     | _               | 12.0 | ns   |  |

| TRST assert time                                                                                        |                     | 100.0           | _    | ns   |  |

| Note: All timings apply to OnCE module data transfers as well as any other transfers via the JTAG port. |                     |                 |      |      |  |

Figure 29 shows the test clock input timing diagram

Figure 29. Test Clock Input Timing

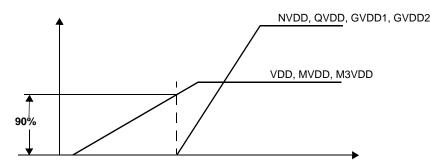

#### ware Design Considerations

2. After the above rails rise to 90% of their nominal voltage, the following I/O power rails may rise in any sequence (see Figure 34): QVDD, NVDD, GVDD1, and GVDD2.

Figure 34. Supply Ramp-Up Sequence

**Notes:** 1. If the M3 memory is not used, M3VDD can be tied to GND.

- 2. If the MAPLE-B is not used, MVDD can be tied to GND.

- 3. If the HSSI port1 is not used, SXCVDD1 and SXPVDD1 must be connected to the designated power supplies.

- 4. If the HSSI port2 is not used, SXCVDD2 and SXPVDD2 must be connected to the designated power supplies.

- 5. If the DDR port 1 interface is not used, it is recommended that GVDD1 be left unconnected.

- **6.** If the DDR port 2 interface is not used, it is recommended that GVDD2 be left unconnected.

### 3.1.4 Reset Guidelines

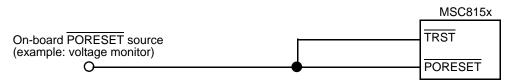

When a debugger is not used, implement the connection scheme shown in Figure 35.

Figure 35. Reset Connection in Functional Application

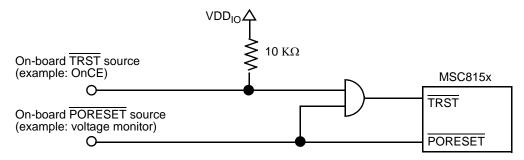

When a debugger is used, implement the connection scheme shown in Figure 36.

Figure 36. Reset Connection in Debugger Application

## 3.3 Clock and Timing Signal Board Layout Considerations

When laying out the system board, use the following guidelines:

- Keep clock and timing signal paths as short as possible and route with 50  $\Omega$  impedance.

- Use a serial termination resistor placed close to the clock buffer to minimize signal reflection. Use the following equation to compute the resistor value:

Rterm = Rim - Rbuf

where Rim = trace characteristic impedance

Rbuf = clock buffer internal impedance.

## 3.4 SGMII AC-Coupled Serial Link Connection Example

Figure 39 shows an example of a 4-wire AC-coupled serial link connection. For additional layout suggestions, see *AN3556 MSC815x High Speed Serial Interface Hardware Design Considerations*, available on the Freescale website or from your local sales office or representative.

Figure 39. 4-Wire AC-Coupled SGMII Serial Link Connection Example

### 3.5.1.2 DDR Interface Is Used With 32-Bit DDR Memory Only

Table 41 lists unused pin connection when using 32-bit DDR memory. The 32 most significant data lines are not used.

Table 41. Connectivity of DDR Related Pins When Using 32-bit DDR Memory Only

| Signal Name | Pin Connection |

|-------------|----------------|

| MDQ[31-0]   | in use         |

| MDQ[63–32]  | NC             |

| MDQS[3-0]   | in use         |

| MDQS[7-4]   | NC             |

| MDQS[3-0]   | in use         |

| MDQS[7-4]   | NC             |

| MA[15-0]    | in use         |

| MCK[2-0]    | in use         |

| MCK[2-0]    | in use         |

| MCS[1-0]    | in use         |

| MDM[3-0]    | in use         |

| MDM[7-4]    | NC             |

| MBA[2-0]    | in use         |

| MCAS        | in use         |

| MCKE[1-0]   | in use         |

| MODT[1-0]   | in use         |

| MMDIC[1-0]  | in use         |

| MRAS        | in use         |

| MWE         | in use         |

| MVREF       | in use         |

| GVDD1/GVDD2 | in use         |

Notes:

- : 1. For the signals listed in this table, the initial M stands for M1 or M2 depending on which DDR controller is not used.

- 2. For MSC8152 Revision 1 silicon, these pins were connected to GND (or VDD). For newer revisions of the MSC8152, connecting these pins to GND increases device power consumption.

### 3.5.1.3 ECC Unused Pin Connections

When the error code correction mechanism is not used in any 32- or 64-bit DDR configuration, refer to Table 42 to determine the correct pin connections.

Table 42. Connectivity of Unused ECC Mechanism Pins

| Signal Name | Pin connection |

|-------------|----------------|

| MECC[7-0]   | NC             |

| MDM8        | NC             |

| MDQS8       | NC             |

| MDQS8       | NC             |

Notes: 1. For the signals listed in this table, the initial M stands for M1 or M2 depending on which DDR controller is not used.

For MSC8152 Revision 1 silicon, these pins were connected to GND (or VDD). For newer revisions of the MSC8152, connecting these pins to GND increases device power consumption.

MSC8152 Dual-Core Digital Signal Processor Data Sheet, Rev. 6

### 3.5.1.4 DDR2 Unused MAPAR Pin Connections

When the MAPAR signals are not used, refer to Table 43 to determine the correct pin connections.

Table 43. Connectivity of MAPAR Pins for DDR2

| Signal Name |                                                                                                                                                                                                                                                                                                                                | Signal Name | Pin connection |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------|--|

| MAPAR_OUT   |                                                                                                                                                                                                                                                                                                                                |             | NC             |  |

| MAPAR_IN    |                                                                                                                                                                                                                                                                                                                                |             | NC             |  |

| Notes:      | <ol> <li>For the signals listed in this table, the initial M stands for M1 or M2 depending on which DDR controller is used for DDR2.</li> <li>For MSC8152 Revision 1 silicon, these pins were connected to GND. For newer revisions of the MSC8152, connecting thes pins to GND increases device power consumption.</li> </ol> |             |                |  |

### 3.5.2 HSSI-Related Pins

### 3.5.2.1 HSSI Port Is Not Used

The signal names in Table 44 and Table 45 are generic names for a RapidIO interface. For actual pin names refer to Table 1.

Table 44. Connectivity of Serial RapidIO Interface Related Pins When the RapidIO Interface Is Not Used

| Signal Name                                                                                                   | Pin Connection |  |  |  |

|---------------------------------------------------------------------------------------------------------------|----------------|--|--|--|

| SR_IMP_CAL_RX                                                                                                 | NC             |  |  |  |

| SR_IMP_CAL_TX                                                                                                 | NC             |  |  |  |

| SR[1-2]_REF_CLK                                                                                               | SXCVSS         |  |  |  |

| SR[1-2]_REF_CLK                                                                                               | SXCVSS         |  |  |  |

| SR[1-2]_RXD[3-0]                                                                                              | SXCVSS         |  |  |  |

| SR[1-2]_RXD[3-0]                                                                                              | SXCVSS         |  |  |  |

| SR[1-2]_TXD[3-0]                                                                                              | NC             |  |  |  |

| SR[1-2]_TXD[3-0]                                                                                              | NC             |  |  |  |

| SR[1-2]_PLL_AVDD                                                                                              | In use         |  |  |  |

| SR[1-2]_PLL_AGND                                                                                              | In use         |  |  |  |

| SXPVSS                                                                                                        | In use         |  |  |  |

| SXCVSS                                                                                                        | In use         |  |  |  |

| SXPVDD                                                                                                        | In use         |  |  |  |

| SXCVDD In use                                                                                                 |                |  |  |  |

| Note: All lanes in the HSSI SerDes should be powered down. Refer to the MSC8152 Reference Manual for details. |                |  |  |  |

### 3.5.2.2 HSSI Specific Lane Is Not Used

Table 45. Connectivity of HSSI Related Pins When Specific Lane Is Not Used

| Signal Name     | Pin Connection |

|-----------------|----------------|

| SR_IMP_CAL_RX   | In use         |

| SR_IMP_CAL_TX   | In use         |

| SR[1-2]_REF_CLK | In use         |

| SR[1-2]_REF_CLK | In use         |

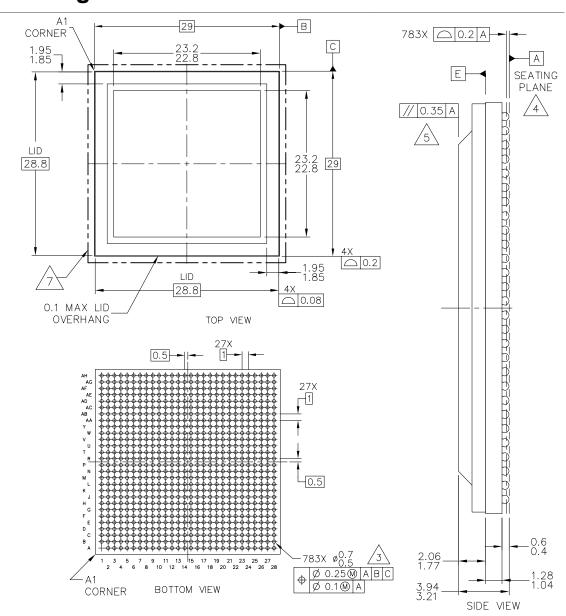

# 5 Package Information

#### **NOTES:**

- ALL DIMENSIONS IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

MAXIMUM SOLDER BALL DIAMETER MEASURE PARALLEL TO DATUM A.

DATUM A, THE SEATING PLANE, IS DETERMINED BY THE SPHERICAL CROWNS OF THE SOLDER BALLS.

A PARALLELISM MEASUREMENT SHALL EXCLUDE ANY EFFECT OF MARK ON TOP SURFACE OF PACKAGE.

- 6. ALL DIMENSIONS ARE SYMMETRIC ACROSS THE PACKAGE CENTER LINES, UNLESS DIMENSIONED OTHERWISE.

- 7. 29.2MM MAXIMUM PACKAGE ASSEMBLY (LID + LAMINATE) X AND Y.

Figure 40. MSC8152 Mechanical Information, 783-ball FC-PBGA Package

MSC8152 Dual-Core Digital Signal Processor Data Sheet, Rev. 6

## 6 Product Documentation

Following is a general list of supporting documentation:

- *MSC8152 Technical Data Sheet* (MSC8152). Details the signals, AC/DC characteristics, clock signal characteristics, package and pinout, and electrical design considerations of the MSC8152 device.

- *MSC8152 Reference Manual* (MSC8152RM). Includes functional descriptions of the extended cores and all the internal subsystems including configuration and programming information.

- Application Notes. Cover various programming topics related to the StarCore DSP core and the MSC8152 device.

- QUICC Engine Block Reference Manual with Protocol Interworking (QEIWRM). Provides detailed information regarding the QUICC Engine technology including functional description, registers, and programming information.

- *SC3850 DSP Core Reference Manual*. Covers the SC3850 core architecture, control registers, clock registers, program control, and instruction set.

- MSC8156SC3850 DSP Core Subsystem Reference Manual. Covers core subsystem architecture, functionality, and registers.

## 7 Revision History

Table 50 provides a revision history for this data sheet.

**Table 50. Document Revision History**

| Rev. | Date      | Description                                                                                                                                                                      |

|------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | Jun. 2010 | Initial public release.                                                                                                                                                          |

| 1    | Dec 2010  | <ul> <li>Updated Table 16.</li> <li>Updated Section 3.1.2, Power-On Ramp Time.</li> </ul>                                                                                        |

| 2    | Mar 2011  | <ul> <li>Updated Table 8.</li> <li>Updated Table 15.</li> <li>Updated Table 17.</li> <li>Updated Table 33.</li> <li>Updated Table 35.</li> <li>Updated Table 39.</li> </ul>      |

| 3    | May 2011  | <ul> <li>Updated Table 1. Changed the pin types for the following:</li> <li>F25 from ground to power.</li> <li>F26 from power to ground.</li> <li>T6 from power to O.</li> </ul> |

| 4    | Oct 2011  | • Updated Table 34 and Table 35 to reflect 1 Gbps and 100 Mbps data rate instead of 1 GHz and 100 MHz.                                                                           |

| 5    | Dec 2011  | Added note 4 to Table 39.                                                                                                                                                        |

| 6    | Aug 2013  | Updated Section 4, "Ordering Information".                                                                                                                                       |