Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Details                    |                                                                |

|----------------------------|----------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                       |

| Core Processor             | eZ80                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 50MHz                                                          |

| Connectivity               | EBI/EMI, Ethernet MAC, I <sup>2</sup> C, IrDA, SPI, UART/USART |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                          |

| Number of I/O              | 32                                                             |

| Program Memory Size        | 256KB (256K x 8)                                               |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 16K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                      |

| Data Converters            | ·                                                              |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                             |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 144-LQFP                                                       |

| Supplier Device Package    | 144-LQFP (20x20)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/ez80f91gaz0beg      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| LQFP<br>Pin No | BGA<br>Pin No | Symbol          | Function      | Signal Direction      | Description                                                                                                                           |

|----------------|---------------|-----------------|---------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 17             | F1            | ADDR12          | Address Bus   | Bidirectional         | Configured as an output in normal                                                                                                     |

| 18             | F2            | ADDR13          | Address Bus   | Bidirectional         | operation. The address bus selects a location in memory or I/O space to be                                                            |

| 19             | F3            | ADDR14          | Address Bus   | Bidirectional         | read or written. Configured as an input                                                                                               |

| 20             | F4            | ADDR15          | Address Bus   | Bidirectional         | during bus acknowledge cyclesDrives the Chip Select/Wait State                                                                        |

| 21             | G1            | ADDR16          | Address Bus   | Bidirectional         | Generator block to generate Chip<br>Selects.                                                                                          |

| 22             | G2            | V <sub>DD</sub> | Power Supply  |                       | Power Supply.                                                                                                                         |

| 23             | G3            | V <sub>SS</sub> | Ground        |                       | Ground.                                                                                                                               |

| 24             | F5            | ADDR17          | Address Bus   | Bidirectional         | Configured as an output in normal                                                                                                     |

| 25             | H1            | ADDR18          | Address Bus   | Bidirectional         | operation. The address bus selects a location in memory or I/O space to be                                                            |

| 26             | H2            | ADDR19          | Address Bus   | Bidirectional         | read or written. Configured as an input                                                                                               |

| 27             | G4            | ADDR20          | Address Bus   | Bidirectional         | during bus acknowledge cycles. Drives the Chip Select/Wait State                                                                      |

| 28             | H3            | ADDR21          | Address Bus   | Bidirectional         | Generator block to generate Chip                                                                                                      |

| 29             | J1            | ADDR22          | Address Bus   | Bidirectional         | <sup>–</sup> Selects.                                                                                                                 |

| 30             | G5            | ADDR23          | Address Bus   | Bidirectional         | _                                                                                                                                     |

| 31             | J2            | V <sub>DD</sub> | Power Supply  |                       | Power Supply.                                                                                                                         |

| 32             | H4            | V <sub>SS</sub> | Ground        |                       | Ground.                                                                                                                               |

| 33             | J3            | CS0             | Chip Select 0 | Output, Active<br>Low | $\overline{\text{CS0}}$ Low indicates that an access is occurring in the defined $\overline{\text{CS0}}$ memory or I/O address space. |

| 34             | K1            | CS1             | Chip Select 1 | Output, Active<br>Low | CS1 Low indicates that an access is<br>occurring in the defined CS1 memory<br>or I/O address space.                                   |

| 35             | K2            | CS2             | Chip Select 2 | Output, Active<br>Low | $\overline{\text{CS2}}$ Low indicates that an access is occurring in the defined $\overline{\text{CS2}}$ memory or I/O address space. |

| 36             | L1            | CS3             | Chip Select 3 | Output, Active<br>Low | $\overline{\text{CS3}}$ Low indicates that an access is occurring in the defined $\overline{\text{CS3}}$ memory or I/O address space. |

| 37             | M1            | V <sub>DD</sub> | Power Supply  |                       | Power Supply.                                                                                                                         |

| 38             | M2            | V <sub>SS</sub> | Ground        |                       | Ground.                                                                                                                               |

|                |               |                 |               |                       |                                                                                                                                       |

#### Table 2. Pin Identification on the eZ80F91 ASSP Device (Continued)

| LQFP<br>Pin No | BGA<br>Pin No | Symbol          | Function                      | Signal Direction                                                                 | Description                                                                                                                                                                                                                                                                    |

|----------------|---------------|-----------------|-------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 53             | M6            | INSTRD          | Instruction<br>Read Indicator | Output, Active                                                                   | INSTRD (with MREQ and RD) indi-<br>cates the eZ80F91 device is fetching<br>an instruction from memory. This pin<br>is in a high-impedance state during<br>bus acknowledge cycles.                                                                                              |

| 54             | L6            | WAIT            | WAIT Request                  | Schmitt Trigger<br>input, Active Low                                             | Driving the WAIT pin Low forces the<br>CPU to wait additional clock cycles for<br>an external peripheral or external<br>memory to complete its read or write<br>operation.                                                                                                     |

| 55             | K6            | RESET           | Reset                         | Bidirectional,<br>Active Low<br>Schmitt Trigger<br>input or open<br>drain output | This signal is used to initialize the eZ80F91, and/or allow the eZ80F91 to signal when it resets. See the <u>Reset</u> chapter on page 38 for the timing details. This Schmitt Trigger input allows for RC rise times.                                                         |

| 56             | J6            | NMI             | Nonmaskable<br>Interrupt      | Schmitt Trigger<br>input, Active Low,<br>edge-triggered<br>interrupt             | The NMI input is a higher priority input<br>than the maskable interrupts. It is<br>always recognized at the end of an<br>instruction, regardless of the state of<br>the interrupt enable control bits. This<br>input includes a Schmitt Trigger to<br>allow for RC rise times. |

| 57             | M7            | BUSREQ          | Bus Request                   | Schmitt Trigger<br>input, Active Low                                             | External devices request the eZ80F91 device to release the memory inter-<br>face bus for their use by driving this pin Low.                                                                                                                                                    |

| 58             | L7            | BUSACK          | Bus Acknowl-<br>edge          | Output, Active<br>Low                                                            | The eZ80F91 device responds to a<br>Low on BUSREQ making the address,<br>data, and control signals high imped-<br>ance, and by driving the BUSACK line<br>Low. During bus acknowledge cycles<br>ADDR[23:0], IORQ, and MREQ are<br>inputs.                                      |

| 59             | K7            | V <sub>DD</sub> | Power Supply                  |                                                                                  | Power Supply.                                                                                                                                                                                                                                                                  |

|                |               |                 |                               |                                                                                  |                                                                                                                                                                                                                                                                                |

#### Table 2. Pin Identification on the eZ80F91 ASSP Device (Continued)

# eZ80 CPU Core

The eZ80 CPU is the first 8-bit CPU to support 16MB linear addressing. Each software module or task under a real-time executive or operating system operates in Z80-compatible (64KB) mode or full 24-bit (16MB) address mode.

The CPU instruction set is a superset of the instruction sets for the Z80 and Z180 CPUs. Z80 and Z180 programs can be executed on an eZ80 CPU with little or no modification.

### **Features**

The features of eZ80 CPU include:

- Code-compatible with Z80 and Z180 products

- 24-bit linear address space

- Single-cycle instruction fetch

- Pipelined fetch, decode, and execute

- Dual stack pointers for ADL (24-bit) and Z80 (16-bit) memory modes

- 24-bit CPU registers and Arithmetic Logic Unit (ALU)

- Debug support

- Nonmaskable Interrupt (NMI), plus support for 128 maskable vectored interrupts

## **New Instructions**

Two new eZ80 CPU instructions load/unload the I Register with a 16-bit value. These new instructions are:

- LD I,HL (ED C7)

- LD HL,I (ED D7)

For more information about the eZ80 CPU, its instruction set, and eZ80 programming, refer to the <u>eZ80 CPU User Manual (UM0077)</u>, which is available free for download from the Zilog website.

Т

Т

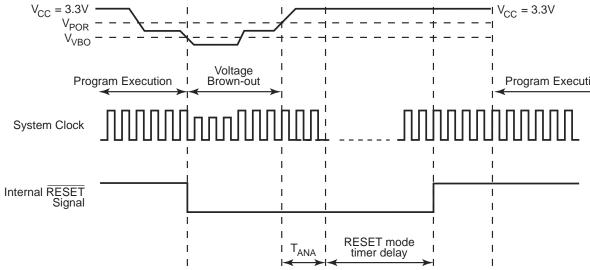

Figure 4. Voltage Brown-Out Reset Operation

# General-Purpose Input/Output

The eZ80F91 device features 32 General-Purpose Input/Output (GPIO) pins. The GPIO pins are assembled as four 8-bit ports: Port A, Port B, Port C, and Port D. All port signals are configured as either inputs or outputs. In addition, all of the port pins are used as vectored interrupt sources for the CPU.

The eZ80F91 ASSPs GPIO ports are slightly different from its eZ80 predecessors. Specifically, Port A pins source 8 mA and sink 10 mA. In addition, the Port B and C inputs now feature Schmitt Trigger input buffers.

## **GPIO** Operation

GPIO operation is the same for all four GPIO ports (Ports A, B, C, and D). Each port features eight GPIO port pins. The operating mode for each pin is controlled by four bits that are divided between four 8-bit registers. The GPIO mode control registers are:

- Port *x* Data Register (Px\_DR)

- Port *x* Data Direction Register (Px\_DDR)

- Port *x* Alternate Register 1 (Px\_ALT1)

- Port *x* Alternate Register 2 (Px\_ALT2)

In the above list, *x* can be A, B, C or D, representing any of the four GPIO ports. The mode for each pin is controlled by setting each register bit pertinent to the pin to be configured. For example, the operating mode for port B pin 7 (PB7) is set by the values contained in PB\_DR[7], PB\_DDR[7], PB\_ALT1[7], and PB\_ALT2[7].

The combination of the GPIO control register bits allows individual configuration of each port pin for nine modes. In all modes, reading of the Port *x* Data Register returns the sampled state or level of the signal on the corresponding pin. Table 6 indicates the function of each port signal based on these four register bits. After a RESET event, all GPIO port pins are configured as standard digital inputs with the interrupts disabled.

In addition to the four mode control registers, each port has an 8-bit register, which is used for clearing edge-triggered interrupts. This register is the Port *x* Alternate Register 0 (Px\_ALT0), in which *x* can be A, B, C or D representing the four GPIO ports. When a GPIO pin is configured as an edge-triggered interrupt, writing 1 to the corresponding bit of the Px\_ALT0 Register clears the interrupt.

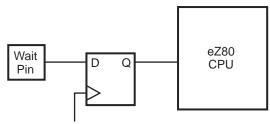

## WAIT Input Signal

Similar to the programmable wait states, an external peripheral drives the  $\overline{WAIT}$  input pin to force the CPU to provide additional clock cycles to complete its read or write operation. Driving the  $\overline{WAIT}$  pin Low stalls the CPU. The CPU resumes operation on the first rising edge of the internal system clock following deassertion of the  $\overline{WAIT}$  pin.

**Caution:** If the WAIT pin is to be driven by an external device, the corresponding chip select for the device must be programmed to provide at least one wait state. Due to input sampling of the WAIT input pin (see Figure 8), one programmable wait state is required to allow the external peripheral sufficient time to assert the WAIT pin. It is recommended that the corresponding chip select for the external device be programmed to provide the maximum number of wait states (seven).

System Clock

Figure 8. Wait Input Sampling Block Diagram

An example of wait state operation is shown in Figure 9. In this example, the chip select is configured to provide a single wait state. The external peripheral accessed drives the  $\overline{\text{WAIT}}$  pin Low to request assertion of an additional wait state. If the  $\overline{\text{WAIT}}$  pin is asserted for additional system clock cycles, wait states are added until the  $\overline{\text{WAIT}}$  pin is deasserted (active High).

#### 68

## **Bus Mode Controller**

The bus mode controller allows the address and data bus timing and signal formats of the eZ80F91 to be configured to connect with external devices compatible with eZ80, Z80, Intel and Motorola microcontrollers. Bus modes for each of the chip selects are configured independently using the Chip Select Bus Mode Control Registers. The number of CPU system clock cycles per bus mode state is also independently programmable. For Intel bus mode, multiplexed address and data are selected in which both the lower byte of the address and the data byte use the data bus, DATA[7:0]. Each of the bus modes are explained in the following sections.

## eZ80 BUS Mode

Chip selects configured for eZ80 BUS Mode do not modify the bus signals from the CPU. The timing diagrams for external Memory and I/O read and write operations are shown in the <u>AC Characteristics</u> section on page 343. The default mode for each chip select is eZ80 Mode.

## Z80 BUS Mode

Chip selects configured for Z80 Mode modify the eZ80 bus signals to match the Z80 microprocessor address and data bus interface signal format and timing. During read operations, the Z80 bus mode employs three states: T1, T2, and T3, as described in Table 19.

#### Table 19. Z80 BUS Mode Read States

STATE T1 The read cycle begins in State T1. The CPU drives the address onto the address bus and the associated chip select signal is asserted.

- STATE T2 During State T2, the RD signal is asserted. Depending on the instruction, either the MREQ or IORQ signal is asserted. If the external WAIT pin is driven Low at least one CPU system clock cycle prior to the end of State T2, additional wait states (T<sub>WAIT</sub>) are asserted until the WAIT pin is driven High.

- STATE T3 During State T3, no bus signals are altered. The data is latched by the eZ80F91 at the rising edge of the CPU system clock at the end of State T3.

| 1 | 1 | 5 |

|---|---|---|

|   |   |   |

| Bit            | Description (Continued)                                                                                                                                                                                                                                                         |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [1:0]          | Watchdog Timer Period                                                                                                                                                                                                                                                           |

| WDT_PERIOD     | 00: WDT_CLK = 00: WDT time-out period is $2^{27}$ clock cycles.<br>WDT_CLK = 01: WDT time-out period is $2^{17}$ clock cycles.<br>WDT_CLK = 10: WDT time-out period is $2^{15}$ clock cycles.<br>WDT_CLK = 11: reserved.                                                        |

|                | 01: WDT_CLK = 00: WDT time-out period is 2 <sup>25</sup> clock cycles.<br>WDT_CLK = 01: WDT time-out period is 2 <sup>14</sup> clock cycles.<br>WDT_CLK = 10: WDT time-out period is 2 <sup>13</sup> clock cycles.<br>WDT_CLK = 11: reserved.                                   |

|                | <ul> <li>10: WDT_CLK = 00: WDT time-out period is 2<sup>22</sup> clock cycles.</li> <li>WDT_CLK = 01: WDT time-out period is 2<sup>11</sup> clock cycles.</li> <li>WDT_CLK = 10: WDT time-out period is 2<sup>9</sup> clock cycles.</li> <li>WDT_CLK = 11: reserved.</li> </ul> |

|                | <ul> <li>11: WDT_CLK = 00: WDT time-out period is 2<sup>18</sup> clock cycles.</li> <li>WDT_CLK = 01: WDT time-out period is 2<sup>7</sup> clock cycles.</li> <li>WDT_CLK = 10: WDT time-out period is 2<sup>5</sup> clock cycles.</li> <li>WDT_CLK = 11: reserved.</li> </ul>  |

| Note: When the | WDT is enabled, no writes are allowed to the WDT_CTL Register.                                                                                                                                                                                                                  |

### **Timer Interrupt Enable Register**

The Timer *x* Interrupt Enable Register, shown in Table 55, is used to control timer interrupt operations. Only bits related to functions present in a given timer are active.

| Table 55. | Timer | Interrupt | Enable | (TMR <i>x</i> _IER) |

|-----------|-------|-----------|--------|---------------------|

|-----------|-------|-----------|--------|---------------------|

| Reset         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 <th>Bit</th> <th>7</th> <th>6</th> <th>5</th> <th>4</th> <th>3</th> <th>2</th> <th>1</th> <th>0</th>                                                                                                           | Bit     | 7                                                                      | 6 | 5                   | 4 | 3 | 2 | 1 | 0              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------------------------------------------------------------|---|---------------------|---|---|---|---|----------------|

| R/W         R/W <th>Field</th> <th>Reserved</th> <th></th> <th colspan="4">IRQ_OC<i>x</i>_EN</th> <th></th> <th>IRQ_<br/>EOC_EN</th> | Field   | Reserved                                                               |   | IRQ_OC <i>x</i> _EN |   |   |   |   | IRQ_<br>EOC_EN |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Reset   | 0                                                                      | 0 | 0                   | 0 | 0 | 0 | 0 | 0              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W     | <b>R/W</b> R/W R/W R/W R/W R/W R/W R/W                                 |   |                     |   |   |   |   |                |

| Address IMRU_IER = 00010, IMR1_IER = 00000, IMR2_IER = 00700, IMR3_IER = 00750                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Address | TMR0_IER = 0061h, TMR1_IER = 0066h, TMR2_IER = 0070h, TMR3_IER = 0075h |   |                     |   |   |   |   |                |

Note: R = read only; R/W = read/write.

| Bit               | Description                                                                                                                                                                                                                                                                                                    |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]               | <b>Reserved</b><br>This bit is unused and must be programmed to 0.                                                                                                                                                                                                                                             |

| [6]<br>IRQ_OC3_EN | <ul> <li>Interrupt Request Output Compare 3 Enable</li> <li>0: Interrupt requests for OC3 are disabled (valid only in OUTPUT COMPARE Mode). OC operations occur in Timer 3.</li> <li>1: Interrupt requests for OC3 are enabled (valid only in OUTPUT COMPARE Mode). OC operations occur in Timer 3.</li> </ul> |

| [5]<br>IRQ_OC2_EN | <ul> <li>Interrupt Request Output Compare 2 Enable</li> <li>0: Interrupt requests for OC2 are disabled (valid only in OUTPUT COMPARE Mode). OC operations occur in Timer 3.</li> <li>1: Interrupt requests for OC2 are enabled (valid only in OUTPUT COMPARE Mode). OC operations occur in Timer 3.</li> </ul> |

| [4]<br>IRQ_OC1_EN | <ul> <li>Interrupt Request Output Compare 1 Enable</li> <li>0: Interrupt requests for OC1 are disabled (valid only in OUTPUT COMPARE Mode). OC operations occur in Timer 3.</li> <li>1: Interrupt requests for OC1 are enabled (valid only in OUTPUT COMPARE Mode). OC operations occur in Timer 3.</li> </ul> |

| [3]<br>IRQ_OC0_EN | <ul> <li>Interrupt Request Output Compare 0 Enable</li> <li>0: Interrupt requests for OC0 are disabled (valid only in OUTPUT COMPARE Mode). OC operations occur in Timer 3.</li> <li>1: Interrupt requests for OC0 are enabled (valid only in OUTPUT COMPARE Mode). OC operations occur in Timer 3.</li> </ul> |

### **Timer Data High Byte Register**

The Timer *x* Data High Byte Register, shown in Table 58, returns the high byte of the count value of the selected timer as it existed at the time that the low byte was read. The Timer Data High Byte Register is read when the timer is in operation. Reading the current count value does not affect timer operation. To read the 16-bit data of the current count value, {TMR $x_DR_H[7:0]$ , TMR $x_DR_L[7:0]$ }, first read the Timer Data Low Byte Register followed by the Timer Data High Byte Register. The Timer Data High Byte Register value is latched into temporary storage when a read of the Timer Data Low Byte Register occurs.

This register shares its address with the corresponding timer reload register.

| Table 58 | . Timer Data | High I | Byte I | Register | (TMRx_D | R_H) |

|----------|--------------|--------|--------|----------|---------|------|

|----------|--------------|--------|--------|----------|---------|------|

| Bit            | 7                                                                             | 6               | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------|-------------------------------------------------------------------------------|-----------------|---|---|---|---|---|---|

| Field          |                                                                               | TMRx_DR_H       |   |   |   |   |   |   |

| Reset          | 0                                                                             | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |

| R/W            | R                                                                             | R               | R | R | R | R | R | R |

| Address        | TMR0_DR_H = 0064h, TMR1_DR_H = 0069h,<br>TMR2_DR_H = 0073h, TMR3_DR_H = 0078h |                 |   |   |   |   |   |   |

| Note: R = read | Note: R = read only.                                                          |                 |   |   |   |   |   |   |

| Bit      | Description                                                                             |

|----------|-----------------------------------------------------------------------------------------|

| [7:0]    | Timer Data Low Byte                                                                     |

| TMR_DR_H | 00h–FFh: These bits represent the high byte of the 2-byte timer data value,             |

|          | {TMRx_DR_H[7:0], TMRx_DR_L[7:0]}. Bit 7 is bit 15 (msb) of the 16-bit timer data value. |

|          | Bit 0 is bit 8 of the 16-bit timer data value.                                          |

| Bit                   | 7                                                                             | 6               | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------------------|-------------------------------------------------------------------------------|-----------------|---|---|---|---|---|---|

| Field                 |                                                                               | TMR_RR_H        |   |   |   |   |   |   |

| Reset                 | 0                                                                             | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |

| R/W                   | W                                                                             | W               | W | W | W | W | W | W |

| Address               | TMR0_RR_H = 0064h, TMR1_RR_H = 0069h,<br>TMR2_RR_H = 0073h, TMR3_RR_H = 0078h |                 |   |   |   |   |   |   |

| Note: W = write only. |                                                                               |                 |   |   |   |   |   |   |

#### Table 60. Timer Reload High Byte Register (TMRx\_RR\_H)

| Bit      | Description                                                                        |

|----------|------------------------------------------------------------------------------------|

| [7:0]    | Timer Reload High Byte                                                             |

| TMR_RR_H | 00h–FFh: These bits represent the high byte of the 2-byte timer reload value,      |

|          | {TMRx_RR_H[7:0], TMRx_RR_L[7:0]}. Bit 7 is bit 15 (msb) of the 16-bit timer reload |

|          | value. Bit 0 is bit 8 of the 16-bit timer reload value.                            |

#### **Timer Input Capture Control Register**

The Timer *x* Input Capture Control Register, shown in Table 61, is used to select the edge or edges to be captured. For Timer 1, CAP\_EDGE\_B is used for IC1 and CAP\_EDGE\_A is for IC0. For Timer 3, CAP\_EDGE\_B is for IC3, and CAP\_EDGE\_A is for IC2.

| Bit     | 7                                          | 6    | 5     | 4   | 3     | 2     | 1     | 0     |

|---------|--------------------------------------------|------|-------|-----|-------|-------|-------|-------|

| Field   |                                            | Rese | erved |     | CAP_E | DGE_B | CAP_E | DGE_A |

| Reset   | 0                                          | 0    | 0     | 0   | 0     | 0     | 0     | 0     |

| R/W     | R/W                                        | R/W  | R/W   | R/W | R/W   | R/W   | R/W   | R/W   |

| Address | TMR1_CAP_CTL = 006Ah, TMR3_CAP_CTL = 007Bh |      |       |     |       |       |       |       |

Note: R = read only; R/W = read/write.

| Bit                 | Description                                                                                                                                                                                                   |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:4]               | Reserved<br>These bits are reserved and must be programmed to 0000.                                                                                                                                           |

| [3:2]<br>CAP_EDGE_B | Capture Edge Enable B<br>00: Disable capture on ICB.<br>01: Enable capture only on the falling edge of ICB.<br>10: Enable capture only on the rising edge of ICB.<br>11: Enable capture on both edges of ICB. |

## **UART Functional Description**

The UART Baud Rate Generator (BRG) creates the clock for the serial transmit and receive functions. The UART module supports all of the various options in the asynchronous transmission and reception protocol including:

- 5- to 9-bit transmit/receive

- Start bit generation and detection

- Parity generation and detection

- Stop bit generation and detection

- Break generation and detection

The UART contains 16-byte-deep FIFOs in each direction. The FIFOs are enabled or disabled by the application. The receive FIFO features trigger-level detection logic, which enables the CPU to block-transfer data bytes from the receive FIFO.

## **UART Functions**

The UART function implements:

- The transmitter and associated control logic

- The receiver and associated control logic

- The modem interface and associated logic

### **UART Transmitter**

The transmitter block controls the data transmitted on the TxD output. It implements the FIFO, access via the UARTx\_THR Register, the transmit shift register, the parity generator, and control logic for the transmitter to control parameters for the asynchronous communications protocol.

The UARTx\_THR is a write-only register. The CPU writes the data byte to be transmitted into this register. In FIFO Mode, up to 16 data bytes are written via the UARTx\_THR Register. The data byte from the FIFO is transferred to the transmit shift register at the appropriate time and transmitted via TxD output. After SYNC\_RESET, the UARTx\_THR Register is empty. Therefore, the Transmit Holding Register Empty (THRE) bit (bit 5 of the UARTx\_LSR Register) is 1. An interrupt is sent to the CPU if interrupts are enabled. The CPU resets this interrupt by loading data into the UARTx\_THR Register, which clears the transmitter interrupt.

The transmit shift register places the byte to be transmitted on the TxD signal serially. The least-significant bit of the byte to be transmitted is shifted out first and the most-significant

meet IrDA specifications. The UART must be enabled to use the endec. For more information about the UART and its BRG, see the <u>Universal Asynchronous Receiver/Transmitter</u> chapter on page 172.

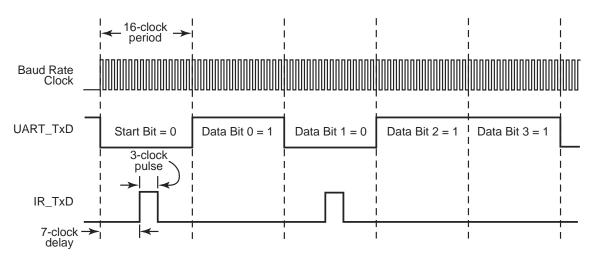

### Transmit

The data to be transmitted via the IR transceiver is the data sent to UART0. The UART transmit signal, TxD, and Baud Rate Clock are used by the endec to generate the modulation signal, IR\_TxD, that drives the infrared transceiver. Each UART bit is 16 clocks wide. If the data to be transmitted is a logic 1 (High), the IR\_TxD signal remains Low (0) for the full 16-clock period. If the data to be transmitted is a logic 0, a 3-clock High (1) pulse is output following a 7-clock Low (0) period. Following the 3-clock High pulse, a 6-clock Low pulse completes the full 16-clock data period. Data transmission is shown in Figure 38. During data transmission, the IR receive function must be disabled by clearing the IR\_RxEN bit in the IR\_CTL reg to 0 to prevent transmitter-to-receiver crosstalk.

### Receive

Data received from the IR transceiver via the IR\_RxD signal is decoded by the endec and passed to the UART. The IR\_RxEN bit in the IR\_CTL Register must be set to enable the receiver decoder. The IrDA serial infrared (SIR) data format uses half duplex communication. Therefore, the UART must not be allowed to transmit while the receiver decoder is enabled. The UART Baud Rate Clock is used by the endec to generate the demodulated signal, RxD, that drives the UART. Each UART bit is 16 clocks wide. If the data to be received is a logic 1 (High), the IR\_RxD signal remains High (1) for the full 16-clock

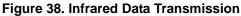

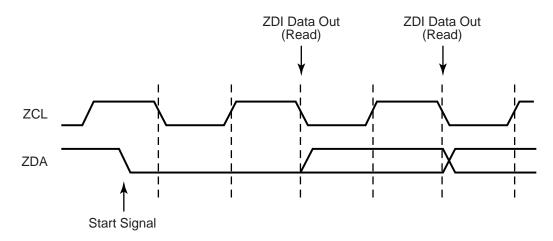

### **ZDI Single-Bit Byte Separator**

Following each 8-bit ZDI data transfer, a single-bit byte separator is used. To initiate a new ZDI command, the single-bit byte separator must be High (logic 1) to allow for a new ZDI start command to be sent. For all other cases, the single-bit byte separator is either Low (logic 0) or High (logic 1). When ZDI is configured to allow the CPU to accept external bus requests, the single-bit byte separator must be Low (logic 0) during all ZDI commands. This Low value indicates that ZDI is still operating and is not ready to relinquish the bus. The CPU does not accept the external bus requests until the single-bit byte separator.

| Bit              | Description                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>ZDI RESET | <b>ZDI System Reset</b><br>0: No action.                                                                                         |

| 201_112021       | <ol> <li>1: Initiate a RESET of the eZ80F91 MCU. This bit is automatically cleared at the end of<br/>the RESET event.</li> </ol> |

| [6:0]            | <b>Reserved</b><br>These bits are reserved and must be programmed to 0000000.                                                    |

### **ZDI Write Data Registers**

These three registers are used in the ZDI write-only register address space to store the data that is written when a write instruction is sent to the ZDI Read/Write Control Register (ZDI\_RW\_CTL). The ZDI Read/Write Control Register is located at ZDI address 16h immediately following the ZDI Write Data registers. As a result, the ZDI Master is allowed to write the data to {ZDI\_WR\_U, ZDI\_WR\_H, ZDI\_WR\_L} and the write command in one data transfer operation. See Table 139.

| Bit     | 7                                                                                                 | 6 | 5      | 4          | 3         | 2      | 1 | 0 |

|---------|---------------------------------------------------------------------------------------------------|---|--------|------------|-----------|--------|---|---|

| Field   |                                                                                                   |   | ZDI_WF | R_L, ZDI_W | R_H or ZD | I_WR_L |   |   |

| Reset   | U                                                                                                 | U | U      | U          | U         | U      | U | U |

| R/W     | W                                                                                                 | W | W      | W          | W         | W      | W | W |

| Address | ZDI_WR_U = 13h, ZDI_WR_H = 14h and ZDI_WR_L = 15h<br>in the ZDI Register write-only address space |   |        |            |           |        |   |   |

Note: U = undefined; W = write.

| Bit       | Description                                                                                 |

|-----------|---------------------------------------------------------------------------------------------|

| [7:0]     | ZDI Write Data                                                                              |

| ZDI_WR_L, | 00h-FFh: These registers contain the data that is written during execution of a write oper- |

| ZDI_WR_H, | ation defined by the ZDI_RW_CTL Register. The 24-bit data value is stored as                |

| or        | {ZDI_WR_U, ZDI_WR_H, ZDI_WR_L}. If less than 24 bits of data are required to com-           |

| ZDI_WR_L  | plete the required operation, the data is taken from the least-significant byte(s).         |

### **ZDI Read/Write Control Register**

The ZDI Read/Write Control Register is used in the ZDI write-only register address to read data from, write data to, and manipulate the CPU's registers or memory locations. When this register is written, the eZ80F91 device immediately performs the operation corresponding to the data value written as described in Table 140. When a read operation is executed via this register, the requested data values are placed in the ZDI Read Data registers {ZDI\_RD\_U, ZDI\_RD\_H, ZDI\_RD\_L}. When a write operation is executed via this

| Bit | Name      | Description                                                                                                                                                                                                                                                                                                                         |

|-----|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10  | RxCF      | 1 = The packet is a control frame.                                                                                                                                                                                                                                                                                                  |

| 9   | RxMcPkt   | 1 = The packet contains a multicast address.                                                                                                                                                                                                                                                                                        |

| 8   | RxBcPkt   | 1 = The packet contains a broadcast address.                                                                                                                                                                                                                                                                                        |

| 7   | RxVLAN    | 1 = The packet is a VLAN packet.                                                                                                                                                                                                                                                                                                    |

| 6   | RxUOpCode | 1 = An unsupported op code is indicated in the op code field of the Ethernet packet.                                                                                                                                                                                                                                                |

| 5   | RxLOOR    | 1 = The Type/Length field is out of range (larger than 1518 bytes).                                                                                                                                                                                                                                                                 |

| 4   | RxLCError | 1 = Type/Length field is not a Type field and it does not match the actual data byte length of the Ethernet packet. The data byte length is the number of bytes of data in the Ethernet packet between the Type/Length field and the FCS.                                                                                           |

| 3   | RxCodeV   | 1 = A code violation is detected. The PHY asserts Rx error (RxER).                                                                                                                                                                                                                                                                  |

| 2   | RxCEvent  | 1 = A carrier event is previously seen. This event is defined as $Rx$ error $RxER = 1$ , receive data valid ( $RxDV$ ) = 0 and receive data ( $RxD$ ) = Eh.                                                                                                                                                                         |

| 1   | RxDvEvent | 1 = A receive data (RxDV) event is previously seen. Indicates that the last Receive event is not long enough to be a valid packet.                                                                                                                                                                                                  |

| 0   | RxOVR     | 1 = A Receive overrun occurs in this packet. An overrun occurs when<br>all of the EMAC Receive buffers are in use and the Receive FIFO is full.<br>The hardware ignores all incoming packets until the EmaclStat Register<br>[Rx_Ovr] bit is cleared by the software. There is no indication as to how<br>many packets are ignored. |

### **EMAC** and the System Clock

Effective Ethernet throughput in any given system is dependent upon factors such as system clock speed, network protocol overhead, application complexity, and network traffic conditions at any given moment. The following information provides a general guideline about the effects of system clock speed on Ethernet operation.

The eZ80F91 ASSP's EMAC block performs a synchronous function that is designed to operate over a wide range of system clock frequencies. To understand its maximum data transfer capabilities at certain system operating frequencies, you must first understand the internal data bus bandwidth that is required under ideal conditions.

For 10BaseT Ethernet connectivity, the data rate is 10 Mbps, which equates to 1.25 Mbps. If the eZ80F91 ASSP is operating in FULL-DUPLEX Mode over 10BaseT, the data rate for RX data and TX data is 1.25 Mbps. Because raw data transfers at this rate consume a certain amount of CPU bandwidth, the CPU must support traffic from both directions as well as operate at a minimum clock frequency of (1.25 + 1.25) \* 2 = 5 MHz while transferring Ethernet packets to and from the physical layer.

### **EMAC Transmit Polling Timer Register**

This register sets the Transmit Polling Period in increments of TPTMR = SYSCLK  $\div$  256. Whenever this register is written, the status of the Transmit Buffer Descriptor is checked to determine if the EMAC owns the Transmit buffer. It then rechecks this status every TPTMR (calculated by TPTMR x EMAC\_PTMR[7:0]). The Transmit Polling Timer is disabled if this register is set to 00h (which also disables the transmitting of packets). If a transmission is in progress when EMAC\_PTMR is set to 00h, the transmission will complete. See Table 204.

| Bit         | 7           | 6     | 5   | 4    | 3    | 2   | 1   | 0   |

|-------------|-------------|-------|-----|------|------|-----|-----|-----|

| Field       |             |       |     | EMAC | PTMR | ľ   | ľ   | I   |

| Reset       | 0           | 0     | 0   | 0    | 0    | 0   | 0   | 0   |

| R/W         | R/W         | R/W   | R/W | R/W  | R/W  | R/W | R/W | R/W |

| Address     |             | 0040h |     |      |      |     |     |     |

| Note: R/W = | read/write. |       |     |      |      |     |     |     |

| Bit         | Descriptio  | n     |     |      |      |     |     |     |

#### Table 204. EMAC Transmit Polling Timer Register (EMAC\_PTMR)

| [7:0]     | Transmit Polling Timer                |

|-----------|---------------------------------------|

| EMAC_PTMR | 00h–FFh: The transmit polling period. |

### **EMAC Reset Control Register**

The bit values in the EMAC Reset Control Register, shown in Table 205, are not selfclearing bits. You are responsible for controlling their state.

#### Table 205. EMAC Reset Control Register (EMAC\_RST)

| Bit                                   | 7     | 6     | 5    | 4     | 3     | 2     | 1     | 0     |

|---------------------------------------|-------|-------|------|-------|-------|-------|-------|-------|

| Field                                 | Rese  | erved | SRST | HRTFN | HRRFN | HRTMC | HRRMC | HRMGT |

| Reset                                 | 0     | 0     | 1    | 0     | 0     | 0     | 0     | 0     |

| R/W                                   | R     | R     | R/W  | R/W   | R/W   | R/W   | R/W   | R/W   |

| Address                               | 0041h |       |      |       |       |       |       |       |

| Note: R - read only: R/W - read/write |       |       |      |       |       |       |       |       |

Note: R = read only; R/W = read/write.

| Higł | h Boundary  | y Pointer H | igh Byte R | egister (El | MAC_RHBI | P_H) |  |

|------|-------------|-------------|------------|-------------|----------|------|--|

|      | 5           | 4           | 3          | 2           | 1        | 0    |  |

|      | EMAC_RHBP_H |             |            |             |          |      |  |

0

R/W

0048h

0

R/W

0

R/W

0

R/W

#### Table 212, EMAC Receive H

0

R/W

0

R

| Addre | ess        |                        |

|-------|------------|------------------------|

| Note: | R = read o | nly, R/W = read/write. |

7

1

R

6

1

R

Bit

Field

Reset

R/W

| Bit         | Description                                                                                                                        |

|-------------|------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]       | Receive High Boundary Pointer High Byte                                                                                            |

| EMAC_RHBP_H | 00h-FFh: These bits represent the high byte of the two-byte EMAC Receive High                                                      |

|             | Boundary Pointer value, {EMAC_RHBP_H, EMAC_RHBP_L}. Bit 7 is bit 15 (msb) of the 16-bit value. Bit 0 is bit 8 of the 16-bit value. |

### **EMAC Receive Read Pointer High and Low Byte Registers**

The Receive Read Pointer Registers, shown in Tables 213 and 214, must be initialized to the EMAC\_BP value (i.e., the start of the Receive buffer). This register points to the address location in which the next Receive packet is read from. The EMAC\_BP[12:5] is loaded into this register whenever the EMAC\_RST [(HRRFN) is set to 1. The RxDMA block uses Emac\_Rrp[12:5] to compare to EmacRwp[12:5] for determining how many buffers remain. The result equates to the EmacBlksLeft Register.

| Field         EMAC_RRP_L           Reset         0         0         0         0         0         0 |       |  |  |  |

|------------------------------------------------------------------------------------------------------|-------|--|--|--|

| Reset 0 0 0 0 0 0 0                                                                                  |       |  |  |  |

|                                                                                                      | 0     |  |  |  |

| <b>R/W</b> R/W R/W R R R R R                                                                         | R     |  |  |  |

| Address 0049h                                                                                        | 0049h |  |  |  |

Note: R = read only, R/W = read/write.

| Bit        | Description                                                                                                                                                                                               |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]      | Receive Read Pointer Low Byte                                                                                                                                                                             |

| EMAC_RRP_L | 00h–FFh: These bits represent the low byte of the two-byte EMAC Receive Read<br>Pointer value, {EMAC_RRP_H, EMAC_RRP_L}. Bit 7 is bit 7 of the 16-bit value. Bit 0<br>is bit 0 (lsb) of the 16-bit value. |

divisor count 204 16-bit 179 DSR 188, 191 DSR0 13, 196 DSR1 16 DTACK 80 DTR 188, 191 DTR0 12, 196 DTR1 15

## Ε

EC0 17, 122, 125, 128 EC1 22, 122, 125, 128 Edge-Triggered Interrupts 50, 51 EI, Op Code Map 279 **EMAC 286** EMAC Address Filter Register 310 EMAC Boundary Pointer Register-Low and High Bytes 318 EMAC Boundary Pointer Register—Upper Byte 319 **EMAC Buffer Size Register 321** EMAC Configuration Register 1 298 EMAC Configuration Register 2 300 EMAC Configuration Register 3 301 EMAC Configuration Register 4 302 EMAC FIFO Data Register—Low and High Bytes 330 EMAC FIFO Flags Register 331 **EMAC** Functional Description 287 EMAC Hash Table Register 310 EMAC Interpacket Gap 304 EMAC Interpacket Gap Register 306 EMAC Interrupt Enable Register 322 EMAC Interrupt Status Register 324 EMAC Interrupts 291 EMAC Maximum Frame Length Register-Low and High Bytes 308 EMAC memory 288, 289 EMAC MII Management Register 311 EMAC MII Status Register 326 EMAC Non-Back-To-Back IPG Register—Part 1 307

EMAC Non-Back-To-Back IPG Register—Part 2 307 EMAC PHY Address Register 314 EMAC PHY Configuration Data Register-Low Byte 312 EMAC PHY Read Status Data Register-Low and High Bytes 325 EMAC PHY Unit Select Address Register 314 EMAC RAM 90, 91, 92, 93 EMAC Receive Blocks Left Register-Low and High Bytes 329 EMAC Receive High Boundary Pointer Register-Low and High Bytes 319 EMAC Receive Read Pointer Register-Low and High Bytes 320 EMAC Receive Write Pointer Register—High Byte 327 EMAC Receive Write Pointer Register—Low Byte 327 EMAC receiver interrupts 291 **EMAC Registers 296 EMAC Reset Control Register 315 EMAC Shared Memory Organization 292 EMAC Station Address Register 303** EMAC system interrupts 291 EMAC Test Register 296 EMAC Transmit Lower Boundary Pointer Register-Low and High Bytes 317 EMAC Transmit Pause Timer Value Register-Low and High Bytes 304 EMAC Transmit Polling Timer Register 315 EMAC Transmit Read Pointer Register-High Byte 328 EMAC Transmit Read Pointer Register-Low Byte 328 EMAC transmitter interrupts 291 EMACMII module 286 Enabling and Disabling the WDT 112 endec 193, 194, 196, 197 IrDA 43 signal pins 196 ENDEC Mode 301, 305 **Erasing Flash Memory 98** Ethernet Media Access Controller 286

buffers 45 SCK 18, 199, 200 idle state 200 pin 201, 205 receive edge 200 signal 201 transmit edge 200 SCL 19, 209, 210, 211, 228 line 212, 214 SCLK 38, 146, 265, 266, 267, 312 periods 151 SDA 19, 209, 210, 211, 220 line 213 see system reset 8 serial bus, SPI 207, 208 serial clock 209  $I^{2}C$  19 SPI 18, 199, 200 serial data 199, 209  $I^{2}C 19$ Serial Peripheral Interface 1 serial peripheral interface 43, 55, 59, 198, 199, 201 flag 207, 208 Functional Description 201 Setting Timer Duration 118 SINGLE PASS Mode 117, 119, 120, 128 Single-Byte I/O Write 96 SLA 216, 217, 222, 278 Op Code Map 280, 284, 285 SLAVE Mode 209, 219, 221, 222, 224, 227 **SPI 201** Slave Receive 219 **SLAVE RECEIVE Mode 209** Slave Select 199 Slave Transmit 219 SLAVE TRANSMIT Mode 209, 219, 224 SLEEP Mode 1, 41, 170, 244, 252 sleep-mode recovery 170 reset 171 software break point instruction 256 Specialty Timer Modes 122 SPI Baud Rate Generator 202 Registers-Low Byte and High Byte 204 SPI Control Register 205

SPI data rate 203 SPI Flags 202 SPI interrupt service routine 55 SPI master device 19, 203 SPI MASTER Mode 201 SPI Mode 17 SPI Receive Buffer Register 208 SPI Registers 203 SPI serial bus 207 SPI serial clock 18 SPI Signals 199 SPI slave device 19 SPI SLAVE Mode 201 SPI Status Register 202, 206 SPI Transmit Shift Register 202, 203, 207 SPIF status bit—see serial peripheral interface flag 207 SPIF—see serial peripheral interface flag 201, 206 SRA 278 Op Code Map 280, 284 SRAM 1, 101, 230, 327, 354 internal Ethernet 292 SS—see Slave Select 17, 199, 200, 201, 203, 205 **STA 224** STANDARD Mode 209 Standard VHDL Package STD\_1149\_1\_2001 259 Start and Stop Conditions 210 start condition 212, 226 starting program counter 56, 57 stop condition 220, 224, 225 supply voltage 2, 39, 48, 209, 267, 336, 337 Switching Between Bus Modes 82 system clock 38, 41, 42, 43, 44, 49, 50, 111, 114, 121, 123, 128, 146, 178, 202, 228, 229, 237, 257, 266, 289, 351 cycle 73, 76, 118 cycle time 343 cycles 9, 65, 68, 69, 73, 76, 80, 112, 257 divider 128 fall time 343 frequency 97, 98, 102, 103, 118, 178, 203, 231 high-frequency 202 internal 66 high time 343

365