Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                  |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 21                                                                        |

| Program Memory Size        | 24KB (12K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 1408 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 5x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2539-e-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-2: PIC18F2X39 PINOUT I/O DESCRIPTIONS | TABLE 1-2: |

|-----------------------------------------------|------------|

|-----------------------------------------------|------------|

| Dia Mara             | Pin Number |           | Pin Buffer |               | Description                                                                             |  |  |  |

|----------------------|------------|-----------|------------|---------------|-----------------------------------------------------------------------------------------|--|--|--|

| Pin Name             | DIP        | SOIC      | Туре       | Туре          | Description                                                                             |  |  |  |

| MCLR/Vpp             | 1          | 1         |            |               | Master Clear (input) or high voltage ICSP programming                                   |  |  |  |

|                      |            |           |            | <b>oT</b>     | enable pin.                                                                             |  |  |  |

| MCLR                 |            |           | Ι          | ST            | Master Clear (Reset) input. This pin is an active low RESET to the device.              |  |  |  |

| VPP                  |            |           | I.         | ST            | High voltage ICSP programming enable pin.                                               |  |  |  |

| NC                   |            |           |            |               | These pins should be left unconnected.                                                  |  |  |  |

| OSC1/CLKI            | 9          | 9         |            |               | Oscillator crystal or external clock input.                                             |  |  |  |

| OSC1                 | Ŭ          | Ŭ         | Ι          | CMOS          | Oscillator crystal input or external clock source input.                                |  |  |  |

| CLKI                 |            |           | I          | CMOS          | External clock source input. Always associated with                                     |  |  |  |

|                      |            |           |            |               | pin function OSC1. (See related OSC1/CLKI,                                              |  |  |  |

|                      |            |           |            |               | OSC2/CLKO pins.)                                                                        |  |  |  |

| OSC2/CLKO/RA6        | 10         | 10        | ~          |               | Oscillator crystal or clock output.                                                     |  |  |  |

| OSC2                 |            |           | 0          | —             | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. |  |  |  |

| CLKO                 |            |           | 0          | _             | In EC mode, OSC2 pin outputs CLKO which has 1/4                                         |  |  |  |

|                      |            |           | -          |               | the frequency of OSC1, and denotes the instruction                                      |  |  |  |

|                      |            |           |            |               | cycle rate.                                                                             |  |  |  |

| RA6                  |            |           | I/O        | TTL           | General purpose I/O pin.                                                                |  |  |  |

|                      |            |           |            |               | PORTA is a bi-directional I/O port.                                                     |  |  |  |

| RA0/AN0              | 2          | 2         |            |               |                                                                                         |  |  |  |

| RA0                  |            |           | I/O        | TTL           | Digital I/O.                                                                            |  |  |  |

| AN0                  |            |           | I          | Analog        | Analog input 0.                                                                         |  |  |  |

| RA1/AN1              | 3          | 3         |            |               |                                                                                         |  |  |  |

| RA1<br>AN1           |            |           | I/O<br>I   | TTL           | Digital I/O.<br>Analog input 1.                                                         |  |  |  |

|                      |            |           | 1          | Analog        |                                                                                         |  |  |  |

| RA2/AN2/VREF-<br>RA2 | 4          | 4         | I/O        | TTL           | Digital I/O.                                                                            |  |  |  |

| AN2                  |            |           | "O         | Analog        | Analog input 2.                                                                         |  |  |  |

| VREF-                |            |           | I          | Analog        | A/D Reference Voltage (Low) input.                                                      |  |  |  |

| RA3/AN3/VREF+        | 5          | 5         |            | č             |                                                                                         |  |  |  |

| RA3                  | -          | _         | I/O        | TTL           | Digital I/O.                                                                            |  |  |  |

| AN3                  |            |           | I          | Analog        | Analog input 3.                                                                         |  |  |  |

| VREF+                |            |           | Ι          | Analog        | A/D Reference Voltage (High) input.                                                     |  |  |  |

| RA4/T0CKI            | 6          | 6         |            |               |                                                                                         |  |  |  |

| RA4                  |            |           | I/O        | ST/OD         | Digital I/O. Open drain when configured as output.                                      |  |  |  |

|                      | _          | _         | I          | ST            | Timer0 external clock input.                                                            |  |  |  |

| RA5/AN4/SS/LVDIN     | 7          | 7         | 1/0        | דדו           | Digital I/O                                                                             |  |  |  |

| RA5<br>AN4           |            |           | I/O<br>I   | TTL<br>Analog | Digital I/O.<br>Analog input 4.                                                         |  |  |  |

| SS                   |            |           | i          | ST            | SPI Slave Select input.                                                                 |  |  |  |

| LVDIN                |            |           | I          | Analog        | Low Voltage Detect input.                                                               |  |  |  |

| RA6                  |            |           |            | -             | See the OSC2/CLKO/RA6 pin.                                                              |  |  |  |

| Legend: TTL = TTL    | compa      | tible inp | ut         |               | CMOS = CMOS compatible input or output                                                  |  |  |  |

| ST = Schr            | nitt Trig  |           |            | CMOS leve     | ls I = Input                                                                            |  |  |  |

| O = Outp             | out        |           |            |               | P = Power                                                                               |  |  |  |

O = Output OD = Open Drain (no P diode to VDD)

© 2002-2013 Microchip Technology Inc.

| TABLE 1-3: | PIC18F4X39 PINOUT I/O DESCRIPTIONS (CONTINUED) |

|------------|------------------------------------------------|

|------------|------------------------------------------------|

| Pin Name                         | Pi  | Pin Number |    |                 | Buffer         | Description                                                                                  |  |  |  |

|----------------------------------|-----|------------|----|-----------------|----------------|----------------------------------------------------------------------------------------------|--|--|--|

| Pin Name                         | DIP | QFN TQFP   |    | Туре Туре       |                | Description                                                                                  |  |  |  |

|                                  |     |            |    |                 |                | PORTC is a bi-directional I/O port.                                                          |  |  |  |

| RC0/T13CKI<br>RC0<br>T13CKI      | 15  | 34         | 32 | I/O<br>I        | ST<br>ST       | Digital I/O.<br>Timer1/Timer3 external clock input.                                          |  |  |  |

| RC3/SCK/SCL<br>RC3               | 18  | 37         | 37 | I/O             | ST             | Digital I/O.                                                                                 |  |  |  |

| SCK                              |     |            |    | I/O<br>I/O      | ST             | Synchronous serial clock input/output for SPI mode.                                          |  |  |  |

| SCL                              |     |            |    | I/O             | ST             | Synchronous serial clock input/output for I <sup>2</sup> C mode.                             |  |  |  |

| RC4/SDI/SDA<br>RC4<br>SDI<br>SDA | 23  | 42         | 42 | I/O<br>I<br>I/O | ST<br>ST<br>ST | Digital I/O.<br>SPI Data in.<br>I <sup>2</sup> C Data I/O.                                   |  |  |  |

| RC5/SDO<br>RC5<br>SDO            | 24  | 43         | 43 | I/O<br>O        | ST<br>—        | Digital I/O.<br>SPI Data out.                                                                |  |  |  |

| RC6/TX/CK<br>RC6<br>TX<br>CK     | 25  | 44         | 44 | I/O<br>O<br>I/O | ST<br>—<br>ST  | Digital I/O.<br>USART Asynchronous Transmit.<br>USART Synchronous Clock (see related RX/DT). |  |  |  |

| RC7/RX/DT<br>RC7<br>RX<br>DT     | 26  | 1          | 1  | I/O<br>I<br>I/O | ST<br>ST<br>ST | Digital I/O.<br>USART Asynchronous Receive.<br>USART Synchronous Data (see related TX/CK).   |  |  |  |

| PWM1                             | 17  | 35         | 36 | 0               | _              | PWM Channel 1 (motor control) output.                                                        |  |  |  |

| PWM2                             | 16  | 36         | 35 | 0               | —              | PWM Channel 2 (motor control) output.                                                        |  |  |  |

| Legend: TTL = TTI                |     |            |    | MOST            |                | CMOS = CMOS compatible input or output                                                       |  |  |  |

ST = Schmitt Trigger input with CMOS levels

OD = Open Drain (no P diode to VDD)

= Input

l P

| Pin Name                                 | Pi               | Pin Number |      |      | Buffer    | Description                                                                                                                                                                         |  |  |  |

|------------------------------------------|------------------|------------|------|------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name                                 | DIP              | QFN        | TQFP | Туре | Туре      | Description                                                                                                                                                                         |  |  |  |

|                                          |                  |            |      |      |           | PORTD is a bi-directional I/O port, or a Parallel Slave<br>Port (PSP) for interfacing to a microprocessor port.<br>These pins have TTL input buffers when PSP module<br>is enabled. |  |  |  |

| RD0/PSP0<br>RD0<br>PSP0                  | 19               | 38         | 38   | I/O  | ST<br>TTL | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                           |  |  |  |

| RD1/PSP1<br>RD1<br>PSP1                  | 20               | 39         | 39   | I/O  | ST<br>TTL | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                           |  |  |  |

| RD2/PSP2<br>RD2<br>PSP2                  | 21               | 40         | 40   | I/O  | ST<br>TTL | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                           |  |  |  |

| RD3/PSP3<br>RD3<br>PSP3                  | 22               | 41         | 41   | I/O  | ST<br>TTL | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                           |  |  |  |

| RD4/PSP4<br>RD4<br>PSP4                  | 27               | 2          | 2    | I/O  | ST<br>TTL | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                           |  |  |  |

| RD5/PSP5<br>RD5<br>PSP5                  | 28               | 3          | 3    | I/O  | ST<br>TTL | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                           |  |  |  |

| RD6/PSP6<br>RD6<br>PSP6                  | 29               | 4          | 4    | I/O  | ST<br>TTL | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                           |  |  |  |

| RD7/PSP7<br>RD7<br>PSP7                  | 30               | 5          | 5    | I/O  | ST<br>TTL | Digital I/O.<br>Parallel Slave Port Data.                                                                                                                                           |  |  |  |

| Legend: TTL = TTL<br>ST = Sch<br>O = Out | mitt Trig<br>put | ger inpu   |      |      | evels     | CMOS = CMOS compatible input or output<br>I = Input<br>P = Power                                                                                                                    |  |  |  |

O = Output OD = Open Drain (no P diode to VDD)

$\ensuremath{\textcircled{}^{\odot}}$  2002-2013 Microchip Technology Inc.

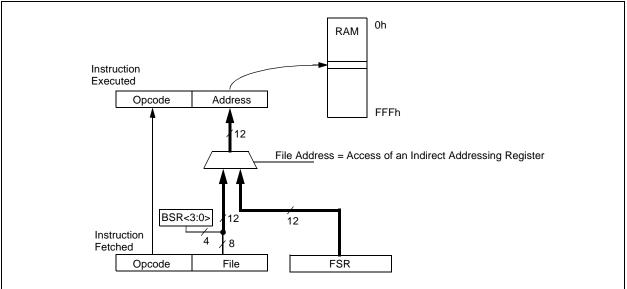

## 4.9 Data Memory Organization

The data memory is implemented as static RAM. Each register in the data memory has a 12-bit address, allowing up to 4096 bytes of data memory. The data memory map is divided into 16 banks that contain 256 bytes each. The lower 4 bits of the Bank Select Register (BSR<3:0>) select which bank will be accessed. The upper 4 bits for the BSR are not implemented.

The data memory contains Special Function Registers (SFRs) and General Purpose Registers (GPRs). The SFRs are used for control and status of the controller and peripheral functions, while GPRs are used for data storage and scratch pad operations in the user's application. The SFRs start at the last location of Bank 15 (FFFh) and extend downwards. Any remaining space beyond the SFRs in the Bank may be implemented as GPRs. GPRs start at the first location of Bank 0 and grow upwards. Any read of an unimplemented location will read as '0's.

The organization of the data memory space for these devices is shown in Figure 4-5 and Figure 4-6. PIC18FX439 devices have 640 bytes of data RAM, extending from Bank 0 to Bank 2 (000h through 27Fh). The block of 128 bytes above this to the top of the bank (280h to 2FFh) is used as data memory for the Motor Control kernel, and is not available to the user. Reading these locations will return random information that reflects the kernel's "scratch" data. Modifying the data in these locations may disrupt the operation of the ProMPT kernel.

PIC18FX539 devices have 1408 bytes of data RAM, extending from Bank 0 to Bank 5 (000h through 57Fh). As with the PIC18FX439 devices, the block of 128 bytes above this to the end of the bank (580h to 5FFh) is used by the Motor Control kernel.

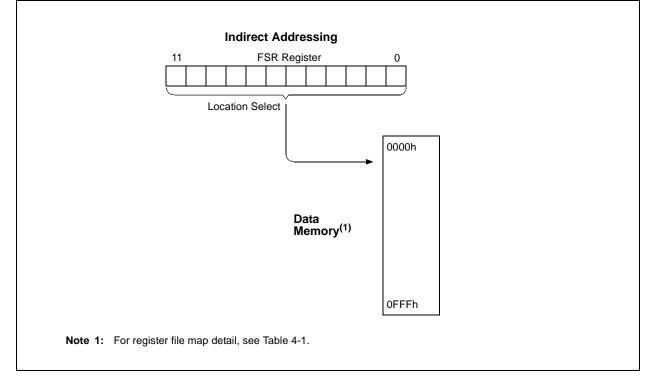

The entire data memory may be accessed directly or indirectly. Direct addressing may require the use of the BSR register. Indirect addressing requires the use of a File Select Register (FSRn) and a corresponding Indirect File Operand (INDFn). Each FSR holds a 12-bit address value that can be used to access any location in the Data Memory map without banking.

The instruction set and architecture allow operations across all banks. This may be accomplished by indirect addressing, or by the use of the MOVFF instruction. The MOVFF instruction is a two-word/two-cycle instruction that moves a value from one register to another.

To ensure that commonly used registers (SFRs and select GPRs) can be accessed in a single cycle, regardless of the current BSR values, an Access Bank is implemented. A segment of Bank 0 and a segment of Bank 15 comprise the Access RAM. Section 4.10 provides a detailed description of the Access RAM.

### 4.9.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly or indirectly. Indirect addressing operates using a File Select Register and corresponding Indirect File Operand. The operation of indirect addressing is shown in Section 4.12.

Enhanced MCU devices may have banked memory in the GPR area. GPRs are not initialized by a Power-on Reset and are unchanged on all other RESETS.

Data RAM is available for use as GPR registers by all instructions. The top half of Bank 15 (F80h to FFFh) contains SFRs. All other banks of data memory contain GPR registers, starting with Bank 0.

### 4.9.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 4-1 and Table 4-2.

The SFRs can be classified into two sets; those associated with the "core" function and those related to the peripheral functions. Those registers related to the "core" are described in this section, while those related to the operation of the peripheral features are described in the section of that peripheral feature.

The SFRs are typically distributed among the peripherals whose functions they control. The unused SFR locations will be unimplemented and read as '0's. See Table 4-1 for addresses for the SFRs.

| Note: | In this chapter and throughout this docu-<br>ment, certain SFR names and individual |  |  |  |  |  |  |

|-------|-------------------------------------------------------------------------------------|--|--|--|--|--|--|

|       | bits are marked with an asterisk (*). This                                          |  |  |  |  |  |  |

|       | denotes registers that are not implemented                                          |  |  |  |  |  |  |

|       |                                                                                     |  |  |  |  |  |  |

|       | in PIC18FXX39 devices, but whose names                                              |  |  |  |  |  |  |

|       | are retained to maintain compatibility with                                         |  |  |  |  |  |  |

|       | PIC18FXX2 devices. The designated bits                                              |  |  |  |  |  |  |

|       | within these registers are reserved a                                               |  |  |  |  |  |  |

|       | may be used by certain modules or the                                               |  |  |  |  |  |  |

|       | Motor Control kernel. Users should not                                              |  |  |  |  |  |  |

|       | write to these registers or alter these bit                                         |  |  |  |  |  |  |

|       | values. Failure to do this may result in                                            |  |  |  |  |  |  |

|       | erratic microcontroller operation.                                                  |  |  |  |  |  |  |

## FIGURE 4-9: INDIRECT ADDRESSING

|         | U-0                         | U-0         | U-0            | R/W-1               | R/W-1                | R/W-1                | R/W-1                 | U-1   |

|---------|-----------------------------|-------------|----------------|---------------------|----------------------|----------------------|-----------------------|-------|

|         |                             |             |                | EEIP <sup>(1)</sup> | BCLIP <sup>(1)</sup> | LVDIP <sup>(1)</sup> | TMR3IP <sup>(1)</sup> |       |

|         | bit 7                       |             |                |                     |                      |                      |                       | bit 0 |

|         |                             |             |                |                     |                      |                      |                       |       |

| bit 7-5 | Unimpleme                   |             |                |                     |                      |                      |                       |       |

| bit 4   | EEIP <sup>(1)</sup> : Da    | ta EEPRON   | //FLASH W      | rite Operatio       | on Interrupt F       | Priority bit         |                       |       |

|         | 1 = High pri                | ,           |                |                     |                      |                      |                       |       |

|         | 0 = Low prive               | -           |                |                     |                      |                      |                       |       |

| bit 3   | BCLIP <sup>(1)</sup> : B    |             | n Interrupt P  | riority bit         |                      |                      |                       |       |

|         | 1 = High pri                | ,           |                |                     |                      |                      |                       |       |

|         | 0 = Low prive               | -           |                |                     |                      |                      |                       |       |

| bit 2   | LVDIP <sup>(1)</sup> : L    | -           | Detect Inter   | rupt Priority       | bit                  |                      |                       |       |

|         | 1 = High prive              | •           |                |                     |                      |                      |                       |       |

|         | 0 = Low priet               | -           |                |                     |                      |                      |                       |       |

| bit 1   |                             |             | rflow Interru  | pt Priority bi      | t                    |                      |                       |       |

|         | 1 = High pri<br>0 = Low pri | •           |                |                     |                      |                      |                       |       |

| h:+ 0   | •                           | •           | d a a (4)      |                     |                      |                      |                       |       |

| bit 0   | Unimpleme                   | entea: Kea  |                |                     |                      |                      |                       |       |

|         | Note 1:                     | Maintain th | is bit cleared | d (= 0).            |                      |                      |                       |       |

|         |                             |             |                | . ,                 |                      |                      |                       |       |

| REGISTER 8-9: | <b>IPR2: PERIPHERAL INTERRUPT PRIORITY REGISTER 2</b> |

|---------------|-------------------------------------------------------|

|---------------|-------------------------------------------------------|

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

NOTES:

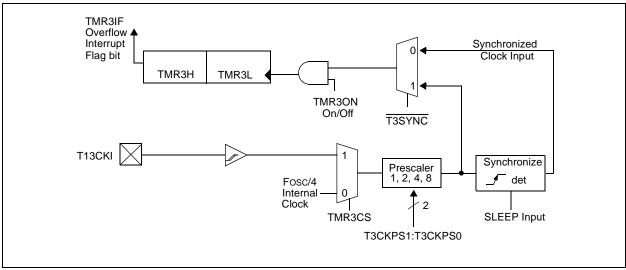

## 13.1 Timer3 Operation

Timer3 can operate in one of these modes:

- · As a timer

- As a synchronous counter

- As an asynchronous counter

## FIGURE 13-1: TIMER3 BLOCK DIAGRAM

The Operating mode is determined by the clock select bit, TMR3CS (T3CON<1>). When TMR3CS = 0, Timer3 increments every instruction cycle. When TMR3CS = 1, Timer3 increments on every rising edge of the Timer1 external clock input.

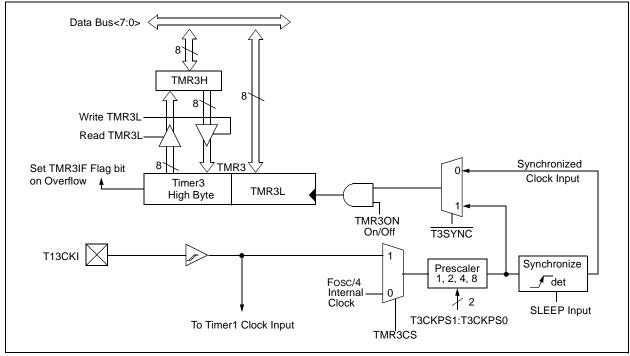

### FIGURE 13-2: TIMER3 BLOCK DIAGRAM CONFIGURED IN 16-BIT READ/WRITE MODE

# 14.4 Developing Applications Using the Motor Control Kernel

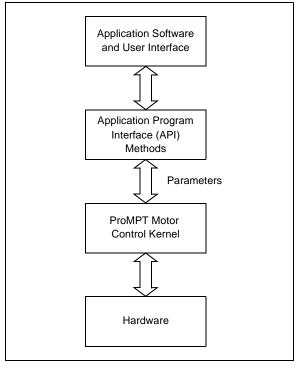

The Motor Control kernel allows users to develop their applications without having knowledge of motor control. The key parameters of the motor control kernel can be set and read through the Application Program Interface (API) methods discussed in the previous section.

The overall application can be thought of as a protocol stack, as shown in Figure 14-3. In this case, the API methods reside between the user's application and the ProMPT kernel, and are used to exchange parameter values. The motor control kernel sets the PWM duty cycles based on the inputs from the application software.

A typical motor control routine is shown in Example 14-1. In this case, the motor will run at 20 Hz for 10 seconds, accelerate to 60 Hz at the rate of 10 Hz/s, remain at 60 Hz for 20 seconds, and finally stop.

### FIGURE 14-3:

### LAYERS OF THE MOTOR CONTROL ARCHITECTURE STACK

## EXAMPLE 14-1: MOTOR CONTROL ROUTINE USING THE ProMPT APIS

```

Void main()

unsigned char i;

unsigned char j;

ProMPT_Init(0);

// Initialize the ProMPT block

i = ProMPT_SetFrequency(10);

// Set motor frequency to 10Hz

for (i=0;i<161;i++)</pre>

// Set counter for 10 sec @ 1/16 sec per tick

{

j = ProMPT_Tick(void);

// Tick of 1/16 sec

ProMPT_ClearTick(void);

// Clearing the Tick flag

}

// Set acceleration rate to 10 Hz/sec

ProMPT_SetAccelRate(10);

i = ProMPT_SetFrequency(60);

// Set motor frequency to 60 Hz

for (i=0;i<161;i++)</pre>

// Set counter for 20 Sec @ 1/16 sec per tick

// (2 loops of 10 Sec each)

{

// Tick of 1/16 Sec

j = ProMPT_Tick(void);

// Clearing the Tick flag

ProMPT_ClearTick(void);

j = ProMPT_Tick(void);

// Tick of 1/16 Sec

ProMPT_ClearTick(void);

// Clearing the Tick flag

i = ProMPT SetFrequency(0);

// Set motor frequency to 0 Hz (stop)

while(1);

// End of the task

```

### 16.4.14 SLEEP OPERATION

While in SLEEP mode, the I<sup>2</sup>C module can receive addresses or data, and when an address match or complete byte transfer occurs, wake the processor from SLEEP (if the MSSP interrupt is enabled).

### 16.4.15 EFFECT OF A RESET

A RESET disables the MSSP module and terminates the current transfer.

### 16.4.16 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the START and STOP conditions allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a RESET, or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit (SSPSTAT<4>) is set, or the bus is IDLE, with both the S and P bits clear. When the bus is busy, enabling the SSP interrupt will generate the interrupt when the STOP condition occurs.

In multi-master operation, the SDA line must be monitored for arbitration, to see if the signal level is the expected output level. This check is performed in hardware, with the result placed in the BCLIF bit.

The states where arbitration can be lost are:

- Address Transfer

- Data Transfer

- A START Condition

- A Repeated START Condition

- An Acknowledge Condition

### 16.4.17 MULTI -MASTER COMMUNICATION, BUS COLLISION, AND BUS ARBITRATION

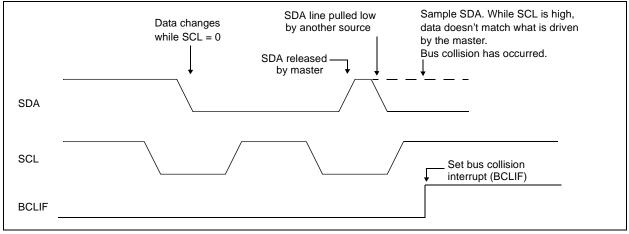

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA, by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin = '0', then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag BCLIF and reset the I<sup>2</sup>C port to its IDLE state (Figure 16-25).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are de-asserted, and the SSPBUF can be written to. When the user services the bus collision Interrupt Service Routine, and if the  $I^2C$  bus is free, the user can resume communication by asserting a START condition.

If a START, Repeated START, STOP, or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are de-asserted, and the respective control bits in the SSPCON2 register are cleared. When the user services the bus collision Interrupt Service Routine, and if the  $l^2C$  bus is free, the user can resume communication by asserting a START condition.

The master will continue to monitor the SDA and SCL pins. If a STOP condition occurs, the SSPIF bit will be set.

A write to the SSPBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of START and STOP conditions allows the determination of when the bus is free. Control of the  $l^2C$  bus can be taken when the P bit is set in the SSPSTAT register, or the bus is IDLE and the S and P bits are cleared.

### FIGURE 16-25: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

© 2002-2013 Microchip Technology Inc.

## 19.0 LOW VOLTAGE DETECT

In many applications, the ability to determine if the device voltage (VDD) is below a specified voltage level is a desirable feature. A window of operation for the application can be created, where the application software can do "housekeeping tasks" before the device voltage exits the valid operating range. This can be done using the Low Voltage Detect module.

This module is a software programmable circuitry, where a device voltage trip point can be specified. When the voltage of the device becomes lower then the specified point, an interrupt flag is set. If the interrupt is enabled, the program execution will branch to the interrupt vector address and the software can then respond to that interrupt source. The Low Voltage Detect circuitry is completely under software control. This allows the circuitry to be "turned off" by the software, which minimizes the current consumption for the device.

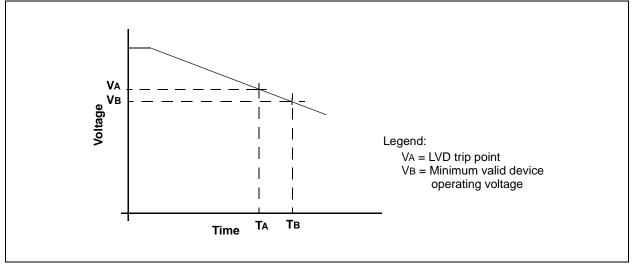

Figure 19-1 shows a possible application voltage curve (typically for batteries). Over time, the device voltage decreases. When the device voltage equals voltage VA, the LVD logic generates an interrupt. This occurs at time TA. The application software then has the time, until the device voltage is no longer in valid operating range, to shutdown the system. Voltage point VB is the minimum valid operating voltage specification. This occurs at time TB. The difference TB – TA is the total time for shutdown.

The block diagram for the LVD module is shown in Figure 19-2. A comparator uses an internally generated reference voltage as the set point. When the selected tap output of the device voltage crosses the set point (is lower than), the LVDIF bit is set.

Each node in the resistor divider represents a "trip point" voltage. The "trip point" voltage is the minimum supply voltage level at which the device can operate before the LVD module asserts an interrupt. When the supply voltage is equal to the trip point, the voltage tapped off of the resistor array is equal to the 1.2V internal reference voltage generated by the voltage reference module. The comparator then generates an interrupt signal setting the LVDIF bit. This voltage is software programmable to any one of 16 values (see Figure 19-2). The trip point is selected by programming the LVDL3:LVDL0 bits (LVDCON<3:0>).

## 21.1 Instruction Set

| ADD   | DLW                                                    | ADD liter                              | al to W                  |     |            |      |  |  |  |  |

|-------|--------------------------------------------------------|----------------------------------------|--------------------------|-----|------------|------|--|--|--|--|

| Synt  | ax:                                                    | [ <i>label</i> ] A                     | [ <i>label</i> ] ADDLW k |     |            |      |  |  |  |  |

| Ope   | rands:                                                 | $0 \le k \le 25$                       | 5                        |     |            |      |  |  |  |  |

| Ope   | ration:                                                | (W) + k $\rightarrow$                  | W                        |     |            |      |  |  |  |  |

| Statu | us Affected:                                           | N, OV, C,                              | DC, Z                    |     |            |      |  |  |  |  |

| Enco  | oding:                                                 | 0000                                   | 1111                     | kkk | k          | kkkk |  |  |  |  |

| Des   | cription:                                              | The conte<br>8-bit litera<br>placed in | I 'k' and                |     |            |      |  |  |  |  |

| Wor   | ds:                                                    | 1                                      | 1                        |     |            |      |  |  |  |  |

| Cycl  | es:                                                    | 1                                      | 1                        |     |            |      |  |  |  |  |

| QC    | ycle Activity:                                         |                                        |                          |     |            |      |  |  |  |  |

|       | Q1                                                     | Q2                                     | Q3                       |     | Q4         |      |  |  |  |  |

|       | Decode                                                 | Read<br>literal 'k'                    | Process<br>Data          |     | Write to W |      |  |  |  |  |

|       | nple:<br>Before Instru<br>W =<br>After Instruct<br>W = | ox10                                   | )x15                     |     |            |      |  |  |  |  |

| ADDWF             | ADD W t                                                                       | o f                                               |                           |                       |                              |

|-------------------|-------------------------------------------------------------------------------|---------------------------------------------------|---------------------------|-----------------------|------------------------------|

| Syntax:           | [ label ] A                                                                   | DDWF                                              | f [,                      | d [,a                 | ]                            |

| Operands:         | $0 \le f \le 25$<br>$d \in [0,1]$<br>$a \in [0,1]$                            | 55                                                |                           |                       |                              |

| Operation:        | (W) + (f)                                                                     | $\rightarrow$ dest                                |                           |                       |                              |

| Status Affected:  | N, OV, C                                                                      | , DC, Z                                           |                           |                       |                              |

| Encoding:         | 0010                                                                          | 01da                                              | fff                       | f                     | ffff                         |

| Description:      | Add W to<br>result is s<br>result is s<br>(default).<br>Bank will<br>BSR is u | stored in<br>stored ba<br>If 'a' is 0<br>be seled | W. If<br>ick in<br>), the | 'd' is<br>regi<br>Acc | s 1, the<br>ister 'f'<br>ess |

| Words:            | 1                                                                             |                                                   |                           |                       |                              |

| Cycles:           | 1                                                                             |                                                   |                           |                       |                              |

| Q Cycle Activity: |                                                                               |                                                   |                           |                       |                              |

| Q1                | Q2                                                                            | Q                                                 | 3                         |                       | Q4                           |

| Decode            | Read<br>register 'f'                                                          | Proce<br>Data                                     |                           |                       | /rite to<br>stination        |

| Example:          | ADDWF                                                                         | REG,                                              | 0, 0                      |                       |                              |

| Before Instru     | uction                                                                        |                                                   |                           |                       |                              |

| W<br>REG          | = 0x17<br>= 0xC2                                                              |                                                   |                           |                       |                              |

| After Instruc     | tion                                                                          |                                                   |                           |                       |                              |

| W                 | = 0xD9                                                                        |                                                   |                           |                       |                              |

0xC2

=

REG

| BCF               | Bit Clear                                                                                | f                               |                                      |                      |

|-------------------|------------------------------------------------------------------------------------------|---------------------------------|--------------------------------------|----------------------|

| Syntax:           | [ <i>label</i> ] B                                                                       | CF f,                           | b[,a]                                |                      |

| Operands:         | $0 \le f \le 255$<br>$0 \le b \le 7$<br>$a \in [0,1]$                                    | 5                               |                                      |                      |

| Operation:        | $0 \rightarrow f < b >$                                                                  |                                 |                                      |                      |

| Status Affected:  | None                                                                                     |                                 |                                      |                      |

| Encoding:         | 1001                                                                                     | bbba                            | ffff                                 | ffff                 |

| Description:      | Bit 'b' in re<br>is 0, the A<br>selected, o<br>If 'a' = 1, t<br>selected a<br>(default). | ccess B<br>overridir<br>hen the | ank will b<br>ng the BS<br>bank will | be<br>R value.<br>be |

| Words:            | 1                                                                                        |                                 |                                      |                      |

| Cycles:           | 1                                                                                        |                                 |                                      |                      |

| Q Cycle Activity: |                                                                                          |                                 |                                      |                      |

| Q1                | Q2                                                                                       | Q3                              | 3                                    | Q4                   |

| Decode            | Read<br>register 'f'                                                                     | Proce<br>Data                   |                                      | Write<br>gister 'f'  |

| Example:          | BCF F                                                                                    | LAG_RE                          | G, 7, (                              | D                    |

| After Instruct    | $\Xi G = 0xC7$                                                                           |                                 |                                      |                      |

|                                             |                                     | Branch if                                                                                    |                                                    |                                       |                     |                    |

|---------------------------------------------|-------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------|---------------------------------------|---------------------|--------------------|

| Syntax:                                     |                                     | [ <i>label</i> ] B                                                                           | [ <i>label</i> ] BN n                              |                                       |                     |                    |

| Operands                                    | S:                                  | -128 ≤ n ≤                                                                                   | $\textbf{-128} \leq n \leq 127$                    |                                       |                     |                    |

| Operation                                   | ו:                                  | if negative bit is '1' (PC) + 2 + 2n $\rightarrow$ PC                                        |                                                    |                                       |                     |                    |

| Status Aff                                  | fected:                             | None                                                                                         |                                                    |                                       |                     |                    |

| Encoding                                    | :                                   | 1110                                                                                         | 0110                                               | nnn                                   | n :                 | nnn                |

|                                             |                                     | program w<br>The 2's cc<br>added to t<br>have incre<br>instruction<br>PC+2+2n.<br>a two-cycl | mpleme<br>he PC.<br>ementec<br>, the ne<br>This ir | ent nui<br>Since<br>I to fet<br>w add | the F<br>ch the     | PC<br>e n<br>will  |

|                                             |                                     |                                                                                              |                                                    |                                       |                     |                    |

| Words:                                      |                                     | 1                                                                                            |                                                    |                                       |                     |                    |

| Words:<br>Cycles:                           |                                     | 1<br>1(2)                                                                                    |                                                    |                                       |                     |                    |

|                                             | Activity                            | 1(2)                                                                                         |                                                    |                                       |                     |                    |

| Cycles:<br>Q Cycle<br>If Jump:              | Activity<br>Q1                      | 1(2)                                                                                         | Q3                                                 | 3                                     | C                   | Q4                 |

| Cycles:<br>Q Cycle<br>If Jump:              | _                                   | 1(2)                                                                                         | Q3<br>Proce<br>Data                                | SS                                    | C<br>Write          |                    |

| Cycles:<br>Q Cycle<br>If Jump:              | Q1<br>code<br>No                    | 1(2)<br>Q2<br>Read literal<br>'n'<br>No                                                      | Proce<br>Data<br>No                                | ess<br>a                              | Write               | to F<br>lo         |

| Cycles:<br>Q Cycle<br>If Jump:<br>De        | Q1<br>ecode<br>No<br>eration        | 1(2)<br>Q2<br>Read literal<br>'n'                                                            | Proce<br>Data                                      | ess<br>a                              | Write               | to F<br>lo         |

| Cycles:<br>Q Cycle<br>If Jump:<br>De<br>ope | Q1<br>ecode<br>No<br>eration<br>np: | 1(2)<br>Q2<br>Read literal<br>'n'<br>No                                                      | Proce<br>Data<br>No                                | ess<br>a                              | Write               | to F<br>lo         |

| Cycles:<br>Q Cycle<br>If Jump:<br>De<br>ope | Q1<br>ecode<br>No<br>eration        | 1(2)<br>Q2<br>Read literal<br>'n'<br>No                                                      | Proce<br>Data<br>No                                | ess<br>a<br>ion                       | Write<br>N<br>opera | to F<br>lo         |

| Cycles:<br>Q Cycle<br>If Jump:<br>De<br>Ope | Q1<br>ecode<br>No<br>eration<br>np: | 1(2)<br>Q2<br>Read literal<br>'n'<br>No<br>operation                                         | Proce<br>Data<br>No<br>operat                      | ess<br>a<br>ion<br>}<br>ess           | Write<br>N<br>opera | to F<br>lo<br>atio |

| <b>丘</b> ) |

|------------|

|            |

|            |

| p)         |

| -          |

| E+2)       |

|            |

| DAW                      | Decimal Adjust W Regis                            | ster     | DECF              | Decrement f                                                                      |

|--------------------------|---------------------------------------------------|----------|-------------------|----------------------------------------------------------------------------------|

| Syntax:                  | [label] DAW                                       |          | Syntax:           | [ <i>label</i> ] DECF f[,d[,a]                                                   |

| Operands:                | None                                              |          | Operands:         | $0 \leq f \leq 255$                                                              |

| Operation:               | If [W<3:0> >9] or [DC = 1                         | ] then   |                   | d ∈ [0,1]                                                                        |

|                          | $(W<3:0>) + 6 \rightarrow W<3:0>;$                |          |                   | a ∈ [0,1]                                                                        |

|                          | else<br>(W<3:0>) → W<3:0>;                        |          | Operation:        | $(f) - 1 \rightarrow dest$                                                       |

|                          | (11 (010)) / 11 (010),                            |          | Status Affected:  | C, DC, N, OV, Z                                                                  |

|                          | If $[W < 7:4 > 9]$ or $[C = 1]$                   |          | Encoding:         | 0000 01da ffff ffff                                                              |

|                          | $(W<7:4>) + 6 \rightarrow W<7:4>$ else            | ,        | Description:      | Decrement register 'f'. If 'd' is 0, the result is stored in W. If 'd' is 1, the |

|                          | $(W<7:4>) \rightarrow W<7:4>;$                    |          |                   | result is stored back in register 'f'                                            |

| Status Affected:         | С                                                 |          |                   | (default). If 'a' is 0, the Access                                               |

| Encoding:                | 0000 0000 0000                                    | 0111     |                   | Bank will be selected, overriding the BSR value. If 'a' = 1, then the            |

| Description:             | DAW adjusts the eight-bit                         | value in |                   | bank will be selected as per the                                                 |

|                          | W, resulting from the earl                        |          |                   | BSR value (default).                                                             |

|                          | tion of two variables (eac packed BCD format) and |          | Words:            | 1                                                                                |

|                          | a correct packed BCD res                          |          | Cycles:           | 1                                                                                |

| Words:                   | 1                                                 |          | Q Cycle Activity: |                                                                                  |

| Cycles:                  | 1                                                 |          | Q1                | Q2 Q3 Q4                                                                         |

| Q Cycle Activity:        |                                                   |          | Decode            | ReadProcessWrite toregister 'f'Datadestination                                   |

| Q1                       | Q2 Q3                                             | Q4       |                   |                                                                                  |

| Decode                   | Read Process                                      | Write    | Example:          | DECF CNT, 1, 0                                                                   |

| Everale4:                | register W Data                                   | W        | Before Instru     | ction                                                                            |

| Example1:                | DAW                                               |          | CNT<br>Z          | = 0x01<br>= 0                                                                    |

| Before Instru<br>W       | = 0xA5                                            |          | After Instructi   | -                                                                                |

| С                        | = 0                                               |          | CNT<br>Z          | = 0x00<br>= 1                                                                    |

| DC<br>After Instruct     | = 0                                               |          | 2                 |                                                                                  |

| W                        | = 0x05                                            |          |                   |                                                                                  |

| С                        | = 1                                               |          |                   |                                                                                  |

| DC<br><u>Example 2</u> : | = 0                                               |          |                   |                                                                                  |

| Before Instru            | ction                                             |          |                   |                                                                                  |

| W                        | = 0xCE                                            |          |                   |                                                                                  |

| C<br>DC                  | = 0<br>= 0                                        |          |                   |                                                                                  |

| After Instruct           | ion                                               |          |                   |                                                                                  |

| W                        | = 0x34                                            |          |                   |                                                                                  |

| C<br>DC                  | = 1<br>= 0                                        |          |                   |                                                                                  |

|                          |                                                   |          |                   |                                                                                  |

| SUBLW               | Subtract            | W from lite                    | ral            |

|---------------------|---------------------|--------------------------------|----------------|

| Syntax:             | [label] S           | SUBLW k                        |                |

| Operands:           | $0 \le k \le 25$    | 55                             |                |

| Operation:          | <b>k – (W)</b> –    | →W                             |                |

| Status Affected:    | N, OV, C            | , DC, Z                        |                |

| Encoding:           | 0000                | 1000 kkł                       | ck kkkk        |

| Description:        |                     | racted from t<br>The result is |                |

| Words:              | 1                   |                                |                |

| Cycles:             | 1                   |                                |                |

| Q Cycle Activity:   | :                   |                                |                |

| Q1                  | Q2                  | Q3                             | Q4             |

| Decode              | Read<br>literal 'k' | Process<br>Data                | Write to W     |

| Example 1:          | SUBLW (             | )x02                           |                |

| Before Instru       | uction              |                                |                |

| W                   | = 1                 |                                |                |

| C<br>After Instruct | = ?                 |                                |                |

| W                   | = 1                 |                                |                |

| С                   | = 1 ; re            | esult is positive              | )              |

| Z<br>N              | = 0 = 0             |                                |                |

| Example 2:          | SUBLW (             | )x02                           |                |

| Before Instru       | uction              |                                |                |

| W                   | = 2                 |                                |                |

| C<br>After Instruct | = ?<br>tion         |                                |                |

| W                   | = 0                 |                                |                |

| Ç                   | = 1 ; re            | esult is zero                  |                |

| Z<br>N              | = 1<br>= 0          |                                |                |

| Example 3:          | SUBLW (             | )x02                           |                |

| Before Instru       | uction              |                                |                |

| W                   | = 3                 |                                |                |

| C<br>After Instruct | = ?                 |                                |                |

| W                   |                     | 's complemen                   | <del>t</del> ) |

| C<br>Z<br>N         |                     | sult is negative               |                |

|                     |                     |                                |                |

| SUBWF                       | Subtrac                                                                          | t W from f                                                                                                                                                                                                                                                                                                           |                      |  |  |  |

|-----------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|--|

| Syntax:                     | [ label ]                                                                        | SUBWF f                                                                                                                                                                                                                                                                                                              | [,d [,a]             |  |  |  |

| Operands:                   | 0 ≤ f ≤ 2<br>d ∈ [0,1<br>a ∈ [0,1                                                | ]                                                                                                                                                                                                                                                                                                                    |                      |  |  |  |

| Operation:                  | (f) – (W)                                                                        | $) \rightarrow dest$                                                                                                                                                                                                                                                                                                 |                      |  |  |  |

| Status Affected:            | N, OV, 0                                                                         | C, DC, Z                                                                                                                                                                                                                                                                                                             |                      |  |  |  |

| Encoding:                   | 0101                                                                             | 11da fi                                                                                                                                                                                                                                                                                                              | ff ffff              |  |  |  |

| Description:                | compler<br>the resu<br>the resu<br>ter 'f' (de<br>Access<br>overridin<br>1, then | Subtract W from register 'f' (2's complement method). If 'd' is 0, the result is stored in W. If 'd' is 1, the result is stored back in register 'f' (default). If 'a' is 0, the Access Bank will be selected, overriding the BSR value. If 'a' is 1, then the bank will be selected as per the BSR value (default). |                      |  |  |  |

| Words:                      | 1                                                                                |                                                                                                                                                                                                                                                                                                                      |                      |  |  |  |

| Cycles:                     | 1                                                                                |                                                                                                                                                                                                                                                                                                                      |                      |  |  |  |

| Q Cycle Activity:           |                                                                                  |                                                                                                                                                                                                                                                                                                                      |                      |  |  |  |

| Q1                          | Q2                                                                               | Q3                                                                                                                                                                                                                                                                                                                   | Q4                   |  |  |  |

| Decode                      | Read<br>register 'f'                                                             | Process<br>Data                                                                                                                                                                                                                                                                                                      | Write to destination |  |  |  |

| Example 1:                  | SUBWF                                                                            | REG, 1, 0                                                                                                                                                                                                                                                                                                            |                      |  |  |  |

| Before Instru               |                                                                                  |                                                                                                                                                                                                                                                                                                                      |                      |  |  |  |

| REG<br>W                    | = 3<br>= 2                                                                       |                                                                                                                                                                                                                                                                                                                      |                      |  |  |  |

| C                           | = ?                                                                              |                                                                                                                                                                                                                                                                                                                      |                      |  |  |  |

| After Instruct<br>REG       | = 1                                                                              |                                                                                                                                                                                                                                                                                                                      |                      |  |  |  |

| W                           | = 2                                                                              |                                                                                                                                                                                                                                                                                                                      | -                    |  |  |  |

| C<br>Z<br>N                 | = 0                                                                              | esult is positiv                                                                                                                                                                                                                                                                                                     | e                    |  |  |  |

|                             | = 0                                                                              |                                                                                                                                                                                                                                                                                                                      |                      |  |  |  |

| Example 2:<br>Before Instru | SUBWF                                                                            | REG, 0, 0                                                                                                                                                                                                                                                                                                            |                      |  |  |  |

| REG                         | = 2                                                                              |                                                                                                                                                                                                                                                                                                                      |                      |  |  |  |

| W<br>C                      | = 2<br>= ?                                                                       |                                                                                                                                                                                                                                                                                                                      |                      |  |  |  |

| After Instruct              | =                                                                                |                                                                                                                                                                                                                                                                                                                      |                      |  |  |  |

| REG                         | = 2                                                                              |                                                                                                                                                                                                                                                                                                                      |                      |  |  |  |

| W<br>C                      | = 0<br>= 1 :r                                                                    | esult is zero                                                                                                                                                                                                                                                                                                        |                      |  |  |  |

| Z<br>N                      | = 1<br>= 0                                                                       |                                                                                                                                                                                                                                                                                                                      |                      |  |  |  |

| Example 3:                  | SUBWF                                                                            | REG, 1, 0                                                                                                                                                                                                                                                                                                            |                      |  |  |  |

| Before Instru               | iction                                                                           |                                                                                                                                                                                                                                                                                                                      |                      |  |  |  |

| REG                         | = 1                                                                              |                                                                                                                                                                                                                                                                                                                      |                      |  |  |  |

| W<br>C                      | = 2<br>= ?                                                                       |                                                                                                                                                                                                                                                                                                                      |                      |  |  |  |