#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 21                                                                        |

| Program Memory Size        | 24KB (12K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 1408 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 5x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2539-e-sp |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.10 Access Bank

The Access Bank is an architectural enhancement which is very useful for C compiler code optimization. The techniques used by the C compiler may also be useful for programs written in assembly.

This data memory region can be used for:

- · Intermediate computational values

- · Local variables of subroutines

- · Faster context saving/switching of variables

- Common variables

- Faster evaluation/control of SFRs (no banking)

The Access Bank is comprised of the upper 128 bytes in Bank 15 (SFRs) and the lower 128 bytes in Bank 0. These two sections will be referred to as Access RAM High and Access RAM Low, respectively. Figure 4-5 and Figure 4-6 indicate the Access RAM areas.

A bit in the instruction word specifies if the operation is to occur in the bank specified by the BSR register, or in the Access Bank. This bit is denoted by the 'a' bit (for access bit).

When forced in the Access Bank (a = 0), the last address in Access RAM Low is followed by the first address in Access RAM High. Access RAM High maps the Special Function registers, so that these registers can be accessed without any software overhead. This is useful for testing status flags and modifying control bits.

#### 4.11 Bank Select Register (BSR)

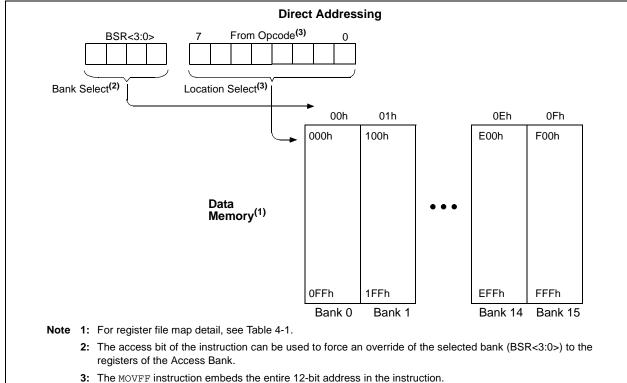

The need for a large general purpose memory space dictates a RAM banking scheme. The data memory is partitioned into sixteen banks. When using direct addressing, the BSR should be configured for the desired bank.

BSR<3:0> holds the upper 4 bits of the 12-bit RAM address. The BSR<7:4> bits will always read '0's, and writes will have no effect.

A MOVLB instruction has been provided in the instruction set to assist in selecting banks.

If the currently selected bank is not implemented, any read will return all '0's and all writes are ignored. The STATUS register bits will be set/cleared as appropriate for the instruction performed.

Each Bank extends up to FFh (256 bytes). All data memory is implemented as static RAM.

A MOVFF instruction ignores the BSR, since the 12-bit addresses are embedded into the instruction word.

Section 4.12 provides a description of indirect addressing, which allows linear addressing of the entire RAM space.

#### FIGURE 4-7: DIRECT ADDRESSING

### REGISTER 5-1: EECON1 REGISTER (ADDRESS FA6h)

| -     |                                                                                                                                                |                | •           |                              |                    |               |               |             |  |  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------|------------------------------|--------------------|---------------|---------------|-------------|--|--|

|       | R/W-x                                                                                                                                          | R/W-x          | U-0         | R/W-0                        | R/W-x              | R/W-0         | R/S-0         | R/S-0       |  |  |

|       | EEPGD                                                                                                                                          | CFGS           |             | FREE                         | WRERR              | WREN          | WR            | RD          |  |  |

|       | bit 7                                                                                                                                          |                |             |                              |                    | ·             |               | bit 0       |  |  |

| bit 7 | FEPGD: F                                                                                                                                       | ASH Progr      | am or Data  |                              | Memory Select      | hit           |               |             |  |  |

| bit i |                                                                                                                                                | FLASH pro      |             |                              |                    | bit           |               |             |  |  |

|       | 0 = Access data EEPROM memory                                                                                                                  |                |             |                              |                    |               |               |             |  |  |

| bit 6 | CFGS: FLASH Program/Data EE or Configuration Select bit                                                                                        |                |             |                              |                    |               |               |             |  |  |

|       |                                                                                                                                                | configuratio   | •           |                              |                    |               |               |             |  |  |

|       | 0 = Access                                                                                                                                     | FLASH pro      | ogram or da | ta EEPRON                    | l memory           |               |               |             |  |  |

| bit 5 | Unimplem                                                                                                                                       | ented: Rea     | d as '0'    |                              |                    |               |               |             |  |  |

| bit 4 | FREE: FLA                                                                                                                                      | SH Row Er      | ase Enable  | e bit                        |                    |               |               |             |  |  |

|       |                                                                                                                                                |                |             | ow addresse<br>se operation) | d by TBLPTR c<br>) | on the next   | WR comma      | and         |  |  |

|       |                                                                                                                                                | n write only   |             |                              |                    |               |               |             |  |  |

| bit 3 | WRERR: F                                                                                                                                       | LASH Prog      | ram/Data E  | E Error Flag                 | g bit              |               |               |             |  |  |

|       | 1 = A write                                                                                                                                    | operation is   | s premature | ely terminate                | d                  |               |               |             |  |  |

|       | · •                                                                                                                                            |                |             |                              | ng in normal op    | eration)      |               |             |  |  |

|       |                                                                                                                                                | ite operation  |             |                              |                    |               |               |             |  |  |

|       |                                                                                                                                                | ten a WREF     |             |                              | and CFGS bits      | s are not cle | eared. This   | allows      |  |  |

| bit 2 | WREN: FL                                                                                                                                       | ASH Progra     | am/Data EE  | Write Enab                   | le bit             |               |               |             |  |  |

|       |                                                                                                                                                | write cycles   |             |                              |                    |               |               |             |  |  |

|       |                                                                                                                                                | write to the   | EEPROM      |                              |                    |               |               |             |  |  |

| bit 1 | WR: Write                                                                                                                                      |                |             |                              |                    |               |               |             |  |  |

|       |                                                                                                                                                |                |             |                              | or a program m     |               |               |             |  |  |

|       | (The operation is self-timed and the bit is cleared by hardware once write is complete. The WR bit can only be set (not cleared) in software.) |                |             |                              |                    |               |               |             |  |  |

|       |                                                                                                                                                | ycle to the E  |             |                              |                    |               |               |             |  |  |

| bit 0 | RD: Read                                                                                                                                       | Control bit    |             |                              |                    |               |               |             |  |  |

|       | 1 = Initiates an EEPROM read                                                                                                                   |                |             |                              |                    |               |               |             |  |  |

|       |                                                                                                                                                |                |             |                              | rdware. The R      | D bit can or  | nly be set (n | ot cleared) |  |  |

|       |                                                                                                                                                | ot initiate ar |             | set when EE                  | :PGD = 1.)         |               |               |             |  |  |

|       | 0 <b>-</b> 0003 H                                                                                                                              |                |             | 1000                         |                    |               |               |             |  |  |

|       | Legend:                                                                                                                                        |                |             |                              |                    |               |               |             |  |  |

|       | R = Reada                                                                                                                                      | ble bit        | W = V       | Writable bit                 | U = Unimp          | lemented b    | it, read as ' | 0'          |  |  |

|       | 1                                                                                                                                              |                |             |                              |                    |               |               |             |  |  |

© 2002-2013 Microchip Technology Inc.

- n = Value at POR

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

#### **REGISTER 8-3:** INTCON3 REGISTER

- n = Value at POR

|        | R/W-1                                           | R/W-1                            | U-0           | R/W-0                | R/W-0      | U-0          | R/W-0          | R/W-0  |

|--------|-------------------------------------------------|----------------------------------|---------------|----------------------|------------|--------------|----------------|--------|

|        | INT2IP <sup>(1)</sup>                           | INT1IP <sup>(1)</sup>            | _             | INT2IE               | INT1IE     | _            | INT2IF         | INT1IF |

|        | bit 7                                           |                                  |               |                      |            |              |                | bit 0  |

|        |                                                 |                                  |               |                      |            |              |                |        |

| bit 7  | INT2IP <sup>(1)</sup> :                         | INT2 Externa                     | al Interrupt  | Priority bit         |            |              |                |        |

|        | 1 = High p                                      |                                  |               |                      |            |              |                |        |

| 1.11.0 | 0 = Low pr                                      | •                                |               | <b>D</b> · · · · · · |            |              |                |        |

| bit 6  |                                                 | INT1 Externa                     | al Interrupt  | Priority bit         |            |              |                |        |

|        | 1 = High p<br>0 = Low pr                        | •                                |               |                      |            |              |                |        |

| bit 5  | •                                               | nented: Read                     | d as '0'      |                      |            |              |                |        |

| bit 4  |                                                 | IT2 External                     |               | able bit             |            |              |                |        |

|        |                                                 | es the INT2 e                    |               |                      |            |              |                |        |

|        | 0 = Disable                                     | es the INT2 e                    | external inte | errupt               |            |              |                |        |

| bit 3  |                                                 | IT1 External                     | -             |                      |            |              |                |        |

|        |                                                 | es the INT1 e                    |               |                      |            |              |                |        |

| 1.11.0 |                                                 | es the INT1 e                    |               | errupt               |            |              |                |        |

| bit 2  |                                                 | nented: Read                     |               |                      |            |              |                |        |

| bit 1  |                                                 | T2 External                      | •             | •                    |            | · • • •      |                |        |

|        |                                                 | IT2 external i<br>IT2 external i | •             |                      | be cleared | in software) |                |        |

| bit 0  |                                                 | T1 External                      | •             |                      |            |              |                |        |

| bit o  |                                                 | T1 external i                    | •             | •                    | be cleared | in software) |                |        |

|        |                                                 | T1 external i                    |               |                      |            |              |                |        |

|        | <b>Note</b> 1: Maintain this bit cleared (= 0). |                                  |               |                      |            |              |                |        |

|        |                                                 |                                  |               |                      |            |              |                |        |

|        | Legend:                                         |                                  |               |                      |            |              |                |        |

|        | R = Reada                                       | able bit                         | VV = V        | Vritable bit         | U = Unir   | nplemented   | bit, read as ' | 0'     |

|        | 1                                               |                                  |               |                      |            |              |                |        |

**Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

'0' = Bit is cleared

'1' = Bit is set

x = Bit is unknown

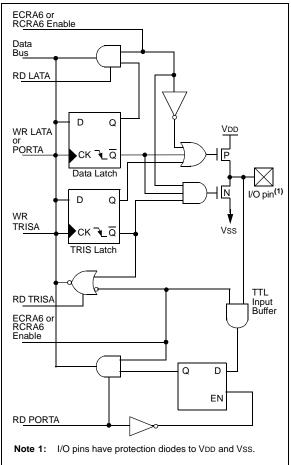

### FIGURE 9-3: BLOCK DIAGRAM OF RA6 PIN

### 11.0 TIMER1 MODULE

The Timer1 module timer/counter has the following features:

- 16-bit timer/counter (two 8-bit registers, TMR1H and TMR1L)

- Readable and writable (both registers)

- Internal or external clock select

- Interrupt-on-overflow from FFFFh to 0000h

Figure 11-1 is a simplified block diagram of the Timer1 module.

Register 11-1 details the Timer1 control register, which sets the Operating mode of the Timer1 module. Timer1 can be enabled or disabled by setting or clearing control bit TMR1ON (T1CON<0>).

U = Unimplemented bit, read as '0'

'0' = Bit is cleared

#### **REGISTER 11-1:** T1CON: TIMER1 CONTROL REGISTER

|         | R/W-0       | U-0                          | R/W-0          | R/W-0          | U-0           | R/W-0     | R/W-0  | R/W-0  |

|---------|-------------|------------------------------|----------------|----------------|---------------|-----------|--------|--------|

|         | RD16        | _                            | T1CKPS1        | T1CKPS0        | _             | T1SYNC    | TMR1CS | TMR10N |

|         | bit 7       |                              |                |                |               | I         |        | bit 0  |

|         |             |                              |                |                |               |           |        |        |

| bit 7   | RD16: 16-   | bit Read/W                   | /rite Mode Er  | nable bit      |               |           |        |        |

|         |             | •                            |                | Timer1 in on   |               |           |        |        |

|         | 0 = Enable  | es register                  | read/write of  | Timer1 in two  | o 8-bit opera | tions     |        |        |

| bit 6   | Unimplen    | nented: Re                   | ad as '0'      |                |               |           |        |        |

| bit 5-4 | T1CKPS1     | :T1CKPS0                     | : Timer1 Inpu  | ut Clock Pres  | cale Select I | bits      |        |        |

|         | -           | rescale va                   |                |                |               |           |        |        |

|         |             | Prescale val<br>Prescale val |                |                |               |           |        |        |

|         |             | rescale val<br>Prescale val  |                |                |               |           |        |        |

| bit 3   |             |                              | intain as '0'  |                |               |           |        |        |

| bit 2   |             |                              |                | nput Synchro   | nization Sal  | oct hit   |        |        |

| DILZ    | When TMI    |                              |                | nput Synchic   |               | ect bit   |        |        |

|         |             |                              | ze external c  | lock input     |               |           |        |        |

|         |             |                              | rnal clock inp |                |               |           |        |        |

|         | When TMI    | R1CS = 0:                    |                |                |               |           |        |        |

|         | This bit is | ignored. Tii                 | mer1 uses th   | e internal clo | ck when TM    | R1CS = 0. |        |        |

| bit 1   | TMR1CS:     | Timer1 Clo                   | ock Source S   | elect bit      |               |           |        |        |

|         | 1 = Extern  | al clock fro                 | m pin RC0/T    | 13CKI (on th   | e rising edge | e)        |        |        |

|         | 0 = Interna | al clock (Fo                 | sc/4)          |                |               |           |        |        |

| bit 0   | TMR10N:     | Timer1 Or                    | ı bit          |                |               |           |        |        |

|         | 1 = Enable  |                              |                |                |               |           |        |        |

|         | 0 = Stops   | Timer1                       |                |                |               |           |        |        |

|         | r           |                              |                |                |               |           |        |        |

|         | Legend:     |                              |                |                |               |           |        |        |

R = Readable bit

- n = Value at POR

W = Writable bit

'1' = Bit is set

x = Bit is unknown

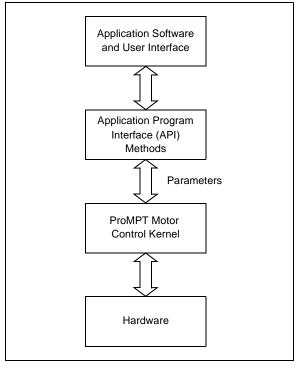

## 14.4 Developing Applications Using the Motor Control Kernel

The Motor Control kernel allows users to develop their applications without having knowledge of motor control. The key parameters of the motor control kernel can be set and read through the Application Program Interface (API) methods discussed in the previous section.

The overall application can be thought of as a protocol stack, as shown in Figure 14-3. In this case, the API methods reside between the user's application and the ProMPT kernel, and are used to exchange parameter values. The motor control kernel sets the PWM duty cycles based on the inputs from the application software.

A typical motor control routine is shown in Example 14-1. In this case, the motor will run at 20 Hz for 10 seconds, accelerate to 60 Hz at the rate of 10 Hz/s, remain at 60 Hz for 20 seconds, and finally stop.

#### FIGURE 14-3:

#### LAYERS OF THE MOTOR CONTROL ARCHITECTURE STACK

#### EXAMPLE 14-1: MOTOR CONTROL ROUTINE USING THE ProMPT APIS

```

Void main()

unsigned char i;

unsigned char j;

ProMPT_Init(0);

// Initialize the ProMPT block

i = ProMPT_SetFrequency(10);

// Set motor frequency to 10Hz

for (i=0;i<161;i++)</pre>

// Set counter for 10 sec @ 1/16 sec per tick

{

j = ProMPT_Tick(void);

// Tick of 1/16 sec

ProMPT_ClearTick(void);

// Clearing the Tick flag

}

// Set acceleration rate to 10 Hz/sec

ProMPT_SetAccelRate(10);

i = ProMPT_SetFrequency(60);

// Set motor frequency to 60 Hz

for (i=0;i<161;i++)</pre>

// Set counter for 20 Sec @ 1/16 sec per tick

// (2 loops of 10 Sec each)

{

// Tick of 1/16 Sec

j = ProMPT_Tick(void);

// Clearing the Tick flag

ProMPT_ClearTick(void);

j = ProMPT_Tick(void);

// Tick of 1/16 Sec

ProMPT_ClearTick(void);

// Clearing the Tick flag

i = ProMPT SetFrequency(0);

// Set motor frequency to 0 Hz (stop)

while(1);

// End of the task

```

### REGISTER 16-3: SSPSTAT: MSSP STATUS REGISTER (I<sup>2</sup>C MODE)

|     | R/W-0                                                           | R/W-0                                              | R-0                       | R-0           | R-0          | R-0                          | R-0                 | R-0       |

|-----|-----------------------------------------------------------------|----------------------------------------------------|---------------------------|---------------|--------------|------------------------------|---------------------|-----------|

|     | SMP                                                             | CKE                                                | D/A                       | Р             | S            | R/W                          | UA                  | BF        |

|     | bit 7                                                           |                                                    |                           |               |              |                              |                     | bit       |

| t 7 | In Master of                                                    | v Rate Contr<br>or Slave mod                       | <u>de:</u>                | Standard Sn   | aad mode (1  | 00 kHz and                   | 1 M山⁊)              |           |

|     |                                                                 | rate control e                                     |                           |               |              |                              | 1 IVII I <i>Z</i> ) |           |

| t 6 | CKE: SME<br>In Master of                                        | Bus Select bi                                      | t<br><u>le:</u>           | 5             | ,            | ,                            |                     |           |

|     |                                                                 | e SMBus spe<br>e SMBus spe                         |                           |               |              |                              |                     |           |

| t 5 | —                                                               | Address bit                                        |                           |               |              |                              |                     |           |

|     |                                                                 | <u>ode:</u><br>es that the la<br>es that the la    |                           |               |              |                              |                     |           |

| t 4 |                                                                 | es that a ST<br>bit was not o                      | letected last             |               |              |                              |                     |           |

|     | Note:                                                           |                                                    | leared on RI              | ESET and w    | hen SSPEN    | is cleared.                  |                     |           |

| 3   |                                                                 | bit<br>es that a ST<br>ī bit was not               |                           |               | ed last      |                              |                     |           |

|     | Note:                                                           | This bit is c                                      | leared on RI              | ESET and w    | hen SSPEN    | is cleared.                  |                     |           |

| t 2 | <b>R/W</b> : Read<br>In <u>Slave m</u><br>1 = Read<br>0 = Write | d/Write bit Ini<br>ode:                            | formation (I <sup>2</sup> | C mode only   | y)           |                              |                     |           |

|     | Note:                                                           |                                                    |                           |               |              | e last addre:<br>bit, STOP b |                     |           |

|     |                                                                 | <u>mode:</u><br>nit is in progi<br>nit is not in p |                           |               |              |                              |                     |           |

|     | Note:                                                           | ORing this in IDLE mo                              |                           | , RSEN, PE    | N, RCEN, o   | r ACKEN wil                  | l indicate if t     | he MSSP i |

| : 1 | 1 = Indicat                                                     | e Address (<br>es that the u<br>ss does not r      | ser needs to              | o update the  | address in t | he SSPADD                    | register            |           |

| 0   |                                                                 | Full Status k                                      |                           | puatoa        |              |                              |                     |           |

| U   | <u>In Transmi</u><br>1 = Receiv                                 |                                                    | SSPBUF is                 |               |              |                              |                     |           |

|     | <u>In Receive</u><br>1 = Data tr                                | <u>mode:</u><br>ansmit in pro                      | ogress (does              | s not include |              | d STOP bits<br>STOP bits),   |                     |           |

|     |                                                                 |                                                    | -                         |               |              |                              |                     |           |

|     | Legend:                                                         |                                                    |                           |               |              |                              |                     |           |

|     | R = Reada                                                       | ble bit                                            | W = Writab                | ole bit       | U = Unimp    | lemented bit                 | , read as '0'       |           |

|     | - n = Value                                                     | at POR                                             | '1' = Bit is :            | set           | '0' = Bit is | cleared                      | x = Bit is ur       | known     |

#### **REGISTER 16-4:** SSPCON1: MSSP CONTROL REGISTER 1 (I<sup>2</sup>C MODE)

| WCOL SSPOV SSPEN CKP SSPM3 SSPM2 SSPM1           | SSPM0 |             | 005140 | 000140 |       | 000511 |       |       |  |

|--------------------------------------------------|-------|-------------|--------|--------|-------|--------|-------|-------|--|

| R/VV-U R/VV-U R/VV-U R/VV-U R/VV-U R/VV-U R/VV-U | R/W-0 | R/W-0 R/W-0 | R/W-0  | R/W-0  | R/W-0 | R/W-0  | R/W-0 | R/W-0 |  |

- bit 7 WCOL: Write Collision Detect bit

- In Master Transmit mode:

- 1 = A write to the SSPBUF register was attempted while the I<sup>2</sup>C conditions were not valid for a transmission to be started (must be cleared in software)

- 0 = No collision

- In Slave Transmit mode:

- 1 = The SSPBUF register is written while it is still transmitting the previous word (must be cleared in software)

- $0 = No \ collision$

- In Receive mode (Master or Slave modes):

This is a "don't care" bit

#### bit 6 SSPOV: Receive Overflow Indicator bit

In Receive mode:

- 1 = A byte is received while the SSPBUF register is still holding the previous byte (must be cleared in software)

- 0 = No overflow

In Transmit mode:

This is a "don't care" bit in Transmit mode

#### bit 5 SSPEN: Synchronous Serial Port Enable bit

- 1 = Enables the serial port and configures the SDA and SCL pins as the serial port pins

- 0 = Disables serial port and configures these pins as I/O port pins

Note: When enabled, the SDA and SCL pins must be properly configured as input or output.

- bit 4 **CKP:** SCK Release Control bit

- In Slave mode:

- 1 = Release clock

- 0 = Holds clock low (clock stretch), used to ensure data setup time

- In Master mode:

Unused in this mode

- bit 3-0 SSPM3:SSPM0: Synchronous Serial Port Mode Select bits

- 1111 =  $I^2C$  Slave mode, 10-bit address with START and STOP bit interrupts enabled

- $1110 = I^2C$  Slave mode, 7-bit address with START and STOP bit interrupts enabled

- $1011 = I^2C$  Firmware Controlled Master mode (Slave IDLE)

- $1000 = I^2C$  Master mode, clock = FOSC / (4 \* (SSPADD+1))

- 0111 =  $I^2C$  Slave mode, 10-bit address

- $0110 = I^2C$  Slave mode, 7-bit address

- **Note:** Bit combinations not specifically listed here are either reserved, or implemented in SPI mode only.

| Legend:            |                  |                                        |  |

|--------------------|------------------|----------------------------------------|--|

| R = Readable bit   | W = Writable bit | U = Unimplemented bit, read as '0'     |  |

| - n = Value at POR | '1' = Bit is set | 0' = Bit is cleared x = Bit is unknown |  |

#### 16.4.3.2 Reception

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register and the SDA line is held low (ACK).

When the address byte overflow condition exists, then the no Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set, or bit SSPOV (SSPCON1<6>) is set.

An MSSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

If SEN is enabled (SSPCON1<0> = 1), RC3/SCK/SCL will be held low (clock stretch) following each data transfer. The clock must be released by setting bit CKP (SSPCON<4>). See Section 16.4.4 ("Clock Stretching"), for more detail.

#### 16.4.3.3 Transmission

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit and pin RC3/SCK/SCL is held low, regardless of SEN (see "Clock Stretching", Section 16.4.4, for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data. The transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then, pin RC3/ SCK/SCL should be enabled by setting bit CKP (SSPCON1<4>). The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 16-9).

The ACK pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line is high (not ACK), then the data transfer is complete. In this case, when the ACK is latched by the slave, the slave logic is reset (resets SSPSTAT register) and the slave monitors for another occurrence of the START bit. If the SDA line was low (ACK), the next transmit data must be loaded into the SSPBUF register. Again, pin RC3/SCK/SCL must be enabled by setting bit CKP.

An MSSP interrupt is generated for each data transfer byte. The SSPIF bit must be cleared in software and the SSPSTAT register is used to determine the status of the byte. The SSPIF bit is set on the falling edge of the ninth clock pulse.

NOTES:

| FIGURE 21-1: | GENERAL FORMAT FOR INSTRUCTIONS                                                                          |                      |

|--------------|----------------------------------------------------------------------------------------------------------|----------------------|

|              | Byte-oriented file register operations                                                                   | Example Instruction  |

|              | <u>15 10 9 8 7 0</u>                                                                                     |                      |

|              | OPCODE d a f (FILE #)                                                                                    | ADDWF MYREG, W, B    |

|              | d = 0 for result destination to be WREG register<br>d = 1 for result destination to be file register (f) |                      |

|              | a = 0 to force Access Bank                                                                               |                      |

|              | a = 1 for BSR to select bank<br>f = 8-bit file register address                                          |                      |

|              | Byte to Byte move operations (2-word)                                                                    |                      |

|              | <u>15 12 11 0</u>                                                                                        |                      |

|              | OPCODE f (Source FILE #)                                                                                 | MOVFF MYREG1, MYREG2 |

|              | 15 12 11 0                                                                                               |                      |

|              | 1111 f (Destination FILE #)                                                                              |                      |

|              | f = 12-bit file register address                                                                         |                      |

|              | Bit-oriented file register operations                                                                    |                      |

|              | <u>15 12 11 9 8 7 0</u>                                                                                  |                      |

|              | OPCODE b (BIT #) a f (FILE #)                                                                            | BSF MYREG, bit, B    |

|              | b = 3-bit position of bit in file register (f)<br>a = 0 to force Access Bank                             |                      |

|              | a = 0 to force Access Bank<br>a = 1 for BSR to select bank                                               |                      |

|              | f = 8-bit file register address                                                                          |                      |

|              | Literal operations                                                                                       |                      |

|              | <u>15 8 7 0</u>                                                                                          |                      |

|              | OPCODE k (literal)                                                                                       | MOVLW 0x7F           |

|              | k = 8-bit immediate value                                                                                |                      |

|              | Control operations                                                                                       |                      |

|              | CALL, GOTO and Branch operations                                                                         |                      |

|              | 15 8 7 0                                                                                                 |                      |

|              | OPCODE n<7:0> (literal)                                                                                  | GOTO Label           |

|              | 15 12 11 0                                                                                               |                      |

|              | 1111 n<19:8> (literal)                                                                                   |                      |

|              | n = 20-bit immediate value                                                                               |                      |

|              | 15 8 7 0                                                                                                 |                      |

|              | OPCODE S n<7:0> (literal)                                                                                | CALL MYFUNC          |

|              | 15 12 11 0                                                                                               |                      |

|              | n<19:8> (literal)                                                                                        |                      |

|              | S = Fast bit                                                                                             |                      |

|              | 15 11 10 0                                                                                               |                      |

|              | OPCODE n<10:0> (literal)                                                                                 | BRA MYFUNC           |

|              | 15 8 7 0                                                                                                 |                      |

|              | OPCODE n<7:0> (literal)                                                                                  | BC MYFUNC            |

|              |                                                                                                          |                      |

|              |                                                                                                          |                      |

#### TABLE 21-2: PIC18FXXX INSTRUCTION SET (CONTINUED)

| Mnem               | onic,       | Description Outlos 16-Bit Instruction |        | Word | Status | Notes |      |                 |       |

|--------------------|-------------|---------------------------------------|--------|------|--------|-------|------|-----------------|-------|

| Opera              | Description |                                       | Cycles | MSb  |        |       | LSb  | Affected        | Notes |

| LITERAL OPERATIONS |             |                                       |        |      |        |       |      |                 |       |

| ADDLW              | k           | Add literal and WREG                  | 1      | 0000 | 1111   | kkkk  | kkkk | C, DC, Z, OV, N |       |

| ANDLW              | k           | AND literal with WREG                 | 1      | 0000 | 1011   | kkkk  | kkkk | Z, N            |       |

| IORLW              | k           | Inclusive OR literal with WREG        | 1      | 0000 | 1001   | kkkk  | kkkk | Z, N            |       |

| LFSR               | f, k        | Move literal (12-bit) 2nd word        | 2      | 1110 | 1110   | 00ff  | kkkk | None            |       |

|                    |             | to FSRx 1st word                      |        | 1111 | 0000   | kkkk  | kkkk |                 |       |

| MOVLB              | k           | Move literal to BSR<3:0>              | 1      | 0000 | 0001   | 0000  | kkkk | None            |       |

| MOVLW              | k           | Move literal to WREG                  | 1      | 0000 | 1110   | kkkk  | kkkk | None            |       |

| MULLW              | k           | Multiply literal with WREG            | 1      | 0000 | 1101   | kkkk  | kkkk | None            |       |

| RETLW              | k           | Return with literal in WREG           | 2      | 0000 | 1100   | kkkk  | kkkk | None            |       |

| SUBLW              | k           | Subtract WREG from literal            | 1      | 0000 | 1000   | kkkk  | kkkk | C, DC, Z, OV, N |       |

| XORLW              | k           | Exclusive OR literal with WREG        | 1      | 0000 | 1010   | kkkk  | kkkk | Z, N            |       |

| DATA MEN           | NORY ↔      | PROGRAM MEMORY OPERATION              | S      |      |        |       |      | •               |       |

| TBLRD*             |             | Table Read                            | 2      | 0000 | 0000   | 0000  | 1000 | None            |       |

| TBLRD*+            |             | Table Read with post-increment        |        | 0000 | 0000   | 0000  | 1001 | None            |       |

| TBLRD*-            |             | Table Read with post-decrement        |        | 0000 | 0000   | 0000  | 1010 | None            |       |

| TBLRD+*            |             | Table Read with pre-increment         |        | 0000 | 0000   | 0000  | 1011 | None            |       |

| TBLWT*             |             | Table Write                           | 2 (5)  | 0000 | 0000   | 0000  | 1100 | None            |       |

| TBLWT*+            |             | Table Write with post-increment       |        | 0000 | 0000   | 0000  | 1101 | None            |       |

| TBLWT*-            |             | Table Write with post-decrement       |        | 0000 | 0000   | 0000  | 1110 | None            |       |

| TBLWT+*            |             | Table Write with pre-increment        |        | 0000 | 0000   | 0000  | 1111 | None            |       |

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are 2-word instructions. The second word of these instructions will be executed as a NOP, unless the first word of the instruction retrieves the information embedded in these 16-bits. This ensures that all program memory locations have a valid instruction.

5: If the Table Write starts the write cycle to internal memory, the write will continue until terminated.

| DAW               | Decimal A         | Adjust W Re                   | gister       | DECF   |              | Decreme                 | nt f                             |                         |

|-------------------|-------------------|-------------------------------|--------------|--------|--------------|-------------------------|----------------------------------|-------------------------|

| Syntax:           | [label] [         | DAW                           |              | Syntax | x:           | [label] [               | DECF f[,d[                       | ,a]                     |

| Operands:         | None              |                               |              | Opera  | nds:         | $0 \le f \le 255$       | 5                                |                         |

| Operation:        | lf [W<3:0>        | >9] or [DC =                  | = 1] then    |        |              | $d \in [0,1]$           |                                  |                         |

|                   |                   | + 6 $\rightarrow$ W<3:0       | )>;          | 0      | 4            | a ∈ [0,1]               | 14                               |                         |

|                   | else<br>(W<3:0>)  | $\rightarrow$ W<3:0>;         |              | Opera  |              | $(f) - 1 \rightarrow c$ |                                  |                         |

|                   | (                 | ,,                            |              |        | Affected:    | C, DC, N,               |                                  |                         |

|                   |                   | >9] or [C =                   |              | Encod  | -            | 0000                    | 01da ff                          |                         |

|                   | (VV<7:4>)<br>else | $+ 6 \rightarrow W < 7$ :     | 4>;          | Descr  | iption:      |                         | t register 'f'.<br>ored in W. If | If 'd' is 0, the        |

|                   |                   | → W<7:4>;                     |              |        |              |                         | ored back in                     |                         |

| Status Affected:  | С                 |                               |              |        |              |                         | f 'a' is 0, the                  |                         |

| Encoding:         | 0000              | 0000 000                      | 00 0111      |        |              |                         | be selected, ralue. If 'a' =     | -                       |

| Description:      | DAW adjus         | ts the eight-b                | oit value in |        |              |                         | be selected a                    |                         |

|                   |                   | ng from the e                 |              |        |              | BSR value               | e (default).                     |                         |

|                   |                   | variables (e<br>CD format) ai |              | Words  | s:           | 1                       |                                  |                         |

|                   |                   | backed BCD                    |              | Cycles | S:           | 1                       |                                  |                         |

| Words:            | 1.                |                               |              | Q Cy   | cle Activity | :                       |                                  |                         |

| Cycles:           | 1                 |                               |              | F      | Q1           | Q2                      | Q3                               | Q4                      |

| Q Cycle Activity: |                   |                               |              |        | Decode       | Read<br>register 'f'    | Process<br>Data                  | Write to<br>destination |

| Q1                | Q2                | Q3                            | Q4           |        |              | register i              | Dulu                             | destination             |

| Decode            | Read              | Process                       | Write        | Exam   | <u>ole</u> : | DECF                    | CNT, 1, 0                        |                         |

|                   | register W        | Data                          | W            | В      | efore Instru | uction                  |                                  |                         |

| Example1:         | DAW               |                               |              |        | CNT<br>Z     | = 0x01<br>= 0           |                                  |                         |

| Before Instru     |                   |                               |              | А      | fter Instruc | -                       |                                  |                         |

| W<br>C            | = 0xA5<br>= 0     |                               |              |        | CNT<br>Z     | = 0x00                  |                                  |                         |

| DC                | = 0               |                               |              |        | Z            | = 1                     |                                  |                         |

| After Instruct    |                   |                               |              |        |              |                         |                                  |                         |

| W<br>C            | = 0x05<br>= 1     |                               |              |        |              |                         |                                  |                         |

| DC<br>Example 2:  | = 0               |                               |              |        |              |                         |                                  |                         |

| Before Instru     | ction             |                               |              |        |              |                         |                                  |                         |

| W                 | = 0xCE            |                               |              |        |              |                         |                                  |                         |

| C<br>DC           | = 0<br>= 0        |                               |              |        |              |                         |                                  |                         |

| After Instruct    | -                 |                               |              |        |              |                         |                                  |                         |

| W                 | = 0x34            |                               |              |        |              |                         |                                  |                         |

| C<br>DC           | = 1<br>= 0        |                               |              |        |              |                         |                                  |                         |

|                   | 2                 |                               |              |        |              |                         |                                  |                         |

| TE  | BLWT         | Table Wri                                                                                                                                                                          | te                                                                                                                                                 |                                                                                                                                 |                                                                                                                               |  |  |  |

|-----|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Sy  | ntax:        | [ label ]                                                                                                                                                                          | TBLWT (                                                                                                                                            | (*;*+;*-;·                                                                                                                      | +*)                                                                                                                           |  |  |  |

| Op  | perands:     | None                                                                                                                                                                               |                                                                                                                                                    |                                                                                                                                 |                                                                                                                               |  |  |  |

|     | peration:    | TBLPTR -<br>if TBLWT*<br>(TABLAT)<br>(TBLPTR)<br>if TBLWT*<br>(TABLAT)<br>(TBLPTR)<br>if TBLWT+<br>(TBLPTR)                                                                        | T) → Holding Register;<br>R - No Change;<br>T*+,<br>T) → Holding Register;<br>R) +1 → TBLPTR;<br>T*-,<br>T) → Holding Register;<br>R) -1 → TBLPTR; |                                                                                                                                 |                                                                                                                               |  |  |  |

| Sta | atus Affecte | d: None                                                                                                                                                                            |                                                                                                                                                    |                                                                                                                                 |                                                                                                                               |  |  |  |

| Er  | ncoding:     | 0000                                                                                                                                                                               | 0000                                                                                                                                               | 0000                                                                                                                            | 11nn<br>nn=0 *<br>=1 *+<br>=2 *-<br>=3 +*                                                                                     |  |  |  |

|     | escription:  | TBLPTR t<br>holding re<br>written to.<br>used to pr<br>gram Men<br>for informa<br>memory.<br>The TBLP<br>to each by<br>TBLPTR f<br>range. The<br>which byte<br>location to<br>TBLP | gisters the<br>The 8 hol<br>ogram the<br>nory (P.M.)<br>ation on w<br>TR (a 21-l<br>rte in the p<br>nas a 2 ME<br>e LSb of th<br>e of the pro      | TABLAT<br>ding regis<br>contents<br>. See Sec<br>riting to Fl<br>bit pointer<br>orogram m<br>Btye addre<br>ne TBLPT<br>ogram me | data is<br>ters are<br>of Pro-<br>ction 5.0<br>LASH<br>) points<br>nemory.<br>ess<br>R selects<br>mory<br>unificant<br>rogram |  |  |  |

|     |              | TBLP                                                                                                                                                                               | 2TR[0] = 1:                                                                                                                                        |                                                                                                                                 | nificant<br>rogram                                                                                                            |  |  |  |

|     |              | The TBLW<br>value of T<br>• no char<br>• post-inc<br>• post-de<br>• pre-incr                                                                                                       | BLPTR as<br>ige<br>crement<br>crement                                                                                                              | ion can m                                                                                                                       |                                                                                                                               |  |  |  |

| W   | ords:        | 1                                                                                                                                                                                  |                                                                                                                                                    |                                                                                                                                 |                                                                                                                               |  |  |  |

|     | /cles:       | 2                                                                                                                                                                                  |                                                                                                                                                    |                                                                                                                                 |                                                                                                                               |  |  |  |

| -   | Cycle Activ  |                                                                                                                                                                                    |                                                                                                                                                    |                                                                                                                                 |                                                                                                                               |  |  |  |

| 3   | Q1           | Q2                                                                                                                                                                                 | Q3                                                                                                                                                 | G                                                                                                                               | 4                                                                                                                             |  |  |  |

|     | Decode       | No<br>operation                                                                                                                                                                    | No<br>operation                                                                                                                                    | N<br>opera                                                                                                                      | 0                                                                                                                             |  |  |  |

|     | No           | No                                                                                                                                                                                 | No                                                                                                                                                 | N                                                                                                                               |                                                                                                                               |  |  |  |

|     | operation    | operation<br>(Read                                                                                                                                                                 | operation                                                                                                                                          | opera<br>(Write to                                                                                                              |                                                                                                                               |  |  |  |

#### TBLWT Table Write (Continued)

|                             | 10.010         |         | (••••••)         |

|-----------------------------|----------------|---------|------------------|

| Example1:                   | TBLWT          | *+;     |                  |

| Before Instruc              | tion           |         |                  |

| TABLAT<br>TBLPTR<br>HOLDING | REGISTER       | =       | 0x55<br>0x00A356 |

| (0x00A356                   | 6)             | =       | 0xFF             |

| After Instruction           | ons (table v   | vrite o | completion)      |

| TABLAT<br>TBLPTR<br>HOLDING | REGISTER       | =       | 0x55<br>0x00A357 |

| (0x00A356                   |                | =       | 0x55             |

| Example 2:                  | TBLWT          | +*;     |                  |

| Before Instruc              | tion           |         |                  |

| TABLAT<br>TBLPTR<br>HOLDING | REGISTER       | =<br>=  | 0x34<br>0x01389A |

| (0x01389A                   | N)<br>REGISTER | =       | 0xFF             |

| (0x01389E                   |                | =       | 0xFF             |

| After Instruction           | on (table wi   | rite co | ompletion)       |

| TABLAT<br>TBLPTR<br>HOLDING | REGISTER       | =<br>=  | 0x34<br>0x01389B |

| (0x01389A                   |                | =       | 0xFF             |

| (0x01389E                   |                | =       | 0x34             |

(Read TABLAT)

(Write to Holding Register or Memory)

### 22.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C17 and MPLAB C18 C Compilers

- MPLINK™ Object Linker/

- MPLIB<sup>™</sup> Object Librarian

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- ICEPIC<sup>™</sup> In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD

- Device Programmers

- PRO MATE<sup>®</sup> II Universal Device Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Development Programmer

- Low Cost Demonstration Boards

- PICDEM<sup>™</sup>1 Demonstration Board

- PICDEM 2 Demonstration Board

- PICDEM 3 Demonstration Board

- PICDEM 17 Demonstration Board

- KEELOQ<sup>®</sup> Demonstration Board

#### 22.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> based application that contains:

- · An interface to debugging tools

- simulator

- programmer (sold separately)

- emulator (sold separately)

- in-circuit debugger (sold separately)

- A full-featured editor

- · A project manager

- Customizable toolbar and key mapping

- · A status bar

- On-line help

The MPLAB IDE allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- Debug using:

- source files

- absolute listing file

- machine code

The ability to use MPLAB IDE with multiple debugging tools allows users to easily switch from the costeffective simulator to a full-featured emulator with minimal retraining.

#### 22.2 MPASM Assembler

The MPASM assembler is a full-featured universal macro assembler for all PIC MCUs.

The MPASM assembler has a command line interface and a Windows shell. It can be used as a stand-alone application on a Windows 3.x or greater system, or it can be used through MPLAB IDE. The MPASM assembler generates relocatable object files for the MPLINK object linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, an absolute LST file that contains source lines and generated machine code, and a COD file for debugging.

The MPASM assembler features include:

- Integration into MPLAB IDE projects.

- User-defined macros to streamline assembly code.

- Conditional assembly for multi-purpose source files.

- Directives that allow complete control over the assembly process.

#### 22.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI 'C' compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers, respectively. These compilers provide powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compilers provide symbol information that is compatible with the MPLAB IDE memory display.

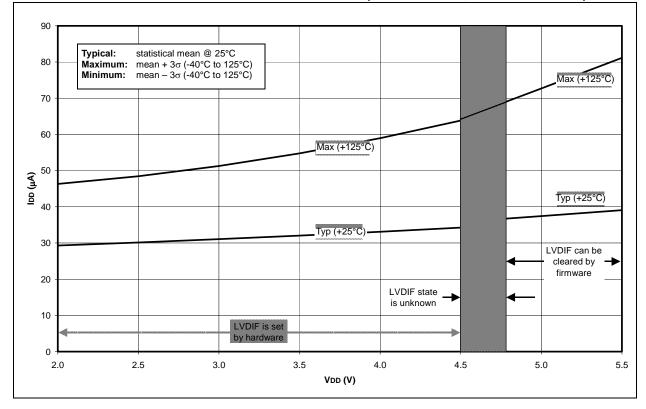

#### 23.1 DC Characteristics: PIC18FXX39 (Industrial, Extended) PIC18LFXX39 (Industrial)

| (Industrial) |      |                                                                         |      | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrialStandard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +85^{\circ}C$ for extended |      |      |                                              |  |  |

|--------------|------|-------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|----------------------------------------------|--|--|

|              |      |                                                                         |      |                                                                                                                                                                                                                                                                                                                          |      |      |                                              |  |  |

|              | Vdd  | Supply Voltage                                                          |      |                                                                                                                                                                                                                                                                                                                          |      |      |                                              |  |  |

| D001         |      | PIC18LFXX39                                                             | 2.0  |                                                                                                                                                                                                                                                                                                                          | 5.5  | V    | HS Osc mode                                  |  |  |

| D001         |      | PIC18FXX39                                                              | 4.2  | —                                                                                                                                                                                                                                                                                                                        | 5.5  | V    |                                              |  |  |

| D002         | Vdr  | RAM Data Retention<br>Voltage <sup>(1)</sup>                            | 1.5  | —                                                                                                                                                                                                                                                                                                                        | -    | V    |                                              |  |  |

| D003         | VPOR | <b>VDD Start Voltage</b><br>to ensure internal<br>Power-on Reset signal |      | —                                                                                                                                                                                                                                                                                                                        | 0.7  | V    | See Section 3.1 (Power-on Reset) for details |  |  |

| D004         | SVDD | <b>VDD Rise Rate</b><br>to ensure internal<br>Power-on Reset signal     | 0.05 | _                                                                                                                                                                                                                                                                                                                        |      | V/ms | See Section 3.1 (Power-on Reset) for details |  |  |