Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I²C, SPI, UART/USART                                                      |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 21                                                                        |

| Program Memory Size        | 24KB (12K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 1408 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 5x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2539-i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 2-1:CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR

| Ranges Tested:                                                                |                                 |  |  |  |  |  |

|-------------------------------------------------------------------------------|---------------------------------|--|--|--|--|--|

| Mode Freq C1 C2                                                               |                                 |  |  |  |  |  |

| HS 20.0 MHz 15-33 pF 15-33 pF                                                 |                                 |  |  |  |  |  |

| These values are for design guidance only.<br>See notes following this table. |                                 |  |  |  |  |  |

| Crystals Used                                                                 |                                 |  |  |  |  |  |

| 20.0 MHz                                                                      | Epson CA-301 20.000M-C ± 30 PPM |  |  |  |  |  |

|                                                                               |                                 |  |  |  |  |  |

- **Note 1:** Higher capacitance increases the stability of the oscillator, but also increases the start-up time.

- 2: Rs may be required in HS mode to avoid overdriving crystals with low drive level specification.

- 3: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components, or verify oscillator performance.

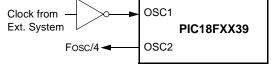

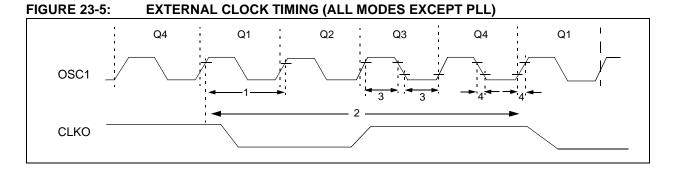

### 2.3 External Clock Input

The EC and ECIO Oscillator modes require an external clock source to be connected to the OSC1 pin. The feedback device between OSC1 and OSC2 is turned off in these modes to save current. There is no oscillator start-up time required after a Power-on Reset or after a recovery from SLEEP mode.

In the EC Oscillator mode, the oscillator frequency divided by 4 is available on the OSC2 pin. This signal may be used for test purposes or to synchronize other logic. Figure 2-3 shows the pin connections for the EC Oscillator mode.

# FIGURE 2-3: EXTERNAL CLOCK INPUT OPERATION (EC CONFIGURATION)

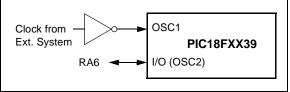

The ECIO Oscillator mode functions like the EC mode, except that the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6). Figure 2-4 shows the pin connections for the ECIO Oscillator mode.

### FIGURE 2-4: EXTERNAL CLOCK INPUT OPERATION (ECIO CONFIGURATION)

## 2.4 HS/PLL

A Phase Locked Loop circuit is provided as a programmable option for users that want to multiply the frequency of the incoming crystal oscillator signal by 4. For an input clock frequency of 5 MHz, the internal clock frequency will be multiplied to 20 MHz. This is useful for customers who are concerned with EMI due to high frequency crystals.

The PLL can only be enabled when the oscillator configuration bits are programmed for HS mode. If they are programmed for any other mode, the PLL is not enabled and the system clock will come directly from OSC1.

The PLL is one of the modes specified by the FOSC<2:0> configuration bits. The Oscillator mode is specified during device programming.

A PLL lock timer is used to ensure that the PLL has locked before device execution starts. The PLL lock timer has a time-out that is called TPLL.

#### 4.2 Return Address Stack

The return address stack allows any combination of up to 31 program calls and interrupts to occur. The PC (Program Counter) is pushed onto the stack when a CALL or RCALL instruction is executed, or an interrupt is acknowledged. The PC value is pulled off the stack on a RETURN, RETLW or a RETFIE instruction. PCLATU and PCLATH are not affected by any of the RETURN or CALL instructions.

The stack operates as a 31-word by 21-bit RAM and a 5-bit stack pointer, with the stack pointer initialized to 00000b after all RESETS. There is no RAM associated with stack pointer 00000b. This is only a RESET value. During a CALL type instruction, causing a push onto the stack, the stack pointer is first incremented and the RAM location pointed to by the stack pointer is written with the contents of the PC. During a RETURN type instruction, causing a pop from the stack, the contents of the RAM location pointed to by the STKPTR are transferred to the PC and then the stack pointer is decremented.

The stack space is not part of either program or data space. The stack pointer is readable and writable, and the address on the top of the stack is readable and writable through SFR registers. Data can also be pushed to, or popped from the stack using the top-of-stack SFRs. Status bits indicate if the stack pointer is at, or beyond the 31 levels provided.

#### 4.2.1 TOP-OF-STACK ACCESS

The top of the stack is readable and writable. Three register locations, TOSU, TOSH and TOSL hold the contents of the stack location pointed to by the STKPTR register. This allows users to implement a software stack if necessary. After a CALL, RCALL or interrupt, the software can read the pushed value by reading the TOSU, TOSH and TOSL registers. These values can be placed on a user defined software stack. At return time, the software can replace the TOSU, TOSH and TOSL and do a return.

The user must disable the global interrupt enable bits during this time to prevent inadvertent stack operations.

#### 4.2.2 RETURN STACK POINTER (STKPTR)

The STKPTR register contains the stack pointer value, the STKFUL (stack full) status bit, and the STKUNF (stack underflow) status bits. Register 4-1 shows the STKPTR register. The value of the stack pointer can be 0 through 31. The stack pointer increments when values are pushed onto the stack and decrements when values are popped off the stack. At RESET, the stack pointer value will be '0'. The user may read and write the stack pointer value. This feature can be used by a Real-Time Operating System for return stack maintenance.

After the PC is pushed onto the stack 31 times (without popping any values off the stack), the STKFUL bit is set. The STKFUL bit can only be cleared in software or by a POR.

The action that takes place when the stack becomes full depends on the state of the STVREN (Stack Overflow Reset Enable) configuration bit. Refer to Section 21.0 for a description of the device configuration bits. If STVREN is set (default), the 31st push will push the (PC + 2) value onto the stack, set the STKFUL bit, and reset the device. The STKFUL bit will remain set and the stack pointer will be set to '0'.

If STVREN is cleared, the STKFUL bit will be set on the 31st push and the stack pointer will increment to 31. Any additional pushes will not overwrite the 31st push, and STKPTR will remain at 31.

When the stack has been popped enough times to unload the stack, the next pop will return a value of zero to the PC and sets the STKUNF bit, while the stack pointer remains at '0'. The STKUNF bit will remain set until cleared in software or a POR occurs.

**Note:** Returning a value of zero to the PC on an underflow has the effect of vectoring the program to the RESET vector, where the stack conditions can be verified and appropriate actions can be taken.

#### 4.14 RCON Register

The Reset Control (RCON) register contains flag bits that allow differentiation between the <u>sources of a</u> <u>device RESET</u>. These flags include the TO, PD, POR, BOR and RI bits. This register is readable and writable.

For PIC18FXX39 devices, the IPEN bit must always be set (= 1) for the ProMPT kernel to function correctly. Refer to Section 8.0 (page 69) for a more detailed discussion.

- Note 1: If the BOREN configuration bit is set (Brown-out Reset enabled), the BOR bit is '1' on a Power-on Reset. After a Brownout Reset has occurred, the BOR bit will be cleared, and must be set by firmware to indicate the occurrence of the next Brown-out Reset.

- 2: It is recommended that the POR bit be set after a Power-on Reset has been detected, so that subsequent Power-on Resets may be detected.

#### REGISTER 4-3: RCON REGISTER

| R/W-0 | U-0 | U-0 | R/W-1 | R-1 | R-1 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-----|-----|-------|-------|

| IPEN  | —   | —   | RI    | TO  | PD  | POR   | BOR   |

| bit 7 |     |     |       |     |     |       | bit 0 |

| bit 7  | IPEN: Interrupt Priority Enal                                                                                      | ble bit             |                                    |

|--------|--------------------------------------------------------------------------------------------------------------------|---------------------|------------------------------------|

|        | Always maintain this bit set                                                                                       |                     | of ProMPT kernel.                  |

| bit 6- | -                                                                                                                  |                     |                                    |

| bit 4  | _ `                                                                                                                |                     |                                    |

|        | 1 = The RESET instruction<br>0 = The RESET instruction<br>(must be set in software                                 | was executed causir | 5                                  |

| bit 3  | <b>TO:</b> Watchdog Time-out Fla                                                                                   | ig bit              |                                    |

|        | <ul> <li>1 = After power-up, CLRWD</li> <li>0 = A WDT time-out occurrence</li> </ul>                               |                     | EP instruction                     |

| bit 2  | PD: Power-down Detection                                                                                           | Flag bit            |                                    |

|        | 1 = After power-up or by the $0 = $ By execution of the SLE                                                        |                     | )                                  |

| bit 1  | POR: Power-on Reset Statu                                                                                          | us bit              |                                    |

|        | 1 = A Power-on Reset has                                                                                           | not occurred        |                                    |

|        | <ul> <li>0 = A Power-on Reset occu<br/>(must be set in software)</li> </ul>                                        |                     | eset occurs)                       |

| bit 0  | <b>BOR:</b> Brown-out Reset Stat                                                                                   | tus bit             |                                    |

|        | <ul> <li>1 = A Brown-out Reset has</li> <li>0 = A Brown-out Reset occ</li> <li>(must be act in activer)</li> </ul> | urred               |                                    |

|        | (must be set in software                                                                                           |                     |                                    |

|        | Legend:                                                                                                            |                     |                                    |

|        | R = Readable bit                                                                                                   | W = Writable bit    | U = Unimplemented bit, read as '0' |

- n = Value at POR

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

#### 8.6 INT0 Interrupt

External interrupts on the RB0/INT0, RB1/INT1 and RB2/INT2 pins are edge triggered: either rising, if the corresponding INTEDGx bit is set in the INTCON2 register, or falling, if the INTEDGx bit is clear. When a valid edge appears on the RBx/INTx pin, the corresponding flag bit INTxF is set. This interrupt can be disabled by clearing the corresponding enable bit INTxE. Flag bit INTxF must be cleared in software in the Interrupt Service Routine before re-enabling the interrupt. All external interrupts (INT0, INT1 and INT2) can wake-up the processor from SLEEP, if bit INTxE was set prior to going into SLEEP. If the global interrupt enable bit GIE is set, the processor will branch to the interrupt vector following wake-up.

The INT0 interrupt is always configured as a high priority interrupt, and cannot be reconfigured. Interrupt priority for INT1 and INT2 is determined by the value contained in the interrupt priority bits, INT1IP (INTCON3<6>) and INT2IP (INTCON3<7>).

Because it is always configured as a high priority interrupt, INTO cannot be used in conjunction with the ProMPT kernel; it must always be disabled (INTCON<4> = 0). Failure to do this may result in erratic operation of the motor control.

#### 8.7 TMR0 Interrupt

In 8-bit mode (which is the default), an overflow in the TMR0 register (FFh  $\rightarrow$  00h) will set flag bit TMR0IF. In 16-bit mode, an overflow in the TMR0H:TMR0L register pair (FFFh  $\rightarrow$  0000h) will set flag bit TMR0IF. The interrupt can be enabled or disabled by setting or clearing enable bit TMR0IE (INTCON<5>). Interrupt priority for Timer0 is determined by the value contained in the interrupt priority bit TMR0IP (INTCON2<2>). See Section 10.0 for further details on the Timer0 module.

#### 8.8 PORTB Interrupt-on-Change

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled or disabled by setting or clearing the enable bit RBIE (INTCON<3>). Interrupt priority for PORTB interrupton-change is determined by the value contained in the interrupt priority bit RBIP (INTCON2<0>).

### 8.9 Context Saving During Interrupts

During an interrupt, the return PC value is saved on the stack. Additionally, the WREG, STATUS and BSR registers are saved on the fast return stack. If a fast return from interrupt is not used (see Section 4.3), the user may need to save the WREG, STATUS and BSR registers in software. Depending on the user's application, other registers may also need to be saved. Example 8-1 saves and restores the WREG, STATUS and BSR registers during an Interrupt Service Routine.

|  | EXAMPLE 8-1: | SAVING STATUS, | WREG AND BSR | <b>REGISTERS IN RAM</b> |

|--|--------------|----------------|--------------|-------------------------|

|--|--------------|----------------|--------------|-------------------------|

| MOVWF<br>MOVFF<br>MOVFF | W_TEMP<br>STATUS, STATUS_TEMP<br>BSR, BSR TEMP | ; W_TEMP is in virtual bank<br>; STATUS_TEMP located anywhere<br>; BSR located anywhere |

|-------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------|

| ;<br>; USER<br>;        | _<br>ISR CODE                                  |                                                                                         |

| MOVFF                   | BSR_TEMP, BSR                                  | ; Restore BSR                                                                           |

| MOVF                    | W_TEMP, W                                      | ; Restore WREG                                                                          |

| MOVFF                   | STATUS_TEMP, STATUS                            | ; Restore STATUS                                                                        |

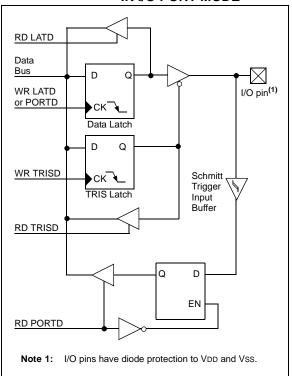

#### 9.4 PORTD, TRISD and LATD Registers

This section is applicable only to the PIC18F4X39 devices.

PORTD is an 8-bit wide, bi-directional port. The corresponding Data Direction register is TRISD. Setting a TRISD bit (= 1) will make the corresponding PORTD pin an input (i.e., put the corresponding output driver in a High Impedance mode). Clearing a TRISD bit (= 0) will make the corresponding PORTD pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATD) is also memory mapped. Read-modify-write operations on the LATD register reads and writes the latched output value for PORTD.

PORTD is an 8-bit port with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

| Note: | On a   | Power-on     | Reset,    | these | pins | are |

|-------|--------|--------------|-----------|-------|------|-----|

|       | config | ured as digi | tal input | s.    |      |     |

PORTD can be configured as an 8-bit wide microprocessor port (parallel slave port) by setting control bit PSPMODE (TRISE<4>). In this mode, the input buffers are TTL. See Section 9.6 for additional information on the Parallel Slave Port (PSP).

#### EXAMPLE 9-4: INITIALIZING PORTD

|       | • ••  |                         |

|-------|-------|-------------------------|

| CLRF  | PORTD | ; Initialize PORTD by   |

|       |       | ; clearing output       |

|       |       | ; data latches          |

| CLRF  | LATD  | ; Alternate method      |

|       |       | ; to clear output       |

|       |       | ; data latches          |

| MOVLW | 0xCF  | ; Value used to         |

|       |       | ; initialize data       |

|       |       | ; direction             |

| MOVWF | TRISD | ; Set RD<3:0> as inputs |

|       |       | ; RD<5:4> as outputs    |

|       |       | ; RD<7:6> as inputs     |

|       |       |                         |

#### FIGURE 9-8:

#### PORTD BLOCK DIAGRAM IN I/O PORT MODE

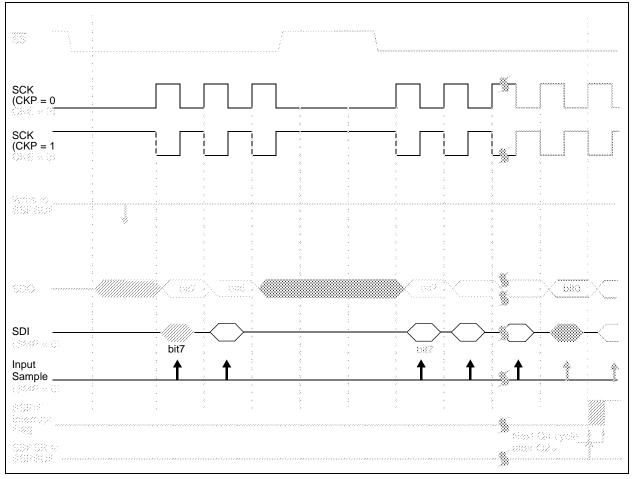

#### 16.3.6 SLAVE MODE

In Slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched, the SSPIF interrupt flag bit is set.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times, as specified in the electrical specifications.

While in SLEEP mode, the slave can transmit/receive data. When a byte is received, the device will wake-up from SLEEP.

#### 16.3.7 SLAVE SELECT SYNCHRONIZATION

The  $\overline{SS}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with  $\overline{SS}$  pin control enabled (SSPCON1<3:0> = 04h). The pin must not be driven low for the  $\overline{SS}$  pin to function as an input. The Data Latch must be high. When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven. When the  $\overline{SS}$  pin goes high, the SDO pin is no

longer driven, even if in the middle of a transmitted byte, and becomes a floating output. External pull-up/ pull-down resistors may be desirable, depending on the application.

| <b>Note 1:</b> When the SPI is in Slave mode with $\overline{SS}$ | Note |

|-------------------------------------------------------------------|------|

| pin control enabled (SSPCON<3:0> =                                |      |

| 0100), the SPI module will reset if the $\overline{SS}$           |      |

| pin is set to VDD.                                                |      |

2: If the SPI is used in Slave mode with CKE set, then the SS pin control must be enabled.

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the  $\overline{SS}$  pin to a high level or clearing the SSPEN bit.

To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver, the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function), since it cannot create a bus conflict.

#### FIGURE 16-4: SLAVE SYNCHRONIZATION WAVEFORM

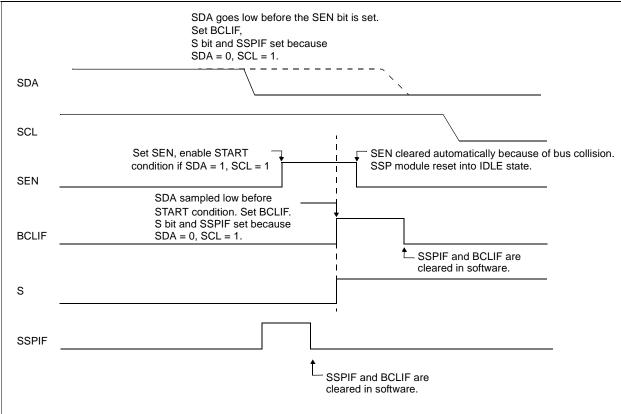

#### 16.4.17.1 Bus Collision During a START Condition

During a START condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the START condition (Figure 16-26).

- b) SCL is sampled low before SDA is asserted low (Figure 16-27).

During a START condition, both the SDA and the SCL pins are monitored.

If the SDA pin is already low, or the SCL pin is already low, then all of the following occur:

- the START condition is aborted,

- the BCLIF flag is set, and

- the MSSP module is reset to its IDLE state (Figure 16-26).

The START condition begins with the SDA and SCL pins de-asserted. When the SDA pin is sampled high, the baud rate generator is loaded from SSPADD<6:0> and counts down to '0'. If the SCL pin is sampled low while SDA is high, a bus collision occurs, because it is assumed that another master is attempting to drive a data '1' during the START condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 16-28). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The baud rate generator is then reloaded and counts down to '0', and during this time, if the SCL pins are sampled as '0', a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a START condition, is that no two bus masters can assert a START condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision, because the two masters must be allowed to arbitrate the first address following the START condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated START or STOP conditions.

#### FIGURE 16-26: BUS COLLISION DURING START CONDITION (SDA ONLY)

#### 17.3 USART Synchronous Master Mode

In Synchronous Master mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit SYNC (TXSTA<4>). In addition, enable bit SPEN (RCSTA<7>) is set in order to configure the RC6/TX/CK and RC7/RX/DT I/O pins to CK (clock) and DT (data) lines, respectively. The Master mode indicates that the processor transmits the master clock on the CK line. The Master mode is entered by setting bit CSRC (TXSTA<7>).

#### 17.3.1 USART SYNCHRONOUS MASTER TRANSMISSION

The USART transmitter block diagram is shown in Figure 17-1. The heart of the transmitter is the Transmit (serial) Shift Register (TSR). The shift register obtains its data from the read/write transmit buffer register TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TCYCLE), the TXREG is empty and interrupt bit TXIF (PIR1<4>) is set. The interrupt can be enabled/disabled by setting/clearing enable bit TXIE

(PIE1<4>). Flag bit TXIF will be set, regardless of the state of enable bit TXIE, and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. TRMT is a read only bit, which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory, so it is not available to the user.

To set up a Synchronous Master Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 17.1).

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN, and CSRC.

- 3. If interrupts are desired, set enable bit TXIE.

- 4. If 9-bit transmission is desired, set bit TX9.

- 5. Enable the transmission by setting bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

Note: TXIF is not cleared immediately upon loading data into the transmit buffer TXREG. The flag bit becomes valid in the second instruction cycle following the load instruction.

| TABLE 17-8: | REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION |

|-------------|-----------------------------------------------------------|

|-------------|-----------------------------------------------------------|

| Name   | Bit 7                                             | Bit 6         | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0     | Value on<br>POR, BOR | Value on<br>All Other<br>RESETS |

|--------|---------------------------------------------------|---------------|--------|--------|-------|--------|--------|-----------|----------------------|---------------------------------|

| INTCON | GIE/<br>GIEH                                      | PEIE/<br>GIEL | TMR0IE | INT0IE | RBIE  | TMR0IF | INTOIF | RBIF      | 0000 000x            | 0000 000u                       |

| PIR1   | PSPIF <sup>(1)</sup>                              | ADIF          | RCIF   | TXIF   | SSPIF | _      | TMR2IF | TMR1IF    | 0000 0000            | 0000 0000                       |

| PIE1   | PSPIE <sup>(1)</sup>                              | ADIE          | RCIE   | TXIE   | SSPIE | —      | TMR2IE | TMR1IE    | 0000 0000            | 0000 0000                       |

| IPR1   | PSPIP <sup>(1)</sup>                              | ADIP          | RCIP   | TXIP   | SSPIP | —      | TMR2IP | TMR1IP    | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN                                              | RX9           | SREN   | CREN   | ADDEN | FERR   | OERR   | RX9D      | 0000 -00x            | 0000 -00x                       |

| TXREG  | G USART Transmit Register 0000 0000               |               |        |        |       |        |        | 0000 0000 |                      |                                 |

| TXSTA  | CSRC                                              | TX9           | TXEN   | SYNC   | _     | BRGH   | TRMT   | TX9D      | 0000 -010            | 0000 -010                       |

| SPBRG  | Baud Rate Generator Register         0000 0000 00 |               |        |        |       |        |        | 0000 0000 |                      |                                 |

Legend: x = unknown, - = unimplemented, read as '0'.

Shaded cells are not used for Synchronous Master Transmission.

**Note 1:** The PSPIF, PSPIE and PSPIP bits are reserved on the PIC18F2X39 devices; always maintain these bits clear.

#### 19.2.1 REFERENCE VOLTAGE SET POINT

The Internal Reference Voltage of the LVD module may be used by other internal circuitry (the Programmable Brown-out Reset). If these circuits are disabled (lower current consumption), the reference voltage circuit requires a time to become stable before a low voltage condition can be reliably detected. This time is invariant of system clock speed. This start-up time is specified in electrical specification parameter 36. The low voltage interrupt flag will not be enabled until a stable reference voltage is reached. Refer to the waveform in Figure 19-4.

#### 19.2.2 CURRENT CONSUMPTION

When the module is enabled, the LVD comparator and voltage divider are enabled and will consume static current. The voltage divider can be tapped from multiple places in the resistor array. Total current consumption, when enabled, is specified in electrical specification parameter #D022B.

#### 19.3 Operation During SLEEP

When enabled, the LVD circuitry continues to operate during SLEEP. If the device voltage crosses the trip point, the LVDIF bit will be set and the device will wakeup from SLEEP. Device execution will continue from the interrupt vector address if interrupts have been globally enabled.

#### 19.4 Effects of a RESET

A device RESET forces all registers to their RESET state. This forces the LVD module to be turned off.

# 20.0 SPECIAL FEATURES OF THE CPU

There are several features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving Operating modes and offer code protection. These are:

- OSC Selection

- RESET

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code Protection

- ID Locations

- In-Circuit Serial Programming

All PIC18FXX39 devices have a Watchdog Timer, which is permanently enabled via the configuration bits, or software controlled. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay on power-up only, designed to keep the part in RESET while the power supply stabilizes. With these two timers on-chip, most applications need no external RESET circuitry.

SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer Wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost, while the LP crystal option saves power. A set of configuration bits are used to select various options.

### 20.1 Configuration Bits

The configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped starting at program memory location 300000h.

The user will note that address 300000h is beyond the user program memory space. In fact, it belongs to the configuration memory space (300000h - 3FFFFh), which can only be accessed using Table Reads and Table Writes.

Programming the configuration registers is done in a manner similar to programming the FLASH memory (see Section 5.5.1). The only difference is the configuration registers are written a byte at a time. The sequence of events for programming configuration registers is:

- 1. Load table pointer with address of configuration register being written.

- 2. Write a single byte using the TBLWT instruction.

- 3. Set EEPGD to point to program memory, set the CFGS bit to access configuration registers, and set WREN to enable byte writes.

- 4. Disable interrupts.

- 5. Write 55h to EECON2.

- 6. Write AAh to EECON2.

- 7. Set the WR bit. This will begin the write cycle.

- 8. CPU will stall for duration of write (approximately 2 ms using internal timer).

- 9. Execute a NOP.

- 10. Re-enable interrupts.

### TABLE 21-1: OPCODE FIELD DESCRIPTIONS

| Field           | Description                                                                                                                                                    |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| a               | RAM access bit                                                                                                                                                 |

|                 | a = 0: RAM location in Access RAM (BSR register is ignored)                                                                                                    |

|                 | a = 1: RAM bank is specified by BSR register                                                                                                                   |

| bbb             | Bit address within an 8-bit file register (0 to 7).                                                                                                            |

| BSR             | Bank Select Register. Used to select the current RAM bank.                                                                                                     |

| d               | Destination select bit<br>d = 0: store result in WREG,<br>d = 1: store result in file register f.                                                              |

| dest            | Destination, either the WREG register or the specified register file location.                                                                                 |

| f               | 8-bit Register file address (0x00 to 0xFF).                                                                                                                    |

| fs              | 12-bit Register file address (0x000 to 0xFFF). This is the source address.                                                                                     |

| fd              | 12-bit Register file address (0x000 to 0xFFF). This is the destination address.                                                                                |

| k               | Literal field, constant data or label (may be either an 8-bit, 12-bit or a 20-bit value).                                                                      |

| label           | Label name.                                                                                                                                                    |

|                 |                                                                                                                                                                |

| mm              | The mode of the TBLPTR register for the Table Read and Table Write instructions.<br>Only used with Table Read and Table Write instructions:                    |

| *               | No Change to register (such as TBLPTR with Table Reads and Writes).                                                                                            |

| *+              | Post-Increment register (such as TBLPTR with Table Reads and Writes).                                                                                          |

| * _             | Post-Decrement register (such as TBLPTR with Table Reads and Writes).                                                                                          |

| +*              | Pre-Increment register (such as TBLPTR with Table Reads and Writes).                                                                                           |

| n               | The relative address (2's complement number) for relative branch instructions, or the direct address for Call/Branch and Return instructions.                  |

| PRODH           | Product of Multiply high byte.                                                                                                                                 |

| PRODL           | Product of Multiply low byte.                                                                                                                                  |

| s               | Fast Call/Return mode select bit                                                                                                                               |

|                 | s = 0: do not update into/from shadow registers                                                                                                                |

|                 | s = 1: certain registers loaded into/from shadow registers (Fast mode)                                                                                         |

| u               | Unused or Unchanged.                                                                                                                                           |

| WREG            | Working register (accumulator).                                                                                                                                |

| x               | Don't care (0 or 1).<br>The assembler will generate code with $x = 0$ . It is the recommended form of use for compatibility with all Microchip software tools. |

| TBLPTR          | 21-bit Table Pointer (points to a Program Memory location).                                                                                                    |

| TABLAT          | 8-bit Table Latch.                                                                                                                                             |

| TOS             | Top-of-Stack.                                                                                                                                                  |

| PC              | Program Counter.                                                                                                                                               |

| PCL             | Program Counter Low Byte.                                                                                                                                      |

| PCH             | Program Counter High Byte.                                                                                                                                     |

| PCLATH          | Program Counter High Byte Latch.                                                                                                                               |

| PCLATU          | Program Counter Upper Byte Latch.                                                                                                                              |

| GIE             | Global Interrupt Enable bit.                                                                                                                                   |

| WDT             | Watchdog Timer.                                                                                                                                                |

| TO              | Time-out bit.                                                                                                                                                  |

| PD              | Power-down bit.                                                                                                                                                |

| C, DC, Z, OV, N |                                                                                                                                                                |

| []              | Optional.                                                                                                                                                      |

| ( )             | Contents.                                                                                                                                                      |

| $\rightarrow$   | Assigned to.                                                                                                                                                   |

|                 | Register bit field.                                                                                                                                            |

| < >             | In the set of.                                                                                                                                                 |

| e               |                                                                                                                                                                |

| italics         | User defined term (font is courier).                                                                                                                           |

| Mnemo   | onic, | Description                    |        | 16-Bit Instruction Word |      |      |      | Status                 | Natas |

|---------|-------|--------------------------------|--------|-------------------------|------|------|------|------------------------|-------|

| Opera   | nds   | Description                    | Cycles | MSb                     |      |      | LSb  | Affected               | Notes |

| CONTROL | OPERA | TIONS                          |        |                         |      |      |      |                        |       |

| BC      | n     | Branch if Carry                | 1 (2)  | 1110                    | 0010 | nnnn | nnnn | None                   |       |

| BN      | n     | Branch if Negative             | 1 (2)  | 1110                    | 0110 | nnnn | nnnn | None                   |       |

| BNC     | n     | Branch if Not Carry            | 1 (2)  | 1110                    | 0011 | nnnn | nnnn | None                   |       |

| BNN     | n     | Branch if Not Negative         | 1 (2)  | 1110                    | 0111 | nnnn | nnnn | None                   |       |

| BNOV    | n     | Branch if Not Overflow         | 1 (2)  | 1110                    | 0101 | nnnn | nnnn | None                   |       |

| BNZ     | n     | Branch if Not Zero             | 2      | 1110                    | 0001 | nnnn | nnnn | None                   |       |

| BOV     | n     | Branch if Overflow             | 1 (2)  | 1110                    | 0100 | nnnn | nnnn | None                   |       |

| BRA     | n     | Branch Unconditionally         | 1 (2)  | 1101                    | 0nnn | nnnn | nnnn | None                   |       |

| BZ      | n     | Branch if Zero                 | 1 (2)  | 1110                    | 0000 | nnnn | nnnn | None                   |       |

| CALL    | n, s  | Call subroutine 1st word       | 2      | 1110                    | 110s | kkkk | kkkk | None                   |       |

|         |       | 2nd word                       |        | 1111                    | kkkk | kkkk | kkkk |                        |       |

| CLRWDT  | —     | Clear Watchdog Timer           | 1      | 0000                    | 0000 | 0000 | 0100 | TO, PD                 |       |

| DAW     | —     | Decimal Adjust WREG            | 1      | 0000                    | 0000 | 0000 | 0111 | С                      |       |

| GOTO    | n     | Go to address 1st word         | 2      | 1110                    | 1111 | kkkk | kkkk | None                   |       |

|         |       | 2nd word                       |        | 1111                    | kkkk | kkkk | kkkk |                        |       |

| NOP     | —     | No Operation                   | 1      | 0000                    | 0000 | 0000 | 0000 | None                   |       |

| NOP     | —     | No Operation                   | 1      | 1111                    | xxxx | XXXX | xxxx | None                   | 4     |

| POP     | —     | Pop top of return stack (TOS)  | 1      | 0000                    | 0000 | 0000 | 0110 | None                   |       |

| PUSH    | —     | Push top of return stack (TOS) | 1      | 0000                    | 0000 | 0000 | 0101 | None                   |       |

| RCALL   | n     | Relative Call                  | 2      | 1101                    | 1nnn | nnnn | nnnn | None                   |       |

| RESET   |       | Software device RESET          | 1      | 0000                    | 0000 | 1111 | 1111 | All                    |       |

| RETFIE  | S     | Return from interrupt enable   | 2      | 0000                    | 0000 | 0001 | 000s | GIE/GIEH,<br>PEIE/GIEL |       |

| RETLW   | k     | Return with literal in WREG    | 2      | 0000                    | 1100 | kkkk | kkkk | None                   |       |

| RETURN  | s     | Return from Subroutine         | 2      | 0000                    | 0000 | 0001 | 001s | None                   |       |

| SLEEP   | _     | Go into Standby mode           | 1      | 0000                    | 0000 | 0000 | 0011 | TO, PD                 |       |

#### TABLE 21-2: PIC18FXXX INSTRUCTION SET (CONTINUED)

**Note** 1: When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are 2-word instructions. The second word of these instructions will be executed as a NOP, unless the first word of the instruction retrieves the information embedded in these 16-bits. This ensures that all program memory locations have a valid instruction.

5: If the Table Write starts the write cycle to internal memory, the write will continue until terminated.

| BRA   |                                                        | Unconditi                                                                                                | onal Brancl             | h               | B                       | SF                                                 | Bit Set f                                                                                                             |                 |                       |  |

|-------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------|-----------------|-------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------|--|

| Synt  | ax:                                                    | [ <i>label</i> ] BRA n                                                                                   |                         | Sy              | ntax:                   | [ <i>label</i> ] B                                 | [label] BSF f,b[,a]                                                                                                   |                 |                       |  |

| Ope   | rands:                                                 | -1024 ≤ n :                                                                                              | ≤ 1023                  |                 | O                       | perands:                                           | $0 \le f \le 255$                                                                                                     | 5               |                       |  |

| Ope   | ration:                                                | (PC) + 2 +                                                                                               | $2n \to PC$             |                 |                         |                                                    | 0 ≤ b ≤ 7<br>a ∈ [0,1]                                                                                                |                 |                       |  |

| Statu | us Affected:                                           | None                                                                                                     |                         |                 | Or                      | peration:                                          | a ∈ [0,1]<br>1 → f <b></b>                                                                                            |                 |                       |  |

| Enco  | oding:                                                 | 1101                                                                                                     | 0nnn nni                | nn nnnn         | •                       | atus Affected:                                     | None $I \rightarrow I < D >$                                                                                          |                 |                       |  |

| Des   | cription:                                              | Add the 2's complement number<br>'2n' to the PC. Since the PC will<br>have incremented to fetch the next |                         | Er              | acoding:<br>escription: | ng: 1000 bbba ffff ff                              |                                                                                                                       |                 |                       |  |

|       |                                                        | instruction, the new address will be<br>PC+2+2n. This instruction is a<br>two-cycle instruction.         |                         |                 |                         | ·                                                  | Access Bank will be selected, over-<br>riding the BSR value. If 'a' = 1, then<br>the bank will be selected as per the |                 |                       |  |

| Wor   | ds:                                                    | 1                                                                                                        |                         |                 |                         |                                                    | BSR value                                                                                                             | ).              |                       |  |

| Cycl  | es:                                                    | 2                                                                                                        |                         |                 |                         | ords:                                              | 1                                                                                                                     |                 |                       |  |

| QC    | ycle Activity:                                         |                                                                                                          |                         |                 | C                       | cles:                                              | 1                                                                                                                     |                 |                       |  |

|       | Q1                                                     | Q2                                                                                                       | Q3                      | Q4              | Q                       | Cycle Activity:                                    |                                                                                                                       |                 |                       |  |

|       | Decode                                                 | Read literal                                                                                             | Process                 | Write to PC     |                         | Q1                                                 | Q2                                                                                                                    | Q3              | Q4                    |  |

|       | No<br>operation                                        | 'n'<br>No<br>operation                                                                                   | Data<br>No<br>operation | No<br>operation |                         | Decode                                             | Read<br>register 'f'                                                                                                  | Process<br>Data | Write<br>register 'f' |  |

|       |                                                        |                                                                                                          |                         |                 | <u>E&gt;</u>            | ample:                                             | BSF F                                                                                                                 | LAG_REG, 7      | , 1                   |  |

|       | <u>nple</u> :<br>Before Instru<br>PC<br>After Instruct | = ado                                                                                                    | BRA Jump<br>dress (HERE |                 |                         | Before Instru<br>FLAG_R<br>After Instruc<br>FLAG_R | EG = 0x0<br>tion                                                                                                      |                 |                       |  |

|       | PC                                                     | = ado                                                                                                    | dress (Jump)            | )               |                         |                                                    |                                                                                                                       |                 |                       |  |

| DEC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | FSZ                                      | Decremer                                            | Decrement f, skip if 0          |                           |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----------------------------------------------------|---------------------------------|---------------------------|--|--|--|--|

| Synt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ax:                                      | [label]                                             | DECFSZ f[,                      | d [,a]]                   |  |  |  |  |

| Ope                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | rands:                                   | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$ |                                 |                           |  |  |  |  |

| Ope                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ration:                                  | $(f) - 1 \rightarrow c$ skip if resu                |                                 |                           |  |  |  |  |

| Statu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | us Affected:                             | None                                                |                                 |                           |  |  |  |  |

| Enco                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | oding:                                   | 0010                                                | 11da ffi                        | f ffff                    |  |  |  |  |

| Description:<br>The contents of register 'f' are dec<br>remented. If 'd' is 0, the result is<br>placed in W. If 'd' is 1, the result is<br>placed back in register 'f' (default).<br>If the result is 0, the next instruc-<br>tion, which is already fetched, is<br>discarded, and a NOP is executed<br>instead, making it a two-cycle<br>instruction. If 'a' is 0, the Access<br>Bank will be selected, overriding<br>the BSR value. If 'a' = 1, then the<br>bank will be selected as per the<br>BSR value (default). |                                          |                                                     |                                 |                           |  |  |  |  |

| Wor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ds:                                      | 1                                                   |                                 |                           |  |  |  |  |

| Cycl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                          | by                                                  | ycles if skip a<br>a 2-word ins | and followed<br>truction. |  |  |  |  |

| QC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Sycle Activity                           |                                                     | 00                              | 04                        |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Q1<br>Decode                             | Q2<br>Read                                          | Q3<br>Process                   | Q4<br>Write to            |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Decode                                   | register 'f'                                        | Data                            | destination               |  |  |  |  |

| lf sk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | kip:                                     |                                                     |                                 |                           |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Q1                                       | Q2                                                  | Q3                              | Q4                        |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | No                                       | No                                                  | No                              | No                        |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | operation                                | operation                                           | operation                       | operation                 |  |  |  |  |

| lf sk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -                                        | ved by 2-wor                                        |                                 |                           |  |  |  |  |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Q1                                       | Q2                                                  | Q3                              | Q4                        |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | No<br>operation                          | No<br>operation                                     | No<br>operation                 | No<br>operation           |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | No                                       | No                                                  | No                              | No                        |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | operation                                | operation                                           | operation                       | operation                 |  |  |  |  |

| <u>Exar</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <u>nple</u> :                            | HERE                                                | DECFSZ<br>GOTO                  | CNT, 1, 1<br>LOOP         |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Before Instru<br>PC                      | uction                                              | (HERE)                          |                           |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | PC = Address (HERE)<br>After Instruction |                                                     |                                 |                           |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CNT<br>If CNT<br>PC                      | = CNT - 1<br>= 0;                                   | G (CONTINUE                     | •)                        |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | If CNT<br>PC                             | ≠ 0;                                                | (CONTINUE) (HERE+2)             | • /                       |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 0                                      |                                                     | (                               |                           |  |  |  |  |

| DCFSNZ                                                  | Decreme                                                                                                                                                                                                                                      | nt f, skip if n                                                                                                                                            | ot 0                    |  |  |

|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|--|

| Syntax:                                                 | [label]                                                                                                                                                                                                                                      | DCFSNZ f[                                                                                                                                                  | ,d [,a]                 |  |  |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$    |                                                                                                                                                                                                                                              |                                                                                                                                                            |                         |  |  |

| Operation:                                              | (f) – 1 $\rightarrow$ of skip if rest                                                                                                                                                                                                        |                                                                                                                                                            |                         |  |  |