### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 21                                                                        |

| Program Memory Size        | 24KB (12K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 1408 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 5x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2539-i-sp |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

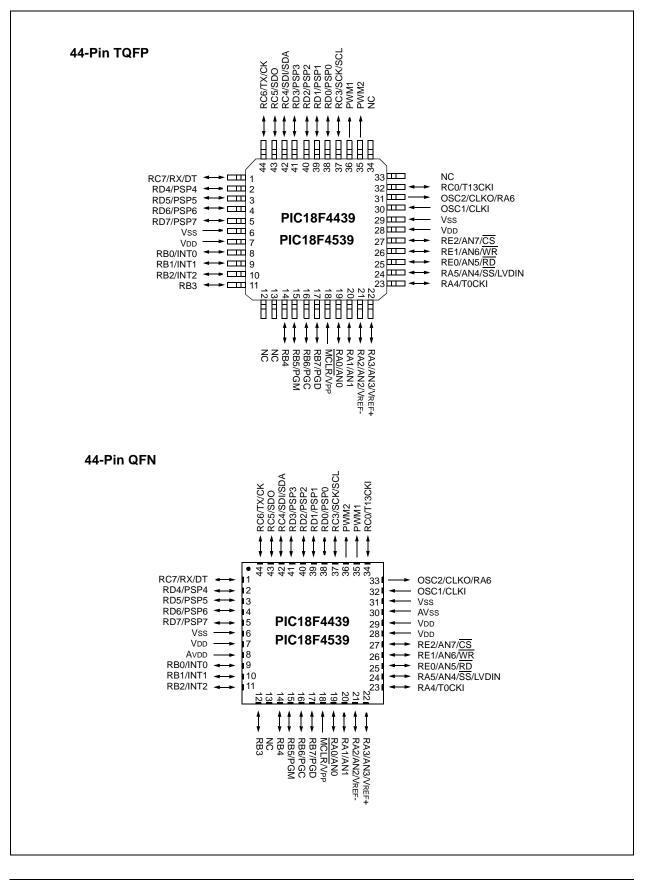

### **Pin Diagrams**

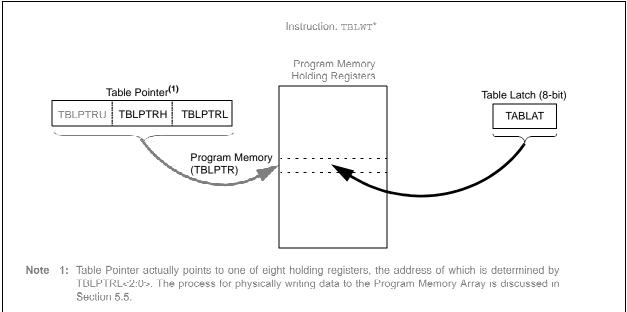

### FIGURE 5-2: TABLE WRITE OPERATION

### 5.2 Control Registers

Several control registers are used in conjunction with the TBLRD and TBLWT instructions. These include the:

- EECON1 register

- EECON2 register

- TABLAT register

- TBLPTR registers

### 5.2.1 EECON1 AND EECON2 REGISTERS

EECON1 is the control register for memory accesses.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the memory write and erase sequences.

Control bit EEPGD determines if the access will be a program or data EEPROM memory access. When clear, any subsequent operations will operate on the data EEPROM memory. When set, any subsequent operations will operate on the program memory.

Control bit CFGS determines if the access will be to the configuration registers or to program memory/data EEPROM memory. When set, subsequent operations will operate on configuration registers, regardless of EEPGD (see Section 20.0, "Special Features of the CPU"). When clear, memory selection access is determined by EEPGD.

The FREE bit, when set, will allow a program memory erase operation. When the FREE bit is set, the erase operation is initiated on the next WR command. When FREE is clear, only writes are enabled.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a MCLR Reset, or a WDT Time-out Reset, during normal operation. In these situations, the user can check the WRERR bit and rewrite the location. It is necessary to reload the data and address registers (EEDATA and EEADR), due to RESET values of zero.

Control bit WR initiates write operations. This bit cannot be cleared, only set, in software. It is cleared in hardware at the completion of the write operation. The inability to clear the WR bit in software prevents the accidental or premature termination of a write operation.

**Note:** Interrupt flag bit, EEIF in the PIR2 register, is set when the write is complete. It must be cleared in software.

### 5.3 Reading the FLASH Program Memory

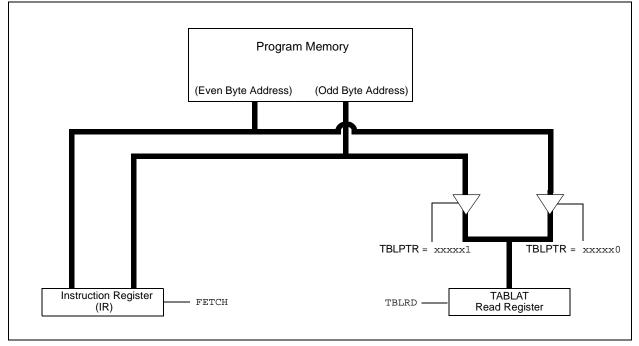

The TBLRD instruction is used to retrieve data from program memory and place into data RAM. Table Reads from program memory are performed one byte at a time. TBLPTR points to a byte address in program space. Executing TBLRD places the byte pointed to into TABLAT. In addition, TBLPTR can be modified automatically for the next Table Read operation.

The internal program memory is typically organized by words. The Least Significant bit of the address selects between the high and low bytes of the word. Figure 5-4 shows the interface between the internal program memory and the TABLAT.

### FIGURE 5-4: READS FROM FLASH PROGRAM MEMORY

### EXAMPLE 5-1: READING A FLASH PROGRAM MEMORY WORD

|           | MOVLW CODE_ADDR_UPPER<br>MOVWF TBLPTRU<br>MOVLW CODE_ADDR_HIGH<br>MOVWF TBLPTRH<br>MOVLW CODE_ADDR_LOW<br>MOVWF TBLPTRL | ; Load TBLPTR with the base<br>; address of the word |

|-----------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| READ_WORD |                                                                                                                         |                                                      |

|           | TBLRD*+                                                                                                                 | ; read into TABLAT and increment                     |

|           | MOVF TABLAT, W                                                                                                          | ; get data                                           |

|           | MOVWF WORD_EVEN                                                                                                         |                                                      |

|           | TBLRD*+                                                                                                                 | ; read into TABLAT and increment                     |

|           | MOVF TABLAT, W                                                                                                          | ; get data                                           |

|           | MOVWF WORD_ODD                                                                                                          |                                                      |

|           |                                                                                                                         |                                                      |

| TABLE 6-1: REGISTERS ASSOCIATED WITH DATA EEPROM MEMOR |

|--------------------------------------------------------|

|--------------------------------------------------------|

| Address | Name   | Bit 7        | Bit 6                | Bit 5     | Bit 4      | Bit 3        | Bit 2 | Bit 1  | Bit 0 | Value on:<br>POR, BOR | Value on<br>All Other<br>RESETS |

|---------|--------|--------------|----------------------|-----------|------------|--------------|-------|--------|-------|-----------------------|---------------------------------|

| FF2h    | INTCON | GIE/<br>GIEH | PEIE/<br>GIEL        | TOIE      | INTE       | RBIE         | TOIF  | INTF   | RBIF  | 0000 000x             | 0000 000u                       |

| FA9h    | EEADR  | EEPRON       | 1 Address            |           | 0000 0000  | 0000 0000    |       |        |       |                       |                                 |

| FA8h    | EEDATA | EEPRON       | EEPROM Data Register |           |            |              |       |        |       |                       | 0000 0000                       |

| FA7h    | EECON2 | EEPRON       | 1 Control R          | Register2 | (not a phy | /sical regis | ter)  |        |       | —                     | —                               |

| FA6h    | EECON1 | EEPGD        | CFGS                 | —         | FREE       | WRERR        | WREN  | WR     | RD    | xx-0 x000             | uu-0 u000                       |

| FA2h    | IPR2   | —            | _                    | _         | EEIP       | BCLIP        | LVDIP | TMR3IP | _     | 1 1111                | 1 1111                          |

| FA1h    | PIR2   | —            | —                    | —         | EEIF       | BCLIF        | LVDIF | TMR3IF | —     | 0 0000                | 0 0000                          |

| FA0h    | PIE2   | _            | _                    | _         | EEIE       | BCLIE        | LVDIE | TMR3IE | _     | 0 0000                | 0 0000                          |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used during FLASH/EEPROM access.

### 8.6 INT0 Interrupt

External interrupts on the RB0/INT0, RB1/INT1 and RB2/INT2 pins are edge triggered: either rising, if the corresponding INTEDGx bit is set in the INTCON2 register, or falling, if the INTEDGx bit is clear. When a valid edge appears on the RBx/INTx pin, the corresponding flag bit INTxF is set. This interrupt can be disabled by clearing the corresponding enable bit INTxE. Flag bit INTxF must be cleared in software in the Interrupt Service Routine before re-enabling the interrupt. All external interrupts (INT0, INT1 and INT2) can wake-up the processor from SLEEP, if bit INTxE was set prior to going into SLEEP. If the global interrupt enable bit GIE is set, the processor will branch to the interrupt vector following wake-up.

The INT0 interrupt is always configured as a high priority interrupt, and cannot be reconfigured. Interrupt priority for INT1 and INT2 is determined by the value contained in the interrupt priority bits, INT1IP (INTCON3<6>) and INT2IP (INTCON3<7>).

Because it is always configured as a high priority interrupt, INTO cannot be used in conjunction with the ProMPT kernel; it must always be disabled (INTCON<4> = 0). Failure to do this may result in erratic operation of the motor control.

### 8.7 TMR0 Interrupt

In 8-bit mode (which is the default), an overflow in the TMR0 register (FFh  $\rightarrow$  00h) will set flag bit TMR0IF. In 16-bit mode, an overflow in the TMR0H:TMR0L register pair (FFFh  $\rightarrow$  0000h) will set flag bit TMR0IF. The interrupt can be enabled or disabled by setting or clearing enable bit TMR0IE (INTCON<5>). Interrupt priority for Timer0 is determined by the value contained in the interrupt priority bit TMR0IP (INTCON2<2>). See Section 10.0 for further details on the Timer0 module.

### 8.8 PORTB Interrupt-on-Change

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled or disabled by setting or clearing the enable bit RBIE (INTCON<3>). Interrupt priority for PORTB interrupton-change is determined by the value contained in the interrupt priority bit RBIP (INTCON2<0>).

### 8.9 Context Saving During Interrupts

During an interrupt, the return PC value is saved on the stack. Additionally, the WREG, STATUS and BSR registers are saved on the fast return stack. If a fast return from interrupt is not used (see Section 4.3), the user may need to save the WREG, STATUS and BSR registers in software. Depending on the user's application, other registers may also need to be saved. Example 8-1 saves and restores the WREG, STATUS and BSR registers during an Interrupt Service Routine.

|  | EXAMPLE 8-1: | SAVING STATUS, | WREG AND BSR | <b>REGISTERS IN RAM</b> |

|--|--------------|----------------|--------------|-------------------------|

|--|--------------|----------------|--------------|-------------------------|

| MOVWF<br>MOVFF<br>MOVFF | W_TEMP<br>STATUS, STATUS_TEMP<br>BSR, BSR TEMP | ; W_TEMP is in virtual bank<br>; STATUS_TEMP located anywhere<br>; BSR located anywhere |

|-------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------|

| ;<br>; USER<br>;        | _<br>ISR CODE                                  |                                                                                         |

| MOVFF                   | BSR_TEMP, BSR                                  | ; Restore BSR                                                                           |

| MOVF                    | W_TEMP, W                                      | ; Restore WREG                                                                          |

| MOVFF                   | STATUS_TEMP, STATUS                            | ; Restore STATUS                                                                        |

NOTES:

### 16.4.6.1 I<sup>2</sup>C Master Mode Operation

The master device generates all of the serial clock pulses and the START and STOP conditions. A transfer is ended with a STOP condition, or with a Repeated START condition. Since the Repeated START condition is also the beginning of the next serial transfer, the  $I^2C$  bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an Acknowledge bit is received. START and STOP conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the R/W bit. In this case, the R/W bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate the receive bit. Serial data is received via SDA, while SCL outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an Acknowledge bit is transmitted. START and STOP conditions indicate the beginning and end of transmission.

The baud rate generator used for the SPI mode operation is used to set the SCL clock frequency for either 100 kHz, 400 kHz or 1 MHz  $I^2C$  operation. See Section 16.4.7 ("Baud Rate Generator"), for more detail. A typical transmit sequence would go as follows:

- 1. The user generates a START condition by setting the START enable bit, SEN (SSPCON2<0>).

- SSPIF is set. The MSSP module will wait the required start time before any other operation takes place.

- 3. The user loads the SSPBUF with the slave address to transmit.

- 4. Address is shifted out the SDA pin until all 8 bits are transmitted.

- 5. The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register (SSPCON2<6>).

- 6. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- 7. The user loads the SSPBUF with eight bits of data.

- 8. Data is shifted out the SDA pin until all 8 bits are transmitted.

- The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register (SSPCON2<6>).

- 10. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- 11. The user generates a STOP condition by setting the STOP enable bit PEN (SSPCON2<2>).

- 12. Interrupt is generated once the STOP condition is complete.

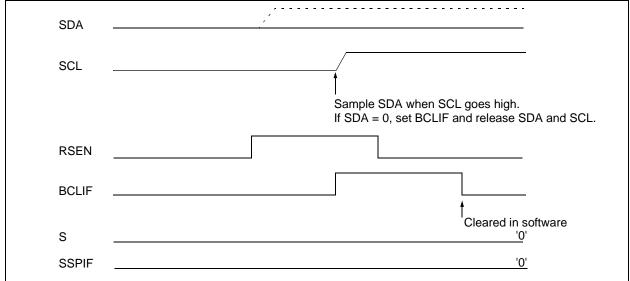

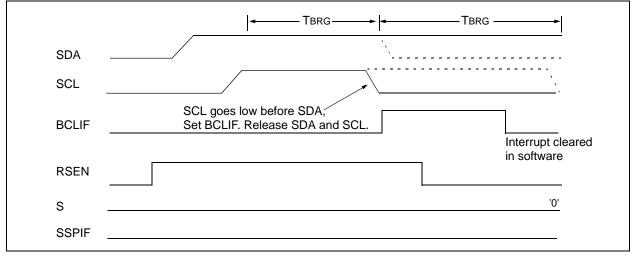

## 16.4.17.2 Bus Collision During a Repeated START Condition

During a Repeated START condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level.

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user de-asserts SDA and the pin is allowed to float high, the BRG is loaded with SSPADD<6:0> and counts down to '0'. The SCL pin is then de-asserted, and when sampled high, the SDA pin is sampled.

If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 16-29). If SDA is sampled high, the BRG is

reloaded and begins counting. If SDA goes from high to low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high to low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated START condition, see Figure 16-30.

If, at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated START condition is complete.

### FIGURE 16-30: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

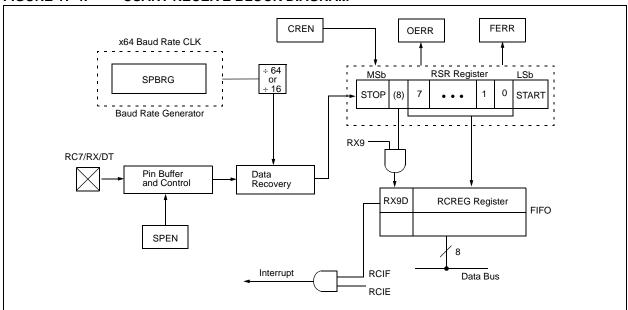

### 17.2.2 USART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 17-4. The data is received on the RC7/RX/DT pin and drives the data recovery block. The data recovery block is actually a high speed shifter operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate or at Fosc. This mode would typically be used in RS-232 systems.

To set up an Asynchronous Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH (Section 17.1).

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, set enable bit RCIE.

- 4. If 9-bit reception is desired, set bit RX9.

- 5. Enable the reception by setting bit CREN.

- Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 7. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If any error occurred, clear the error by clearing enable bit CREN.

- 10. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

## 17.2.3 SETTING UP 9-BIT MODE WITH ADDRESS DETECT

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is required, set the BRGH bit.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If interrupts are required, set the RCEN bit and select the desired priority level with the RCIP bit.

- 4. Set the RX9 bit to enable 9-bit reception.

- 5. Set the ADDEN bit to enable address detect.

- 6. Enable reception by setting the CREN bit.

- 7. The RCIF bit will be set when reception is complete. The interrupt will be acknowledged if the RCIE and GIE bits are set.

- 8. Read the RCSTA register to determine if any error occurred during reception, as well as read bit 9 of data (if applicable).

- 9. Read RCREG to determine if the device is being addressed.

- 10. If any error occurred, clear the CREN bit.

- 11. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and interrupt the CPU.

### FIGURE 17-4: USART RECEIVE BLOCK DIAGRAM

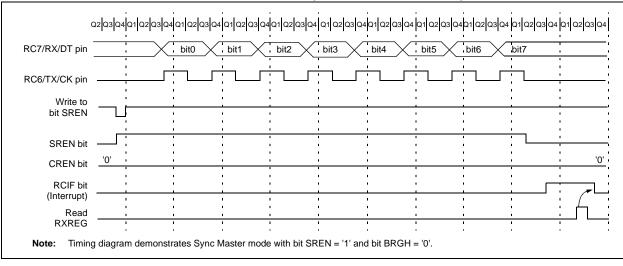

### 17.3.2 USART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either enable bit SREN (RCSTA<5>), or enable bit CREN (RCSTA<4>). Data is sampled on the RC7/RX/DT pin on the falling edge of the clock. If enable bit SREN is set, only a single word is received. If enable bit CREN is set, the reception is continuous until CREN is cleared. If both bits are set, then CREN takes precedence.

To set up a Synchronous Master Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 17.1).

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- 4. If interrupts are desired, set enable bit RCIE.

- 5. If 9-bit reception is desired, set bit RX9.

- 6. If a single reception is required, set bit SREN. For continuous reception, set bit CREN.

- Interrupt flag bit RCIF will be set when reception is complete and an interrupt will be generated if the enable bit RCIE was set.

- 8. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREG register.

- 10. If any error occurred, clear the error by clearing bit CREN.

- 11. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

| Name   | Bit 7                              | Bit 6         | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>All Other<br>RESETS |

|--------|------------------------------------|---------------|--------|--------|-------|--------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE/<br>GIEH                       | PEIE/<br>GIEL | TMR0IE | INTOIE | RBIE  | TMR0IF | INTOIF | RBIF   | 0000 000x            | 0000 000u                       |

| PIR1   | PSPIF <sup>(1)</sup>               | ADIF          | RCIF   | TXIF   | SSPIF | -      | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| PIE1   | PSPIE <sup>(1)</sup>               | ADIE          | RCIE   | TXIE   | SSPIE | -      | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| IPR1   | PSPIP <sup>(1)</sup>               | ADIP          | RCIP   | TXIP   | SSPIP | _      | TMR2IP | TMR1IP | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN                               | RX9           | SREN   | CREN   | ADDEN | FERR   | OERR   | RX9D   | 0000 -00x            | 0000 -00x                       |

| RCREG  | G USART Receive Register           |               |        |        |       |        |        |        | 0000 0000            | 0000 0000                       |

| TXSTA  | CSRC                               | TX9           | TXEN   | SYNC   | _     | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

| SPBRG  | SPBRG Baud Rate Generator Register |               |        |        |       |        |        |        |                      | 0000 0000                       |

### TABLE 17-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for Synchronous Master Reception. **Note 1:** The PSPIF, PSPIE and PSPIP bits are reserved on the PIC18F2X39 devices; always maintain these bits clear.

### FIGURE 17-8: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

### TABLE 21-2: PIC18FXXX INSTRUCTION SET

| Mnemonic,<br>Operands |                                 | Description                              | Cycles     | 16-Bit Instruction Word |              |      |      | Status          | Natas      |

|-----------------------|---------------------------------|------------------------------------------|------------|-------------------------|--------------|------|------|-----------------|------------|

|                       |                                 | Description                              | Cycles     | MSb                     |              |      | LSb  | Affected        | Notes      |

| BYTE-ORI              | ENTED F                         | ILE REGISTER OPERATIONS                  |            |                         |              |      |      |                 |            |

| ADDWF                 | f, d, a                         | Add WREG and f                           | 1          | 0010                    | 01da0        | ffff | ffff | C, DC, Z, OV, N | 1, 2       |

| ADDWFC                | f, d, a                         | Add WREG and Carry bit to f              | 1          | 0010                    | 0da          | ffff | ffff | C, DC, Z, OV, N | 1, 2       |

| ANDWF                 | f, d, a                         | AND WREG with f                          | 1          | 0001                    | 01da         | ffff | ffff | Z, N            | 1,2        |

| CLRF                  | f, a                            | Clear f                                  | 1          | 0110                    | 101a         | ffff | ffff | Z               | 2          |

| COMF                  | f, d, a                         | Complement f                             | 1          | 0001                    | 11da         | ffff | ffff | Z, N            | 1, 2       |

| CPFSEQ                | f, a                            | Compare f with WREG, skip =              | 1 (2 or 3) | 0110                    | 001a         | ffff | ffff | None            | 4          |

| CPFSGT                | f, a                            | Compare f with WREG, skip >              | 1 (2 or 3) | 0110                    | 010a         | ffff | ffff | None            | 4          |

| CPFSLT                | f, a                            | Compare f with WREG, skip <              | 1 (2 or 3) | 0110                    | 000a         | ffff | ffff | None            | 1, 2       |

| DECF                  | f. d. a                         | Decrement f                              | 1          | 0000                    | 01da         | ffff | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| DECFSZ                | f, d, a                         | Decrement f, Skip if 0                   | 1 (2 or 3) | 0010                    | 11da         | ffff | ffff | None            | 1, 2, 3, 4 |

| DCFSNZ                | f, d, a                         | Decrement f, Skip if Not 0               | 1 (2 or 3) | 0100                    | 11da         | ffff | ffff | None            | 1, 2       |

| INCF                  | f, d, a                         | Increment f                              | 1          | 0010                    | 10da         | ffff | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| INCFSZ                | f, d, a                         | Increment f, Skip if 0                   | 1 (2 or 3) | 0011                    | 11da         | ffff | ffff | None            | 4          |

| INFSNZ                | f, d, a                         | Increment f, Skip if Not 0               | 1 (2 or 3) | 0100                    | 10da         | ffff | ffff | None            | 1, 2       |

| IORWF                 | f, d, a                         | Inclusive OR WREG with f                 | 1          | 0001                    | 00da         | ffff | ffff | Z, N            | 1, 2       |

| MOVF                  | f, d, a                         | Move f                                   | 1          | 0101                    | 00da         | ffff | ffff | Z, N            | 1          |

| MOVFF                 | f <sub>s</sub> , f <sub>d</sub> | Move f <sub>s</sub> (source) to 1st word | 2          | 1100                    | ffff         | ffff | ffff | None            |            |

|                       | ·s, ·u                          | f <sub>d</sub> (destination) 2nd word    |            | 1111                    | ffff         | ffff | ffff |                 |            |

| MOVWF                 | f, a                            | Move WREG to f                           | 1          | 0110                    | 111a         | ffff | ffff | None            |            |

| MULWF                 | f, a                            | Multiply WREG with f                     | 1          | 0000                    | 001a         | ffff | ffff | None            |            |

| NEGF                  | f, a                            | Negate f                                 | 1          | 0110                    | 110a         | ffff | ffff | C, DC, Z, OV, N | 1, 2       |

| RLCF                  | f, d, a                         | Rotate Left f through Carry              | 1          | 0011                    | 01da         | ffff | ffff | C, Z, N         | .,_        |

| RLNCF                 | f, d, a                         | Rotate Left f (No Carry)                 | 1          | 0100                    | 01da         | ffff | ffff | Z, N            | 1, 2       |

| RRCF                  | f, d, a                         | Rotate Right f through Carry             | 1          | 0011                    | 00da         | ffff | ffff | C, Z, N         | ., -       |

| RRNCF                 | , ,                             | Rotate Right f (No Carry)                | 1          | 0100                    | 00da         | ffff | ffff | Z, N            |            |

| SETF                  | f, a, a                         | Set f                                    | 1          | 0110                    | 100a         | ffff | ffff | None            |            |

| SUBFWB                | f, d, a                         | Subtract f from WREG with borrow         | 1          | 0101                    | 01da         | ffff | ffff | C, DC, Z, OV, N | 1, 2       |

| SUBWF                 | f, d, a                         | Subtract WREG from f                     | 1          | 0101                    | 11da         | ffff | ffff | C, DC, Z, OV, N |            |

| SUBWFB                | f, d, a                         | Subtract WREG from f with<br>borrow      | 1          | 0101                    | 10da         | ffff | ffff | C, DC, Z, OV, N | 1, 2       |

| SWAPF                 | f, d, a                         | Swap nibbles in f                        | 1          | 0011                    | 10da         | ffff | ffff | None            | 4          |

| TSTFSZ                | f, a                            | Test f, skip if 0                        | 1 (2 or 3) | 0110                    | 100a<br>011a | ffff | ffff | None            | 4<br>1, 2  |

| XORWF                 | f, d, a                         | Exclusive OR WREG with f                 | 1 (2 01 3) | 0001                    | 011a<br>10da | ffff | ffff | Z, N            | 1, 2       |

|                       |                                 |                                          | 1          | 0001                    | IUUU         | TTTT | LTTT | 2, 11           |            |

|                       |                                 | E REGISTER OPERATIONS                    |            |                         |              |      |      | 1               | 1          |

| BCF                   | f, b, a                         | Bit Clear f                              | 1          | 1001                    | bbba         | ffff | ffff | None            | 1, 2       |

| BSF                   | f, b, a                         | Bit Set f                                | 1          | 1000                    | bbba         | ffff | ffff | None            | 1, 2       |

| BTFSC                 |                                 | Bit Test f, Skip if Clear                | 1 (2 or 3) | 1011                    | bbba         | ffff | ffff | None            | 3, 4       |

| BTFSS                 | f, b, a                         | Bit Test f, Skip if Set                  | 1 (2 or 3) | 1010                    | bbba         | ffff | ffff | None            | 3, 4       |

| BTG                   | f, d, a                         | Bit Toggle f                             | 1          | 0111                    | bbba         | ffff | ffff | None            | 1, 2       |

**Note** 1: When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are 2-word instructions. The second word of these instructions will be executed as a NOP, unless the first word of the instruction retrieves the information embedded in these 16-bits. This ensures that all program memory locations have a valid instruction.

5: If the Table Write starts the write cycle to internal memory, the write will continue until terminated.

|                                                      | Move f to                                                                                                                                                                                                                                       | f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                |                                        |  |  |  |  |  |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------------------|--|--|--|--|--|

| Syntax:                                              | [ label ]                                                                                                                                                                                                                                       | MOVFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | f <sub>s</sub> ,f <sub>d</sub> |                                        |  |  |  |  |  |

| Operands:                                            | •                                                                                                                                                                                                                                               | $\begin{array}{l} 0 \leq f_{s} \leq 4095 \\ 0 \leq f_{d} \leq 4095 \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                |                                        |  |  |  |  |  |

| Operation:                                           | $(f_s) \to f_d$                                                                                                                                                                                                                                 | $(f_s) \rightarrow f_d$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                |                                        |  |  |  |  |  |

| Status Affected:                                     | None                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                |                                        |  |  |  |  |  |

| Encoding:<br>1st word (source)<br>2nd word (destin.) |                                                                                                                                                                                                                                                 | ffff<br>ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ffff<br>ffff                   | ffff <sub>s</sub><br>ffff <sub>d</sub> |  |  |  |  |  |

| Description:                                         | are moved<br>'f <sub>d</sub> '. Locat<br>anywhere<br>space (00<br>of destina<br>where from<br>Either sou<br>W (a useff<br>MOVFF is<br>transferrin<br>to a periph<br>transmit b<br>The MOVF<br>the PCL, 7<br>the destin<br><b>Note:</b> TH<br>sh | The contents of source register ${}^{f}s'$<br>are moved to destination register<br>${}^{f}d'$ . Location of source ${}^{f}s'$ can be<br>anywhere in the 4096 byte data<br>space (000h to FFFh), and location<br>of destination ${}^{f}d'$ can also be any-<br>where from 000h to FFFh.<br>Either source or destination can be<br>W (a useful special situation).<br>MOVFF is particularly useful for<br>transferring a data memory location<br>to a peripheral register (such as the<br>transmit buffer or an I/O port).<br>The MOVFF instruction cannot use<br>the PCL, TOSU, TOSH or TOSL as<br>the destination register. |                                |                                        |  |  |  |  |  |

| Words:                                               | 2                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                |                                        |  |  |  |  |  |

| Cycles:                                              | 2 (3)                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                |                                        |  |  |  |  |  |

| Q Cycle Activity:                                    |                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                |                                        |  |  |  |  |  |

| Q1                                                   | Q2                                                                                                                                                                                                                                              | Q                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3                              | Q4                                     |  |  |  |  |  |

| Decode                                               | Read<br>register 'f'<br>(src)                                                                                                                                                                                                                   | Proce<br>Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                | No<br>operation                        |  |  |  |  |  |

|                                                      | No                                                                                                                                                                                                                                              | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                | Write                                  |  |  |  |  |  |

| Before Instructio | n |       |

|-------------------|---|-------|

| REG1              | = | 0x33  |

| REG2              | = | 0x11  |

| After Instruction |   |       |

| REG1              | = | 0x33, |

| REG2              | = | 0x33  |

| MOV   | MOVLB Move literal to low nibble in BSR |                     |                                                                      |      |                             |  |  |  |  |

|-------|-----------------------------------------|---------------------|----------------------------------------------------------------------|------|-----------------------------|--|--|--|--|

| Synt  | ax:                                     | [ label ]           | MOVLB                                                                | k    |                             |  |  |  |  |

| Oper  | rands:                                  | $0 \le k \le 25$    | 5                                                                    |      |                             |  |  |  |  |

| Oper  | ration:                                 | $k \to BSR$         | $k \rightarrow BSR$                                                  |      |                             |  |  |  |  |

| Statu | is Affected:                            | fected: None        |                                                                      |      |                             |  |  |  |  |

| Enco  | oding:                                  | 0000                | 0001                                                                 | kkkk | kkkk                        |  |  |  |  |

| Desc  | cription:                               |                     | The 8-bit literal 'k' is loaded into the Bank Select Register (BSR). |      |                             |  |  |  |  |

| Word  | ds:                                     | 1                   |                                                                      |      |                             |  |  |  |  |

| Cycle | es:                                     | 1                   |                                                                      |      |                             |  |  |  |  |

| QC    | ycle Activity:                          |                     |                                                                      |      |                             |  |  |  |  |

|       | Q1                                      | Q2                  | Q3                                                                   |      | Q4                          |  |  |  |  |

|       | Decode                                  | Read literal<br>'k' | Proce:<br>Data                                                       |      | Write<br>eral 'k' to<br>BSR |  |  |  |  |

| _     |                                         |                     |                                                                      |      |                             |  |  |  |  |

Example: MOVLB 5

| Before Instruction |      |

|--------------------|------|

| BSR register =     | 0x02 |

| After Instruction  |      |

| BSR register =     | 0x05 |

## 22.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C17 and MPLAB C18 C Compilers

- MPLINK™ Object Linker/

- MPLIB<sup>™</sup> Object Librarian

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- ICEPIC<sup>™</sup> In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD

- Device Programmers

- PRO MATE<sup>®</sup> II Universal Device Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Development Programmer

- Low Cost Demonstration Boards

- PICDEM<sup>™</sup>1 Demonstration Board

- PICDEM 2 Demonstration Board

- PICDEM 3 Demonstration Board

- PICDEM 17 Demonstration Board

- KEELOQ<sup>®</sup> Demonstration Board

### 22.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> based application that contains:

- · An interface to debugging tools

- simulator

- programmer (sold separately)

- emulator (sold separately)

- in-circuit debugger (sold separately)

- A full-featured editor

- · A project manager

- Customizable toolbar and key mapping

- · A status bar

- On-line help

The MPLAB IDE allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- Debug using:

- source files

- absolute listing file

- machine code

The ability to use MPLAB IDE with multiple debugging tools allows users to easily switch from the costeffective simulator to a full-featured emulator with minimal retraining.

### 22.2 MPASM Assembler

The MPASM assembler is a full-featured universal macro assembler for all PIC MCUs.

The MPASM assembler has a command line interface and a Windows shell. It can be used as a stand-alone application on a Windows 3.x or greater system, or it can be used through MPLAB IDE. The MPASM assembler generates relocatable object files for the MPLINK object linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, an absolute LST file that contains source lines and generated machine code, and a COD file for debugging.

The MPASM assembler features include:

- Integration into MPLAB IDE projects.

- User-defined macros to streamline assembly code.

- Conditional assembly for multi-purpose source files.

- Directives that allow complete control over the assembly process.

### 22.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI 'C' compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers, respectively. These compilers provide powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compilers provide symbol information that is compatible with the MPLAB IDE memory display.

### 23.2 DC Characteristics: PIC18FXX39 (Industrial, Extended) PIC18LFXX39 (Industrial) (Continued)

| DC CHARACTERISTICS  |        |                                            | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \end{array}$ |     |       |                                                      |  |

|---------------------|--------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------------------------------------------------------|--|

| Param<br>No.        | Symbol | Characteristic                             | tic Min Max                                                                                                                                                                                                                                                     |     | Units | Conditions                                           |  |

|                     | Vol    | Output Low Voltage                         |                                                                                                                                                                                                                                                                 |     |       |                                                      |  |

| D080                |        | I/O ports                                  | —                                                                                                                                                                                                                                                               | 0.6 | V     | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C          |  |

| D080A               |        |                                            | —                                                                                                                                                                                                                                                               | 0.6 | V     | IOL = 7.0 mA, VDD = 4.5V,<br>-40°C to +125°C         |  |

|                     | Vон    | Output High Voltage <sup>(2)</sup>         |                                                                                                                                                                                                                                                                 |     |       |                                                      |  |

| D090                |        | I/O ports                                  | Vdd - 0.7                                                                                                                                                                                                                                                       | —   | V     | IOH = -3.0 mA, VDD = 4.5V,<br>-40°С to +85°С         |  |

| D090A               |        |                                            | Vdd - 0.7                                                                                                                                                                                                                                                       | —   | V     | IOH = -2.5 mA, VDD = 4.5V,<br>-40°С to +125°С        |  |

| D150                | Vod    | Open Drain High Voltage                    | —                                                                                                                                                                                                                                                               | 8.5 | V     | RA4 pin                                              |  |

|                     |        | Capacitive Loading Specs<br>on Output Pins |                                                                                                                                                                                                                                                                 |     |       |                                                      |  |

| D100 <sup>(3)</sup> | Cosc2  | OSC2 pin                                   | _                                                                                                                                                                                                                                                               | 15  | pF    | In HS mode when external clock is used to drive OSC1 |  |

| D101                | Сю     | All I/O pins                               | —                                                                                                                                                                                                                                                               | 50  | pF    | To meet the AC Timing<br>Specifications              |  |

| D102                | Св     | SCL, SDA                                   | —                                                                                                                                                                                                                                                               | 400 | pF    | In I <sup>2</sup> C mode                             |  |

**Note 1:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

**2:** Negative current is defined as current sourced by the pin.

3: Parameter is characterized but not tested.

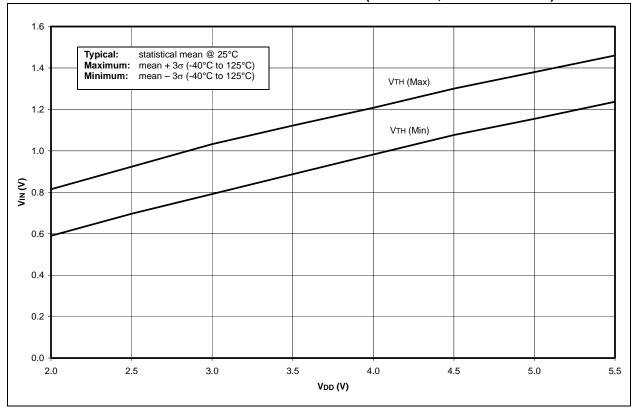

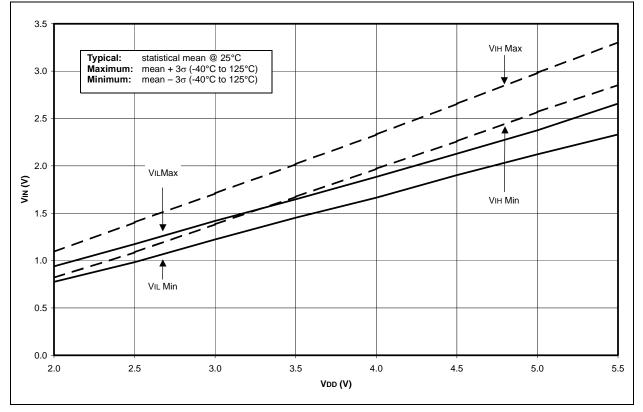

FIGURE 24-17: MINIMUM AND MAXIMUM VIN vs. VDD (TTL INPUT, -40°C TO +125°C)

© 2002-2013 Microchip Technology Inc.

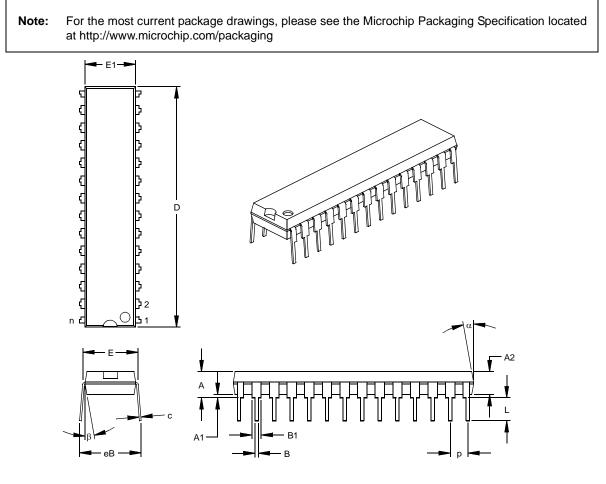

#### 25.2 **Package Details**

The following sections give the technical details of the packages.

### 28-Lead Skinny Plastic Dual In-line (SP) – 300 mil (PDIP)

|                            | Units | INCHES* |       |       | MILLIMETERS |       |       |  |

|----------------------------|-------|---------|-------|-------|-------------|-------|-------|--|

| Dimension Limits           |       | MIN     | NOM   | MAX   | MIN         | NOM   | MAX   |  |

| Number of Pins             | n     |         | 28    |       |             | 28    |       |  |

| Pitch                      | р     |         | .100  |       |             | 2.54  |       |  |

| Top to Seating Plane       | Α     | .140    | .150  | .160  | 3.56        | 3.81  | 4.06  |  |

| Molded Package Thickness   |       | .125    | .130  | .135  | 3.18        | 3.30  | 3.43  |  |

| Base to Seating Plane      | A1    | .015    |       |       | 0.38        |       |       |  |

| Shoulder to Shoulder Width | E     | .300    | .310  | .325  | 7.62        | 7.87  | 8.26  |  |

| Molded Package Width       | E1    | .275    | .285  | .295  | 6.99        | 7.24  | 7.49  |  |

| Overall Length             | D     | 1.345   | 1.365 | 1.385 | 34.16       | 34.67 | 35.18 |  |

| Tip to Seating Plane       | L     | .125    | .130  | .135  | 3.18        | 3.30  | 3.43  |  |

| Lead Thickness             | С     | .008    | .012  | .015  | 0.20        | 0.29  | 0.38  |  |

| Upper Lead Width           | B1    | .040    | .053  | .065  | 1.02        | 1.33  | 1.65  |  |

| Lower Lead Width           | В     | .016    | .019  | .022  | 0.41        | 0.48  | 0.56  |  |

| Overall Row Spacing        | § eB  | .320    | .350  | .430  | 8.13        | 8.89  | 10.92 |  |

| Mold Draft Angle Top       | α     | 5       | 10    | 15    | 5           | 10    | 15    |  |

| Mold Draft Angle Bottom β  |       | 5       | 10    | 15    | 5           | 10    | 15    |  |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimension D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MO-095

Drawing No. C04-070

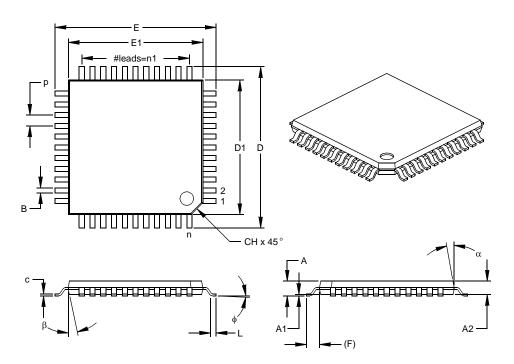

### 44-Lead Plastic Thin Quad Flatpack (PT) 10x10x1 mm Body, 1.0/0.10 mm Lead Form (TQFP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units     | INCHES |                                                        |                                                        | MILLIMETERS*                                           |                                                        |                                                        |

|-----------|--------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|

| on Limits | MIN    | NOM                                                    | MAX                                                    | MIN                                                    | NOM                                                    | MAX                                                    |

| n         |        | 44                                                     |                                                        |                                                        | 44                                                     |                                                        |

| р         |        | .031                                                   |                                                        |                                                        | 0.80                                                   |                                                        |

| n1        |        | 11                                                     |                                                        |                                                        | 11                                                     |                                                        |

| Α         | .039   | .043                                                   | .047                                                   | 1.00                                                   | 1.10                                                   | 1.20                                                   |

| A2        | .037   | .039                                                   | .041                                                   | 0.95                                                   | 1.00                                                   | 1.05                                                   |

| A1        | .002   | .004                                                   | .006                                                   | 0.05                                                   | 0.10                                                   | 0.15                                                   |

| L         | .018   | .024                                                   | .030                                                   | 0.45                                                   | 0.60                                                   | 0.75                                                   |

| (F)       |        | .039                                                   |                                                        | 1.00                                                   |                                                        |                                                        |

| ø         | 0      | 3.5                                                    | 7                                                      | 0                                                      | 3.5                                                    | 7                                                      |

| Е         | .463   | .472                                                   | .482                                                   | 11.75                                                  | 12.00                                                  | 12.25                                                  |

| D         | .463   | .472                                                   | .482                                                   | 11.75                                                  | 12.00                                                  | 12.25                                                  |

| E1        | .390   | .394                                                   | .398                                                   | 9.90                                                   | 10.00                                                  | 10.10                                                  |

| D1        | .390   | .394                                                   | .398                                                   | 9.90                                                   | 10.00                                                  | 10.10                                                  |

| С         | .004   | .006                                                   | .008                                                   | 0.09                                                   | 0.15                                                   | 0.20                                                   |

| В         | .012   | .015                                                   | .017                                                   | 0.30                                                   | 0.38                                                   | 0.44                                                   |

| CH        | .025   | .035                                                   | .045                                                   | 0.64                                                   | 0.89                                                   | 1.14                                                   |

| α         | 5      | 10                                                     | 15                                                     | 5                                                      | 10                                                     | 15                                                     |

| β         | 5      | 10                                                     | 15                                                     | 5                                                      | 10                                                     | 15                                                     |

|           |        | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-026 Drawing No. C04-076

| PIC18F4X39 Pin Functions              |

|---------------------------------------|

| MCLR/VPP                              |

| OSC1/CLKI                             |

| OSC2/CLKO/RA614                       |

| PWM116                                |

| PWM216                                |

| RA0/AN014                             |

| RA1/AN114                             |

| RA2/AN2/VREF14                        |

| RA3/AN3/VREF+14                       |

| RA4/T0CKI                             |

| RA5/AN4/SS/LVDIN14                    |

| RB0/INT15                             |

| RB1/INT115                            |

| RB2/INT215                            |

| RB315                                 |

| RB415                                 |

| RB5/PGM15                             |

| RB6/PGC15                             |

| RB7/PGD15                             |

| RC0/T13CKI                            |

| RC3/SCK/SCL16                         |

| RC4/SDI/SDA16                         |

| RC5/SDO16                             |

| RC6/TX/CK                             |

| RC7/RX/DT16                           |

| RD0/PSP017                            |

| RD1/PSP117                            |

| RD2/PSP217                            |

| RD3/PSP317                            |

| RD4/PSP417                            |

| RD5/PSP517                            |

| RD6/PSP617                            |

| RD7/PSP717                            |

| RE0/AN5/ <u>RD</u>                    |

| RE1/AN6/WR18                          |

| RE2/AN7/CS18                          |

| VDD                                   |

| Vss                                   |

| PIC18FXX39 Voltage-Frequency Graph    |

| (Industrial)                          |

| PIC18LFXX39 Voltage-Frequency Graph   |

| (Industrial)                          |

| PICDEM 1 Low Cost PIC MCU             |

| Demonstration Board                   |

| PICDEM 17 Demonstration Board         |

| PICDEM 2 Low Cost PIC16CXX            |

| Demonstration Board                   |

| PICDEM 3 Low Cost PIC16CXXX           |

| Demonstration Board                   |

| PICSTART Plus Entry Level Development |

| Programmer                            |

| PIE Registers                         |

| Pinout I/O Descriptions               |

| PIC18F2X39                            |

| PIC18F4X39                            |

| PIR Registers                         |

| PLL Lock Time-out24                   |

|                                       |

| Pointer, FSR                          |

|                                       |

| PORTA                                                                                                                                                                            |                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| Associated Registers                                                                                                                                                             | . 85                                             |

| LATA Register                                                                                                                                                                    | . 83                                             |

| PORTA Register                                                                                                                                                                   |                                                  |

| TRISA Register                                                                                                                                                                   | . 83                                             |

| PORTB                                                                                                                                                                            |                                                  |

| Associated Registers                                                                                                                                                             | . 88                                             |

| LATB Register                                                                                                                                                                    | . 86                                             |

| PORTB Register                                                                                                                                                                   | . 86                                             |

| RB0/INT Pin, External                                                                                                                                                            |                                                  |

| RB7:RB4 Interrupt-on-Change Flag                                                                                                                                                 |                                                  |

| (RBIF Bit)                                                                                                                                                                       | . 86                                             |

| TRISB Register                                                                                                                                                                   |                                                  |

| PORTC                                                                                                                                                                            |                                                  |

| Associated Registers                                                                                                                                                             | . 90                                             |

| LATC Register                                                                                                                                                                    | . 89                                             |

| PORTC Register                                                                                                                                                                   | . 89                                             |

| RC3/SCK/SCL Pin                                                                                                                                                                  | 139                                              |

| RC7/RX/DT Pin                                                                                                                                                                    | 168                                              |

| TRISC Register                                                                                                                                                                   | 165                                              |

| PORTD                                                                                                                                                                            |                                                  |