Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40MHz                                                                    |

| Connectivity               | I²C, SPI, UART/USART                                                     |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                               |

| Number of I/O              | 32                                                                       |

| Program Memory Size        | 12KB (6K x 16)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 640 × 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                              |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4439-e-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

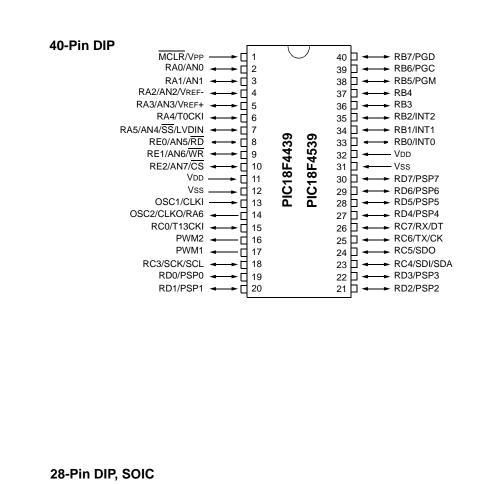

#### Pin Diagrams (Cont.'d)

MCLR/VPP --> □ ° 1 RA0/AN0 🔶 2 27 🗖 ↔ RB6/PGC 26 🗖 ↔ RB5/PGM RA1/AN1 🔶 🗌 3 RA2/AN2/VREF- -→ 🗌 25 🗖 🖚 RB4 4 PIC18F2439 PIC18F2539 24 □ ← RB3 RA3/AN3/Vref+ ----5 RA4/T0CKI ↔ □ RA5/AN4/SS/LVDIN ↔ □ 23 - RB2/INT2 6 22 🗖 🔶 RB1/INT1 7 → 🗌 Vss -8 OSC1/CLKI -→ 🗌 9 20 🗖 🖛 VDD - 🗌 10 19 🗖 🖛 Vss OSC2/CLKO/RA6 🗲 18 → RC7/RX/DT 17 → RC6/TX/CK RC0/T13CKI -- 🗆 11 PWM2 🗕 12 PWM1 ↔ □ 13 16 → RC5/SDO RC3/SCK/SCL ←► 14

**Preliminary**

## 2.5 Effects of SLEEP Mode on the On-Chip Oscillator

When the device executes a SLEEP instruction, the oscillator is turned off and the device is held at the beginning of an instruction cycle (Q1 state). With the oscillator off, the OSC1 and OSC2 signals will stop oscillating. Since all the transistor switching currents have been removed, SLEEP mode achieves the lowest current consumption of the device (only leakage currents). Enabling any on-chip feature that will operate during SLEEP will increase the current consumed during SLEEP. The user can wake from SLEEP through external RESET, Watchdog Timer Reset, or through an interrupt.

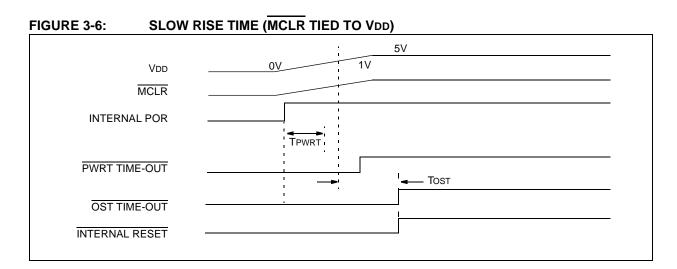

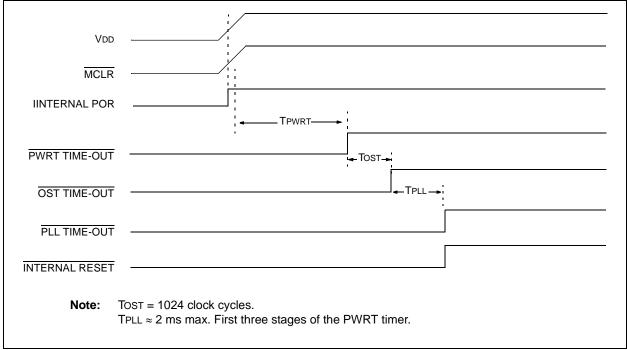

## 2.6 Power-up Delays

Power-up delays are controlled by two timers, so that no external RESET circuitry is required for most applications. The delays ensure that the device is kept in RESET, until the device power supply and clock are stable. For additional information on RESET operation, see Section 3.0. The first timer is the Power-up Timer (PWRT), which optionally provides a fixed delay of 72 ms (nominal) on power-up only (POR and BOR). The second timer is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable.

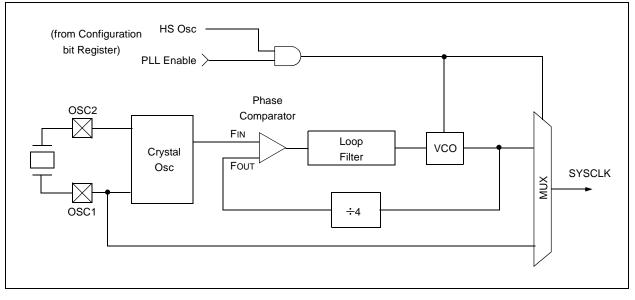

With the PLL enabled (HS/PLL Oscillator mode), the time-out sequence following a Power-on Reset is different from other Oscillator modes. The time-out sequence is as follows:

- 1. The PWRT time-out is invoked after a POR time delay has expired.

- 2. The Oscillator Start-up Timer (OST) is invoked. However, this is still not a sufficient amount of time to allow the PLL to lock at high frequencies.

- 3. The PWRT timer is used to provide an additional fixed 2 ms (nominal) time-out to allow the PLL ample time to lock to the incoming clock frequency.

### TABLE 2-2: OSC1 AND OSC2 PIN STATES IN SLEEP MODE

| OSC Mode | OSC1 Pin                                               | OSC2 Pin                                                  |

|----------|--------------------------------------------------------|-----------------------------------------------------------|

| ECIO     | Floating                                               | Configured as PORTA, bit 6                                |

| EC       | Floating                                               | At logic low                                              |

| HS       | Feedback inverter disabled, at quiescent voltage level | Feedback inverter disabled, at quiescent<br>voltage level |

**Note:** See Table 3-1 in the "**Reset**" section, for time-outs due to SLEEP and MCLR Reset.

<sup>© 2002-2013</sup> Microchip Technology Inc.

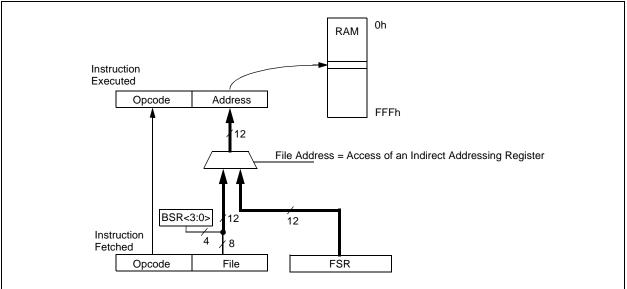

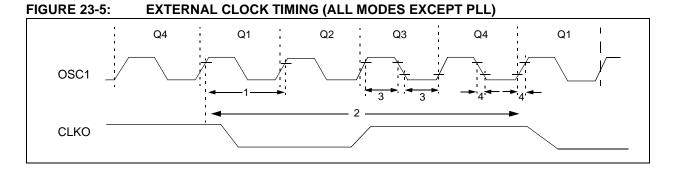

## FIGURE 4-9: INDIRECT ADDRESSING

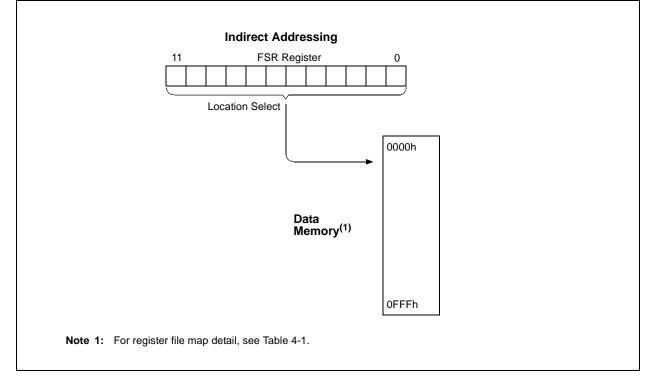

### FIGURE 5-2: TABLE WRITE OPERATION

## 5.2 Control Registers

Several control registers are used in conjunction with the TBLRD and TBLWT instructions. These include the:

- EECON1 register

- EECON2 register

- TABLAT register

- TBLPTR registers

#### 5.2.1 EECON1 AND EECON2 REGISTERS

EECON1 is the control register for memory accesses.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the memory write and erase sequences.

Control bit EEPGD determines if the access will be a program or data EEPROM memory access. When clear, any subsequent operations will operate on the data EEPROM memory. When set, any subsequent operations will operate on the program memory.

Control bit CFGS determines if the access will be to the configuration registers or to program memory/data EEPROM memory. When set, subsequent operations will operate on configuration registers, regardless of EEPGD (see Section 20.0, "Special Features of the CPU"). When clear, memory selection access is determined by EEPGD.

The FREE bit, when set, will allow a program memory erase operation. When the FREE bit is set, the erase operation is initiated on the next WR command. When FREE is clear, only writes are enabled.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a MCLR Reset, or a WDT Time-out Reset, during normal operation. In these situations, the user can check the WRERR bit and rewrite the location. It is necessary to reload the data and address registers (EEDATA and EEADR), due to RESET values of zero.

Control bit WR initiates write operations. This bit cannot be cleared, only set, in software. It is cleared in hardware at the completion of the write operation. The inability to clear the WR bit in software prevents the accidental or premature termination of a write operation.

**Note:** Interrupt flag bit, EEIF in the PIR2 register, is set when the write is complete. It must be cleared in software.

## 6.0 DATA EEPROM MEMORY

The Data EEPROM is readable and writable during normal operation over the entire VDD range. The data memory is not directly mapped in the register file space. Instead, it is indirectly addressed through the Special Function Registers (SFR).

There are four SFRs used to read and write the program and data EEPROM memory. These registers are:

- EECON1

- EECON2

- EEDATA

- EEADR

The EEPROM data memory allows byte read and write. When interfacing to the data memory block, EEDATA holds the 8-bit data for read/write and EEADR holds the address of the EEPROM location being accessed. These devices have 256 bytes of data EEPROM with an address range from 0h to FFh.

The EEPROM data memory is rated for high erase/ write cycles. A byte write automatically erases the location and writes the new data (erase-before-write). The write time is controlled by an on-chip timer. The write time will vary with voltage and temperature, as well as from chip to chip. Please refer to parameter D122 (Electrical Characteristics, Section 23.0) for exact limits.

## 6.1 EEADR

The address register can address up to a maximum of 256 bytes of data EEPROM.

## 6.2 EECON1 and EECON2 Registers

EECON1 is the control register for EEPROM memory accesses.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the EEPROM write sequence.

Control bits RD and WR initiate read and write operations, respectively. These bits cannot be cleared, only set, in software. They are cleared in hardware at the completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental or premature termination of a write operation.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a  $\overline{\text{MCLR}}$  Reset, or a WDT Time-out Reset during normal operation. In these situations, the user can check the WRERR bit and rewrite the location. It is necessary to reload the data and address registers (EEDATA and EEADR), due to the RESET condition forcing the contents of the registers to zero.

Note: Interrupt flag bit, EEIF in the PIR2 register, is set when write is complete. It must be cleared in software.

| Name                   | Bit# | Buffer                | Function                                                                                                                     |

|------------------------|------|-----------------------|------------------------------------------------------------------------------------------------------------------------------|

| RB0/INT0               | bit0 | TTL/ST(1)             | Input/output pin or external interrupt input0.<br>Internal software programmable weak pull-up.                               |

| RB1/INT1               | bit1 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input1.<br>Internal software programmable weak pull-up.                               |

| RB2/INT2               | bit2 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input2.<br>Internal software programmable weak pull-up.                               |

| RB3                    | bit3 | TTL                   | Input/output pin.<br>Internal software programmable weak pull-up.                                                            |

| RB4                    | bit4 | TTL                   | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up.                                 |

| RB5/PGM <sup>(4)</sup> | bit5 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up.<br>Low voltage ICSP enable pin. |

| RB6/PGC                | bit6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up.<br>Serial programming clock.    |

| RB7/PGD                | bit7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up.<br>Serial programming data.     |

#### TABLE 9-3: PORTB FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

**Note 1:** This buffer is a Schmitt Trigger input when configured as the external interrupt.

**2:** This buffer is a Schmitt Trigger input when used in Serial Programming mode.

**3:** A device configuration bit selects which I/O pin the CCP2 pin is multiplexed on.

4: Low Voltage ICSP Programming (LVP) is enabled by default, which disables the RB5 I/O function. LVP must be disabled to enable RB5 as an I/O pin and allow maximum compatibility to the other 28-pin and 40-pin mid-range devices.

| TABLE 9-4: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTB |

|------------|--------------------------------------------|

|------------|--------------------------------------------|

| Name    | Bit 7        | Bit 6         | Bit 5      | Bit 4   | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>All Other<br>RESETS |

|---------|--------------|---------------|------------|---------|--------|--------|--------|--------|----------------------|---------------------------------|

| PORTB   | RB7          | RB6           | RB5        | RB4     | RB3    | RB2    | RB1    | RB0    | xxxx xxxx            | uuuu uuuu                       |

| LATB    | LATB Data    | a Output Re   | gister     |         |        |        |        |        | xxxx xxxx            | uuuu uuuu                       |

| TRISB   | PORTB D      | ata Directio  | n Register |         |        |        |        |        | 1111 1111            | 1111 1111                       |

| INTCON  | GIE/<br>GIEH | PEIE/<br>GIEL | TMR0IE     | INTOIE  | RBIE   | TMR0IF | INTOIF | RBIF   | 0000 000x            | 0000 000u                       |

| INTCON2 | RBPU         | INTEDG0       | INTEDG1    | INTEDG2 | _      | TMR0IP | _      | RBIP   | 1111 -1-1            | 1111 -1-1                       |

| INTCON3 | INT2IP       | INT1IP        | —          | INT2IE  | INT1IE | _      | INT2IF | INT1IF | 11-0 0-00            | 11-0 0-00                       |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

#### TABLE 9-7:PORTD FUNCTIONS

| Name     | Bit# | Buffer Type           | Function                                           |

|----------|------|-----------------------|----------------------------------------------------|

| RD0/PSP0 | bit0 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit0. |

| RD1/PSP1 | bit1 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit1. |

| RD2/PSP2 | bit2 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit2. |

| RD3/PSP3 | bit3 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit3. |

| RD4/PSP4 | bit4 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit4. |

| RD5/PSP5 | bit5 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit5. |

| RD6/PSP6 | bit6 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit6. |

| RD7/PSP7 | bit7 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit7. |

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

### TABLE 9-8: SUMMARY OF REGISTERS ASSOCIATED WITH PORTD

| Name  | Bit 7    | Bit 6       | Bit 5      | Bit 4   | Bit 3 | Bit 2   | Bit 1       | Bit 0   | Value on<br>POR, BOR | Value on<br>All Other<br>RESETS |

|-------|----------|-------------|------------|---------|-------|---------|-------------|---------|----------------------|---------------------------------|

| PORTD | RD7      | RD6         | RD5        | RD4     | RD3   | RD2     | RD1         | RD0     | xxxx xxxx            | uuuu uuuu                       |

| LATD  | LATD Dat | a Output R  | egister    |         |       |         |             |         | xxxx xxxx            | uuuu uuuu                       |

| TRISD | PORTD D  | ata Directi | on Registe | er      |       |         |             |         | 1111 1111            | 1111 1111                       |

| TRISE | IBF      | OBF         | IBOV       | PSPMODE |       | PORTE D | ata Directi | on bits | 0000 -111            | 0000 -111                       |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTD.

NOTES:

### **REGISTER 16-4:** SSPCON1: MSSP CONTROL REGISTER 1 (I<sup>2</sup>C MODE)

| WCOL SSPOV SSPEN CKP SSPM3 SSPM2 SSPM1           | SSPM0 |             | 005140 | 000140 |       | 000511 |       |       |  |

|--------------------------------------------------|-------|-------------|--------|--------|-------|--------|-------|-------|--|

| R/VV-U R/VV-U R/VV-U R/VV-U R/VV-U R/VV-U R/VV-U | R/W-0 | R/W-0 R/W-0 | R/W-0  | R/W-0  | R/W-0 | R/W-0  | R/W-0 | R/W-0 |  |

- bit 7 WCOL: Write Collision Detect bit

- In Master Transmit mode:

- 1 = A write to the SSPBUF register was attempted while the I<sup>2</sup>C conditions were not valid for a transmission to be started (must be cleared in software)

- 0 = No collision

- In Slave Transmit mode:

- 1 = The SSPBUF register is written while it is still transmitting the previous word (must be cleared in software)

- $0 = No \ collision$

- In Receive mode (Master or Slave modes):

This is a "don't care" bit

#### bit 6 SSPOV: Receive Overflow Indicator bit

In Receive mode:

- 1 = A byte is received while the SSPBUF register is still holding the previous byte (must be cleared in software)

- 0 = No overflow

In Transmit mode:

This is a "don't care" bit in Transmit mode

#### bit 5 SSPEN: Synchronous Serial Port Enable bit

- 1 = Enables the serial port and configures the SDA and SCL pins as the serial port pins

- 0 = Disables serial port and configures these pins as I/O port pins

Note: When enabled, the SDA and SCL pins must be properly configured as input or output.

- bit 4 **CKP:** SCK Release Control bit

- In Slave mode:

- 1 = Release clock

- 0 = Holds clock low (clock stretch), used to ensure data setup time

- In Master mode:

Unused in this mode

- bit 3-0 SSPM3:SSPM0: Synchronous Serial Port Mode Select bits

- 1111 =  $I^2C$  Slave mode, 10-bit address with START and STOP bit interrupts enabled

- $1110 = I^2C$  Slave mode, 7-bit address with START and STOP bit interrupts enabled

- $1011 = I^2C$  Firmware Controlled Master mode (Slave IDLE)

- $1000 = I^2C$  Master mode, clock = FOSC / (4 \* (SSPADD+1))

- 0111 =  $I^2C$  Slave mode, 10-bit address

- $0110 = I^2C$  Slave mode, 7-bit address

- **Note:** Bit combinations not specifically listed here are either reserved, or implemented in SPI mode only.

| Legend:            |                  |                                        |  |

|--------------------|------------------|----------------------------------------|--|

| R = Readable bit   | W = Writable bit | U = Unimplemented bit, read as '0'     |  |

| - n = Value at POR | '1' = Bit is set | 0' = Bit is cleared x = Bit is unknown |  |

#### 19.2.1 REFERENCE VOLTAGE SET POINT

The Internal Reference Voltage of the LVD module may be used by other internal circuitry (the Programmable Brown-out Reset). If these circuits are disabled (lower current consumption), the reference voltage circuit requires a time to become stable before a low voltage condition can be reliably detected. This time is invariant of system clock speed. This start-up time is specified in electrical specification parameter 36. The low voltage interrupt flag will not be enabled until a stable reference voltage is reached. Refer to the waveform in Figure 19-4.

#### 19.2.2 CURRENT CONSUMPTION

When the module is enabled, the LVD comparator and voltage divider are enabled and will consume static current. The voltage divider can be tapped from multiple places in the resistor array. Total current consumption, when enabled, is specified in electrical specification parameter #D022B.

### 19.3 Operation During SLEEP

When enabled, the LVD circuitry continues to operate during SLEEP. If the device voltage crosses the trip point, the LVDIF bit will be set and the device will wakeup from SLEEP. Device execution will continue from the interrupt vector address if interrupts have been globally enabled.

### 19.4 Effects of a RESET

A device RESET forces all registers to their RESET state. This forces the LVD module to be turned off.

NOTES:

| File    | Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Default/<br>Unprogrammed<br>Value |

|---------|----------|-------|-------|-------|-------|--------|--------|--------|--------|-----------------------------------|

| 300001h | CONFIG1H | _     | _     | (1)   |       | —      | FOSC2  | FOSC1  | FOSC0  | 1010                              |

| 300002h | CONFIG2L | _     | _     | _     | _     | BORV1  | BORV0  | BOREN  | PWRTEN | 1111                              |

| 300003h | CONFIG2H | _     | _     | _     | _     | WDTPS2 | WDTPS1 | WDTPS0 | WDTEN  | 1111                              |

| 300005h | CONFIG3H | _     | —     | _     | _     | —      | —      | _      | _(1)   | 1                                 |

| 300006h | CONFIG4L | DEBUG | _     |       |       | —      | LVP    |        | STVREN | 11-1                              |

| 300008h | CONFIG5L | _     | _     | —     | -     | _(1)   | CP2    | CP1    | CP0    | 1111                              |

| 300009h | CONFIG5H | CPD   | CPB   | —     | -     | —      | —      | -      | —      | 11                                |

| 30000Ah | CONFIG6L | _     | _     | _     |       | _(1)   | WRT2   | WRT1   | WRT0   | 1111                              |

| 30000Bh | CONFIG6H | WRTD  | WRTB  | WRTC  | -     | —      | —      | -      | —      | 111                               |

| 30000Ch | CONFIG7L | _     | _     | —     | -     | _(1)   | EBTR2  | EBTR1  | EBTR0  | 1111                              |

| 30000Dh | CONFIG7H | _     | EBTRB | _     | _     | —      | _      | _      | —      | -1                                |

| 3FFFFEh | DEVID1   | DEV2  | DEV1  | DEV0  | REV4  | REV3   | REV2   | REV1   | REV0   | (2)                               |

| 3FFFFFh | DEVID2   | DEV10 | DEV9  | DEV8  | DEV7  | DEV6   | DEV5   | DEV4   | DEV3   | 0000 0100                         |

### TABLE 20-1: CONFIGURATION BITS AND DEVICE IDS

Legend: x = unknown, u = unchanged, - = unimplemented. Shaded cells are unimplemented, read as '0'.

Note 1: Unimplemented, but reserved; maintain this bit set.

2: See Register 20-11 for DEVID1 values.

#### REGISTER 20-1: CONFIG1H: CONFIGURATION REGISTER 1 HIGH (BYTE ADDRESS 300001h)

| U-0   | U-0 | U-1 | U-0 | U-0 | R/P-0 | R/P-1 | R/P-0 |

|-------|-----|-----|-----|-----|-------|-------|-------|

| —     | —   | —   | —   | —   | FOSC2 | FOSC1 | FOSC0 |

| bit 7 |     |     |     |     |       |       | bit 0 |

- bit 7-6 Unimplemented: Read as '0'

- bit 5 Unimplemented and reserved: Maintain as '1'

- bit 4-3 Unimplemented: Read as '0'

- bit 2-0 FOSC2:FOSC0: Oscillator Selection bits

- 111 = Reserved

- 110 = HS oscillator with PLL enabled; clock frequency = (4 x Fosc)

- 101 = EC oscillator w/ OSC2 configured as RA6

- 100 = EC oscillator w/ OSC2 configured as divide-by-4 clock output

- 011 = Reserved

- 010 = HS oscillator

- 001 = Reserved

- 000 = Reserved

#### Legend:

| R = Readable bit        | P = Programmable bit | U = Unimplemented bit, read as '0'  |

|-------------------------|----------------------|-------------------------------------|

| - n = Value when device | e is unprogrammed    | u = Unchanged from programmed state |

### 20.3 Power-down Mode (SLEEP)

Power-down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If enabled, the Watchdog Timer will be cleared, but keeps running, the  $\overline{PD}$  bit (RCON<3>) is cleared, the  $\overline{TO}$  (RCON<4>) bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, low or hi-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD or VSS, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D and disable external clocks. Pull all I/O pins that are hi-impedance inputs, high or low externally, to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC).

#### 20.3.1 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. External RESET input on MCLR pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change or a Peripheral Interrupt.

The following peripheral interrupts can wake the device from SLEEP:

- 1. PSP read or write.

- 2. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 3. TMR3 interrupt. Timer3 must be operating as an asynchronous counter.

- 4. CCP Capture mode interrupt.

- 5. Special event trigger (Timer1 in Asynchronous mode using an external clock).

- 6. MSSP (START/STOP) bit detect interrupt.

- MSSP transmit or receive in Slave mode (SPI/I<sup>2</sup>C).

- 8. USART RX or TX (Synchronous Slave mode).

- 9. A/D conversion (when A/D clock source is RC).

- 10. EEPROM write operation complete.

- 11. LVD interrupt.

Other peripherals cannot generate interrupts, since during SLEEP, no on-chip clocks are present.

External MCLR Reset will cause a device RESET. All other events are considered a continuation of program execution and will cause a "wake-up". The TO and PD bits in the RCON register can be used to determine the cause of the device RESET. The PD bit, which is set on power-up, is cleared when SLEEP is invoked. The TO bit is cleared, if a WDT time-out occurred (and caused wake-up).

When the SLEEP instruction is being executed, the next instruction (PC + 2) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

#### 20.3.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If an interrupt condition (interrupt flag bit and interrupt enable bits are set) occurs before the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt condition occurs during or after the execution of a SLEEP instruction, the device will immediately wake-up from SLEEP. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

### 21.1 Instruction Set

| ADD              | DLW                                                            | ADD liter             | al to W                                                                                   |   |    |          |  |  |  |

|------------------|----------------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------|---|----|----------|--|--|--|

| Synt             | ax:                                                            | [ <i>label</i> ] A    | [label] ADDLW k                                                                           |   |    |          |  |  |  |

| Ope              | rands:                                                         | $0 \le k \le 25$      | $0 \le k \le 255$                                                                         |   |    |          |  |  |  |

| Ope              | ration:                                                        | (W) + k $\rightarrow$ | $(W) + k \to W$                                                                           |   |    |          |  |  |  |

| Status Affected: |                                                                | N, OV, C,             | N, OV, C, DC, Z                                                                           |   |    |          |  |  |  |

| Enco             | oding:                                                         | 0000                  | 1111 kkk                                                                                  |   | k  | kkkk     |  |  |  |

| Des              | cription:                                                      | 8-bit litera          | The contents of W are added to the<br>8-bit literal 'k' and the result is<br>placed in W. |   |    |          |  |  |  |

| Wor              | ds:                                                            | 1                     |                                                                                           |   |    |          |  |  |  |

| Cycl             | es:                                                            | 1                     | 1                                                                                         |   |    |          |  |  |  |

| QC               | ycle Activity:                                                 |                       |                                                                                           |   |    |          |  |  |  |

|                  | Q1                                                             | Q2                    | Q3                                                                                        | 6 |    | Q4       |  |  |  |

|                  | Decode                                                         | Read<br>literal 'k'   | Proce<br>Data                                                                             |   | Wr | ite to W |  |  |  |

|                  | <u>mple</u> :<br>Before Instru<br>W =<br>After Instruct<br>W = | ox10                  | )x15                                                                                      |   |    |          |  |  |  |

| ADDWF             | ADD W t                                                                       | o f                                               |                           |                       |                              |

|-------------------|-------------------------------------------------------------------------------|---------------------------------------------------|---------------------------|-----------------------|------------------------------|

| Syntax:           | [ label ] A                                                                   | DDWF                                              | f [,                      | d [,a                 | ı]                           |

| Operands:         | $0 \le f \le 25$<br>$d \in [0,1]$<br>$a \in [0,1]$                            | 55                                                |                           |                       |                              |

| Operation:        | (W) + (f)                                                                     | $\rightarrow$ dest                                |                           |                       |                              |

| Status Affected:  | N, OV, C                                                                      | , DC, Z                                           |                           |                       |                              |

| Encoding:         | 0010                                                                          | 01da                                              | fff                       | f                     | ffff                         |

| Description:      | Add W to<br>result is s<br>result is s<br>(default).<br>Bank will<br>BSR is u | stored in<br>stored ba<br>If 'a' is 0<br>be seled | W. If<br>ick in<br>), the | 'd' is<br>regi<br>Acc | s 1, the<br>ister 'f'<br>ess |

| Words:            | 1                                                                             |                                                   |                           |                       |                              |

| Cycles:           | 1                                                                             |                                                   |                           |                       |                              |

| Q Cycle Activity: |                                                                               |                                                   |                           |                       |                              |

| Q1                | Q2                                                                            | Q                                                 | 3                         |                       | Q4                           |

| Decode            | Read<br>register 'f'                                                          | Proce<br>Data                                     |                           |                       | /rite to<br>stination        |

| Example:          | ADDWF                                                                         | REG,                                              | 0, 0                      |                       |                              |

| Before Instru     | uction                                                                        |                                                   |                           |                       |                              |

| W<br>REG          | = 0x17<br>= 0xC2                                                              |                                                   |                           |                       |                              |

| After Instruc     | tion                                                                          |                                                   |                           |                       |                              |

| W                 | = 0xD9                                                                        |                                                   |                           |                       |                              |

0xC2

=

REG

## 22.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C17 and MPLAB C18 C Compilers

- MPLINK™ Object Linker/

- MPLIB<sup>™</sup> Object Librarian

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- ICEPIC<sup>™</sup> In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD

- Device Programmers

- PRO MATE<sup>®</sup> II Universal Device Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Development Programmer

- Low Cost Demonstration Boards

- PICDEM<sup>™</sup>1 Demonstration Board

- PICDEM 2 Demonstration Board

- PICDEM 3 Demonstration Board

- PICDEM 17 Demonstration Board

- KEELOQ<sup>®</sup> Demonstration Board

### 22.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> based application that contains:

- · An interface to debugging tools

- simulator

- programmer (sold separately)

- emulator (sold separately)

- in-circuit debugger (sold separately)

- A full-featured editor

- · A project manager

- Customizable toolbar and key mapping

- · A status bar

- On-line help

The MPLAB IDE allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- Debug using:

- source files

- absolute listing file

- machine code

The ability to use MPLAB IDE with multiple debugging tools allows users to easily switch from the cost-effective simulator to a full-featured emulator with minimal retraining.

### 22.2 MPASM Assembler

The MPASM assembler is a full-featured universal macro assembler for all PIC MCUs.

The MPASM assembler has a command line interface and a Windows shell. It can be used as a stand-alone application on a Windows 3.x or greater system, or it can be used through MPLAB IDE. The MPASM assembler generates relocatable object files for the MPLINK object linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, an absolute LST file that contains source lines and generated machine code, and a COD file for debugging.

The MPASM assembler features include:

- Integration into MPLAB IDE projects.

- User-defined macros to streamline assembly code.

- Conditional assembly for multi-purpose source files.

- Directives that allow complete control over the assembly process.

### 22.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI 'C' compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers, respectively. These compilers provide powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compilers provide symbol information that is compatible with the MPLAB IDE memory display.

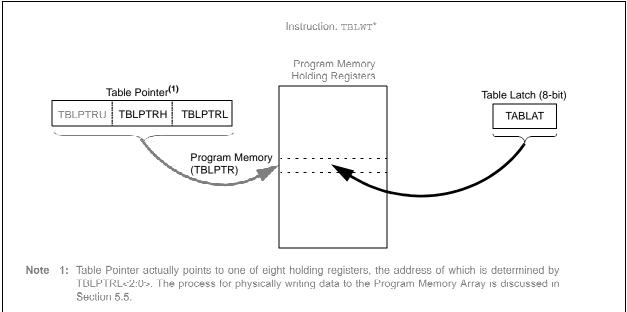

### 23.3.3 TIMING DIAGRAMS AND SPECIFICATIONS

### TABLE 23-4: EXTERNAL CLOCK TIMING REQUIREMENTS

| Param.<br>No. | Symbol        | Characteristic                                | Min | Мах  | Units | Conditions                    |

|---------------|---------------|-----------------------------------------------|-----|------|-------|-------------------------------|

| 1A            | Fosc          | External CLKI Frequency <sup>(1)</sup>        | DC  | 40   | MHz   | EC, ECIO, -40°C to +85°C      |

|               |               | Oscillator Frequency <sup>(1)</sup>           | DC  | 25   | MHz   | EC, ECIO, +85°C to +125°C     |

|               |               |                                               | 4   | 25   | MHz   | HS osc                        |

|               |               |                                               | 4   | 10   | MHz   | HS + PLL osc, -40°C to +85°C  |

|               |               |                                               | 4   | 6.25 | MHz   | HS + PLL osc, +85°C to +125°C |

| 1             | Tosc          | External CLKI Period <sup>(1)</sup>           | 25  | _    | ns    | EC, ECIO, -40°C to +85°C      |

|               |               | Oscillator Period <sup>(1)</sup>              | 40  | _    | ns    | EC, ECIO, +85°C to +125°C     |

|               |               |                                               | 40  | 250  | ns    | HS osc                        |

|               |               |                                               | 100 | 250  | ns    | HS + PLL osc, -40°C to +85°C  |

|               |               |                                               | 160 | 250  | ns    | HS + PLL osc, +85°C to +125°C |

| 2             | Тсү           | Instruction Cycle Time <sup>(1)</sup>         | 100 | _    | ns    | Tcy = 4/Fosc, -40°C to +85°C  |

|               |               |                                               | 160 | —    | ns    | TcY = 4/Fosc, +85°C to +125°C |

| 3             | TosL,<br>TosH | External Clock in (OSC1)<br>High or Low Time  | 10  | —    | ns    | HS osc                        |

| 4             | TosR,<br>TosF | External Clock in (OSC1)<br>Rise or Fall Time | _   | 7.5  | ns    | HS osc                        |

**Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time-base period for all configurations except PLL. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin. When an external clock input is used, the "max." cycle time limit is "DC" (no clock) for all devices.

### TABLE 23-5:PLL CLOCK TIMING SPECIFICATIONS (VDD = 4.2 TO 5.5V)

| Param<br>No. | Sym             | Characteristic                | Min | Тур† | Max | Units | Conditions   |

|--------------|-----------------|-------------------------------|-----|------|-----|-------|--------------|

| —            | Fosc            | Oscillator Frequency Range    | 4   | _    | 10  | MHz   | HS mode only |

| —            | Fsys            | On-Chip VCO System Frequency  | 16  | _    | 40  | MHz   | HS mode only |

| —            | t <sub>rc</sub> | PLL Start-up Time (Lock Time) | _   | _    | 2   | ms    |              |

| —            | $\Delta CLK$    | CLKO Stability (Jitter)       | -2  |      | +2  | %     |              |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

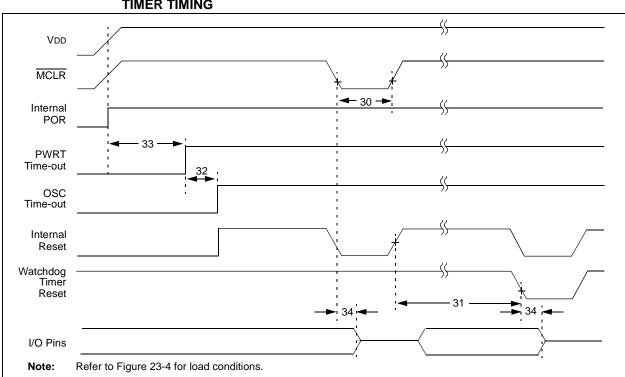

# FIGURE 23-7: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

## FIGURE 23-8: BROWN-OUT RESET TIMING

## TABLE 23-7:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER<br/>AND BROWN-OUT RESET REQUIREMENTS

| Param.<br>No. | Symbol | Characteristic                                           | Min       | Тур | Мах       | Units | Conditions                 |

|---------------|--------|----------------------------------------------------------|-----------|-----|-----------|-------|----------------------------|

| 30            | TmcL   | MCLR Pulse Width (low)                                   | 2         | _   | _         | μS    |                            |

| 31            | Twdt   | Watchdog Timer Time-out Period (No<br>Postscaler)        | 7         | 18  | 33        | ms    |                            |

| 32            | Tost   | Oscillation Start-up Timer Period                        | 1024 Tosc |     | 1024 Tosc |       | Tosc = OSC1 period         |

| 33            | TPWRT  | Power up Timer Period                                    | 28        | 72  | 132       | ms    |                            |

| 34            | TIOZ   | I/O high impedance from MCLR Low or Watchdog Timer Reset | —         | 2   | —         | μS    |                            |

| 35            | TBOR   | Brown-out Reset Pulse Width                              | 200       |     | _         | μS    | $VDD \le BVDD$ (see D005)  |

| 36            | TIVRST | Time for Internal Reference<br>Voltage to become stable  | —         | 20  | 500       | μS    |                            |

| 37            | Tlvd   | Low Voltage Detect Pulse Width                           | 200       |     | —         | μS    | $VDD \leq VLVD$ (see D420) |

| SSPSTAT Register                              |    |

|-----------------------------------------------|----|

| R/W Bit                                       | 39 |

| Status Bits                                   |    |

| Significance and the Initialization Condition |    |

| for RCON Register                             | 25 |

| SUBFWB                                        | 46 |

| SUBLW                                         | 47 |

| SUBWF                                         | 47 |

| SUBWFB                                        | 48 |

| SWAPF                                         | 48 |

## Т

| TABLAT Register                            | 54       |

|--------------------------------------------|----------|

| Table Pointer Operations (table)           | 54       |

| TBLPTR Register                            |          |

| TBLRD                                      |          |

| TBLWT                                      | 250      |

| Time-out Sequence                          | 24       |

| Time-out in Various Sitations              | 25       |

| Timer0                                     |          |

| 16-bit Mode Timer Reads and Writes         |          |

| Associated Registers                       |          |

| Clock Source Edge Select (T0SE Bit)        |          |

| Clock Source Select (TOCS Bit)             |          |

| Operation                                  |          |

| Overflow Interrupt                         |          |

| Prescaler. See Prescaler, Timer0           |          |

| Timer1                                     | 102      |

| 16-bit Read/Write Mode                     |          |

|                                            |          |

| Associated Registers                       |          |

| Operation                                  |          |

| Oscillator                                 |          |

| Overflow Interrupt                         |          |

| TMR1H Register                             |          |

| TMR1L Register                             |          |

| Timer2                                     |          |

| TMR2 to PR2 Match Interrupt                |          |

| Timer3                                     | 109      |

| Associated Registers                       | 111      |

| Operation                                  | 110      |

| Oscillator                                 | 109      |

| Overflow Interrupt                         | 109, 111 |

| TMR3H Register                             |          |

| TMR3L Register                             |          |

| Timing Diagrams                            |          |

| A/D Conversion                             |          |

| Acknowledge Sequence                       |          |

| Asynchronous Reception                     |          |

| Asynchronous Transmission                  | 173      |

| Asynchronous Transmission (Back to Back)   |          |

| Baud Rate Generator with Clock Arbitration |          |

| BRG Reset Due to SDA Arbitration           |          |

| During START Condition                     | 161      |

| Brown-out Reset (BOR)                      |          |

| Bus Collision During a STOP Condition      |          |

| (Case 1)                                   | 160      |

| Bus Collision During a STOP Condition      |          |

|                                            |          |

| (Case 2)                                   |          |

| Bus Collision During Repeated START        |          |

| Condition (Case 1)                         |          |

| Bus Collision During Repeated START        |          |

| Condition (Case 2)                         | 162      |

| Bus Collision During START Condition       |          |

| (SCL = 0)                                  | 161      |

| Bus Collision During Start Condition       |          |

| (SDA Only)                                 |          |

| Bus Collision for Transmit and Acknowledge | 159      |

|                                            |          |

| CLKO and I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 271                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock Synchronization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Clock/Instruction Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Example SPI Master Mode (CKE = 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 276                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Example SPI Master Mode (CKE = 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 277                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Example SPI Slave Mode (CKE = 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Example SPI Slave Mode (CKE = 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 279                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| External Clock (All Modes except PLL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| First START Bit Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| I <sup>2</sup> C Bus Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 280                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| I <sup>2</sup> C Bus START/STOP Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 280                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| I <sup>2</sup> C Master Mode (7 or 10-bit Transmission)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| I <sup>2</sup> C Master Mode (7-bit Reception)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 157                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |