Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                               |

| Number of I/O              | 32                                                                       |

| Program Memory Size        | 12KB (6K x 16)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 640 × 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                              |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4439-i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 1-1: PIC18FXX39 DEVICE FEATURES

| Features                                | PIC18F2439                                                                       | PIC18F2539                                                                       | PIC18F4439                                                                       | PIC18F4539                                                                       |

|-----------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Operating Frequency                     | DC - 40 MHz                                                                      |

| Program Memory (Bytes)                  | 12K                                                                              | 24K                                                                              | 12K                                                                              | 24K                                                                              |

| Program Memory (Instructions)           | 6144                                                                             | 12288                                                                            | 6144                                                                             | 12288                                                                            |

| Data Memory (Bytes)                     | 640                                                                              | 1408                                                                             | 640                                                                              | 1408                                                                             |

| Data EEPROM Memory (Bytes)              | 256                                                                              | 256                                                                              | 256                                                                              | 256                                                                              |

| Interrupt Sources                       | 15                                                                               | 15                                                                               | 16                                                                               | 16                                                                               |

| I/O Ports                               | Ports A, B, C                                                                    | Ports A, B, C                                                                    | Ports A, B, C, D, E                                                              | Ports A, B, C, D, E                                                              |

| Timers                                  | 3                                                                                | 3                                                                                | 3                                                                                | 3                                                                                |

| PWM Modules <sup>(1)</sup>              | 2                                                                                | 2                                                                                | 2                                                                                | 2                                                                                |

| Single Phase Induction<br>Motor Control | Yes                                                                              | Yes                                                                              | Yes                                                                              | Yes                                                                              |

| Serial Communications                   | MSSP,<br>Addressable<br>USART                                                    | MSSP,<br>Addressable<br>USART                                                    | MSSP,<br>Addressable<br>USART                                                    | MSSP,<br>Addressable<br>USART                                                    |

| Parallel Communications                 | —                                                                                | —                                                                                | PSP                                                                              | PSP                                                                              |

| 10-bit Analog-to-Digital Module         | 5 input channels                                                                 | 5 input channels                                                                 | 8 input channels                                                                 | 8 input channels                                                                 |

| RESETS (and Delays)                     | POR, BOR,<br>RESET Instruction,<br>Stack Full,<br>Stack Underflow<br>(PWRT, OST) |

| Programmable Low Voltage<br>Detect      | Yes                                                                              | Yes                                                                              | Yes                                                                              | Yes                                                                              |

| Programmable Brown-out Reset            | Yes                                                                              | Yes                                                                              | Yes                                                                              | Yes                                                                              |

| Instruction Set                         | 75 Instructions                                                                  | 75 Instructions                                                                  | 75 Instructions                                                                  | 75 Instructions                                                                  |

| Packages                                | 28-pin DIP<br>28-pin SOIC                                                        | 28-pin DIP<br>28-pin SOIC                                                        | 40-pin DIP<br>44-pin TQFP<br>44-pin QFN                                          | 40-pin DIP<br>44-pin TQFP<br>44-pin QFN                                          |

**Note 1:** PWM modules are used exclusively in conjunction with the motor control kernel, and are not available for other applications.

### TABLE 1-3:PIC18F4X39 PINOUT I/O DESCRIPTIONS

| Pin Nama                | Pin Number |          |           | Pin Buffer |               | Description                                                                                                                       |  |  |  |

|-------------------------|------------|----------|-----------|------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name                | DIP        | QFN      | TQFP      | Туре       | Туре          | Description                                                                                                                       |  |  |  |

| MCLR/VPP<br>MCLR        | 1          | 18       | 18        | I          | ST            | Master Clear (input) or high voltage ICSP<br>programming enable pin.<br>Master Clear (Reset) input. This pin is an active         |  |  |  |

| Vpp                     |            |          |           | Ι          | ST            | low RESET to the device.<br>High voltage ICSP programming enable pin.                                                             |  |  |  |

| OSC1/CLKI<br>OSC1       | 13         | 32       | 30        | Ι          | CMOS          | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source input.                           |  |  |  |

| CLKI                    |            |          |           | Ι          | CMOS          | External clock source input. Always associated with pin function OSC1. (See related OSC1/CLKI, OSC2/CLKO pins.)                   |  |  |  |

| OSC2/CLKO/RA6<br>OSC2   | 14         | 33       | 31        | 0          | _             | Oscillator crystal or clock output.<br>Oscillator crystal output. Connects to crystal<br>or resonator in Crystal Oscillator mode. |  |  |  |

| CLKO                    |            |          |           | 0          | —             | In EC mode, OSC2 pin outputs CLKO,<br>which has 1/4 the frequency of OSC1 and<br>denotes the instruction cycle rate.              |  |  |  |

| RA6                     |            |          |           | I/O        | TTL           | General purpose I/O pin.                                                                                                          |  |  |  |

|                         |            |          |           |            |               | PORTA is a bi-directional I/O port.                                                                                               |  |  |  |

| RA0/AN0                 | 2          | 19       | 19        |            |               |                                                                                                                                   |  |  |  |

| RA0                     |            |          |           | I/O        | TTL           | Digital I/O.                                                                                                                      |  |  |  |

| AN0                     |            |          |           | I          | Analog        | Analog input 0.                                                                                                                   |  |  |  |

| RA1/AN1                 | 3          | 20       | 20        |            |               |                                                                                                                                   |  |  |  |

| RA1<br>AN1              |            |          |           | I/O<br>I   | TTL<br>Analog | Digital I/O.<br>Analog input 1.                                                                                                   |  |  |  |

| RA2/AN2/VREF-           | 4          | 21       | 21        |            | Analog        |                                                                                                                                   |  |  |  |

| RAZ/ANZ/VREF-           | 4          | 21       | 21        | I/O        | TTL           | Digital I/O.                                                                                                                      |  |  |  |

| AN2                     |            |          |           | 1          | Analog        | Analog input 2.                                                                                                                   |  |  |  |

| VREF-                   |            |          |           | Ι          | Analog        | A/D Reference Voltage (Low) input.                                                                                                |  |  |  |

| RA3/AN3/VREF+           | 5          | 22       | 22        |            |               |                                                                                                                                   |  |  |  |

| RA3                     |            |          |           | I/O        | TTL           | Digital I/O.                                                                                                                      |  |  |  |

| AN3                     |            |          |           | 1          | Analog        | Analog input 3.                                                                                                                   |  |  |  |

| VREF+                   |            |          |           | I          | Analog        | A/D Reference Voltage (High) input.                                                                                               |  |  |  |

| RA4/T0CKI               | 6          | 23       | 23        | 1/0        |               | Digital I/O. Open drain when configured as output                                                                                 |  |  |  |

| RA4<br>T0CKI            |            |          |           | 1/O<br>1   | ST/OD<br>ST   | Digital I/O. Open drain when configured as output.<br>Timer0 external clock input.                                                |  |  |  |

| RA5/AN4/SS/LVDIN        | 7          | 24       | 24        | 1          | 01            | Timero externar clock input.                                                                                                      |  |  |  |

| RA5/AN4/S5/LVDIN<br>RA5 | 1          | 24       | 24        | I/O        | TTL           | Digital I/O.                                                                                                                      |  |  |  |

| AN4                     |            |          |           | 1          | Analog        | Analog input 4.                                                                                                                   |  |  |  |

| SS                      |            |          |           | Ι          | ST            | SPI Slave Select input.                                                                                                           |  |  |  |

| LVDIN                   |            |          |           | Ι          | Analog        | Low Voltage Detect input.                                                                                                         |  |  |  |

| RA6                     |            |          |           |            |               | (See the OSC2/CLKO/RA6 pin.)                                                                                                      |  |  |  |

| Legend: TTL = TTL       |            |          |           |            |               | CMOS = CMOS compatible input or output                                                                                            |  |  |  |

| ST = Schn               | •          | ger inpu | ut with C | MOS le     |               | = Input                                                                                                                           |  |  |  |

| O = Outp                |            | / D      | iada ta \ | ()         |               | P = Power                                                                                                                         |  |  |  |

OD = Open Drain (no P diode to VDD)

## 4.0 MEMORY ORGANIZATION

There are three memory blocks in Enhanced MCU devices. These memory blocks are:

- Program Memory

- Data RAM

- Data EEPROM

Data and program memory use separate busses, which allows for concurrent access of these blocks.

Additional detailed information for FLASH program memory and Data EEPROM is provided in Section 5.0 and Section 6.0, respectively.

#### 4.1 Program Memory Organization

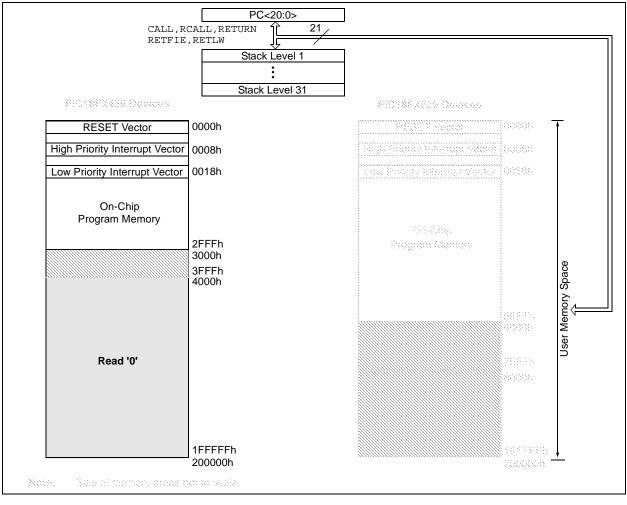

A 21-bit program counter is capable of addressing the 2-Mbyte program memory space. Accessing a location between the physically implemented memory and the top of the 2-MByte range will cause a read of all '0's (a NOP instruction).

The PIC18F2539 and PIC18F4539 each have a total of 24 Kbytes, or 12K of single word instructions of FLASH memory, from addresses 0000h to 5FFFh. The next 8 Kbytes beyond this space (from 6000h to 7FFFh) are reserved for the Motor Control kernel; accessing locations in this range will return random information.

The PIC18F2439 and PIC18F4439 each have 12 Kbytes, or 6K of single word instructions of FLASH memory, from addresses 0000h to 2FFFh. The next 4 Kbytes of this space (from 3000h to 3FFFh) are reserved for the Motor Control kernel; accessing locations in this range will return random information.

The RESET vector address for all devices is at 0000h, and the interrupt vector addresses are at 0008h and 0018h.

The memory maps for the PIC18FX439 and PIC18FX539 devices are shown in Figure 4-1.

Note: The ProMPT Motor Control kernel is identical for all PIC18FXX39 devices, regardless of the difference in reserved block size between PIC18FX439 and PIC18FX539 devices

#### FIGURE 4-1: PROGRAM MEMORY MAP AND STACK FOR PIC18FXX39 DEVICES

### 4.9 Data Memory Organization

The data memory is implemented as static RAM. Each register in the data memory has a 12-bit address, allowing up to 4096 bytes of data memory. The data memory map is divided into 16 banks that contain 256 bytes each. The lower 4 bits of the Bank Select Register (BSR<3:0>) select which bank will be accessed. The upper 4 bits for the BSR are not implemented.

The data memory contains Special Function Registers (SFRs) and General Purpose Registers (GPRs). The SFRs are used for control and status of the controller and peripheral functions, while GPRs are used for data storage and scratch pad operations in the user's application. The SFRs start at the last location of Bank 15 (FFFh) and extend downwards. Any remaining space beyond the SFRs in the Bank may be implemented as GPRs. GPRs start at the first location of Bank 0 and grow upwards. Any read of an unimplemented location will read as '0's.

The organization of the data memory space for these devices is shown in Figure 4-5 and Figure 4-6. PIC18FX439 devices have 640 bytes of data RAM, extending from Bank 0 to Bank 2 (000h through 27Fh). The block of 128 bytes above this to the top of the bank (280h to 2FFh) is used as data memory for the Motor Control kernel, and is not available to the user. Reading these locations will return random information that reflects the kernel's "scratch" data. Modifying the data in these locations may disrupt the operation of the ProMPT kernel.

PIC18FX539 devices have 1408 bytes of data RAM, extending from Bank 0 to Bank 5 (000h through 57Fh). As with the PIC18FX439 devices, the block of 128 bytes above this to the end of the bank (580h to 5FFh) is used by the Motor Control kernel.

The entire data memory may be accessed directly or indirectly. Direct addressing may require the use of the BSR register. Indirect addressing requires the use of a File Select Register (FSRn) and a corresponding Indirect File Operand (INDFn). Each FSR holds a 12-bit address value that can be used to access any location in the Data Memory map without banking.

The instruction set and architecture allow operations across all banks. This may be accomplished by indirect addressing, or by the use of the MOVFF instruction. The MOVFF instruction is a two-word/two-cycle instruction that moves a value from one register to another.

To ensure that commonly used registers (SFRs and select GPRs) can be accessed in a single cycle, regardless of the current BSR values, an Access Bank is implemented. A segment of Bank 0 and a segment of Bank 15 comprise the Access RAM. Section 4.10 provides a detailed description of the Access RAM.

#### 4.9.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly or indirectly. Indirect addressing operates using a File Select Register and corresponding Indirect File Operand. The operation of indirect addressing is shown in Section 4.12.

Enhanced MCU devices may have banked memory in the GPR area. GPRs are not initialized by a Power-on Reset and are unchanged on all other RESETS.

Data RAM is available for use as GPR registers by all instructions. The top half of Bank 15 (F80h to FFFh) contains SFRs. All other banks of data memory contain GPR registers, starting with Bank 0.

#### 4.9.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 4-1 and Table 4-2.

The SFRs can be classified into two sets; those associated with the "core" function and those related to the peripheral functions. Those registers related to the "core" are described in this section, while those related to the operation of the peripheral features are described in the section of that peripheral feature.

The SFRs are typically distributed among the peripherals whose functions they control. The unused SFR locations will be unimplemented and read as '0's. See Table 4-1 for addresses for the SFRs.

| Note: | In this chapter and throughout this docu-<br>ment, certain SFR names and individual |

|-------|-------------------------------------------------------------------------------------|

|       | bits are marked with an asterisk (*). This                                          |

|       | denotes registers that are not implemented                                          |

|       |                                                                                     |

|       | in PIC18FXX39 devices, but whose names                                              |

|       | are retained to maintain compatibility with                                         |

|       | PIC18FXX2 devices. The designated bits                                              |

|       | within these registers are reserved and                                             |

|       | may be used by certain modules or the                                               |

|       | Motor Control kernel. Users should not                                              |

|       | write to these registers or alter these bit                                         |

|       | values. Failure to do this may result in                                            |

|       | erratic microcontroller operation.                                                  |

### 5.4 Erasing FLASH Program memory

The minimum erase block is 32 words or 64 bytes. Only through the use of an external programmer, or through ICSP control can larger blocks of program memory be bulk erased. Word erase in the FLASH array is not supported.

When initiating an erase sequence from the microcontroller itself, a block of 64 bytes of program memory is erased. The Most Significant 16 bits of the TBLPTR<21:6> point to the block being erased; TBLPTR<5:0> are ignored.

The EECON1 register commands the erase operation. The EEPGD bit must be set to point to the FLASH program memory. The WREN bit must be set to enable write operations. The FREE bit is set to select an erase operation.

For protection, the write initiate sequence for EECON2 must be used.

A long write is necessary for erasing the internal FLASH. Instruction execution is halted while in a long write cycle. The long write will be terminated by the internal programming timer.

#### 5.4.1 FLASH PROGRAM MEMORY ERASE SEQUENCE

The sequence of events for erasing a block of internal program memory location is:

- 1. Load table pointer with address of row being erased.

- Set EEPGD bit to point to program memory, clear CFGS bit to access program memory, set WREN bit to enable writes, and set FREE bit to enable the erase.

- 3. Disable interrupts.

- 4. Write 55h to EECON2.

- 5. Write AAh to EECON2.

- 6. Set the WR bit. This will begin the row erase cycle.

- 7. The CPU will stall for duration of the erase (about 2 ms using internal timer).

- 8. Re-enable interrupts.

#### EXAMPLE 5-2: ERASING A FLASH PROGRAM MEMORY ROW

|           | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>MOVLW<br>MOVWF | CODE_ADDR_UPPER<br>TBLPTRU<br>CODE_ADDR_HIGH<br>TBLPTRH<br>CODE_ADDR_LOW<br>TBLPTRL | ; load TBLPTR with the base<br>; address of the memory block |

|-----------|----------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------|

| ERASE_ROW | 110 V WF                                           |                                                                                     |                                                              |

| _         | BSF                                                | EECON1, EEPGD                                                                       | ; point to FLASH program memory                              |

|           | BCF                                                | EECON1,CFGS                                                                         | ; access FLASH program memory                                |

|           | BSF                                                | EECON1,WREN                                                                         | ; enable write to memory                                     |

|           | BSF                                                | EECON1, FREE                                                                        | ; enable Row Erase operation                                 |

|           | BCF                                                | INTCON,GIE                                                                          | ; disable interrupts                                         |

|           | MOVLW                                              | 55h                                                                                 |                                                              |

| Required  | MOVWF                                              | EECON2                                                                              | ; write 55h                                                  |

| Sequence  | MOVLW                                              | AAh                                                                                 |                                                              |

|           | MOVWF                                              | EECON2                                                                              | ; write AAh                                                  |

|           | BSF                                                | EECON1,WR                                                                           | ; start erase (CPU stall)                                    |

|           | BSF                                                | INTCON, GIE                                                                         | ; re-enable interrupts                                       |

## REGISTER 6-1: EECON1 REGISTER (ADDRESS FA6h)

|       |              |                                 | `             | ,            |               |              |                |              |

|-------|--------------|---------------------------------|---------------|--------------|---------------|--------------|----------------|--------------|

|       | R/W-x        | R/W-x                           | U-0           | R/W-0        | R/W-x         | R/W-0        | R/S-0          | R/S-0        |

|       | EEPGD        | CFGS                            | —             | FREE         | WRERR         | WREN         | WR             | RD           |

|       | bit 7        |                                 |               |              |               |              |                | bit 0        |

|       |              |                                 |               |              |               |              |                |              |

| bit 7 |              | -                               |               |              | lemory Selec  | ct bit       |                |              |

|       |              | s FLASH pro<br>s data EEPR      |               |              |               |              |                |              |

| bit 6 |              |                                 |               |              | tion Select b | it           |                |              |

| bit 0 |              | s configuration                 |               | -            |               |              |                |              |

|       |              | S FLASH pro                     |               |              |               |              |                |              |

| bit 5 | Unimplem     | ented: Rea                      | d as '0'      |              |               |              |                |              |

| bit 4 | FREE: FL/    | ASH Row Er                      | ase Enable    | bit          |               |              |                |              |

|       |              |                                 |               |              | by TBLPTR     | on the nex   | t WR comm      | and          |

|       |              | d by comple<br>n write only     | tion of erase | e operation) |               |              |                |              |

| bit 3 |              | LASH Prog                       | ram/Data El   | = Error Elao | bit           |              |                |              |

| Sit 0 |              | operation is                    |               | -            |               |              |                |              |

|       | (any M       | CLR or any                      | WDT Reset     |              | timed progra  | mming in n   | ormal opera    | tion)        |

|       |              | ite operatior                   | •             |              |               |              |                |              |

|       |              | hen a WREF<br>the error co      | •             | he EEPGD (   | or FREE bits  | are not clea | red. This all  | ows tracing  |

| bit 2 |              | ASH Progra                      | m/Data EE     | Write Enabl  | o hit         |              |                |              |

| DIT Z |              | write cycles                    |               |              | e bit         |              |                |              |

|       |              | write to the                    |               |              |               |              |                |              |

| bit 1 | WR: Write    | Control bit                     |               |              |               |              |                |              |

|       |              |                                 |               |              | or a program  |              |                |              |

|       |              | peration is s<br>can only be    |               |              | leared by ha  | rdware once  | e write is coi | mplete. The  |

|       |              | can only be<br>sycle to the E   |               |              | ware.)        |              |                |              |

| bit 0 | RD: Read     | -                               |               | ·            |               |              |                |              |

|       | 1 = Initiate | s an EEPRC                      | OM read       |              |               |              |                |              |

|       |              | •                               |               |              | rdware. The   | RD bit can c | only be set (i | not cleared) |

|       |              | vare. RD bit<br>lot initiate ar |               |              | PGD = 1.)     |              |                |              |

|       | 0 - 2000 1   | iet millato ul                  |               |              |               |              |                |              |

|       | Legend:      |                                 |               |              |               |              |                |              |

|       | R = Reada    | ble bit                         | W = W         | /ritable bit | U = Unim      | nlemented    | hit read as    | '0'          |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'                    |      |

|-----------------------------------------------------------------------------------------|------|

|                                                                                         |      |

| - n = Value at POR $(1)^{2}$ = Bit is set $(0)^{2}$ = Bit is cleared x = Bit is unknown | nown |

## 9.0 I/O PORTS

Depending on the device selected, there are either three or five ports available. Some pins of the I/O ports are multiplexed with an alternate function from the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Each port has three registers for its operation. These registers are:

- TRIS register (data direction register)

- PORT register (reads the levels on the pins of the device)

- LAT register (output latch)

The data latch (LAT register) is useful for read-modifywrite operations on the value that the I/O pins are driving.

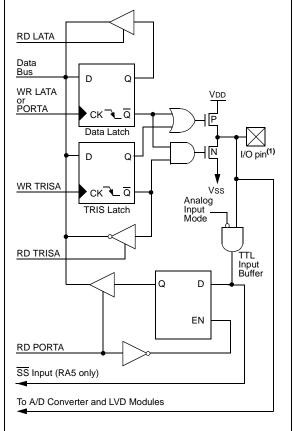

### 9.1 PORTA, TRISA and LATA Registers

PORTA is a 7-bit wide, bi-directional port. The corresponding Data Direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a High Impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch.

The Data Latch register (LATA) is also memory mapped. Read-modify-write operations on the LATA register reads and writes the latched output value for PORTA.

The RA4 pin is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers.

The other PORTA pins are multiplexed with analog inputs and the analog VREF+ and VREF- inputs. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

#### EXAMPLE 9-1: INITIALIZING PORTA

| C | CLRF PORTA   | ; Initialize PORTA by<br>; clearing output |

|---|--------------|--------------------------------------------|

|   |              | , 5 1                                      |

|   |              | ; data latches                             |

| C | CLRF LATA    | ; Alternate method                         |

|   |              | ; to clear output                          |

|   |              | ; data latches                             |

| Ν | IOVLW 0x07   | ; Configure A/D                            |

| Ν | NOVWF ADCON1 | ; for digital inputs                       |

| Ν | NOVLW 0xCF   | ; Value used to                            |

|   |              | ; initialize data                          |

|   |              | ; direction                                |

| Ν | NOVWF TRISA  | ; Set RA<3:0> as inputs                    |

|   |              | ; RA<5:4> as outputs                       |

|   |              |                                            |

#### FIGURE 9-1:

#### BLOCK DIAGRAM OF RA3:RA0 AND RA5 PINS

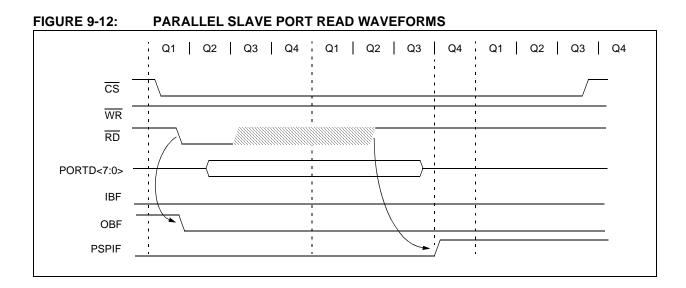

TABLE 9-11: REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

| Name   | Bit 7        | Bit 6         | Bit 5        | Bit 4          | Bit 3 | Bit 2     | Bit 1         | Bit 0  | Value on<br>POR, BOR | Value on<br>All Other<br>RESETS |

|--------|--------------|---------------|--------------|----------------|-------|-----------|---------------|--------|----------------------|---------------------------------|

| PORTD  | Port Data    | Latch whe     | n written; F | Port pins when | read  |           |               |        | xxxx xxxx            | uuuu uuuu                       |

| LATD   | LATD Data    | a Output b    | its          |                |       |           |               |        | xxxx xxxx            | uuuu uuuu                       |

| TRISD  | PORTD D      | ata Directi   | on bits      |                |       |           |               |        | 1111 1111            | 1111 1111                       |

| PORTE  | —            | _             | —            | —              | _     | RE2       | RE1           | RE0    | 000                  | 000                             |

| LATE   | —            | _             | _            | _              | _     | LATE Data | a Output bits | 3      | xxx                  | uuu                             |

| TRISE  | IBF          | OBF           | IBOV         | PSPMODE        | _     | PORTE D   | ata Directio  | n bits | 0000 -111            | 0000 -111                       |

| INTCON | GIE/<br>GIEH | PEIE/<br>GIEL | TMR0IF       | INTOIE         | RBIE  | TMR0IF    | INTOIF        | RBIF   | 0000 000x            | 0000 000u                       |

| PIR1   | PSPIF        | ADIF          | RCIF         | TXIF           | SSPIF | _         | TMR2IF        | TMR1IF | 0000 0000            | 0000 0000                       |

| PIE1   | PSPIE        | ADIE          | RCIE         | TXIE           | SSPIE |           | TMR2IE        | TMR1IE | 0000 0000            | 0000 0000                       |

| IPR1   | PSPIP        | ADIP          | RCIP         | TXIP           | SSPIP | _         | TMR2IP        | TMR1IP | 0000 0000            | 0000 0000                       |

| ADCON1 | ADFM         | ADCS2         | —            | —              | PCFG3 | PCFG2     | PCFG1         | PCFG0  | 00 0000              | 00 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Parallel Slave Port.

## 11.0 TIMER1 MODULE

The Timer1 module timer/counter has the following features:

- 16-bit timer/counter (two 8-bit registers, TMR1H and TMR1L)

- Readable and writable (both registers)

- Internal or external clock select

- Interrupt-on-overflow from FFFFh to 0000h

Figure 11-1 is a simplified block diagram of the Timer1 module.

Register 11-1 details the Timer1 control register, which sets the Operating mode of the Timer1 module. Timer1 can be enabled or disabled by setting or clearing control bit TMR1ON (T1CON<0>).

U = Unimplemented bit, read as '0'

'0' = Bit is cleared

#### **REGISTER 11-1:** T1CON: TIMER1 CONTROL REGISTER

|         | R/W-0       | U-0                          | R/W-0          | R/W-0          | U-0           | R/W-0     | R/W-0  | R/W-0  |

|---------|-------------|------------------------------|----------------|----------------|---------------|-----------|--------|--------|

|         | RD16        | _                            | T1CKPS1        | T1CKPS0        | _             | T1SYNC    | TMR1CS | TMR10N |

|         | bit 7       |                              |                |                |               | I         |        | bit 0  |

|         |             |                              |                |                |               |           |        |        |

| bit 7   | RD16: 16-   | bit Read/W                   | /rite Mode Er  | nable bit      |               |           |        |        |

|         |             | •                            |                | Timer1 in on   |               |           |        |        |

|         | 0 = Enable  | es register                  | read/write of  | Timer1 in two  | o 8-bit opera | tions     |        |        |

| bit 6   | Unimplen    | nented: Re                   | ad as '0'      |                |               |           |        |        |

| bit 5-4 | T1CKPS1     | :T1CKPS0                     | : Timer1 Inpu  | ut Clock Pres  | cale Select I | bits      |        |        |

|         | -           | rescale va                   |                |                |               |           |        |        |

|         |             | Prescale val<br>Prescale val |                |                |               |           |        |        |

|         |             | rescale val<br>Prescale val  |                |                |               |           |        |        |

| bit 3   |             |                              | intain as '0'  |                |               |           |        |        |

| bit 2   |             |                              |                | nput Synchro   | nization Sal  | oct hit   |        |        |

| DILZ    | When TMI    |                              |                | nput Synchic   |               | ect bit   |        |        |

|         |             |                              | ze external c  | lock input     |               |           |        |        |

|         |             |                              | rnal clock inp |                |               |           |        |        |

|         | When TMI    | R1CS = 0:                    |                |                |               |           |        |        |

|         | This bit is | ignored. Tii                 | mer1 uses th   | e internal clo | ck when TM    | R1CS = 0. |        |        |

| bit 1   | TMR1CS:     | Timer1 Clo                   | ock Source S   | elect bit      |               |           |        |        |

|         | 1 = Extern  | al clock fro                 | m pin RC0/T    | 13CKI (on th   | e rising edge | e)        |        |        |

|         | 0 = Interna | al clock (Fo                 | sc/4)          |                |               |           |        |        |

| bit 0   | TMR10N:     | Timer1 Or                    | ı bit          |                |               |           |        |        |

|         | 1 = Enable  |                              |                |                |               |           |        |        |

|         | 0 = Stops   | Timer1                       |                |                |               |           |        |        |

|         | r           |                              |                |                |               |           |        |        |

|         | Legend:     |                              |                |                |               |           |        |        |

R = Readable bit

- n = Value at POR

W = Writable bit

'1' = Bit is set

x = Bit is unknown

NOTES:

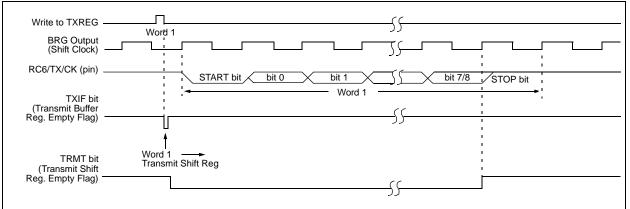

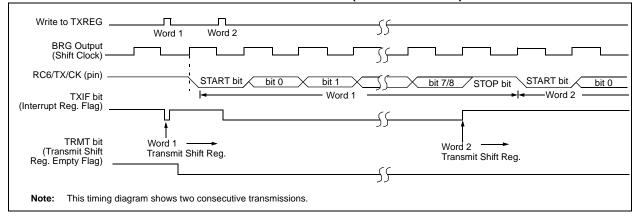

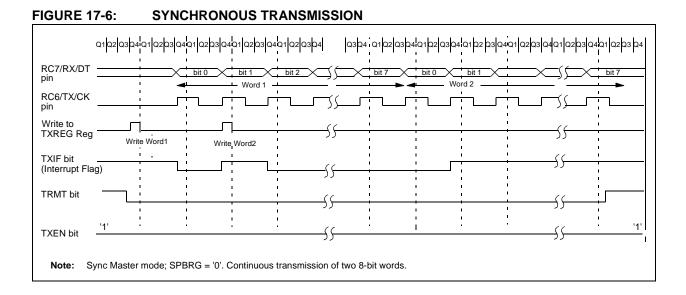

#### FIGURE 17-3: ASYNCHRONOUS TRANSMISSION (BACK TO BACK)

## TABLE 17-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Name   | Bit 7                | Bit 6       | Bit 5    | Bit 4         | Bit 3 | Bit 2  | Bit 1         | Bit 0  | Value on<br>POR, BOR | Value on<br>All Other<br>RESETS |

|--------|----------------------|-------------|----------|---------------|-------|--------|---------------|--------|----------------------|---------------------------------|

| INTCON | GIE/GIEH             | PEIE/GIEL   | TMR0IE   | <b>INTOIE</b> | RBIE  | TMR0IF | <b>INT0IF</b> | RBIF   | 0000 000x            | 0000 000u                       |

| PIR1   | PSPIF <sup>(1)</sup> | ADIF        | RCIF     | TXIF          | SSPIF | _      | TMR2IF        | TMR1IF | 0000 0000            | 0000 0000                       |

| PIE1   | PSPIE <sup>(1)</sup> | ADIE        | RCIE     | TXIE          | SSPIE | _      | TMR2IE        | TMR1IE | 0000 0000            | 0000 0000                       |

| IPR1   | PSPIP <sup>(1)</sup> | ADIP        | RCIP     | TXIP          | SSPIP | _      | TMR2IP        | TMR1IP | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN                 | RX9         | SREN     | CREN          | ADDEN | FERR   | OERR          | RX9D   | 0000 -00x            | 0000 -00x                       |

| TXREG  | USART Tra            | nsmit Regis | ter      |               |       |        |               |        | 0000 0000            | 0000 0000                       |

| TXSTA  | CSRC                 | TX9         | TXEN     | SYNC          | —     | BRGH   | TRMT          | TX9D   | 0000 -010            | 0000 -010                       |

| SPBRG  | Baud Rate            | Generator F | Register |               |       |        |               |        | 0000 0000            | 0000 0000                       |

Legend: x = unknown, - = unimplemented locations read as '0'.

Shaded cells are not used for Asynchronous Transmission.

Note 1: The PSPIF, PSPIE and PSPIP bits are reserved on the PIC18F2X39 devices; always maintain these bits clear.

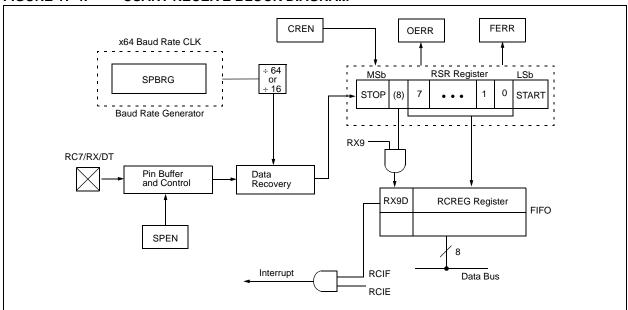

#### 17.2.2 USART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 17-4. The data is received on the RC7/RX/DT pin and drives the data recovery block. The data recovery block is actually a high speed shifter operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate or at Fosc. This mode would typically be used in RS-232 systems.

To set up an Asynchronous Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH (Section 17.1).

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, set enable bit RCIE.

- 4. If 9-bit reception is desired, set bit RX9.

- 5. Enable the reception by setting bit CREN.

- Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 7. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If any error occurred, clear the error by clearing enable bit CREN.

- 10. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

## 17.2.3 SETTING UP 9-BIT MODE WITH ADDRESS DETECT

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is required, set the BRGH bit.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If interrupts are required, set the RCEN bit and select the desired priority level with the RCIP bit.

- 4. Set the RX9 bit to enable 9-bit reception.

- 5. Set the ADDEN bit to enable address detect.

- 6. Enable reception by setting the CREN bit.

- 7. The RCIF bit will be set when reception is complete. The interrupt will be acknowledged if the RCIE and GIE bits are set.

- 8. Read the RCSTA register to determine if any error occurred during reception, as well as read bit 9 of data (if applicable).

- 9. Read RCREG to determine if the device is being addressed.

- 10. If any error occurred, clear the CREN bit.

- 11. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and interrupt the CPU.

#### FIGURE 17-4: USART RECEIVE BLOCK DIAGRAM

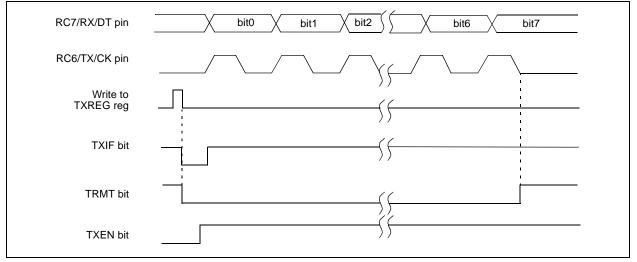

#### FIGURE 17-7: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

NOTES:

## 20.0 SPECIAL FEATURES OF THE CPU

There are several features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving Operating modes and offer code protection. These are:

- OSC Selection

- RESET

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code Protection

- ID Locations

- In-Circuit Serial Programming

All PIC18FXX39 devices have a Watchdog Timer, which is permanently enabled via the configuration bits, or software controlled. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay on power-up only, designed to keep the part in RESET while the power supply stabilizes. With these two timers on-chip, most applications need no external RESET circuitry.

SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer Wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost, while the LP crystal option saves power. A set of configuration bits are used to select various options.

## 20.1 Configuration Bits

The configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped starting at program memory location 300000h.

The user will note that address 300000h is beyond the user program memory space. In fact, it belongs to the configuration memory space (300000h - 3FFFFh), which can only be accessed using Table Reads and Table Writes.

Programming the configuration registers is done in a manner similar to programming the FLASH memory (see Section 5.5.1). The only difference is the configuration registers are written a byte at a time. The sequence of events for programming configuration registers is:

- 1. Load table pointer with address of configuration register being written.

- 2. Write a single byte using the TBLWT instruction.

- 3. Set EEPGD to point to program memory, set the CFGS bit to access configuration registers, and set WREN to enable byte writes.

- 4. Disable interrupts.

- 5. Write 55h to EECON2.

- 6. Write AAh to EECON2.

- 7. Set the WR bit. This will begin the write cycle.

- CPU will stall for duration of write (approximately 2 ms using internal timer).

- 9. Execute a NOP.

- 10. Re-enable interrupts.

| BTF      | BTFSC Bit Test File, Skip if Clear                    |                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                   |      |               |  |  |  |  |

|----------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------|--|--|--|--|

| Synta    | ax:                                                   | [ <i>label</i> ] B                                                                                                       | [ <i>label</i> ] BTFSC f,b[,a]                                                                                                                                                                                                                                                                                                                                                                                    |      |               |  |  |  |  |

| Oper     | ands:                                                 | $\begin{array}{l} 0\leq f\leq 255\\ 0\leq b\leq 7\\ a\in [0,1] \end{array}$                                              |                                                                                                                                                                                                                                                                                                                                                                                                                   |      |               |  |  |  |  |

| Oper     | ation:                                                | skip if (f <b< td=""><td>&gt;) = 0</td><td></td><td></td></b<>                                                           | >) = 0                                                                                                                                                                                                                                                                                                                                                                                                            |      |               |  |  |  |  |

| Statu    | is Affected:                                          | None                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                   |      |               |  |  |  |  |

| Enco     | oding:                                                | 1011                                                                                                                     | bbba                                                                                                                                                                                                                                                                                                                                                                                                              | ffff | ffff          |  |  |  |  |

| Desc     | ription:                                              | next instru-<br>If bit 'b' is 0<br>fetched du<br>execution i<br>executed in<br>cycle instru<br>Access Ba<br>riding the B | If bit 'b' in register 'f' is 0, then the<br>next instruction is skipped.<br>If bit 'b' is 0, then the next instruction<br>fetched during the current instruction<br>execution is discarded, and a NOP is<br>executed instead, making this a two-<br>cycle instruction. If 'a' is 0, the<br>Access Bank will be selected, over-<br>riding the BSR value. If 'a' = 1, then<br>the bank will be selected as per the |      |               |  |  |  |  |

| Word     | ds:                                                   | 1                                                                                                                        | (,                                                                                                                                                                                                                                                                                                                                                                                                                |      |               |  |  |  |  |

| Cycle    | es:                                                   |                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                   |      |               |  |  |  |  |

| QC       | ycle Activity:                                        | •                                                                                                                        | 0.0                                                                                                                                                                                                                                                                                                                                                                                                               |      | 04            |  |  |  |  |

|          | Q1<br>Decode                                          | Q2<br>Read                                                                                                               | Q3<br>Process D                                                                                                                                                                                                                                                                                                                                                                                                   | ata  | Q4<br>No      |  |  |  |  |

|          | Decode                                                | register 'f'                                                                                                             | 1100000 D                                                                                                                                                                                                                                                                                                                                                                                                         |      | eration       |  |  |  |  |

| lf sk    | ip:                                                   |                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                   |      |               |  |  |  |  |

|          | Q1                                                    | Q2                                                                                                                       | Q3                                                                                                                                                                                                                                                                                                                                                                                                                | ;    | Q4            |  |  |  |  |

|          | No<br>operation                                       | No<br>operation                                                                                                          | No<br>operatio                                                                                                                                                                                                                                                                                                                                                                                                    | n op | No<br>eration |  |  |  |  |

| lf sk    | ip and follow                                         |                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                   |      |               |  |  |  |  |

|          | Q1                                                    | Q2                                                                                                                       | Q3                                                                                                                                                                                                                                                                                                                                                                                                                |      | Q4            |  |  |  |  |

|          | No                                                    | No                                                                                                                       | No                                                                                                                                                                                                                                                                                                                                                                                                                |      | No            |  |  |  |  |

|          | operation<br>No                                       | operation<br>No                                                                                                          | operatio<br>No                                                                                                                                                                                                                                                                                                                                                                                                    | n op | eration<br>No |  |  |  |  |

|          | operation                                             | operation                                                                                                                | operatio                                                                                                                                                                                                                                                                                                                                                                                                          | n op | eration       |  |  |  |  |

| Example: |                                                       | HERE BTFSC FLAG, 1, 0<br>FALSE :<br>TRUE :                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                   |      |               |  |  |  |  |

| I        | Before Instru<br>PC                                   |                                                                                                                          | iress (HER                                                                                                                                                                                                                                                                                                                                                                                                        | E)   |               |  |  |  |  |

| ,        | After Instructi<br>If FLAG<´<br>PC<br>If FLAG<´<br>PC | l> = 0;<br>= add<br>l> = 1;                                                                                              | <b>iress</b> (TRU<br><b>iress</b> (FAI                                                                                                                                                                                                                                                                                                                                                                            |      |               |  |  |  |  |

| BTFSS                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Bit Test File, Skip if Set                                                                                 |                                                                                      |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | FSS f,b[,a]                                                                                                |                                                                                      |  |  |  |  |

| Operands:                                                                                                                                                             | $0 \le f \le 255$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                            |                                                                                      |  |  |  |  |

|                                                                                                                                                                       | 0 ≤ b ≤ 7<br>a ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                            |                                                                                      |  |  |  |  |

| Operation                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ) _ 1                                                                                                      |                                                                                      |  |  |  |  |

| Operation:                                                                                                                                                            | skip if (f <b< td=""><td>&gt;) = 1</td><td></td></b<>                                                                                                                                                                                                                                                                                                                                                                                                                                                 | >) = 1                                                                                                     |                                                                                      |  |  |  |  |

| Status Affected:                                                                                                                                                      | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                            |                                                                                      |  |  |  |  |

| Encoding:                                                                                                                                                             | 1010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bbba ff                                                                                                    | ff ffff                                                                              |  |  |  |  |

| Description:<br>Words:                                                                                                                                                | If bit 'b' in register 'f' is 1, then the<br>next instruction is skipped.<br>If bit 'b' is 1, then the next instruction<br>fetched during the current instruc-<br>tion execution, is discarded and a<br>NOP is executed instead, making this<br>a two-cycle instruction. If 'a' is 0, the<br>Access Bank will be selected, over-<br>riding the BSR value. If 'a' = 1, then<br>the bank will be selected as per the<br>BSR value (default).<br>1<br>1(2)<br><b>Note:</b> 3 cycles if skip and followed |                                                                                                            |                                                                                      |  |  |  |  |