innin receive

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 32                                                                        |

| Program Memory Size        | 24KB (12K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 1408 x 8                                                                  |

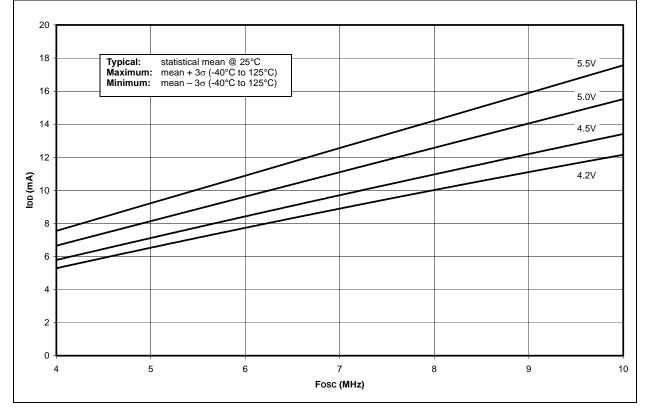

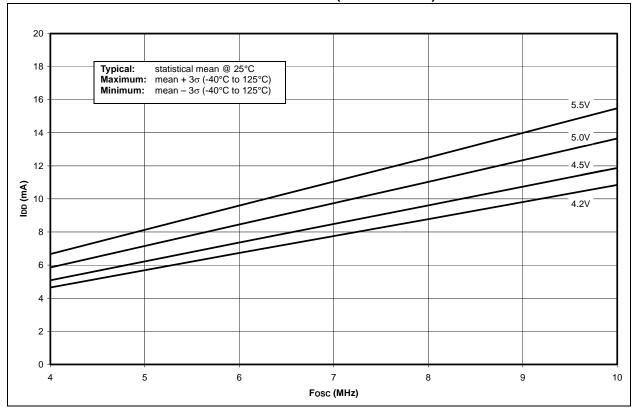

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-TQFP                                                                   |

| Supplier Device Package    | 44-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4539-e-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 1.0   | Device Overview                                                             | 7   |

|-------|-----------------------------------------------------------------------------|-----|

| 2.0   | Oscillator Configurations                                                   | 19  |

| 3.0   | Reset                                                                       | 23  |

| 4.0   | Memory Organization                                                         | 33  |

| 5.0   | FLASH Program Memory                                                        | 51  |

| 6.0   | Data EEPROM Memory                                                          | 61  |

| 7.0   | 8 X 8 Hardware Multiplier                                                   | 67  |

| 8.0   | Interrupts                                                                  | 69  |

| 9.0   | I/O Ports                                                                   | 83  |

| 10.0  | Timer0 Module                                                               | 99  |

| 11.0  | Timer1 Module                                                               | 103 |

| 12.0  | Timer2 Module                                                               | 107 |

| 13.0  | Timer3 Module                                                               | 109 |

| 14.0  | Single Phase Induction Motor Control Kernel                                 | 113 |

| 15.0  | Pulse Width Modulation (PWM) Modules                                        | 123 |

| 16.0  | Master Synchronous Serial Port (MSSP) Module                                |     |

| 17.0  | Addressable Universal Synchronous Asynchronous Receiver Transmitter (USART) | 165 |

| 18.0  | Compatible 10-bit Analog-to-Digital Converter (A/D) Module                  |     |

| 19.0  | Low Voltage Detect                                                          | 189 |

| 20.0  | Special Features of the CPU                                                 | 195 |

| 21.0  | Instruction Set Summary                                                     | 211 |

| 22.0  | Development Support                                                         | 253 |

| 23.0  | Electrical Characteristics                                                  | 259 |

| 24.0  | DC and AC Characteristics Graphs and Tables                                 | 287 |

| 25.0  | Packaging Information                                                       | 297 |

| Appe  | ndix A: Revision History                                                    | 305 |

| Appe  | ndix B: Device Differences                                                  | 305 |

|       | ndix C: Conversion Considerations                                           |     |

| Appe  | ndix D: Migration from High-End to Enhanced Devices                         | 307 |

| Index |                                                                             | 309 |

|       | ne Support                                                                  |     |

| Syste | ms Information and Upgrade Hot Line                                         | 317 |

|       | er Response                                                                 |     |

| PIC1  | 3FXX39 Product Identification System                                        | 319 |

| TABLE 1-2: | PIC18F2X39 PINOUT I/O DESCRIPTIONS (CONTINUED) | ) |

|------------|------------------------------------------------|---|

|------------|------------------------------------------------|---|

| Pin Name         | Pin Number     Pin     Buffer       DIP     SOIC     Type     Buffer |           | er Pin Bu   |     | Description                                               |

|------------------|----------------------------------------------------------------------|-----------|-------------|-----|-----------------------------------------------------------|

| Pin Name         |                                                                      |           | Description |     |                                                           |

|                  |                                                                      |           |             |     | PORTB is a bi-directional I/O port. PORTB can be software |

|                  |                                                                      |           |             |     | programmed for internal weak pull-ups on all inputs.      |

| RB0/INT0         | 21                                                                   | 21        |             |     |                                                           |

| RB0              |                                                                      |           | I/O         | TTL | Digital I/O.                                              |

| INT0             |                                                                      |           | I           | ST  | External interrupt 0.                                     |

| RB1/INT1         | 22                                                                   | 22        |             |     |                                                           |

| RB1              |                                                                      |           | I/O         | TTL | Digital I/O.                                              |

| INT1             |                                                                      |           | I           | ST  | External interrupt 1.                                     |

| RB2/INT2         | 23                                                                   | 23        |             |     |                                                           |

| RB2              |                                                                      |           | I/O         | TTL | Digital I/O.                                              |

| INT2             |                                                                      |           | I           | ST  | External interrupt 2.                                     |

| RB3              | 24                                                                   | 24        | I/O         | TTL | Digital I/O.                                              |

| RB4              | 25                                                                   | 25        | I/O         | TTL | Digital I/O.                                              |

|                  |                                                                      |           |             |     | Interrupt-on-change pin.                                  |

| RB5/PGM          | 26                                                                   | 26        |             |     |                                                           |

| RB5              |                                                                      |           | I/O         | TTL | Digital I/O. Interrupt-on-change pin.                     |

| PGM              |                                                                      |           | I/O         | ST  | Low Voltage ICSP programming enable pin.                  |

| RB6/PGC          | 27                                                                   | 27        |             |     |                                                           |

| RB6              |                                                                      |           | I/O         | TTL | Digital I/O. Interrupt-on-change pin.                     |

| PGC              |                                                                      |           | I/O         | ST  | In-Circuit Debugger and ICSP programming clock pin.       |

| RB7/PGD          | 28                                                                   | 28        |             |     |                                                           |

| RB7              |                                                                      |           | I/O         | TTL | Digital I/O. Interrupt-on-change pin.                     |

| PGD              |                                                                      |           | I/O         | ST  | In-Circuit Debugger and ICSP programming data pin.        |

| Legend: TTL = TT | L compat                                                             | tible inp | ut          |     | CMOS = CMOS compatible input or output                    |

ST = Schmitt Trigger input with CMOS levels O = Output OD = Open Drain (no P diode to VDD)

= Input

Р = Power

L

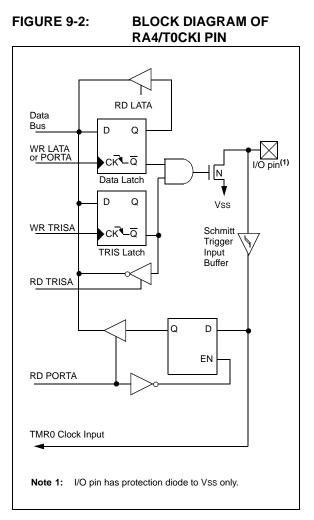

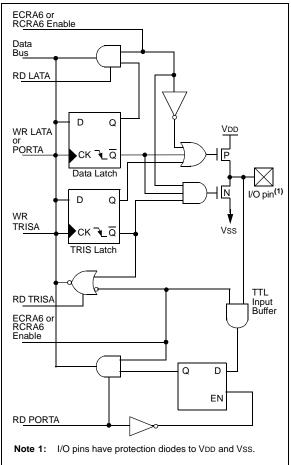

### FIGURE 9-3: BLOCK DIAGRAM OF RA6 PIN

### 11.0 TIMER1 MODULE

The Timer1 module timer/counter has the following features:

- 16-bit timer/counter (two 8-bit registers, TMR1H and TMR1L)

- Readable and writable (both registers)

- Internal or external clock select

- Interrupt-on-overflow from FFFFh to 0000h

Figure 11-1 is a simplified block diagram of the Timer1 module.

Register 11-1 details the Timer1 control register, which sets the Operating mode of the Timer1 module. Timer1 can be enabled or disabled by setting or clearing control bit TMR1ON (T1CON<0>).

U = Unimplemented bit, read as '0'

'0' = Bit is cleared

#### **REGISTER 11-1:** T1CON: TIMER1 CONTROL REGISTER

|         | R/W-0       | U-0                                                               | R/W-0          | R/W-0          | U-0           | R/W-0     | R/W-0  | R/W-0  |  |  |  |

|---------|-------------|-------------------------------------------------------------------|----------------|----------------|---------------|-----------|--------|--------|--|--|--|

|         | RD16        | _                                                                 | T1CKPS1        | T1CKPS0        | _             | T1SYNC    | TMR1CS | TMR10N |  |  |  |

|         | bit 7       |                                                                   |                |                |               | I         |        | bit 0  |  |  |  |

|         |             |                                                                   |                |                |               |           |        |        |  |  |  |

| bit 7   | RD16: 16-   | bit Read/W                                                        | /rite Mode Er  | nable bit      |               |           |        |        |  |  |  |

|         |             | 1 = Enables register read/write of Timer1 in one 16-bit operation |                |                |               |           |        |        |  |  |  |

|         | 0 = Enable  | es register                                                       | read/write of  | Timer1 in two  | o 8-bit opera | tions     |        |        |  |  |  |

| bit 6   | Unimplen    | nented: Re                                                        | ad as '0'      |                |               |           |        |        |  |  |  |

| bit 5-4 | T1CKPS1     | :T1CKPS0                                                          | : Timer1 Inpu  | ut Clock Pres  | cale Select I | bits      |        |        |  |  |  |

|         | -           | rescale va                                                        |                |                |               |           |        |        |  |  |  |

|         |             | Prescale val<br>Prescale val                                      |                |                |               |           |        |        |  |  |  |

|         |             | rescale val<br>Prescale val                                       |                |                |               |           |        |        |  |  |  |

| bit 3   |             |                                                                   | intain as '0'  |                |               |           |        |        |  |  |  |

| bit 2   |             |                                                                   |                | nput Synchro   | nization Sal  | oct hit   |        |        |  |  |  |

| DILZ    | When TMI    |                                                                   |                | nput Synchic   |               | ect bit   |        |        |  |  |  |

|         |             |                                                                   | ze external c  | lock input     |               |           |        |        |  |  |  |

|         |             |                                                                   | rnal clock inp |                |               |           |        |        |  |  |  |

|         | When TMI    | R1CS = 0:                                                         |                |                |               |           |        |        |  |  |  |

|         | This bit is | ignored. Tii                                                      | mer1 uses th   | e internal clo | ck when TM    | R1CS = 0. |        |        |  |  |  |

| bit 1   | TMR1CS:     | Timer1 Clo                                                        | ock Source S   | elect bit      |               |           |        |        |  |  |  |

|         | 1 = Extern  | al clock fro                                                      | m pin RC0/T    | 13CKI (on th   | e rising edge | e)        |        |        |  |  |  |

|         | 0 = Interna | al clock (Fo                                                      | sc/4)          |                |               |           |        |        |  |  |  |

| bit 0   | TMR10N:     | Timer1 Or                                                         | ı bit          |                |               |           |        |        |  |  |  |

|         | 1 = Enable  |                                                                   |                |                |               |           |        |        |  |  |  |

|         | 0 = Stops   | Timer1                                                            |                |                |               |           |        |        |  |  |  |

|         | r           |                                                                   |                |                |               |           |        |        |  |  |  |

|         | Legend:     |                                                                   |                |                |               |           |        |        |  |  |  |

R = Readable bit

- n = Value at POR

W = Writable bit

'1' = Bit is set

x = Bit is unknown

### 15.1.2 PWM DUTY CYCLE

The PWM duty cycle is set by the Motor Control module when it writes a 10-bit value to the CCPR1L and CCP1CON registers, where CCPR1L contains the eight Most Significant bits and CCP1CON<5:4> contains the two Least Significant bits. The duty cycle time is given by the equation:

PWM duty cycle = (10-bit CCP register value) • Tosc • (TMR2 prescale value)

where Tosc and the duty cycle are in the same unit of time.

The CCPR1H register and a 2-bit internal latch are used to double-buffer the PWM duty cycle. This buffering is essential for glitchless PWM operation. At the same time, the value of TMR2 is concatenated with either an internal 2-bit Q clock, or 2 bits of the TMR2 prescaler. When the CCPR1H:latch pair value matches that of the TMR2:latch pair, the PWM1 pin is cleared.

The maximum PWM resolution (bits) for a given PWM frequency is given by the equation:

PWM Resolution (max) =

$$\frac{\log(\frac{FOSC}{FPWM})}{\log(2)}$$

bits

where FPWM is the PWM frequency, or (1/PWM period).

Note: If the PWM duty cycle value is longer than the PWM period, the PWM1 pin will not be cleared.

| Name                | Bit 7                | Bit 6        | Bit 5       | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>All Other<br>RESETS |

|---------------------|----------------------|--------------|-------------|--------|-------|--------|--------|--------|----------------------|---------------------------------|

| INTCON              | GIE/GIEH             | PEIE/GIEL    | TMR0IE      | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF   | 0000 000x            | 0000 000u                       |

| PIR1                | PSPIF <sup>(1)</sup> | ADIF         | RCIF        | TXIF   | SSPIF | —      | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| PIE1                | PSPIE <sup>(1)</sup> | ADIE         | RCIE        | TXIE   | SSPIE | —      | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| IPR1                | PSPIP <sup>(1)</sup> | ADIP         | RCIP        | TXIP   | SSPIP | _      | TMR2IP | TMR1IP | 0000 0000            | 0000 0000                       |

| TMR2 <sup>*</sup>   | *                    | *            | *           | *      | *     | *      | *      | *      | 0000 0000            | 0000 0000                       |

| PR2 <sup>*</sup>    | *                    | *            | *           | *      | *     | *      | *      | *      | 1111 1111            | 1111 1111                       |

| T2CON <sup>*</sup>  | *                    | *            | *           | *      | *     | *      | *      | *      | -000 0000            | -000 0000                       |

| CCPR1L <sup>*</sup> | *                    | *            | *           | *      | *     | *      | *      | *      | xxxx xxxx            | uuuu uuuu                       |

| CCPR1H              | PWM Reg              | ister1 (MSB) | (read-only) |        |       |        |        |        | xxxx xxxx            | uuuu uuuu                       |

| CCP1CON*            | —                    | _            | *           | *      | *     | *      | *      | *      | 00 0000              | 00 0000                         |

| CCPR2L <sup>*</sup> | *                    | *            | *           | *      | *     | *      | *      | *      | xxxx xxxx            | uuuu uuuu                       |

| CCPR2H <sup>*</sup> | PWM Reg              | ister2 (MSB) | (read-only) |        |       |        |        |        | xxxx xxxx            | uuuu uuuu                       |

| CCP2CON*            | —                    | _            | *           | *      | *     | *      | *      | *      | 00 0000              | 00 0000                         |

| L                   |                      | -            |             |        | 1 101 |        |        |        |                      |                                 |

### TABLE 15-1: REGISTERS ASSOCIATED WITH PWM AND TIMER2

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0' unless otherwise noted. Shaded cells are not used by PWM and Timer2.

These registers are retained to maintain compatibility with PIC18FXX2 devices; however, the indicated bits are reserved in PIC18FXX39 devices. Users should not alter the values of these bits.

Note 1: The PSPIF, PSPIE and PSPIP bits are reserved on the PIC18F2X39 devices; always maintain these bits clear.

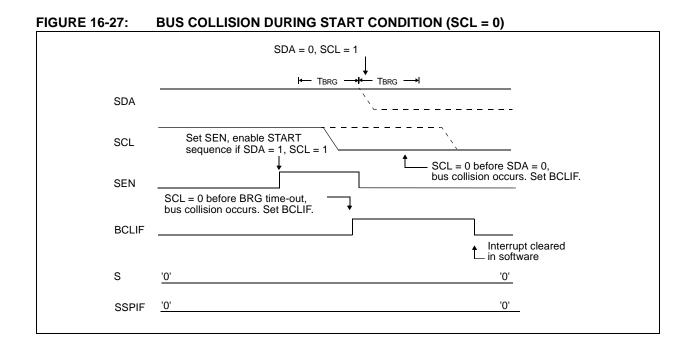

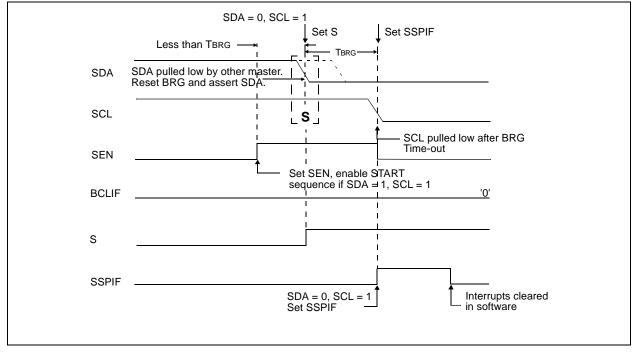

#### FIGURE 16-28: BRG RESET DUE TO SDA ARBITRATION DURING START CONDITION

### 17.0 ADDRESSABLE UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (USART)

The Universal Synchronous Asynchronous Receiver Transmitter (USART) module is one of the two serial I/O modules. (USART is also known as a Serial Communications Interface or SCI.) The USART can be configured as a full-duplex asynchronous system that can communicate with peripheral devices, such as CRT terminals and personal computers, or it can be configured as a half-duplex synchronous system that can communicate with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs, etc.

The USART can be configured in the following modes:

- Asynchronous (full-duplex)

- Synchronous Master (half-duplex)

- Synchronous Slave (half-duplex)

In order to configure pins RC6/TX/CK and RC7/RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter:

- bit SPEN (RCSTA<7>) must be set (= 1),

- bit TRISC<6> must be cleared (= 0), and

- bit TRISC<7> must be set (= 1).

Register 17-1 shows the Transmit Status and Control Register (TXSTA) and Register 17-2 shows the Receive Status and Control Register (RCSTA).

## 20.0 SPECIAL FEATURES OF THE CPU

There are several features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving Operating modes and offer code protection. These are:

- OSC Selection

- RESET

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code Protection

- ID Locations

- In-Circuit Serial Programming

All PIC18FXX39 devices have a Watchdog Timer, which is permanently enabled via the configuration bits, or software controlled. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay on power-up only, designed to keep the part in RESET while the power supply stabilizes. With these two timers on-chip, most applications need no external RESET circuitry.

SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer Wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost, while the LP crystal option saves power. A set of configuration bits are used to select various options.

### 20.1 Configuration Bits

The configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped starting at program memory location 300000h.

The user will note that address 300000h is beyond the user program memory space. In fact, it belongs to the configuration memory space (300000h - 3FFFFh), which can only be accessed using Table Reads and Table Writes.

Programming the configuration registers is done in a manner similar to programming the FLASH memory (see Section 5.5.1). The only difference is the configuration registers are written a byte at a time. The sequence of events for programming configuration registers is:

- 1. Load table pointer with address of configuration register being written.

- 2. Write a single byte using the TBLWT instruction.

- 3. Set EEPGD to point to program memory, set the CFGS bit to access configuration registers, and set WREN to enable byte writes.

- 4. Disable interrupts.

- 5. Write 55h to EECON2.

- 6. Write AAh to EECON2.

- 7. Set the WR bit. This will begin the write cycle.

- 8. CPU will stall for duration of write (approximately 2 ms using internal timer).

- 9. Execute a NOP.

- 10. Re-enable interrupts.

### TABLE 21-2: PIC18FXXX INSTRUCTION SET

| Mnemonic, |                                 | Description                              | Cycles     | 16   | Bit Instr    | uction W | ord  | Status                             | Notes      |

|-----------|---------------------------------|------------------------------------------|------------|------|--------------|----------|------|------------------------------------|------------|

| Opera     | nds                             | Description                              | Cycles     | MSb  |              |          | LSb  | Affected                           | Notes      |

| BYTE-ORI  |                                 | ILE REGISTER OPERATIONS                  |            |      |              |          |      |                                    |            |

| ADDWF     | f, d, a                         | Add WREG and f                           | 1          | 0010 | 01da0        | ffff     | ffff | C, DC, Z, OV, N                    | 1, 2       |

| ADDWFC    | f, d, a                         | Add WREG and Carry bit to f              | 1          | 0010 | 0da          | ffff     | ffff | C, DC, Z, OV, N                    | 1, 2       |

| ANDWF     | f, d, a                         | AND WREG with f                          | 1          | 0001 | 01da         | ffff     | ffff | Z, N                               | 1,2        |

| CLRF      | f, a                            | Clear f                                  | 1          | 0110 | 101a         | ffff     | ffff | Z                                  | 2          |

| COMF      | f, d, a                         | Complement f                             | 1          | 0001 | 11da         | ffff     | ffff | Z, N                               | 1, 2       |

| CPFSEQ    | f, a                            | Compare f with WREG, skip =              | 1 (2 or 3) | 0110 | 001a         | ffff     | ffff | None                               | 4          |

| CPFSGT    | f, a                            | Compare f with WREG, skip >              | 1 (2 or 3) | 0110 | 010a         | ffff     | ffff | None                               | 4          |

| CPFSLT    | f, a                            | Compare f with WREG, skip <              | 1 (2 or 3) | 0110 | 000a         | ffff     | ffff | None                               | 1, 2       |

| DECF      | f, d, a                         | Decrement f                              | 1          | 0000 | 01da         | ffff     | ffff | C, DC, Z, OV, N                    | 1, 2, 3, 4 |

| DECFSZ    | f, d, a                         | Decrement f, Skip if 0                   | 1 (2 or 3) | 0010 | 11da         | ffff     | ffff | None                               | 1, 2, 3, 4 |

| DCFSNZ    | f, d, a                         | Decrement f, Skip if Not 0               | 1 (2 or 3) | 0100 | 11da         | ffff     | ffff | None                               | 1, 2       |

| INCF      | f, d, a                         | Increment f                              | 1          | 0010 | 10da         | ffff     | ffff | C, DC, Z, OV, N                    | 1, 2, 3, 4 |

| INCFSZ    | f, d, a                         | Increment f, Skip if 0                   | 1 (2 or 3) | 0011 | 11da         | ffff     | ffff | None                               | 4          |

| INFSNZ    | f, d, a                         | Increment f, Skip if Not 0               | 1 (2 or 3) | 0100 | 10da         | ffff     | ffff | None                               | 1, 2       |

| IORWF     | f, d, a                         | Inclusive OR WREG with f                 | 1          | 0001 | 00da         | ffff     | ffff | Z, N                               | 1, 2       |

| MOVF      | f, d, a                         | Move f                                   | 1          | 0101 | 00da         | ffff     | ffff | Z, N                               | 1          |

| MOVFF     | f <sub>s</sub> , f <sub>d</sub> | Move f <sub>s</sub> (source) to 1st word | 2          | 1100 | ffff         | ffff     | ffff | None                               |            |

|           | ·s, ·u                          | f <sub>d</sub> (destination) 2nd word    | -          | 1111 | ffff         | ffff     | ffff |                                    |            |

| MOVWF     | f, a                            | Move WREG to f                           | 1          | 0110 | 111a         | ffff     | ffff | None                               |            |

| MULWF     | f, a                            | Multiply WREG with f                     | 1          | 0000 | 001a         | ffff     | ffff | None                               |            |

| NEGF      | f, a                            | Negate f                                 | 1          | 0110 | 110a         | ffff     | ffff | C, DC, Z, OV, N                    | 1, 2       |

| RLCF      | f, d, a                         | Rotate Left f through Carry              | 1          | 0011 | 01da         | ffff     | ffff | C, Z, N                            | ., _       |

| RLNCF     | f, d, a                         | Rotate Left f (No Carry)                 | 1          | 0100 | 01da         | ffff     | ffff | Z, N                               | 1, 2       |

| RRCF      | f, d, a                         | Rotate Right f through Carry             | 1          | 0011 | 00da         | ffff     | ffff | C, Z, N                            | 1, 2       |

| RRNCF     | , ,                             | Rotate Right f (No Carry)                | 1          | 0100 | 00da         | ffff     | ffff | Z, N                               |            |

| SETF      | f, a, u                         | Set f                                    | 1          | 0110 | 100a         | ffff     | ffff | None                               |            |

| SUBFWB    | f, d, a                         | Subtract f from WREG with borrow         | 1          | 0101 | 01da         | ffff     | ffff | C, DC, Z, OV, N                    | 1, 2       |

| SUBWF     | f, d, a                         | Subtract WREG from f                     | 1          | 0101 | 11da         | ffff     | ffff | C, DC, Z, OV, N                    |            |

| SUBWFB    | f, d, a                         | Subtract WREG from f with<br>borrow      | 1          | 0101 | 11da<br>10da | ffff     | ffff | C, DC, Z, OV, N<br>C, DC, Z, OV, N | 1, 2       |

| SWAPF     | f, d, a                         | Swap nibbles in f                        | 1          | 0011 | 10da         | ffff     | ffff | None                               | 4          |

| TSTFSZ    | f, a                            | Test f, skip if 0                        | 1 (2 or 3) | 0110 | 100a<br>011a | ffff     | ffff | None                               | 4<br>1, 2  |

| XORWF     | f, d, a                         | Exclusive OR WREG with f                 | 1 (2 01 3) | 0001 | 011a<br>10da | ffff     | ffff | Z, N                               | 1,∠        |

|           |                                 | E REGISTER OPERATIONS                    | 1'         | 0001 | Toda         | ±±±±     | LLLL | <u>, 11</u>                        |            |

|           |                                 |                                          |            |      |              |          |      |                                    | 4.0        |

| BCF       | f, b, a                         | Bit Clear f                              | 1          | 1001 | bbba         | ffff     | ffff | None                               | 1, 2       |

| BSF       | f, b, a                         | Bit Set f                                | 1          | 1000 | bbba         | ffff     | ffff | None                               | 1, 2       |

| BTFSC     |                                 | Bit Test f, Skip if Clear                | 1 (2 or 3) | 1011 | bbba         | ffff     | ffff | None                               | 3, 4       |

| BTFSS     | f, b, a                         | Bit Test f, Skip if Set                  | 1 (2 or 3) | 1010 | bbba         | ffff     | ffff | None                               | 3, 4       |

| BTG       | f, d, a                         | Bit Toggle f                             | 1          | 0111 | bbba         | ffff     | ffff | None                               | 1, 2       |

**Note** 1: When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are 2-word instructions. The second word of these instructions will be executed as a NOP, unless the first word of the instruction retrieves the information embedded in these 16-bits. This ensures that all program memory locations have a valid instruction.

5: If the Table Write starts the write cycle to internal memory, the write will continue until terminated.

| BCF               | Bit Clear                                                                                | f                               |                                      |                      |  |  |  |  |

|-------------------|------------------------------------------------------------------------------------------|---------------------------------|--------------------------------------|----------------------|--|--|--|--|

| Syntax:           | [ <i>label</i> ] B                                                                       | CF f,                           | b[,a]                                |                      |  |  |  |  |

| Operands:         | $0 \le f \le 255$<br>$0 \le b \le 7$<br>$a \in [0,1]$                                    |                                 |                                      |                      |  |  |  |  |

| Operation:        | $0 \rightarrow f < b >$                                                                  |                                 |                                      |                      |  |  |  |  |

| Status Affected:  | None                                                                                     |                                 |                                      |                      |  |  |  |  |

| Encoding:         | 1001                                                                                     | bbba                            | ffff                                 | ffff                 |  |  |  |  |

| Description:      | Bit 'b' in re<br>is 0, the A<br>selected, o<br>If 'a' = 1, t<br>selected a<br>(default). | ccess B<br>overridir<br>hen the | ank will b<br>ng the BS<br>bank will | be<br>R value.<br>be |  |  |  |  |

| Words:            | 1                                                                                        |                                 |                                      |                      |  |  |  |  |

| Cycles:           | 1                                                                                        | 1                               |                                      |                      |  |  |  |  |

| Q Cycle Activity: |                                                                                          |                                 |                                      |                      |  |  |  |  |

| Q1                | Q2                                                                                       | Q3                              | 3                                    | Q4                   |  |  |  |  |

| Decode            | Read<br>register 'f'                                                                     | Proce<br>Data                   |                                      | Write<br>gister 'f'  |  |  |  |  |

| Example:          | BCF F                                                                                    | LAG_RE                          | G, 7, (                              | D                    |  |  |  |  |

| After Instruct    | $\Xi G = 0xC7$                                                                           |                                 |                                      |                      |  |  |  |  |

|                                                                                                                                                                                                                                        | Branch if                                                              |                                                       | -            |                                  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------|--------------|----------------------------------|--|--|--|

| Syntax:                                                                                                                                                                                                                                | [ <i>label</i> ] B                                                     | [ <i>label</i> ] BN n                                 |              |                                  |  |  |  |

| Operands:                                                                                                                                                                                                                              | -128 ≤ n ≤                                                             | $-128 \le n \le 127$                                  |              |                                  |  |  |  |

| Operation:                                                                                                                                                                                                                             | •                                                                      | if negative bit is '1' (PC) + 2 + 2n $\rightarrow$ PC |              |                                  |  |  |  |

| Status Affected                                                                                                                                                                                                                        | : None                                                                 |                                                       |              |                                  |  |  |  |

| Encoding:                                                                                                                                                                                                                              | 1110                                                                   | 0110                                                  | nnnn         | nnr                              |  |  |  |

| program will branch.<br>The 2's complement number '2n'<br>added to the PC. Since the PC w<br>have incremented to fetch the net<br>instruction, the new address will b<br>PC+2+2n. This instruction is ther<br>a two-cycle instruction. |                                                                        |                                                       |              |                                  |  |  |  |

|                                                                                                                                                                                                                                        | a two-cyc                                                              | le instruc                                            | tion.        |                                  |  |  |  |

| Words:                                                                                                                                                                                                                                 | 1                                                                      | ie instruc                                            | tion.        |                                  |  |  |  |

| Words:<br>Cycles:                                                                                                                                                                                                                      | •                                                                      | ie instruc                                            | tion.        |                                  |  |  |  |

|                                                                                                                                                                                                                                        | 1<br>1(2)                                                              | ie instruc                                            | tion.        |                                  |  |  |  |

| Cycles:<br>Q Cycle Activi                                                                                                                                                                                                              | 1<br>1(2)                                                              | Q3                                                    | tion.        | Q4                               |  |  |  |

| Cycles:<br>Q Cycle Activi<br>If Jump:                                                                                                                                                                                                  | 1<br>1(2)<br>ty:                                                       |                                                       |              | Q4<br>rite to F                  |  |  |  |

| Cycles:<br>Q Cycle Activi<br>If Jump:<br>Q1<br>Decode<br>No                                                                                                                                                                            | 1<br>1(2)<br>ty:<br>                                                   | Q3<br>Proces<br>Data<br>No                            | s Wi         | rite to F                        |  |  |  |

| Cycles:<br>Q Cycle Activi<br>If Jump:<br>Q1<br>Decode<br>No<br>operation                                                                                                                                                               | 1<br>1(2)<br>ty:<br>Q2<br>Read literal<br>'n'                          | Q3<br>Proces<br>Data                                  | s Wi         | rite to F                        |  |  |  |

| Cycles:<br>Q Cycle Activi<br>If Jump:<br>Q1<br>Decode<br>No<br>operation<br>If No Jump:                                                                                                                                                | 1<br>1(2)<br>ty:<br>Q2<br>Read literal<br>'n'<br>No<br>operation       | Q3<br>Proces<br>Data<br>No                            | s Wi         | rite to F<br>No<br>peratio       |  |  |  |

| Cycles:<br>Q Cycle Activi<br>If Jump:<br>Q1<br>Decode<br>No<br>operation<br>If No Jump:<br>Q1                                                                                                                                          | 1<br>1(2)<br>ty:<br>Q2<br>Read literal<br>'n'<br>No<br>operation<br>Q2 | Q3<br>Proces<br>Data<br>No<br>operatio                | s Wi<br>on o | rite to F<br>No<br>peratio<br>Q4 |  |  |  |

| Cycles:<br>Q Cycle Activi<br>If Jump:<br>Q1<br>Decode<br>No<br>operation<br>If No Jump:                                                                                                                                                | 1<br>1(2)<br>ty:<br>Q2<br>Read literal<br>'n'<br>No<br>operation       | Q3<br>Proces<br>Data<br>No<br>operatio                | s Wi<br>on o | rite to F<br>No<br>peratio       |  |  |  |

| <b>丘</b> ) |

|------------|

|            |

|            |

| p)         |

| -          |

| E+2)       |

|            |

| BRA   |                                                                                                                                                                                                                                                   | Unconditi                              | onal Brancl                            | h                              | E                                                                                                                                                                        | BSF                                                   | Bit Set f                                   |                       |                             |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------|-----------------------|-----------------------------|--|

| Synt  | ax:                                                                                                                                                                                                                                               | [label] B                              | RA n                                   |                                | S                                                                                                                                                                        | Syntax:                                               | [label] B                                   | SF f,b[,a]            |                             |  |

| Ope   | rands:                                                                                                                                                                                                                                            | -1024 ≤ n :                            | ≤ 1023                                 |                                | C                                                                                                                                                                        | Operands:                                             |                                             | $0 \leq f \leq 255$   |                             |  |

| Ope   | ration:                                                                                                                                                                                                                                           | (PC) + 2 +                             | $2n \rightarrow PC$                    |                                |                                                                                                                                                                          |                                                       | 0 ≤ b ≤ 7<br>a ∈ [0,1]                      |                       |                             |  |

| State | us Affected:                                                                                                                                                                                                                                      | None                                   |                                        |                                |                                                                                                                                                                          | Operation:                                            | $a \in [0, 1]$<br>1 $\rightarrow$ f <b></b> |                       |                             |  |

| Enco  | Encoding:11010nnnnnnnnnnnDescription:Add the 2's complement number<br>'2n' to the PC. Since the PC will<br>have incremented to fetch the next<br>instruction, the new address will be<br>PC+2+2n. This instruction is a<br>two-cycle instruction. |                                        |                                        | Status Affected:               | None                                                                                                                                                                     |                                                       |                                             |                       |                             |  |

| Des   |                                                                                                                                                                                                                                                   |                                        | E                                      | Encoding:<br>Description:      | 1000bbbaffffffffBit 'b' in register 'f' is set. If 'a' is 0Access Bank will be selected, over-riding the BSR value. If 'a' = 1, thenthe bank will be selected as per the |                                                       |                                             |                       |                             |  |

| Wor   | ds:                                                                                                                                                                                                                                               | 1                                      |                                        |                                |                                                                                                                                                                          |                                                       | BSR value                                   | ).                    |                             |  |

| Cycl  | es:                                                                                                                                                                                                                                               | 2                                      |                                        |                                | -                                                                                                                                                                        | Vords:                                                | 1                                           |                       |                             |  |

| QC    | ycle Activity:                                                                                                                                                                                                                                    |                                        |                                        |                                | C                                                                                                                                                                        | Cycles:                                               | 1                                           |                       |                             |  |

|       | Q1                                                                                                                                                                                                                                                | Q2                                     | Q3                                     | Q4                             |                                                                                                                                                                          | Q Cycle Activity:                                     |                                             |                       |                             |  |

|       | Decode<br>No<br>operation                                                                                                                                                                                                                         | Read literal<br>'n'<br>No<br>operation | Process<br>Data<br>No<br>operation     | Write to PC<br>No<br>operation |                                                                                                                                                                          | Q1<br>Decode                                          | Q2<br>Read<br>register 'f'                  | Q3<br>Process<br>Data | Q4<br>Write<br>register 'f' |  |

|       | operation                                                                                                                                                                                                                                         | oporation                              | opolation                              | opolation                      | <u></u>                                                                                                                                                                  | xample:                                               | BSF F                                       | LAG_REG, 7            | , 1                         |  |

|       | n <u>ple</u> :<br>Before Instru<br>PC<br>After Instruct<br>PC                                                                                                                                                                                     | = add                                  | BRA Jump<br>dress (HERE<br>dress (Jump |                                |                                                                                                                                                                          | Before Instru<br>FLAG_RI<br>After Instruct<br>FLAG_RI | EG = 0x0<br>ion                             |                       |                             |  |

| DEC      | FSZ                 | Decremer                                                                                                                                                                                                                                        | Decrement f, skip if 0                                                                                                           |                           |  |  |  |  |  |

|----------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------------|--|--|--|--|--|

| Synt     | ax:                 | [label]                                                                                                                                                                                                                                         | [label] DECFSZ f[,d[,a]]                                                                                                         |                           |  |  |  |  |  |

| Ope      | rands:              | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                             |                                                                                                                                  |                           |  |  |  |  |  |

| Ope      | ration:             | .,                                                                                                                                                                                                                                              | $(f) - 1 \rightarrow dest,$<br>skip if result = 0                                                                                |                           |  |  |  |  |  |

| Statu    | us Affected:        | None                                                                                                                                                                                                                                            |                                                                                                                                  |                           |  |  |  |  |  |

| Enco     | oding:              | 0010                                                                                                                                                                                                                                            | 11da ffi                                                                                                                         | f ffff                    |  |  |  |  |  |

| Desc     | cription:           | nts of register<br>If 'd' is 0, the<br><i>W</i> . If 'd' is 1,<br>ck in register<br>It is 0, the ne<br>is already fr<br>and a NOP i<br>baking it a tw<br>. If 'a' is 0, the<br>perselected,<br>alue. If 'a' =<br>perselected a<br>de (default). | the result is<br>"f' (default).<br>ext instruc-<br>etched, is<br>s executed<br>o-cycle<br>ne Access<br>overriding<br>1, then the |                           |  |  |  |  |  |

| Wor      | ds:                 | 1                                                                                                                                                                                                                                               |                                                                                                                                  |                           |  |  |  |  |  |

| Cycl     |                     | by                                                                                                                                                                                                                                              | ycles if skip a<br>a 2-word ins                                                                                                  | and followed<br>truction. |  |  |  |  |  |

| QC       | Sycle Activity      |                                                                                                                                                                                                                                                 | 00                                                                                                                               | 04                        |  |  |  |  |  |

|          | Q1<br>Decode        | Q2<br>Read                                                                                                                                                                                                                                      | Q3<br>Process                                                                                                                    | Q4<br>Write to            |  |  |  |  |  |

|          | Decoue              | register 'f'                                                                                                                                                                                                                                    | Data                                                                                                                             | destination               |  |  |  |  |  |

| lf sk    | kip:                |                                                                                                                                                                                                                                                 |                                                                                                                                  |                           |  |  |  |  |  |

|          | Q1                  | Q2                                                                                                                                                                                                                                              | Q3                                                                                                                               | Q4                        |  |  |  |  |  |

|          | No                  | No                                                                                                                                                                                                                                              | No                                                                                                                               | No                        |  |  |  |  |  |

|          | operation           | operation                                                                                                                                                                                                                                       | operation                                                                                                                        | operation                 |  |  |  |  |  |

| lf sk    | -                   | ved by 2-word                                                                                                                                                                                                                                   |                                                                                                                                  |                           |  |  |  |  |  |

| 1        | Q1                  | Q2                                                                                                                                                                                                                                              | Q3                                                                                                                               | Q4                        |  |  |  |  |  |

|          | No<br>operation     | No<br>operation                                                                                                                                                                                                                                 | No<br>operation                                                                                                                  | No<br>operation           |  |  |  |  |  |

|          | No                  | No                                                                                                                                                                                                                                              | No                                                                                                                               | No                        |  |  |  |  |  |

|          | operation           | operation                                                                                                                                                                                                                                       | operation                                                                                                                        | operation                 |  |  |  |  |  |

| Example: |                     | HERE                                                                                                                                                                                                                                            | GOTO LOOP                                                                                                                        |                           |  |  |  |  |  |

|          | Before Instru       |                                                                                                                                                                                                                                                 |                                                                                                                                  |                           |  |  |  |  |  |

|          | PC<br>After Instruc | = Address                                                                                                                                                                                                                                       | (HERE)                                                                                                                           |                           |  |  |  |  |  |

|          | CNT<br>If CNT<br>PC | = CNT - 1<br>= 0;<br>= Address                                                                                                                                                                                                                  | G (CONTINUE                                                                                                                      | :)                        |  |  |  |  |  |

|          | If CNT<br>PC        | ≠ 0;                                                                                                                                                                                                                                            | G (HERE+2)                                                                                                                       |                           |  |  |  |  |  |

| DCFSNZ Decrement f, skip if not 0                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                     |                                                               |                         |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------|-------------------------|--|--|--|--|--|

| Syntax:                                                                                                                                                                                                                                                                                                                                                                                                                                                                | [label]                                             | DCFSNZ f[                                                     | ,d [,a]                 |  |  |  |  |  |

| Operands:                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$ | 5                                                             |                         |  |  |  |  |  |

| Operation:                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                     | (f) $-1 \rightarrow \text{dest}$ ,<br>skip if result $\neq 0$ |                         |  |  |  |  |  |

| Status Affected:                                                                                                                                                                                                                                                                                                                                                                                                                                                       | None                                                | None                                                          |                         |  |  |  |  |  |

| Encoding:                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0100                                                | 11da fff                                                      | f ffff                  |  |  |  |  |  |

| Description:<br>The contents of register 'f' are deremented. If 'd' is 0, the result is placed in W. If 'd' is 1, the result placed back in register 'f' (defaul If the result is not 0, the next instruction, which is already fetched, is discarded, and a NOP executed instead, making it a two cycle instruction. If 'a' is 0, the Access Bank will be selected, overriding the BSR value. If 'a' = then the bank will be selected as per the BSR value (default). |                                                     |                                                               |                         |  |  |  |  |  |

| Words: 1                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                     |                                                               |                         |  |  |  |  |  |

| Cycles: 1(2)<br>Note: 3 cycles if skip and followed<br>by a 2-word instruction.                                                                                                                                                                                                                                                                                                                                                                                        |                                                     |                                                               |                         |  |  |  |  |  |

| Q Cycle Activity                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -                                                   |                                                               |                         |  |  |  |  |  |

| Q1                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Q2                                                  | Q3                                                            | Q4                      |  |  |  |  |  |

| Decode                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Read<br>register 'f'                                | Process<br>Data                                               | Write to<br>destination |  |  |  |  |  |