Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                               |

| Number of I/O              | 32                                                                       |

| Program Memory Size        | 24KB (12K x 16)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 1408 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                              |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4539-i-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

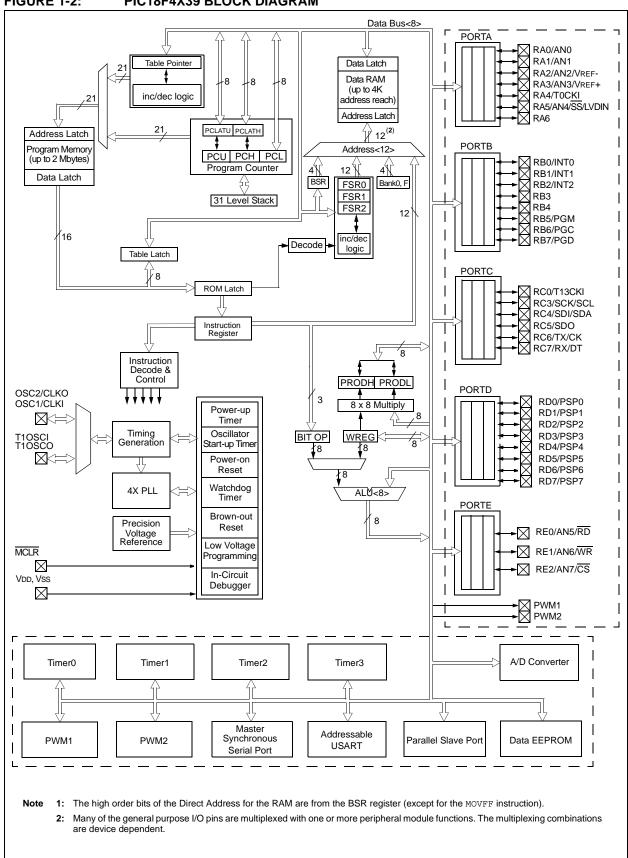

FIGURE 1-2: PIC18F4X39 BLOCK DIAGRAM

© 2002-2013 Microchip Technology Inc.

TABLE 3-3: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

| Register               | Applicable Devices |      | plicable Devices Power-on Reset,<br>Brown-out Reset |      | MCLR Resets WDT Reset RESET Instruction Stack Resets | Wake-up via WDT<br>or Interrupt |                          |

|------------------------|--------------------|------|-----------------------------------------------------|------|------------------------------------------------------|---------------------------------|--------------------------|

| IPR2                   | 2439               | 4439 | 2539                                                | 4539 | 1 1111                                               | 1 1111                          | u uuuu                   |

| PIR2                   | 2439               | 4439 | 2539                                                | 4539 | 0 0000                                               | 0 0000                          | u uuuu <sup>(3)</sup>    |

| PIE2                   | 2439               | 4439 | 2539                                                | 4539 | 0 0000                                               | 0 0000                          | u uuuu                   |

| IPR1                   | 2439               | 4439 | 2539                                                | 4539 | 1111 1111                                            | 1111 1111                       | uuuu uuuu                |

| IFKI                   | 2439               | 4439 | 2539                                                | 4539 | -111 1111                                            | -111 1111                       | -uuu uuuu                |

| PIR1                   | 2439               | 4439 | 2539                                                | 4539 | 0000 0000                                            | 0000 0000                       | uuuu uuuu(3)             |

| PIRT                   | 2439               | 4439 | 2539                                                | 4539 | -000 0000                                            | -000 0000                       | -uuu uuuu(3)             |

| DIE4                   | 2439               | 4439 | 2539                                                | 4539 | 0000 0000                                            | 0000 0000                       | uuuu uuuu                |

| PIE1                   | 2439               | 4439 | 2539                                                | 4539 | -000 0000                                            | -000 0000                       | -uuu uuuu                |

| TRISE                  | 2439               | 4439 | 2539                                                | 4539 | 0000 -111                                            | 0000 -111                       | uuuu -uuu                |

| TRISD                  | 2439               | 4439 | 2539                                                | 4539 | 1111 1111                                            | 1111 1111                       | uuuu uuuu                |

| TRISC*                 | 2439               | 4439 | 2539                                                | 4539 | 1111 1111                                            | 1111 1111                       | uuuu uuuu                |

| TRISB                  | 2439               | 4439 | 2539                                                | 4539 | 1111 1111                                            | 1111 1111                       | uuuu uuuu                |

| TRISA <sup>(5,6)</sup> | 2439               | 4439 | 2539                                                | 4539 | -111 1111 <sup>(5)</sup>                             | -111 1111 <b>(5)</b>            | -uuu uuuu <sup>(5)</sup> |

| LATE                   | 2439               | 4439 | 2539                                                | 4539 | xxx                                                  | uuu                             | uuu                      |

| LATD                   | 2439               | 4439 | 2539                                                | 4539 | xxxx xxxx                                            | uuuu uuuu                       | uuuu uuuu                |

| LATC*                  | 2439               | 4439 | 2539                                                | 4539 | xxxx xxxx                                            | uuuu uuuu                       | uuuu uuuu                |

| LATB                   | 2439               | 4439 | 2539                                                | 4539 | xxxx xxxx                                            | uuuu uuuu                       | uuuu uuuu                |

| LATA <sup>(5,6)</sup>  | 2439               | 4439 | 2539                                                | 4539 | -xxx xxxx(5)                                         | -uuu uuuu <sup>(5)</sup>        | -uuu uuuu <b>(5)</b>     |

| PORTE                  | 2439               | 4439 | 2539                                                | 4539 | 000                                                  | 000                             | uuu                      |

| PORTD                  | 2439               | 4439 | 2539                                                | 4539 | xxxx xxxx                                            | uuuu uuuu                       | uuuu uuuu                |

| PORTC*                 | 2439               | 4439 | 2539                                                | 4539 | xxxx xxxx                                            | uuuu uuuu                       | uuuu uuuu                |

| PORTB                  | 2439               | 4439 | 2539                                                | 4539 | xxxx xxxx                                            | uuuu uuuu                       | uuuu uuuu                |

| PORTA <sup>(5,6)</sup> | 2439               | 4439 | 2539                                                | 4539 | -x0x 0000 <b>(5)</b>                                 | -u0u 0000 <b>(5)</b>            | -uuu uuuu <b>(5)</b>     |

- Legend: u = unchanged, x = unknown, = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

- \* These registers are retained to maintain compatibility with PIC18FXX2 devices; however, one or more bits are reserved. Users should not modify the value of these bits. See Section 4.9.2 for details.

- **Note 1:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- 3: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- 4: See Table 3-2 for RESET value for specific condition.

- **5:** Bit 6 of PORTA, LATA, and TRISA are enabled in ECIO and RCIO Oscillator modes only. In all other Oscillator modes, they are disabled and read '0'.

- 6: Bit 6 of PORTA, LATA and TRISA are not available on all devices. When unimplemented, they are read '0'.

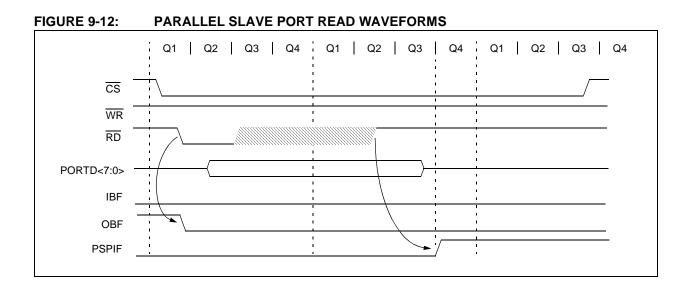

TABLE 9-11: REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

| Name   | Bit 7        | Bit 6         | Bit 5        | Bit 4         | Bit 3 | Bit 2     | Bit 1         | Bit 0     | Value on<br>POR, BOR | Value on<br>All Other<br>RESETS |

|--------|--------------|---------------|--------------|---------------|-------|-----------|---------------|-----------|----------------------|---------------------------------|

| PORTD  | Port Data    | Latch whe     | n written; F | ort pins when | read  |           |               |           | xxxx xxxx            | uuuu uuuu                       |

| LATD   | LATD Data    | a Output b    | its          |               |       |           |               | xxxx xxxx | uuuu uuuu            |                                 |

| TRISD  | PORTD D      | ata Directi   | on bits      |               |       |           |               | 1111 1111 | 1111 1111            |                                 |

| PORTE  | _            | _             | _            | _             | _     | RE2       | RE1           | RE0       | 000                  | 000                             |

| LATE   | _            | _             | _            | _             | _     | LATE Data | a Output bits | 3         | xxx                  | uuu                             |

| TRISE  | IBF          | OBF           | IBOV         | PSPMODE       | _     | PORTE D   | ata Directio  | n bits    | 0000 -111            | 0000 -111                       |

| INTCON | GIE/<br>GIEH | PEIE/<br>GIEL | TMR0IF       | INT0IE        | RBIE  | TMR0IF    | INT0IF        | RBIF      | 0000 000x            | 0000 000u                       |

| PIR1   | PSPIF        | ADIF          | RCIF         | TXIF          | SSPIF | _         | TMR2IF        | TMR1IF    | 0000 0000            | 0000 0000                       |

| PIE1   | PSPIE        | ADIE          | RCIE         | TXIE          | SSPIE | _         | TMR2IE        | TMR1IE    | 0000 0000            | 0000 0000                       |

| IPR1   | PSPIP        | ADIP          | RCIP         | TXIP          | SSPIP | _         | TMR2IP        | TMR1IP    | 0000 0000            | 0000 0000                       |

| ADCON1 | ADFM         | ADCS2         | _            | -             | PCFG3 | PCFG2     | PCFG1         | PCFG0     | 00 0000              | 00 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Parallel Slave Port.

NOTES:

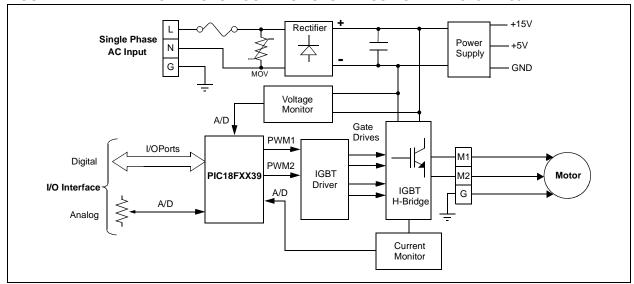

# 14.0 SINGLE PHASE INDUCTION MOTOR CONTROL KERNEL

The Motor Control kernel of the PIC18FXX39 family uses Programmable Motor Processor Technology (ProMPT) to control the speed of a single phase induction motor, with variable frequency technology. The controller's two PWM modules are used to synthesize a sine wave current through the motor windings. The kernel provides open loop control for a continuous frequency range of 15 Hz to 127 Hz.

#### 14.1 Theory of Operation

The speed of an induction motor is a function of frequency, slip and the number of poles in the motor. They are related by the equation:

$$Speed = (F \times 120/P) - Slip$$

where *Speed* and *Slip* are in RPM, *F* is the frequency of the input voltage (in Hertz), and *P* represents the number of motor poles (for this equation, either 2, 4, 6 or 8).

For the purpose of this discussion, slip is assumed to be constant across the motor's useful operating range. Since the rated speed is based on the number of poles (which is fixed at the time of manufacture), this leaves changing the frequency of the supplied voltage as the only way to vary the motor's speed. When the frequency controlling a motor is reduced, however, its impedance is also reduced, resulting in a higher motor current draw.

It can be shown that the voltage applied to the motor is proportional to both the frequency and the current (Equation 14-1). So to keep the current constant at, or below the Full Load Amp rating, the RMS voltage to the motor must be reduced as the frequency is reduced. By varying the supply voltage and frequency at a constant

ratio, the motor's speed can be varied with constant current. Maintaining this constant ratio is the function of the Motor Control kernel.

EQUATION 14-1: KEY RELATIONSHIPS IN SINGLE PHASE MOTORS

$$V \propto \phi \times \omega$$

(1-1)

or:  $V \propto 2\pi f \phi$  (1-2)

$I \propto \phi \propto \frac{V}{f}$  (1-3)

where:  $V$  is applied voltage

$I$  is motor current

$\phi$  is stator flux

$f$  is input frequency

#### 14.2 Typical Hardware Interface

A block diagram for a recommended single phase induction motor control using the PIC18FXX39 is shown in Figure 14-1.

The single phase AC supply is rectified, using a diode bridge and filtered, using a capacitor. The PWM outputs from the PIC18FXX39 synthesize the AC to drive the motor from this DC bus by switching Insulated Gate Bipolar Transistors (IGBTs) on and off. The IGBT gate driver converts the TTL level of PWMs to the required IGBT gate voltage level, and supplies the gate charging current when the IGBT turns on.

The I/O ports of the microcontroller can be used for the external logic controls. The A/D channels can be used for monitoring the DC bus voltage and motor current; a potentiometer can also be connected to one of these channels to provide a variable frequency reference for the motor.

void ProMPT\_SetAccelRate(unsigned char rate)

Resources used: 0 stack level

rate range: 0 to 255

Description: Sets the acceleration to the value of rate in Hz/second. The default setting is 10 Hz/s.

void ProMPT\_SetBoostEndModulation(unsigned char modulation)

Resources used: Hardware Multiplier; 0 stack levels

modulation range: 0 to 200

**Description:** Sets the End Modulation (in %) for the Boost logic. Boost mode operates at Boost Frequency, and the modulation ramps from BoostStartModulation to BoostEndModulation. This function should not be called while Boost is enabled.

unsigned char ProMPT\_SetBoostFrequency(unsigned char frequency)

Resources used: 0 stack levels frequency range: 0 to 127

**Description:** Sets the frequency the drive goes to in Boost mode. Frequency must be < 128. On exit, w = 0 if the command is successful, or w = FFh if the frequency is out of range. This function should not be called while Boost is enabled.

void ProMPT\_SetBoostStartModulation(unsigned char modulation)

Resources used: Hardware Multiplier; 0 stack levels modulation range: 0 to BoostEndModulation

**Description:** Sets the Start Modulation (in %) for the Boost logic. Boost mode operates at Boost Frequency, and the modulation ramps from BoostStartModulation to BoostEndModulation. This function should not be called while Boost is enabled.

void ProMPT\_SetBoostTime(unsigned char time)

Resources used: Hardware Multiplier; 0 stack levels

time range: 0 to 255

**Description:** Sets the amount of time in seconds for the Boost mode. Boost mode operates at Boost Frequency, and the modulation ramps from BoostStartModulation to BoostEndModulation over BoostTime. This function should not be called while Boost is enabled.

void ProMPT\_SetDecelRate(unsigned char rate)

Resources used: 0 stack levels

rate range: 0 to 255

**Description:** Sets the deceleration to the value of rate in Hz per second. The default setting is 5 Hz/s.

unsigned char ProMPT\_SetFrequency(unsigned char frequency)

Resources used: 2 stack levels frequency range: 0 to 127

**Description:** Sets the output frequency of the drive is running. Frequency is limited to 0 to 127, but should be controlled within the valid operational range of the motor. Modulation is determined from the V/F curve, which is set up with the ProMPT\_SetVFCurve method. If frequency = 0, the drive will stop. If the drive is stopped and frequency > 0, the drive will start.

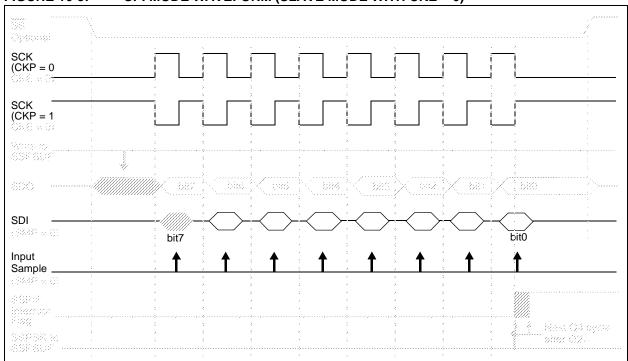

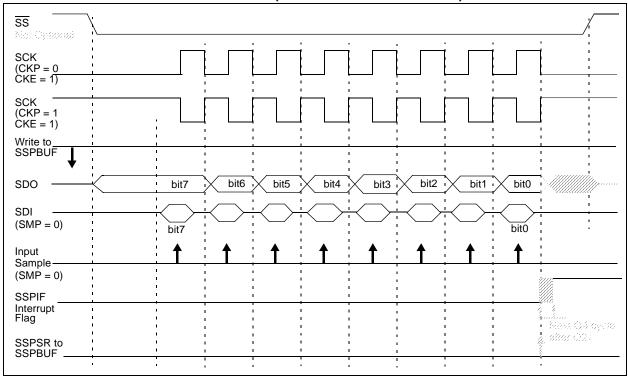

FIGURE 16-5: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 0)

FIGURE 16-6: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

#### REGISTER 16-4: SSPCON1: MSSP CONTROL REGISTER 1 (I<sup>2</sup>C MODE)

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| WCOL  | SSPOV | SSPEN | CKP   | SSPM3 | SSPM2 | SSPM1 | SSPM0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

#### bit 7 WCOL: Write Collision Detect bit

#### In Master Transmit mode:

- 1 = A write to the SSPBUF register was attempted while the I<sup>2</sup>C conditions were not valid for a transmission to be started (must be cleared in software)

- 0 = No collision

#### In Slave Transmit mode:

- 1 = The SSPBUF register is written while it is still transmitting the previous word (must be cleared in software)

- 0 = No collision

#### In Receive mode (Master or Slave modes):

This is a "don't care" bit

#### bit 6 SSPOV: Receive Overflow Indicator bit

#### In Receive mode:

- 1 = A byte is received while the SSPBUF register is still holding the previous byte (must be cleared in software)

- 0 = No overflow

#### In Transmit mode:

This is a "don't care" bit in Transmit mode

- bit 5 SSPEN: Synchronous Serial Port Enable bit

- 1 = Enables the serial port and configures the SDA and SCL pins as the serial port pins

- 0 = Disables serial port and configures these pins as I/O port pins

**Note:** When enabled, the SDA and SCL pins must be properly configured as input or output.

#### bit 4 **CKP:** SCK Release Control bit

#### In Slave mode:

- 1 = Release clock

- 0 = Holds clock low (clock stretch), used to ensure data setup time

#### In Master mode:

Unused in this mode

#### bit 3-0 SSPM3:SSPM0: Synchronous Serial Port Mode Select bits

- $1111 = I^2C$  Slave mode, 10-bit address with START and STOP bit interrupts enabled

- $1110 = I^2C$  Slave mode, 7-bit address with START and STOP bit interrupts enabled

- 1011 = I<sup>2</sup>C Firmware Controlled Master mode (Slave IDLE)

- $1000 = I^2C$  Master mode, clock = Fosc / (4 \* (SSPADD+1))

- $0111 = I^2C$  Slave mode, 10-bit address

- $0110 = I^2C$  Slave mode, 7-bit address

**Note:** Bit combinations not specifically listed here are either reserved, or implemented in SPI mode only.

| Legend:            |                  |                       |                    |

|--------------------|------------------|-----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### 16.4.14 SLEEP OPERATION

While in SLEEP mode, the I<sup>2</sup>C module can receive addresses or data, and when an address match or complete byte transfer occurs, wake the processor from SLEEP (if the MSSP interrupt is enabled).

#### 16.4.15 EFFECT OF A RESET

A RESET disables the MSSP module and terminates the current transfer.

#### 16.4.16 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the START and STOP conditions allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a RESET, or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit (SSPSTAT<4>) is set, or the bus is IDLE, with both the S and P bits clear. When the bus is busy, enabling the SSP interrupt will generate the interrupt when the STOP condition occurs.

In multi-master operation, the SDA line must be monitored for arbitration, to see if the signal level is the expected output level. This check is performed in hardware, with the result placed in the BCLIF bit.

The states where arbitration can be lost are:

- · Address Transfer

- Data Transfer

- A START Condition

- · A Repeated START Condition

- An Acknowledge Condition

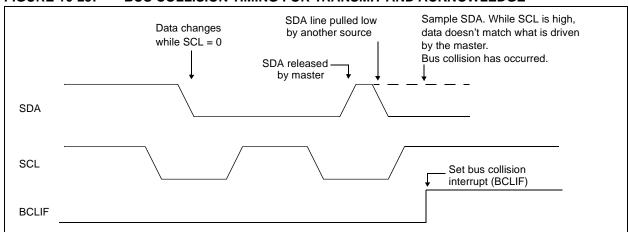

#### 16.4.17 MULTI -MASTER COMMUNICATION, BUS COLLISION, AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA, by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin = '0', then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag BCLIF and reset the I<sup>2</sup>C port to its IDLE state (Figure 16-25).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are de-asserted, and the SSPBUF can be written to. When the user services the bus collision Interrupt Service Routine, and if the  $\rm I^2C$  bus is free, the user can resume communication by asserting a START condition.

If a START, Repeated START, STOP, or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are de-asserted, and the respective control bits in the SSPCON2 register are cleared. When the user services the bus collision Interrupt Service Routine, and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a START condition.

The master will continue to monitor the SDA and SCL pins. If a STOP condition occurs, the SSPIF bit will be set.

A write to the SSPBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of START and STOP conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPSTAT register, or the bus is IDLE and the S and P bits are cleared.

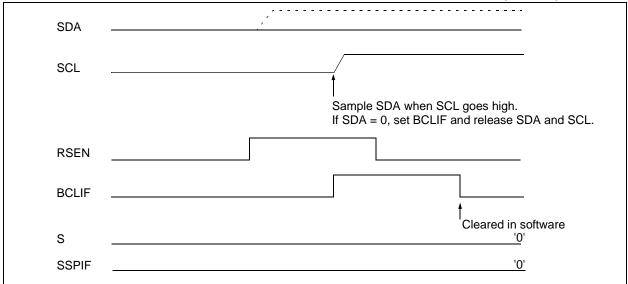

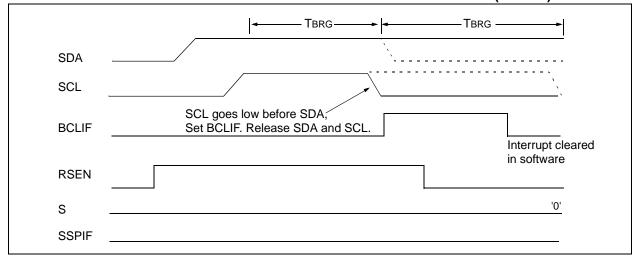

## 16.4.17.2 Bus Collision During a Repeated START Condition

During a Repeated START condition, a bus collision occurs if:

- A low level is sampled on SDA when SCL goes from low level to high level.

- SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user de-asserts SDA and the pin is allowed to float high, the BRG is loaded with SSPADD<6:0> and counts down to '0'. The SCL pin is then de-asserted, and when sampled high, the SDA pin is sampled.

If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 16-29). If SDA is sampled high, the BRG is

reloaded and begins counting. If SDA goes from high to low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high to low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated START condition, see Figure 16-30.

If, at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated START condition is complete.

FIGURE 16-29: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

FIGURE 16-30: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

#### REGISTER 20-11: DEVID1: DEVICE ID REGISTER 1 FOR PIC18FXX39 (BYTE ADDRESS 3FFFFEh)

| R     | R    | R    | R    | R    | R    | R    | R     |

|-------|------|------|------|------|------|------|-------|

| DEV2  | DEV1 | DEV0 | REV4 | REV3 | REV2 | REV1 | REV0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

bit 7-5 **DEV2:DEV0:** Device ID bits

000 = PIC18F2539

001 = PIC18F4539

100 = PIC18F2439

101 = PIC18F4439

bit 4-0 REV4:REV0: Revision ID bits

These bits are used to indicate the device revision.

Legend:

R = Readable bit P = Programmable bit U = Unimplemented bit, read as '0'

- n = Value when device is unprogrammed u = Unchanged from programmed state

#### REGISTER 20-12: DEVID2: DEVICE ID REGISTER 2 FOR PIC18FXX39 (BYTE ADDRESS 3FFFFFh)

| R     | R    | R    | R    | R    | R    | R    | R     |

|-------|------|------|------|------|------|------|-------|

| DEV10 | DEV9 | DEV8 | DEV7 | DEV6 | DEV5 | DEV4 | DEV3  |

| bit 7 |      |      |      |      |      |      | bit 0 |

#### bit 7-0 **DEV10:DEV3:** Device ID bits

These bits are used with the DEV2:DEV0 bits in the Device ID Register 1 to identify the part number.

Legend:

R = Readable bit P = Programmable bit U = Unimplemented bit, read as '0'

- n = Value when device is unprogrammed u = Unchanged from programmed state

TABLE 21-2: PIC18FXXX INSTRUCTION SET

| Mnemo     | nic,          | Description                              | Cycles     | 16-  | Bit Instru | uction W | ord  | Status          | Notes      |

|-----------|---------------|------------------------------------------|------------|------|------------|----------|------|-----------------|------------|

| Operai    | nds           | Description                              | Cycles     | MSb  |            |          | LSb  | Affected        | Notes      |

| BYTE-ORIE | NTED F        | ILE REGISTER OPERATIONS                  |            |      |            |          |      |                 |            |

| ADDWF     | f, d, a       | Add WREG and f                           | 1          | 0010 | 01da0      | ffff     | ffff | C, DC, Z, OV, N | 1, 2       |

| ADDWFC    | f, d, a       | Add WREG and Carry bit to f              | 1          | 0010 | 0da        | ffff     | ffff | C, DC, Z, OV, N | 1, 2       |

| ANDWF     | f, d, a       | AND WREG with f                          | 1          | 0001 | 01da       | ffff     | ffff | Z, N            | 1,2        |

| CLRF      | f, a          | Clear f                                  | 1          | 0110 | 101a       | ffff     | ffff | Z               | 2          |

| COMF      | f, d, a       | Complement f                             | 1          | 0001 | 11da       | ffff     | ffff | Z, N            | 1, 2       |

| CPFSEQ    | f, a          | Compare f with WREG, skip =              | 1 (2 or 3) | 0110 | 001a       | ffff     | ffff | None            | 4          |

| CPFSGT    | f, a          | Compare f with WREG, skip >              | 1 (2 or 3) | 0110 | 010a       | ffff     | ffff | None            | 4          |

| CPFSLT    | f, a          | Compare f with WREG, skip <              | 1 (2 or 3) | 0110 | 000a       | ffff     | ffff | None            | 1, 2       |

| DECF      | f, d, a       | Decrement f                              | 1          | 0000 | 01da       | ffff     | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| DECFSZ    | f, d, a       | Decrement f, Skip if 0                   | 1 (2 or 3) | 0010 | 11da       | ffff     | ffff | None            | 1, 2, 3, 4 |

| DCFSNZ    | f, d, a       | Decrement f, Skip if Not 0               | 1 (2 or 3) | 0100 | 11da       | ffff     | ffff | None            | 1, 2       |

| INCF      | f, d, a       | Increment f                              | 1          | 0010 | 10da       | ffff     | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| INCFSZ    | f, d, a       | Increment f, Skip if 0                   | 1 (2 or 3) | 0011 | 11da       | ffff     | ffff | None            | 4          |

| INFSNZ    | f, d, a       | Increment f, Skip if Not 0               | 1 (2 or 3) | 0100 | 10da       | ffff     | ffff | None            | 1, 2       |

| IORWF     | f, d, a       | Inclusive OR WREG with f                 | 1          | 0001 | 00da       | ffff     | ffff | Z, N            | 1, 2       |

| MOVF      | f, d, a       | Move f                                   | 1          | 0101 | 00da       | ffff     | ffff | Z, N            | 1          |

| MOVFF     | $f_s$ , $f_d$ | Move f <sub>s</sub> (source) to 1st word | 2          | 1100 | ffff       | ffff     | ffff | None            |            |

|           | 0 0           | f <sub>d</sub> (destination) 2nd word    |            | 1111 | ffff       | ffff     | ffff |                 |            |

| MOVWF     | f, a          | Move WREG to f                           | 1          | 0110 | 111a       | ffff     | ffff | None            |            |

| MULWF     | f, a          | Multiply WREG with f                     | 1          | 0000 | 001a       | ffff     | ffff | None            |            |

| NEGF      | f, a          | Negate f                                 | 1          | 0110 | 110a       | ffff     | ffff | C, DC, Z, OV, N | 1, 2       |

| RLCF      | f, d, a       | Rotate Left f through Carry              | 1          | 0011 | 01da       | ffff     | ffff | C, Z, N         |            |

| RLNCF     | f, d, a       | Rotate Left f (No Carry)                 | 1          | 0100 | 01da       | ffff     | ffff | Z, N            | 1, 2       |

| RRCF      | f, d, a       | Rotate Right f through Carry             | 1          | 0011 | 00da       | ffff     | ffff | C, Z, N         |            |

| RRNCF     | f, d, a       | Rotate Right f (No Carry)                | 1          | 0100 | 00da       | ffff     | ffff | Z, N            |            |

| SETF      | f, a          | Set f                                    | 1          | 0110 | 100a       | ffff     | ffff | None            |            |

| SUBFWB    | f, d, a       | Subtract f from WREG with borrow         | 1          | 0101 | 01da       | ffff     | ffff | C, DC, Z, OV, N | 1, 2       |

| SUBWF     | f, d, a       | Subtract WREG from f                     | 1          | 0101 | 11da       | ffff     | ffff | C, DC, Z, OV, N |            |

| SUBWFB    | f, d, a       | Subtract WREG from f with borrow         | 1          | 0101 | 10da       | ffff     | ffff | C, DC, Z, OV, N | 1, 2       |

| SWAPF     | f, d, a       | Swap nibbles in f                        | 1          | 0011 | 10da       | ffff     | ffff | None            | 4          |

| TSTFSZ    | f, a          | Test f, skip if 0                        | 1 (2 or 3) | 0110 | 011a       | ffff     | ffff | None            | 1, 2       |

| XORWF     | f, d, a       | Exclusive OR WREG with f                 | 1          | 0001 | 10da       | ffff     | ffff | Z, N            | '          |

| BIT-ORIEN | TED FIL       | E REGISTER OPERATIONS                    |            |      |            |          |      | l               | L          |

| BCF       | f, b, a       | Bit Clear f                              | 1          | 1001 | bbba       | ffff     | ffff | None            | 1, 2       |

| BSF       | f, b, a       | Bit Set f                                | 1          | 1000 | bbba       | ffff     | ffff | None            | 1, 2       |

| BTFSC     | f, b, a       | Bit Test f, Skip if Clear                | 1 (2 or 3) | 1011 | bbba       | ffff     | ffff | None            | 3, 4       |

| BTFSS     | f, b, a       | Bit Test f, Skip if Set                  | 1 (2 or 3) | 1010 | bbba       | ffff     | ffff | None            | 3, 4       |

| BTG       | f, d, a       | Bit Toggle f                             | 1          | 0111 | bbba       | ffff     | ffff | None            | 1, 2       |

| -         | ,,            | JJ -                                     | <u> </u>   |      |            |          |      | 1               | ,          |

Note 1: When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

<sup>2:</sup> If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned.

<sup>3:</sup> If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

**<sup>4:</sup>** Some instructions are 2-word instructions. The second word of these instructions will be executed as a NOP, unless the first word of the instruction retrieves the information embedded in these 16-bits. This ensures that all program memory locations have a valid instruction.

<sup>5:</sup> If the Table Write starts the write cycle to internal memory, the write will continue until terminated.

**FIGURE 23-9:** TIMERO AND TIMER1 EXTERNAL CLOCK TIMINGS T0CKI T13CKI TMR0 or TMR1 Note: Refer to Figure 23-4 for load conditions.

**TABLE 23-8:** TIMERO AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Symbol    |                           | Characteristic     |                          | Min                                          | Max    | Units | Conditions                               |

|--------------|-----------|---------------------------|--------------------|--------------------------|----------------------------------------------|--------|-------|------------------------------------------|

| 40           | Tt0H      | T0CKI High Pu             | lse Width          | No Prescaler             | 0.5Tcy + 20                                  | _      | ns    |                                          |

|              |           |                           |                    | With Prescaler           | 10                                           | _      | ns    |                                          |

| 41           | Tt0L      | T0CKI Low Pul             | se Width           | No Prescaler             | 0.5Tcy + 20                                  | _      | ns    |                                          |

|              |           |                           |                    | With Prescaler           | 10                                           | _      | ns    |                                          |

| 42           | Tt0P      | T0CKI Period              |                    | No Prescaler             | Tcy + 10                                     | _      | ns    |                                          |

|              |           |                           |                    | With Prescaler           | Greater of:<br>20 ns or <u>TCY + 40</u><br>N | _      | ns    | N = prescale<br>value<br>(1, 2, 4,, 256) |

| 45           | Tt1H      | T13CKI High               | Synchronous, no    | prescaler                | 0.5Tcy + 20                                  | _      | ns    |                                          |

|              |           | Time                      | Synchronous,       | PIC18FXXXX               | 10                                           | _      | ns    |                                          |

|              |           |                           | with prescaler     | PIC18 <b>LF</b> XXXX     | 25                                           | _      | ns    |                                          |

|              |           |                           | Asynchronous       | PIC18FXXXX               | 30                                           | _      | ns    |                                          |

|              |           |                           |                    | PIC18 <b>LF</b> XXXX     | 50                                           | _      | ns    |                                          |

| 46           | Tt1L      | T13CKI Low                | Synchronous, no    | prescaler                | 0.5Tcy + 5                                   | _      | ns    |                                          |

|              |           | Time                      | Synchronous,       | PIC18FXXXX               | 10                                           | _      | ns    |                                          |

|              |           |                           | with prescaler     | PIC18 <b>LF</b> XXXX     | 25                                           | _      | ns    |                                          |

|              |           |                           | Asynchronous       | PIC18FXXXX               | 30                                           | _      | ns    |                                          |

|              |           |                           |                    | PIC18 <b>LF</b> XXXX     | 50                                           | _      | ns    |                                          |

| 47           | Tt1P      | T13CKI input period       | Synchronous        |                          | Greater of:<br>20 ns or <u>Tcy + 40</u><br>N | _      | ns    | N = prescale<br>value<br>(1, 2, 4, 8)    |

|              |           |                           | Asynchronous       |                          | 60                                           | _      | ns    |                                          |

|              | Ft1       | T13CKI oscillat           | or input frequency | or input frequency range |                                              | 50     | kHz   |                                          |

| 48           | Tcke2tmrl | Delay from exterincrement | ernal T13CKI clock | edge to timer            | 2 Tosc                                       | 7 Tosc |       |                                          |

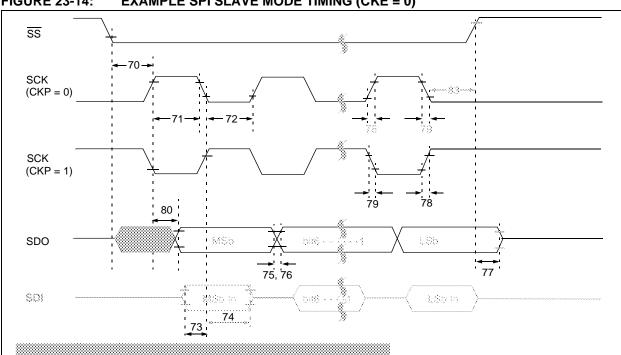

FIGURE 23-14: **EXAMPLE SPI SLAVE MODE TIMING (CKE = 0)**

TABLE 23-13: EXAMPLE SPI MODE REQUIREMENTS (SLAVE MODE TIMING (CKE = 0))

| Param. No. | Symbol                | Characteristic                               |                                    | Min           | Max | Units | Conditions |

|------------|-----------------------|----------------------------------------------|------------------------------------|---------------|-----|-------|------------|

| 70         | TssL2scH,<br>TssL2scL | SS↓ to SCK↓ or SCK↑ input                    |                                    | Tcy           | _   | ns    |            |

| 71         | TscH                  | SCK input high time (Slave mode)             | Continuous                         | 1.25 Tcy + 30 | _   | ns    |            |

| 71A        |                       |                                              | Single Byte                        | 40            | _   | ns    | (Note 1)   |

| 72         | TscL                  | SCK input low time (Slave mode)              | Continuous                         | 1.25 Tcy + 30 | _   | ns    |            |

| 72A        |                       |                                              | Single Byte                        | 40            | _   | ns    | (Note 1)   |

| 73         | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to SCK ed       | 1 , ,                              |               | _   | ns    |            |

| 73A        | Тв2в                  | Last clock edge of Byte 1 to the first clock | k edge of Byte 2                   | 1.5 Tcy + 40  | _   | ns    | (Note 2)   |

| 74         | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edg       | time of SDI data input to SCK edge |               |     | ns    |            |

| 75         | TdoR                  | SDO data output rise time                    | PIC18FXXXX                         | _             | 25  | ns    |            |

|            |                       |                                              | PIC18 <b>LF</b> XXXX               | _             | 60  | ns    | VDD = 2V   |

| 76         | TdoF                  | SDO data output fall time                    | PIC18FXXXX                         | _             | 25  | ns    |            |

|            |                       |                                              | PIC18 <b>LF</b> XXXX               | _             | 60  | ns    | VDD = 2V   |

| 77         | TssH2doZ              | SS↑ to SDO output hi-impedance               |                                    | 10            | 50  | ns    |            |

| 78         | TscR                  | SCK output rise time (Master mode)           | PIC18FXXXX                         | _             | 25  | ns    |            |

|            |                       |                                              | PIC18LFXXXX                        | _             | 60  | ns    | VDD = 2V   |

| 79         | TscF                  | SCK output fall time (Master mode)           | PIC18FXXXX                         | _             | 25  | ns    |            |

|            |                       |                                              | PIC18 <b>LF</b> XXXX               | _             | 60  | ns    | VDD = 2V   |

| 80         | TscH2doV,             | SDO data output valid after SCK edge         | PIC18FXXXX                         | _             | 50  | ns    |            |

|            | TscL2doV              |                                              | PIC18LFXXXX                        | _             | 150 | ns    | VDD = 2V   |

| 83         | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK edge                          | <u> </u>                           | 1.5 Tcy + 40  | _   | ns    |            |

Note 1: Requires the use of Parameter # 73A.

2: Only if Parameter # 71A and # 72A are used.

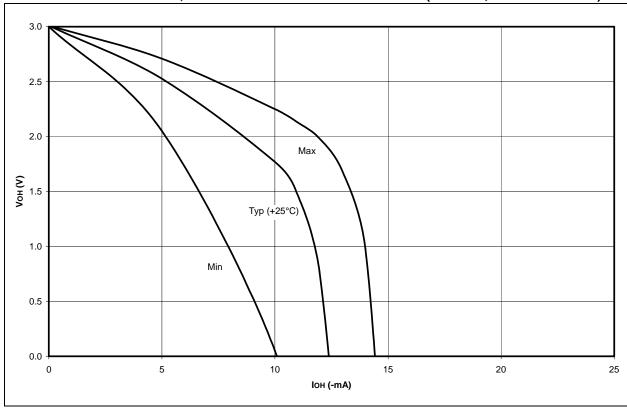

FIGURE 24-13: TYPICAL, MINIMUM AND MAXIMUM Voh vs. Ioh (VDD = 3V, -40°C TO +125°C)

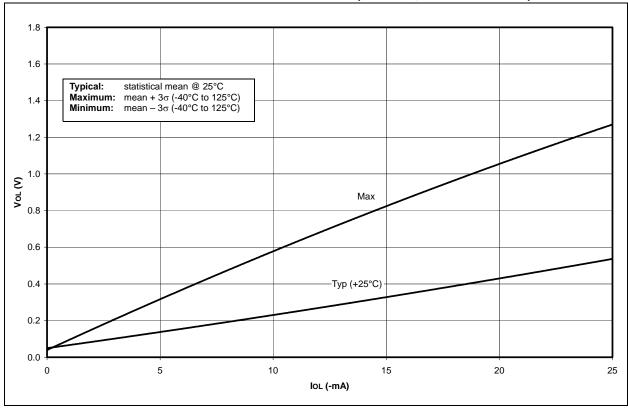

FIGURE 24-14: TYPICAL AND MAXIMUM Vol vs. Iol (VDD = 5V, -40°C TO +125°C)

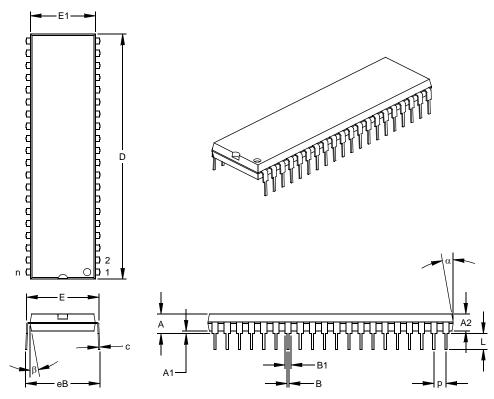

#### 40-Lead Plastic Dual In-line (P) - 600 mil (PDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units    |       | INCHES* |       | MILLIMETERS |       |       |

|----------------------------|----------|-------|---------|-------|-------------|-------|-------|

| Dimensio                   | n Limits | MIN   | NOM     | MAX   | MIN         | NOM   | MAX   |

| Number of Pins             | n        |       | 40      |       |             | 40    |       |

| Pitch                      | р        |       | .100    |       |             | 2.54  |       |

| Top to Seating Plane       | Α        | .160  | .175    | .190  | 4.06        | 4.45  | 4.83  |

| Molded Package Thickness   | A2       | .140  | .150    | .160  | 3.56        | 3.81  | 4.06  |

| Base to Seating Plane      | A1       | .015  |         |       | 0.38        |       |       |

| Shoulder to Shoulder Width | Е        | .595  | .600    | .625  | 15.11       | 15.24 | 15.88 |

| Molded Package Width       | E1       | .530  | .545    | .560  | 13.46       | 13.84 | 14.22 |

| Overall Length             | D        | 2.045 | 2.058   | 2.065 | 51.94       | 52.26 | 52.45 |

| Tip to Seating Plane       | L        | .120  | .130    | .135  | 3.05        | 3.30  | 3.43  |

| Lead Thickness             | С        | .008  | .012    | .015  | 0.20        | 0.29  | 0.38  |

| Upper Lead Width           | B1       | .030  | .050    | .070  | 0.76        | 1.27  | 1.78  |

| Lower Lead Width           | В        | .014  | .018    | .022  | 0.36        | 0.46  | 0.56  |

| Overall Row Spacing §      | eВ       | .620  | .650    | .680  | 15.75       | 16.51 | 17.27 |

| Mold Draft Angle Top       | α        | 5     | 10      | 15    | 5           | 10    | 15    |

| Mold Draft Angle Bottom    | β        | 5     | 10      | 15    | 5           | 10    | 15    |

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side.

JEDEC Equivalent: MO-011

Drawing No. C04-016

<sup>\*</sup> Controlling Parameter § Significant Characteristic

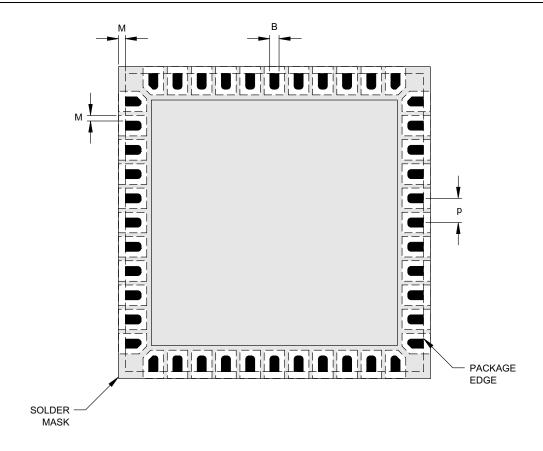

# 44-Lead Quad Flat No Lead Package (ML) 8x8 mm Body (QFN) Land Pattern and Solder Mask

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                    | Units            |      | INCHES   |      | MILLIMETERS* |          |      |

|--------------------|------------------|------|----------|------|--------------|----------|------|

|                    | Dimension Limits | MIN  | NOM      | MAX  | MIN          | NOM      | MAX  |

| Pitch              | р                |      | .026 BSC |      |              | 0.65 BSC |      |

| Pad Width          | В                |      |          |      |              |          |      |

| Pad Length         | L                |      |          |      |              |          |      |

| Pad to Solder Mask | M                | .005 |          | .006 | 0.13         |          | 0.15 |

<sup>\*</sup>Controlling Parameter

Drawing No. C04-2103

| PIC18F4X39 Pin Functions              | PORTA                                    |

|---------------------------------------|------------------------------------------|

| MCLR/VPP14                            | Associated Registers8                    |

| OSC1/CLKI14                           |                                          |

| OSC2/CLKO/RA614                       |                                          |

| PWM116                                | 3                                        |

| PWM2                                  |                                          |

| RA0/AN0                               |                                          |

|                                       |                                          |

| RA1/AN114                             | <u> </u>                                 |

| RA2/AN2/VREF14                        | 3                                        |

| RA3/AN3/VREF+14                       | RB0/INT Pin, External8                   |

| RA4/T0CKI14                           | RB7:RB4 Interrupt-on-Change Flag         |

| RA5/AN4/SS/LVDIN14                    | (RBIF Bit) 8                             |

| RB0/INT15                             |                                          |

| RB1/INT115                            | PORTC                                    |

| RB2/INT2                              |                                          |

| RB3                                   |                                          |

|                                       |                                          |

| RB4                                   | PORTC Register                           |

| RB5/PGM15                             |                                          |

| RB6/PGC15                             |                                          |

| RB7/PGD15                             | TRISC Register89, 16                     |

| RC0/T13CKI16                          | PORTD                                    |

| RC3/SCK/SCL16                         | Associated Registers9                    |

| RC4/SDI/SDA16                         |                                          |

| RC5/SDO                               | 3                                        |

| RC6/TX/CK                             | · · · · · · · · · · · · · · · · · · ·    |

| RC7/RX/DT16                           | 9                                        |

|                                       | •                                        |

| RD0/PSP0                              |                                          |

| RD1/PSP117                            |                                          |

| RD2/PSP217                            |                                          |

| RD3/PSP317                            | LATE Register9                           |

| RD4/PSP417                            |                                          |

| RD5/PSP517                            | PSP Mode Select (PSPMODE Bit)91, 9       |

| RD6/PSP617                            | <del></del>                              |

| RD7/PSP717                            |                                          |

| RE0/AN5/RD                            |                                          |

| RE1/AN6/WR                            |                                          |

| RE2/AN7/CS                            |                                          |

|                                       |                                          |

| VDD                                   | <b>5</b> \ ,                             |

| Vss18                                 |                                          |

| PIC18FXX39 Voltage-Frequency Graph    | Switching Between Timer0 and WDT 10      |

| (Industrial)260                       |                                          |

| PIC18LFXX39 Voltage-Frequency Graph   | Power-on Reset (POR)2                    |

| (Industrial)260                       |                                          |

| PICDEM 1 Low Cost PIC MCU             | Power-up Timer (PWRT)2                   |

| Demonstration Board255                | Prescaler, Timer010                      |

| PICDEM 17 Demonstration Board         | Assignment (PSA Bit)                     |

|                                       |                                          |

| PICDEM 2 Low Cost PIC16CXX            | Rate Select (T0PS2:T0PS0 Bits)           |

| Demonstration Board255                |                                          |

| PICDEM 3 Low Cost PIC16CXXX           | Prescaler, Timer2 12                     |

| Demonstration Board256                | PRO MATE II Universal Device Programmer  |

| PICSTART Plus Entry Level Development | Product Identification System31          |

| Programmer                            | Program Counter                          |

| PIE Registers76–77                    | · ·                                      |

| Pinout I/O Descriptions               | PCLATH Register                          |

| PIC18F2X3911                          | PCLATU Register                          |

| PIC18F4X39                            | _                                        |

|                                       | 3 ,                                      |

| PIR Registers                         | Interrupt Vector                         |

| PLL Lock Time-out24                   | ·                                        |

| Pointer, FSR47                        |                                          |

| POP240                                | Program Verification and Code Protection |

| POR. See Power-on Reset               | Associated Registers                     |

|                                       | Configuration Register21                 |

|                                       | Data EEPROM21                            |

|                                       | Program Memory                           |

|                                       |                                          |

| Programming, Device Instructions211 PSP.See Parallel Slave Port. | TXSTA (Transmit Status and Control)          |     |

|------------------------------------------------------------------|----------------------------------------------|-----|

| Pulse Width Modulation (PWM)123                                  | RESET23,                                     |     |

| Pulse Width Modulation. See PWM.                                 | Brown-out Reset (BOR)                        |     |

| PUSH240                                                          | MCLR Reset (During SLEEP)                    |     |

| PWM                                                              | MCLR Reset (Normal Operation)                |     |

| Associated Registers124                                          | Oscillator Start-up Timer (OST)              |     |

| CCPR1H:CCPR1L Registers                                          | Power-on Reset (POR)                         |     |

| Duty Cycle                                                       | Power-up Timer (PWRT)                        |     |

| • •                                                              |                                              |     |

| Period                                                           | Programmable Brown-out Reset (BOR)           |     |

| TMR2 to PR2 Match123                                             | RESET Instruction                            |     |

| Q                                                                | Stack Full Reset                             |     |

| Q Clock                                                          | Stack Underflow Reset                        |     |

| Q Clock124                                                       | Watchdog Timer (WDT) Reset                   |     |

| R                                                                | RETFIE                                       |     |

| RAM. See Data Memory                                             | RETLW                                        |     |

| RCALL241                                                         | RETURN                                       |     |

| RCSTA Register                                                   | Return Address Stack                         |     |

| SPEN Bit                                                         | Associated Registers                         |     |

|                                                                  | Pointer (STKPTR)                             |     |

| Register File                                                    | Top-of-Stack Access                          |     |

| Registers ADCONO (A/D Control 0)                                 | Revision History                             |     |

| ADCON0 (A/D Control 0)                                           | RLCF                                         |     |

| ADCON1 (A/D Control 1)                                           | RLNCF                                        |     |

| CCP1CON and CCP2CON (PWM Control)                                | RRCF                                         |     |

| CONFIG1H (Configuration 1 High)196                               | RRNCF                                        | 245 |

| CONFIG2H (Configuration 2 High)197                               | S                                            |     |

| CONFIG2L (Configuration 2 Low)197                                | 3                                            |     |

| CONFIG4L (Configuration 4 Low)198                                | SCI. See USART                               |     |

| CONFIG5H (Configuration 5 High)199                               | SCK                                          | 125 |

| CONFIG5L (Configuration 5 Low)199                                | SDI                                          | 125 |

| CONFIG6H (Configuration 6 High)200                               | SDO                                          | 125 |

| CONFIG6L (Configuration 6 Low)200                                | Serial Clock, SCK                            | 125 |

| CONFIG7H (Configuration 7 High)201                               | Serial Communication Interface. See USART    |     |

| CONFIG7L (Configuration 7 Low)201                                | Serial Data In, SDI                          | 125 |

| DEVID1 (Device ID 1)202                                          | Serial Data Out, SDO                         |     |

| DEVID2 (Device ID 2)202                                          | Serial Peripheral Interface. See SPI Mode    |     |

| EECON1 (Data EEPROM Control 1)53, 62                             | SETF                                         | 245 |

| File Summary43–45                                                | Single Phase Induction Motor Control Module. |     |

| INTCON (Interrupt Control)71                                     | See Motor Control.                           | 113 |

| INTCON2 (Interrupt Control 2)72                                  | Slave Select Synchronization                 |     |

| INTCON3 (Interrupt Control 3)73                                  | Slave Select, SS                             |     |

| IPR1 (Peripheral Interrupt Priority 1)78                         | SLEEP195,                                    |     |

| IPR2 (Peripheral Interrupt Priority 2)79                         | Software Simulator (MPLAB SIM)               |     |

| LVDCON (LVD Control)191                                          | Special Features of the CPU                  |     |

| PIE1 (Peripheral Interrupt Enable 1)76                           | Configuration Registers                      |     |

| PIE2 (Peripheral Interrupt Enable 2)77                           | Special Function Registers                   |     |

| PIR1 (Peripheral Interrupt Request 1)74                          | •                                            |     |

| PIR2 (Peripheral Interrupt Request 2)                            | Map                                          | 42  |

| ,                                                                | SPI Mode                                     | 400 |

| RCON (Register Control)80                                        | Associated Registers                         |     |

| RCON (RESET Control)                                             | Bus Mode Compatibility                       |     |

| RCSTA (Receive Status and Control)                               | Effects of a RESET                           |     |

| SSPCON1 (MSSP Control 1)                                         | Master Mode                                  |     |

| SPI Mode                                                         | Master/Slave Connection                      |     |

| SSPCON1 (MSSP Control 1), I <sup>2</sup> C Mode                  | Overview                                     |     |

| SSPCON2 (MSSP Control 2), I <sup>2</sup> C Mode137               | Serial Clock                                 |     |

| SSPSTAT (MSSP Status)                                            | Serial Data In                               |     |

| SPI Mode                                                         | Serial Data Out                              |     |

| SSPSTAT (MSSP Status), I <sup>2</sup> C Mode135                  | Slave Mode                                   |     |

| STATUS49                                                         | Slave Select                                 | 125 |

| STKPTR (Stack Pointer)35                                         | Slave Select Synchronization                 |     |

| T0CON (Timer0 Control)99                                         | Slave Synch Timing                           | 131 |

| T1CON (Timer 1 Control)103                                       | SLEEP Operation                              |     |

| T2CON (Timer2 Control)107                                        | SPI Clock                                    | 130 |

| T3CON (Timer3 Control)109                                        | SS                                           | 125 |

| TRISE94                                                          | SSPOV Status Flag                            | 155 |

|                                                                  | -                                            |     |

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O, Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA and Z-Scale are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip Technology Germany II GmbH & Co. & KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2002-2013, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 9781620769362

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.