Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 32                                                                        |

| Program Memory Size        | 24KB (12K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 1408 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-TQFP                                                                   |

| Supplier Device Package    | 44-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4539-i-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.13 STATUS Register

The STATUS register, shown in Register 4-2, contains the arithmetic status of the ALU. The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC, C, OV, or N bits, then the write to these five bits is disabled. These bits are set or cleared according to the device logic. Therefore, the result of an instruction with the STATUS register as destination may be different than intended. For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF, MOVFF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C, DC, OV, or N bits from the STATUS register. For other instructions not affecting any status bits, see Table 21-2.

| Note: | The C and DC bits operate as a borrow and      |

|-------|------------------------------------------------|

|       | digit borrow bit respectively, in subtraction. |

#### REGISTER 4-2: STATUS REGISTER

| U-0   | U-0 | U-0 | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|-------|-----|-----|-------|-------|-------|-------|-------|

| _     | —   | —   | N     | OV    | Z     | DC    | С     |

| bit 7 |     |     |       |       |       |       | bit 0 |

| bit 7-5 | Unimpler                | mented: Read as                   | s '0'                                                |                                                                                                                                     |

|---------|-------------------------|-----------------------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | negative (<br>1 = Resul |                                   | arithmetic (2's compl                                | ement). It indicates whether the result was                                                                                         |

| bit 3   | 7-bit mag<br>1 = Overf  | used for signed nitude, which cau | uses the sign bit (bit 7                             | ement). It indicates an overflow of the<br>7) to change state.<br>this arithmetic operation)                                        |

| bit 2   | Z: Zero bi              | it                                |                                                      |                                                                                                                                     |

|         |                         |                                   | netic or logic operation<br>netic or logic operation |                                                                                                                                     |

| bit 1   |                         | carry/borrow bit                  | BLW, and SUBWF instr                                 | uctions                                                                                                                             |

|         |                         |                                   | th low order bit of the                              |                                                                                                                                     |

|         |                         |                                   | 4th low order bit of th                              |                                                                                                                                     |

|         | Note:                   | complement of                     | · ·                                                  | A subtraction is executed by adding the two's<br>For rotate (RRF, RLF) instructions, this bit is<br>f the source register.          |

| bit 0   | C: Carry/               | borrow bit                        |                                                      |                                                                                                                                     |

|         | For ADDW                | F, ADDLW, SU                      | BLW, and SUBWF instru                                | ictions                                                                                                                             |

|         |                         |                                   | lost Significant bit of t<br>Most Significant bit of |                                                                                                                                     |

|         | Note:                   | complement of                     | the second operand.                                  | A subtraction is executed by adding the two's<br>For rotate (RRF, RLF) instructions, this bit is<br>der bit of the source register. |

|         | Legend:                 |                                   |                                                      |                                                                                                                                     |

|         | R = Read                | able bit                          | W = Writable bit                                     | U = Unimplemented bit, read as '0'                                                                                                  |

|         |                         |                                   |                                                      | •                                                                                                                                   |

- n = Value at POR

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

#### 6.3 Reading the Data EEPROM Memory

To read a data memory location, the user must write the address to the EEADR register, clear the EEPGD control bit (EECON1<7>), clear the CFGS control bit

EXAMPLE 6-1: DATA EEPROM READ

| MOVLW | DATA_EE_ADDR  | ;                                            |

|-------|---------------|----------------------------------------------|

| MOVWF | EEADR         | ; Data Memory Address to read                |

| BCF   | EECON1, EEPGD | ; Point to DATA memory                       |

| BCF   | EECON1, CFGS  | ; Access program FLASH or Data EEPROM memory |

| BSF   | EECON1, RD    | ; EEPROM Read                                |

| MOVF  | EEDATA, W     | ; W = EEDATA                                 |

|       |               |                                              |

#### 6.4 Writing to the Data EEPROM Memory

To write an EEPROM data location, the address must first be written to the EEADR register and the data written to the EEDATA register. Then, the sequence in Example 6-2 must be followed to initiate the write cycle.

The write will not initiate if the above sequence is not exactly followed (write 55h to EECON2, write AAh to EECON2, then set WR bit) for each byte. It is strongly recommended that interrupts be disabled during this code segment.

Additionally, the WREN bit in EECON1 must be set to enable writes. This mechanism prevents accidental writes to data EEPROM due to unexpected code exe-

| cution (i.e., runaway programs). The WREN bit should |

|------------------------------------------------------|

| be kept clear at all times, except when updating the |

| EEPROM. The WREN bit is not cleared by hardware.     |

(EECON1<6>), and then set control bit RD

(EECON1<0>). The data is available for the very next

instruction cycle; therefore, the EEDATA register can

be read by the next instruction. EEDATA will hold this

value until another read operation, or until it is written to

by the user (during a write operation).

After a write sequence has been initiated, EECON1, EEADR and EDATA cannot be modified. The WR bit will be inhibited from being set unless the WREN bit is set. The WREN bit must be set on a previous instruction. Both WR and WREN cannot be set with the same instruction.

At the completion of the write cycle, the WR bit is cleared in hardware and the EEPROM Write Complete Interrupt Flag bit (EEIF) is set. The user may either enable this interrupt, or poll this bit. EEIF must be cleared by software.

|                      | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>BCF<br>BCF<br>BSF | EEADR<br>DATA_EE_DATA<br>EEDATA<br>EECON1, EEPGD<br>EECON1, CFGS<br>EECON1, WREN | ; Data Memory Value to write<br>; Point to DATA memory<br>; Access program FLASH or Data EEPROM memory<br>; Enable writes |

|----------------------|-------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Required<br>Sequence |                                                       | INTCON, GIE<br>55h<br>EECON2<br>AAh                                              | ; Disable interrupts<br>;<br>; Write 55h<br>;                                                                             |

|                      | MOVWF<br>BSF<br>BSF                                   |                                                                                  | ; Write AAh<br>; Set WR bit to begin write<br>; Enable interrupts                                                         |

|                      | •<br>•                                                |                                                                                  | ; user code execution                                                                                                     |

|                      | •<br>BCF                                              | EECON1, WREN                                                                     | ; Disable writes on write complete (EEIF set)                                                                             |

EXAMPLE 6-2: DATA EEPROM WRITE

NOTES:

#### 15.1.2 PWM DUTY CYCLE

The PWM duty cycle is set by the Motor Control module when it writes a 10-bit value to the CCPR1L and CCP1CON registers, where CCPR1L contains the eight Most Significant bits and CCP1CON<5:4> contains the two Least Significant bits. The duty cycle time is given by the equation:

PWM duty cycle = (10-bit CCP register value) • Tosc • (TMR2 prescale value)

where Tosc and the duty cycle are in the same unit of time.

The CCPR1H register and a 2-bit internal latch are used to double-buffer the PWM duty cycle. This buffering is essential for glitchless PWM operation. At the same time, the value of TMR2 is concatenated with either an internal 2-bit Q clock, or 2 bits of the TMR2 prescaler. When the CCPR1H:latch pair value matches that of the TMR2:latch pair, the PWM1 pin is cleared.

The maximum PWM resolution (bits) for a given PWM frequency is given by the equation:

PWM Resolution (max) =

$$\frac{\log(\frac{FOSC}{FPWM})}{\log(2)}$$

bits

where FPWM is the PWM frequency, or (1/PWM period).

Note: If the PWM duty cycle value is longer than the PWM period, the PWM1 pin will not be cleared.

| Name                | Bit 7                | Bit 6        | Bit 5       | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>All Other<br>RESETS |

|---------------------|----------------------|--------------|-------------|--------|-------|--------|--------|--------|----------------------|---------------------------------|

| INTCON              | GIE/GIEH             | PEIE/GIEL    | TMR0IE      | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF   | 0000 000x            | 0000 000u                       |

| PIR1                | PSPIF <sup>(1)</sup> | ADIF         | RCIF        | TXIF   | SSPIF | —      | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| PIE1                | PSPIE <sup>(1)</sup> | ADIE         | RCIE        | TXIE   | SSPIE | —      | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| IPR1                | PSPIP <sup>(1)</sup> | ADIP         | RCIP        | TXIP   | SSPIP | _      | TMR2IP | TMR1IP | 0000 0000            | 0000 0000                       |

| TMR2 <sup>*</sup>   | *                    | *            | *           | *      | *     | *      | *      | *      | 0000 0000            | 0000 0000                       |

| PR2 <sup>*</sup>    | *                    | *            | *           | *      | *     | *      | *      | *      | 1111 1111            | 1111 1111                       |

| T2CON <sup>*</sup>  | *                    | *            | *           | *      | *     | *      | *      | *      | -000 0000            | -000 0000                       |

| CCPR1L <sup>*</sup> | *                    | *            | *           | *      | *     | *      | *      | *      | xxxx xxxx            | uuuu uuuu                       |

| CCPR1H              | PWM Reg              | ister1 (MSB) | (read-only) |        |       |        |        |        | xxxx xxxx            | uuuu uuuu                       |

| CCP1CON*            | —                    | _            | *           | *      | *     | *      | *      | *      | 00 0000              | 00 0000                         |

| CCPR2L <sup>*</sup> | *                    | *            | *           | *      | *     | *      | *      | *      | xxxx xxxx            | uuuu uuuu                       |

| CCPR2H <sup>*</sup> | PWM Reg              | ister2 (MSB) | (read-only) |        |       |        |        |        | xxxx xxxx            | uuuu uuuu                       |

| CCP2CON*            | —                    | _            | *           | *      | *     | *      | *      | *      | 00 0000              | 00 0000                         |

| L                   |                      | -            |             |        | 1 101 |        |        |        |                      |                                 |

#### TABLE 15-1: REGISTERS ASSOCIATED WITH PWM AND TIMER2

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0' unless otherwise noted. Shaded cells are not used by PWM and Timer2.

These registers are retained to maintain compatibility with PIC18FXX2 devices; however, the indicated bits are reserved in PIC18FXX39 devices. Users should not alter the values of these bits.

Note 1: The PSPIF, PSPIE and PSPIP bits are reserved on the PIC18F2X39 devices; always maintain these bits clear.

### REGISTER 16-3: SSPSTAT: MSSP STATUS REGISTER (I<sup>2</sup>C MODE)

|     | R/W-0                                                           | R/W-0                                              | R-0                       | R-0           | R-0          | R-0                          | R-0                 | R-0       |

|-----|-----------------------------------------------------------------|----------------------------------------------------|---------------------------|---------------|--------------|------------------------------|---------------------|-----------|

|     | SMP                                                             | CKE                                                | D/A                       | Р             | S            | R/W                          | UA                  | BF        |

|     | bit 7                                                           |                                                    |                           |               |              |                              |                     | bit       |

| t 7 | In Master of                                                    | v Rate Contr<br>or Slave mod                       | <u>de:</u>                | Standard Sn   | aad mode (1  | 00 kHz and                   | 1 M山⁊)              |           |

|     |                                                                 | rate control e                                     |                           |               |              |                              | 1 IVII I <i>Z</i> ) |           |

| t 6 | CKE: SME<br>In Master of                                        | Bus Select bi                                      | t<br><u>le:</u>           | 5             | ,            | ,                            |                     |           |

|     |                                                                 | e SMBus spe<br>e SMBus spe                         |                           |               |              |                              |                     |           |

| t 5 | —                                                               | Address bit                                        |                           |               |              |                              |                     |           |

|     |                                                                 | <u>ode:</u><br>es that the la<br>es that the la    |                           |               |              |                              |                     |           |

| t 4 |                                                                 | es that a ST<br>bit was not o                      | letected last             |               |              |                              |                     |           |

|     | Note:                                                           |                                                    | leared on RI              | ESET and w    | hen SSPEN    | is cleared.                  |                     |           |

| 3   |                                                                 | bit<br>es that a ST<br>ī bit was not               |                           |               | ed last      |                              |                     |           |

|     | Note:                                                           | This bit is c                                      | leared on RI              | ESET and w    | hen SSPEN    | is cleared.                  |                     |           |

| t 2 | <b>R/W</b> : Read<br>In <u>Slave m</u><br>1 = Read<br>0 = Write | d/Write bit Ini<br>ode:                            | formation (I <sup>2</sup> | C mode only   | y)           |                              |                     |           |

|     | Note:                                                           |                                                    |                           |               |              | e last addre:<br>bit, STOP b |                     |           |

|     |                                                                 | <u>mode:</u><br>nit is in progi<br>nit is not in p |                           |               |              |                              |                     |           |

|     | Note:                                                           | ORing this in IDLE mo                              |                           | , RSEN, PE    | N, RCEN, o   | r ACKEN wil                  | l indicate if t     | he MSSP i |

| 1   | 1 = Indicat                                                     | e Address (<br>es that the u<br>ss does not r      | ser needs to              | o update the  | address in t | he SSPADD                    | register            |           |

| 0   |                                                                 | Full Status k                                      |                           | puatoa        |              |                              |                     |           |

| U   | <u>In Transmi</u><br>1 = Receiv                                 |                                                    | SSPBUF is                 |               |              |                              |                     |           |

|     | <u>In Receive</u><br>1 = Data tr                                | <u>mode:</u><br>ansmit in pro                      | ogress (does              | s not include |              | d STOP bits<br>STOP bits),   |                     |           |

|     |                                                                 |                                                    | -                         |               |              |                              |                     |           |

|     | Legend:                                                         |                                                    |                           |               |              |                              |                     |           |

|     | R = Reada                                                       | ble bit                                            | W = Writab                | ole bit       | U = Unimp    | lemented bit                 | , read as '0'       |           |

|     | - n = Value                                                     | at POR                                             | '1' = Bit is :            | set           | '0' = Bit is | cleared                      | x = Bit is ur       | known     |

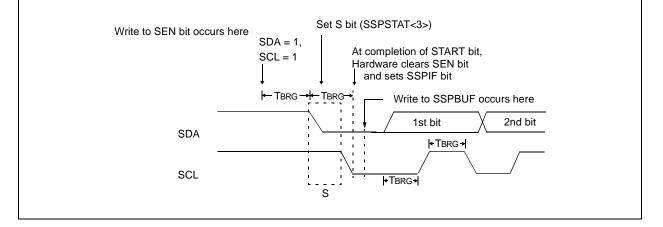

#### 16.4.8 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a START condition, the user sets the START condition enable bit, SEN (SSPCON2<0>). If the SDA and SCL pins are sampled high, the baud rate generator is reloaded with the contents of SSPADD<6:0> and starts its count. If SCL and SDA are both sampled high when the baud rate generator times out (TBRG), the SDA pin is driven low. The action of the SDA being driven low, while SCL is high, is the START condition and causes the S bit (SSPSTAT<3>) to be set. Following this, the baud rate generator is reloaded with the contents of SSPADD<6:0> and resumes its count. When the baud rate generator times out (TBRG), the SEN bit (SSPCON2<0>) will be automatically cleared by hardware, the baud rate generator is suspended, leaving the SDA line held low and the START condition is complete.

**Note:** If at the beginning of the START condition, the SDA and SCL pins are already sampled low, or if during the START condition the SCL line is sampled low before the SDA line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCLIF is set, the START condition is aborted, and the I<sup>2</sup>C module is reset into its IDLE state.

#### FIGURE 16-19: FIRST START BIT TIMING

#### 16.4.8.1 WCOL Status Flag

If the user writes the SSPBUF when a START sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing to the lower 5 bits of SSPCON2 is disabled until the START condition is complete.

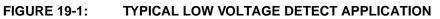

#### 19.0 LOW VOLTAGE DETECT

In many applications, the ability to determine if the device voltage (VDD) is below a specified voltage level is a desirable feature. A window of operation for the application can be created, where the application software can do "housekeeping tasks" before the device voltage exits the valid operating range. This can be done using the Low Voltage Detect module.

This module is a software programmable circuitry, where a device voltage trip point can be specified. When the voltage of the device becomes lower then the specified point, an interrupt flag is set. If the interrupt is enabled, the program execution will branch to the interrupt vector address and the software can then respond to that interrupt source. The Low Voltage Detect circuitry is completely under software control. This allows the circuitry to be "turned off" by the software, which minimizes the current consumption for the device.

Figure 19-1 shows a possible application voltage curve (typically for batteries). Over time, the device voltage decreases. When the device voltage equals voltage VA, the LVD logic generates an interrupt. This occurs at time TA. The application software then has the time, until the device voltage is no longer in valid operating range, to shutdown the system. Voltage point VB is the minimum valid operating voltage specification. This occurs at time TB. The difference TB – TA is the total time for shutdown.

The block diagram for the LVD module is shown in Figure 19-2. A comparator uses an internally generated reference voltage as the set point. When the selected tap output of the device voltage crosses the set point (is lower than), the LVDIF bit is set.

Each node in the resistor divider represents a "trip point" voltage. The "trip point" voltage is the minimum supply voltage level at which the device can operate before the LVD module asserts an interrupt. When the supply voltage is equal to the trip point, the voltage tapped off of the resistor array is equal to the 1.2V internal reference voltage generated by the voltage reference module. The comparator then generates an interrupt signal setting the LVDIF bit. This voltage is software programmable to any one of 16 values (see Figure 19-2). The trip point is selected by programming the LVDL3:LVDL0 bits (LVDCON<3:0>).

| 1ER 20-4. | CONFIG4L   | CONFIG                                                                                     | URATION      | REGISTER                                | (4LOW (B | TIEADD     | XE33 3000    | 0011)  |  |  |  |  |

|-----------|------------|--------------------------------------------------------------------------------------------|--------------|-----------------------------------------|----------|------------|--------------|--------|--|--|--|--|

|           | R/P-1      | U-0                                                                                        | U-0          | U-0                                     | U-0      | R/P-1      | U-0          | R/P-1  |  |  |  |  |

|           | DEBUG      | _                                                                                          | —            | —                                       |          | LVP        | —            | STVREN |  |  |  |  |

|           | bit 7      |                                                                                            |              |                                         |          |            |              | bit 0  |  |  |  |  |

| bit 7     | 1 = Backgr | ound Debu                                                                                  |              | nable bit<br>d. RB6 and<br>d. RB6 and I | •        | •          | • •          |        |  |  |  |  |

| bit 6-3   | Unimplem   | Unimplemented: Read as '0'                                                                 |              |                                         |          |            |              |        |  |  |  |  |

| bit 2     | LVP: Low \ | /oltage ICS                                                                                | P Enable bit |                                         |          |            |              |        |  |  |  |  |

|           |            | 1 = Low Voltage ICSP enabled<br>0 = Low Voltage ICSP disabled                              |              |                                         |          |            |              |        |  |  |  |  |

| bit 1     | Unimplem   | Unimplemented: Read as '0'                                                                 |              |                                         |          |            |              |        |  |  |  |  |

| bit 0     | STVREN: S  | STVREN: Stack Full/Underflow Reset Enable bit                                              |              |                                         |          |            |              |        |  |  |  |  |

|           |            | 1 = Stack Full/Underflow will cause RESET<br>0 = Stack Full/Underflow will not cause RESET |              |                                         |          |            |              |        |  |  |  |  |

|           | Legend:    |                                                                                            |              |                                         |          |            |              |        |  |  |  |  |

|           | R = Readat | ole bit                                                                                    | C = Cleara   | able bit                                | U = Unin | nplemented | bit, read as | 'O'    |  |  |  |  |

| REGISTER 20-4: | CONFIG4L: CONFIGURATION REGISTER 4 LOW (BYTE ADDRESS 300006h) |

|----------------|---------------------------------------------------------------|

|----------------|---------------------------------------------------------------|

- n = Value when device is unprogrammed

u = Unchanged from programmed state

|                    | R                                                                                                                                                                                                              | R    | R    | R    | R        | R           | R         | R        |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|----------|-------------|-----------|----------|

|                    | DEV2                                                                                                                                                                                                           | DEV1 | DEV0 | REV4 | REV3     | REV2        | REV1      | REV0     |

|                    | bit 7                                                                                                                                                                                                          |      |      |      |          |             |           | bit 0    |

| bit 7-5<br>bit 4-0 | <b>DEV2:DEV0:</b> Device ID bits<br>000 = PIC18F2539<br>001 = PIC18F4539<br>100 = PIC18F2439<br>101 = PIC18F4439<br><b>REV4:REV0:</b> Revision ID bits<br>These bits are used to indicate the device revision. |      |      |      |          |             |           |          |

|                    | Legend:         R = Readable bit       P = Programmable bit       U = Unimplemented bit, read as '0'                                                                                                           |      |      |      |          |             |           |          |

|                    | - n = Value when device is unprogrammed                                                                                                                                                                        |      |      |      | u = Uncł | nanged from | programme | ed state |

#### RE

### REGISTER 20-12: DEVID2: DEVICE ID REGISTER 2 FOR PIC18FXX39 (BYTE ADDRESS 3FFFFFh)

| R     | R    | R    | R    | R    | R    | R    | R     |

|-------|------|------|------|------|------|------|-------|

| DEV10 | DEV9 | DEV8 | DEV7 | DEV6 | DEV5 | DEV4 | DEV3  |

| bit 7 |      |      |      |      |      |      | bit 0 |

#### bit 7-0 DEV10:DEV3: Device ID bits These bits are used with the DEV2:DEV0 bits in the Device ID Register 1 to identify the part number.

| Legend:                |                      |                                     |

|------------------------|----------------------|-------------------------------------|

| R = Readable bit       | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| - n = Value when devic | e is unprogrammed    | u = Unchanged from programmed state |

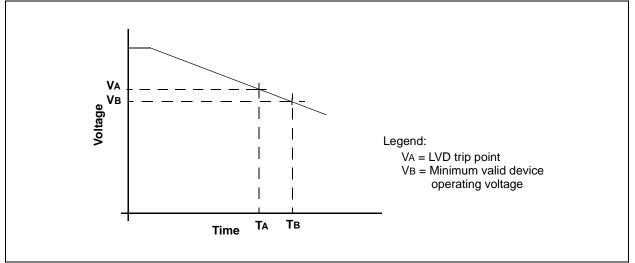

| 21   22   23<br>س osc1 /     | Q4;Q1 Q2 Q3 Q4;Q1<br>~_/~_/~_/~_/~ |                     |              | ; Q1 Q2 Q3 Q4<br>;/~_/~_/~_ | Q1 Q2 Q3 Q4;             | Q1 Q2 Q3 Q4;<br>/~_/~_/ |

|------------------------------|------------------------------------|---------------------|--------------|-----------------------------|--------------------------|-------------------------|

| CLKO <sup>(4)</sup>          |                                    | Tost(2)             | /            | \/                          | \/ <del></del>           |                         |

| INT pin                      |                                    |                     |              | 1<br>1<br>-                 |                          |                         |

| INTF Flag<br>(INTCON<1>)     |                                    |                     |              | Interrupt Latency           | (3)                      |                         |

| GIEH bit<br>(INTCON<7>)      |                                    | DCESSOR IN<br>SLEEP |              | <br> <br>                   | 1 1<br>1 1<br>1 1<br>1 1 | i                       |

| INSTRUCTION FLOW             | 1 I<br>1 I                         |                     | 1            | 1                           | · ·                      | 1                       |

| PC X PC                      | <u>χ PC+2</u> χ                    | PC+4                | PC+4         | X PC + 4                    | <u>χ 0008h</u>           | ( 000Ah                 |

| Instruction I Inst(PC) = SLI | EEP Inst(PC + 2)                   | I                   | Inst(PC + 4) | 1<br>1<br>1                 | Inst(0008h)              | Inst(000Ah)             |

| Instruction<br>Executed      | ) SLEEP                            |                     | Inst(PC + 2) | Dummy Cycle                 | Dummy Cycle              | Inst(0008h)             |

|                              |                                    |                     |              |                             |                          |                         |

**Note 1:** XT, HS or LP Oscillator mode assumed.

2: GIE = 1 assumed. In this case, after wake-up, the processor jumps to the interrupt routine. If GIE = 0, execution will continue in-line.

3: TOST = 1024 TOSC (drawing not to scale). This delay will not occur for RC and EC Osc modes.

4: CLKO is not available in these Osc modes, but shown here for timing reference.

#### 20.4 Program Verification and Code Protection

The overall structure of the code protection on the PIC18 FLASH devices differs significantly from other PIC devices. The user program memory is divided on binary boundaries into individual blocks, each of which has three separate code protection bits associated with it:

- Code Protect bit (CPn)

- Write Protect bit (WRTn)

- External Block Table Read bit (EBTRn)

The code protection bits are located in Configuration Registers 5L through 7H. Their locations within the registers are summarized in Table 20-3.

In the PIC18FXX39 family, program memory is divided into segments of 8 Kbytes. The first block in turn divided into a boot block of 512 bytes and a separately protected remainder (Block 0) of 7.5 Kbytes. This means for PIC18FXX39 devices, that there may be up to five blocks, depending on the program memory size. The organization of the blocks and their associated code protection bits are shown in Figure 20-3. For PIC18FX439 devices, program memory is divided into three blocks: a boot block, Block 0 (7.5 Kbytes) and Block 1 (8 Kbytes). Block 1 is further divided in half; the upper portion above 3000h is reserved, and unavailable to user applications. The entire block can be protected as a whole by bits CP1, WRT1 and EBTR1. By default, Block 1 is not code protected.

For PIC18FX539 devices, program memory is divided into five blocks: the boot block, Block 0 (7.5 Kbytes), and Blocks 1 through 3 (8 Kbytes). Code protection is implemented for the boot block and Blocks 0 through 2. There is no provision for code protection for Block 3.

Note: The reserved segments of the program memory space are used by the Motor Control kernel. For the kernel to function properly, this area must not be write protected. If users are developing applications that require code protection for PIC18FX439 devices, they should restrict program code (or at least those sections requiring protection) to below the 1FFFh memory boundary.

|                              | V                                                                  | Branch if                                                                                           | Branch if Not Overflow                                                                                              |                                                                                   |  |  |  |  |

|------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--|--|--|--|

| Synt                         | ax:                                                                | [label] B                                                                                           | NOV n                                                                                                               |                                                                                   |  |  |  |  |

| Ope                          | rands:                                                             | -128 ≤ n ≤                                                                                          | 127                                                                                                                 |                                                                                   |  |  |  |  |

| Ope                          | ration:                                                            | if overflow<br>(PC) + 2 +                                                                           |                                                                                                                     |                                                                                   |  |  |  |  |

| Statu                        | us Affected:                                                       | None                                                                                                |                                                                                                                     |                                                                                   |  |  |  |  |

| Enco                         | oding:                                                             | 1110                                                                                                | 0101 nn                                                                                                             | nn nnnn                                                                           |  |  |  |  |

| Description:                 |                                                                    | program w<br>The 2's co<br>added to t<br>have incre<br>instruction<br>PC+2+2n.                      | flow bit is '0'<br>vill branch.<br>mplement nu<br>he PC. Since<br>mented to fe<br>, the new ad<br>This instruction. | umber '2n' is<br>e the PC will<br>etch the next<br>dress will be<br>ction is then |  |  |  |  |

| Wor                          | ds:                                                                | 1                                                                                                   | 1                                                                                                                   |                                                                                   |  |  |  |  |

| Cycl                         | es:                                                                | 1(2)                                                                                                | 1(2)                                                                                                                |                                                                                   |  |  |  |  |

|                              |                                                                    |                                                                                                     |                                                                                                                     |                                                                                   |  |  |  |  |

|                              | Cycle Activity:<br>ump:                                            | _                                                                                                   | 03                                                                                                                  | 04                                                                                |  |  |  |  |

|                              | ump:<br>Q1                                                         | Q2                                                                                                  | Q3<br>Process                                                                                                       | Q4<br>Write to PC                                                                 |  |  |  |  |

|                              | ump:                                                               | _                                                                                                   | Q3<br>Process<br>Data                                                                                               | Q4<br>Write to PC                                                                 |  |  |  |  |

|                              | Ump:<br>Q1<br>Decode<br>No                                         | Q2<br>Read literal<br>'n'<br>No                                                                     | Process<br>Data<br>No                                                                                               | Write to PC                                                                       |  |  |  |  |

| lf Ju                        | Q1<br>Decode<br>No<br>operation                                    | Q2<br>Read literal<br>'n'                                                                           | Process<br>Data                                                                                                     | Write to PC                                                                       |  |  |  |  |

| lf Ju                        | Q1<br>Decode<br>No<br>operation<br>o Jump:                         | Q2<br>Read literal<br>'n'<br>No<br>operation                                                        | Process<br>Data<br>No<br>operation                                                                                  | Write to PC<br>No<br>operation                                                    |  |  |  |  |

| lf Ju                        | ump:<br>Q1<br>Decode<br>No<br>operation<br>o Jump:<br>Q1           | Q2<br>Read literal<br>'n'<br>No<br>operation<br>Q2                                                  | Process<br>Data<br>No<br>operation<br>Q3                                                                            | Write to PC<br>No<br>operation<br>Q4                                              |  |  |  |  |

| lf Ju                        | Q1<br>Decode<br>No<br>operation<br>o Jump:                         | Q2<br>Read literal<br>'n'<br>No<br>operation<br>Q2<br>Read literal                                  | Process<br>Data<br>No<br>operation<br>Q3<br>Process                                                                 | Write to PC<br>No<br>operation<br>Q4<br>No                                        |  |  |  |  |

| lf Ju                        | ump:<br>Q1<br>Decode<br>No<br>operation<br>o Jump:<br>Q1           | Q2<br>Read literal<br>'n'<br>No<br>operation<br>Q2                                                  | Process<br>Data<br>No<br>operation<br>Q3                                                                            | Write to PC<br>No<br>operation<br>Q4                                              |  |  |  |  |

| lf Ju                        | ump:<br>Q1<br>Decode<br>No<br>operation<br>o Jump:<br>Q1           | Q2<br>Read literal<br>'n'<br>No<br>operation<br>Q2<br>Read literal                                  | Process<br>Data<br>No<br>operation<br>Q3<br>Process                                                                 | Write to PC<br>No<br>operation<br>Q4<br>No                                        |  |  |  |  |

| lf Ju<br>lf N<br><u>Exar</u> | ump:<br>Q1<br>Decode<br>No<br>operation<br>o Jump:<br>Q1<br>Decode | Q2<br>Read literal<br>'n'<br>No<br>operation<br>Q2<br>Read literal<br>'n'<br>HERE<br>uction<br>= ad | Process<br>Data<br>No<br>operation<br>Q3<br>Process<br>Data                                                         | Write to PC<br>No<br>operation<br>Q4<br>No<br>operation                           |  |  |  |  |

| Synt  | ax:                   | [ <i>label</i> ] B                                                                                          | NZ n                                                             |                                                                |                                               |  |  |

|-------|-----------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------|-----------------------------------------------|--|--|

| Ope   | rands:                | 128 ≤ n ≤                                                                                                   |                                                                  |                                                                |                                               |  |  |

| Ope   | ration:               |                                                                                                             | if zero bit is '0'<br>(PC) + 2 + 2n $\rightarrow$ PC             |                                                                |                                               |  |  |

| Statu | us Affected:          | None                                                                                                        |                                                                  |                                                                |                                               |  |  |

| Enco  | oding:                | 1110                                                                                                        | 0001                                                             | nnnn                                                           | nnnn                                          |  |  |

|       | cription:             | If the Zero<br>program w<br>The 2's co<br>added to t<br>have incre<br>instruction<br>PC+2+2n.<br>a two-cycl | vill branc<br>mpleme<br>he PC.<br>mented<br>, the new<br>This in | h.<br>nt numb<br>Since th<br>to fetch<br>w addres<br>structior | per '2n' i<br>le PC w<br>the new<br>ss will b |  |  |

| Wor   | ds:                   | 1                                                                                                           |                                                                  |                                                                |                                               |  |  |

| Cycl  | es:                   | 1(2)                                                                                                        |                                                                  |                                                                |                                               |  |  |

|       | ycle Activity<br>ump: |                                                                                                             |                                                                  |                                                                |                                               |  |  |

|       | Q1                    | Q2                                                                                                          | Q3                                                               |                                                                | Q4                                            |  |  |

|       | Decode                | Read literal<br>'n'                                                                                         | Proces<br>Data                                                   |                                                                | rite to PC                                    |  |  |

|       | No<br>operation       | No<br>operation                                                                                             | No<br>operati                                                    | on o                                                           | No<br>peration                                |  |  |

| If N  | o Jump:               |                                                                                                             |                                                                  |                                                                |                                               |  |  |

|       | Q1                    | Q2                                                                                                          | Q3                                                               |                                                                | Q4                                            |  |  |

|       | Decode                | Read literal<br>'n'                                                                                         | Proces<br>Data                                                   |                                                                | No<br>peration                                |  |  |

|       |                       |                                                                                                             |                                                                  |                                                                |                                               |  |  |

| FC                             | =           | address (HERE)                                 |

|--------------------------------|-------------|------------------------------------------------|

| After Instruction              |             |                                                |

| If Zero<br>PC<br>If Zero<br>PC | =<br>=<br>= | 0;<br>address (Jump)<br>1;<br>address (HERE+2) |

| BTF                       | sc                                                    | Bit Test Fi                                                                                                              | Bit Test File, Skip if Clear                                                                                                                                                                                                                                                                                                                                                                                      |         |               |  |  |  |

|---------------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------|--|--|--|

| Synta                     | ax:                                                   | [ <i>label</i> ] B                                                                                                       | FSC f,b                                                                                                                                                                                                                                                                                                                                                                                                           | [,a]    |               |  |  |  |

| Oper                      | ands:                                                 | $\begin{array}{l} 0\leq f\leq 255\\ 0\leq b\leq 7\\ a\in [0,1] \end{array}$                                              |                                                                                                                                                                                                                                                                                                                                                                                                                   |         |               |  |  |  |

| Oper                      | ation:                                                | skip if (f <b< td=""><td>&gt;) = 0</td><td></td><td></td></b<>                                                           | >) = 0                                                                                                                                                                                                                                                                                                                                                                                                            |         |               |  |  |  |

| Statu                     | is Affected:                                          | None                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                   |         |               |  |  |  |

| Enco                      | oding:                                                | 1011                                                                                                                     | bbba                                                                                                                                                                                                                                                                                                                                                                                                              | ffff    | ffff          |  |  |  |

| Encoding:<br>Description: |                                                       | next instru-<br>If bit 'b' is 0<br>fetched du<br>execution i<br>executed in<br>cycle instru<br>Access Ba<br>riding the B | If bit 'b' in register 'f' is 0, then the<br>next instruction is skipped.<br>If bit 'b' is 0, then the next instruction<br>fetched during the current instruction<br>execution is discarded, and a NOP is<br>executed instead, making this a two-<br>cycle instruction. If 'a' is 0, the<br>Access Bank will be selected, over-<br>riding the BSR value. If 'a' = 1, then<br>the bank will be selected as per the |         |               |  |  |  |

| Word                      | ds:                                                   | 1                                                                                                                        | (,                                                                                                                                                                                                                                                                                                                                                                                                                |         |               |  |  |  |

| Cycle                     | es:                                                   |                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                   |         |               |  |  |  |

| QC                        | ycle Activity:                                        | •                                                                                                                        | 0.0                                                                                                                                                                                                                                                                                                                                                                                                               |         | ~ /           |  |  |  |

|                           | Q1<br>Decode                                          | Q2<br>Read                                                                                                               | Q3<br>Process D                                                                                                                                                                                                                                                                                                                                                                                                   | ata     | Q4<br>No      |  |  |  |

|                           | Decode                                                | register 'f'                                                                                                             | 1100000 D                                                                                                                                                                                                                                                                                                                                                                                                         |         | eration       |  |  |  |

| lf sk                     | ip:                                                   |                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                   |         |               |  |  |  |

|                           | Q1                                                    | Q2                                                                                                                       | Q3                                                                                                                                                                                                                                                                                                                                                                                                                |         | Q4            |  |  |  |

|                           | No<br>operation                                       | No<br>operation                                                                                                          | No<br>operatio                                                                                                                                                                                                                                                                                                                                                                                                    | n op    | No<br>eration |  |  |  |

| lf sk                     | ip and follow                                         |                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                   |         |               |  |  |  |

|                           | Q1                                                    | Q2                                                                                                                       | Q3                                                                                                                                                                                                                                                                                                                                                                                                                |         | Q4            |  |  |  |

|                           | No                                                    | No                                                                                                                       | No                                                                                                                                                                                                                                                                                                                                                                                                                |         | No            |  |  |  |

|                           | operation<br>No                                       | operation<br>No                                                                                                          | operatio<br>No                                                                                                                                                                                                                                                                                                                                                                                                    | n op    | eration<br>No |  |  |  |

|                           | operation                                             | operation                                                                                                                | operatio                                                                                                                                                                                                                                                                                                                                                                                                          | n op    | eration       |  |  |  |

| <u>Exan</u>               | nple:                                                 | HERE B'<br>FALSE :<br>TRUE :                                                                                             | TFSC F                                                                                                                                                                                                                                                                                                                                                                                                            | LAG, 1, | . 0           |  |  |  |

| I                         | Before Instru<br>PC                                   |                                                                                                                          | iress (HER                                                                                                                                                                                                                                                                                                                                                                                                        | E)      |               |  |  |  |

| ,                         | After Instructi<br>If FLAG<´<br>PC<br>If FLAG<´<br>PC | l> = 0;<br>= add<br>l> = 1;                                                                                              | <b>iress</b> (TRU<br><b>iress</b> (FAI                                                                                                                                                                                                                                                                                                                                                                            |         |               |  |  |  |

| BTFSS                                                                                                                                                                      |                                                                                                                                                                                       | Bit Test File, Skip if Set                                                                                               |                                                                                                                                    |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:                                                                                                                                                                    |                                                                                                                                                                                       | [ <i>label</i> ] BTFSS f,b[,a]                                                                                           |                                                                                                                                    |  |  |  |  |

| Operands:                                                                                                                                                                  | $0 \le f \le 255$                                                                                                                                                                     |                                                                                                                          |                                                                                                                                    |  |  |  |  |

|                                                                                                                                                                            | 0 ≤ b ≤ 7<br>a ∈ [0,1]                                                                                                                                                                |                                                                                                                          |                                                                                                                                    |  |  |  |  |

| Operation                                                                                                                                                                  |                                                                                                                                                                                       | ) _ 1                                                                                                                    |                                                                                                                                    |  |  |  |  |

| Operation:                                                                                                                                                                 | skip if (f <b< td=""><td>&gt;) = 1</td><td></td></b<>                                                                                                                                 | >) = 1                                                                                                                   |                                                                                                                                    |  |  |  |  |

| Status Affected:                                                                                                                                                           | None                                                                                                                                                                                  |                                                                                                                          |                                                                                                                                    |  |  |  |  |

| Encoding:                                                                                                                                                                  | 1010                                                                                                                                                                                  | bbba ff                                                                                                                  | ff ffff                                                                                                                            |  |  |  |  |

| Words:<br>Cycles:                                                                                                                                                          | If bit 'b' is 1<br>fetched dur<br>tion execut<br>NOP is exec<br>a two-cycle<br>Access Bar<br>riding the E<br>the bank w<br>BSR value<br>1<br>1(2)                                     | ring the curre<br>ion, is discar<br>cuted insteac<br>e instruction.<br>nk will be sel<br>SSR value. If<br>ill be selecte | xt instruction<br>ent instruc-<br>ded and a<br>I, making this<br>If 'a' is 0, the<br>ected, over-<br>'a' = 1, then<br>d as per the |  |  |  |  |

|                                                                                                                                                                            | by                                                                                                                                                                                    |                                                                                                                          |                                                                                                                                    |  |  |  |  |

|                                                                                                                                                                            | -                                                                                                                                                                                     | a 2-word ins                                                                                                             |                                                                                                                                    |  |  |  |  |

| Q Cycle Activity:                                                                                                                                                          |                                                                                                                                                                                       | a 2-word ins                                                                                                             | truction.                                                                                                                          |  |  |  |  |