Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 21                                                                         |

| Program Memory Size        | 12KB (6K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 640 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 5x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

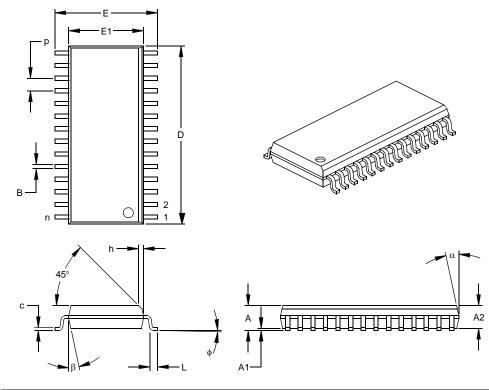

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf2439-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 1-1: PIC18FXX39 DEVICE FEATURES

| Features                                | PIC18F2439                                                                       | PIC18F2539                                                                       | PIC18F4439                                                                       | PIC18F4539                                                                       |

|-----------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Operating Frequency                     | DC - 40 MHz                                                                      |

| Program Memory (Bytes)                  | 12K                                                                              | 24K                                                                              | 12K                                                                              | 24K                                                                              |

| Program Memory (Instructions)           | 6144                                                                             | 12288                                                                            | 6144                                                                             | 12288                                                                            |

| Data Memory (Bytes)                     | 640                                                                              | 1408                                                                             | 640                                                                              | 1408                                                                             |

| Data EEPROM Memory (Bytes)              | 256                                                                              | 256                                                                              | 256                                                                              | 256                                                                              |

| Interrupt Sources                       | 15                                                                               | 15                                                                               | 16                                                                               | 16                                                                               |

| I/O Ports                               | Ports A, B, C                                                                    | Ports A, B, C                                                                    | Ports A, B, C, D, E                                                              | Ports A, B, C, D, E                                                              |

| Timers                                  | 3                                                                                | 3                                                                                | 3                                                                                | 3                                                                                |

| PWM Modules <sup>(1)</sup>              | 2                                                                                | 2                                                                                | 2                                                                                | 2                                                                                |

| Single Phase Induction<br>Motor Control | Yes                                                                              | Yes                                                                              | Yes                                                                              | Yes                                                                              |

| Serial Communications                   | MSSP,<br>Addressable<br>USART                                                    | MSSP,<br>Addressable<br>USART                                                    | MSSP,<br>Addressable<br>USART                                                    | MSSP,<br>Addressable<br>USART                                                    |

| Parallel Communications                 | —                                                                                | —                                                                                | PSP                                                                              | PSP                                                                              |

| 10-bit Analog-to-Digital Module         | 5 input channels                                                                 | 5 input channels                                                                 | 8 input channels                                                                 | 8 input channels                                                                 |

| RESETS (and Delays)                     | POR, BOR,<br>RESET Instruction,<br>Stack Full,<br>Stack Underflow<br>(PWRT, OST) |

| Programmable Low Voltage<br>Detect      | Yes                                                                              | Yes                                                                              | Yes                                                                              | Yes                                                                              |

| Programmable Brown-out Reset            | Yes                                                                              | Yes                                                                              | Yes                                                                              | Yes                                                                              |

| Instruction Set                         | 75 Instructions                                                                  | 75 Instructions                                                                  | 75 Instructions                                                                  | 75 Instructions                                                                  |

| Packages                                | 28-pin DIP<br>28-pin SOIC                                                        | 28-pin DIP<br>28-pin SOIC                                                        | 40-pin DIP<br>44-pin TQFP<br>44-pin QFN                                          | 40-pin DIP<br>44-pin TQFP<br>44-pin QFN                                          |

**Note 1:** PWM modules are used exclusively in conjunction with the motor control kernel, and are not available for other applications.

NOTES:

|         | U-0                              | U-0         | U-0           | R/W-0         | R/W-0        | R/W-0     | R/W-0          | U-0    |

|---------|----------------------------------|-------------|---------------|---------------|--------------|-----------|----------------|--------|

|         | —                                |             | —             | EEIE          | BCLIE        | LVDIE     | TMR3IE         | —      |

|         | bit 7                            |             |               |               |              |           |                | bit 0  |

|         |                                  |             |               |               |              |           |                |        |

| bit 7-5 | Unimplement                      | ted: Read   | d as '0'      |               |              |           |                |        |

| bit 4   | EEIE: Data EE                    | EPROM/F     | LASH Write    | e Operation   | nterrupt En  | able bit  |                |        |

|         | 1 = Enabled<br>0 = Disabled      |             |               |               |              |           |                |        |

| hit O   |                                  | alliaian Ir | torrupt Eng   | bla bit       |              |           |                |        |

| bit 3   | BCLIE: Bus C                     |             | iterrupt ⊑na  |               |              |           |                |        |

|         | 1 = Enabled<br>0 = Disabled      |             |               |               |              |           |                |        |

| bit 2   | LVDIE: Low V                     | oltage De   | etect Interru | pt Enable bit |              |           |                |        |

|         | 1 = Enabled                      |             |               |               |              |           |                |        |

|         | 0 = Disabled                     |             | _             |               |              |           |                |        |

| bit 1   | TMR3IE: TMR                      |             | -             |               |              |           |                |        |

|         | 1 = Enables th<br>0 = Disables t |             |               | •             |              |           |                |        |

| bit 0   | Unimplement                      | ted: Read   | d as '0'      |               |              |           |                |        |

|         |                                  |             |               |               |              |           |                |        |

|         | Legend:                          |             |               |               |              |           |                |        |

|         | R = Readable                     | bit         | W = W         | /ritable bit  | U = Unim     | plemented | bit, read as ' | 0'     |

|         | - n = Value at                   | POR         | '1' = B       | it is set     | '0' = Bit is | s cleared | x = Bit is u   | nknown |

|         |                                  |             |               |               |              |           |                |        |

### REGISTER 8-7: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

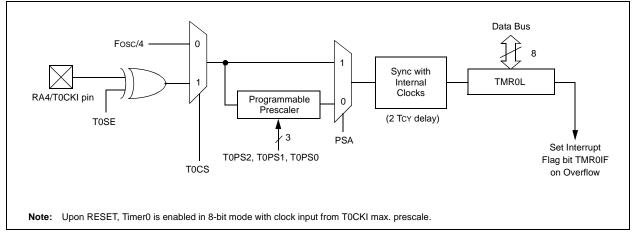

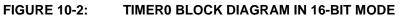

### FIGURE 10-1: TIMER0 BLOCK DIAGRAM IN 8-BIT MODE

## 11.0 TIMER1 MODULE

The Timer1 module timer/counter has the following features:

- 16-bit timer/counter (two 8-bit registers, TMR1H and TMR1L)

- Readable and writable (both registers)

- Internal or external clock select

- Interrupt-on-overflow from FFFFh to 0000h

Figure 11-1 is a simplified block diagram of the Timer1 module.

Register 11-1 details the Timer1 control register, which sets the Operating mode of the Timer1 module. Timer1 can be enabled or disabled by setting or clearing control bit TMR1ON (T1CON<0>).

U = Unimplemented bit, read as '0'

'0' = Bit is cleared

### **REGISTER 11-1:** T1CON: TIMER1 CONTROL REGISTER

|         | R/W-0       | U-0                          | R/W-0          | R/W-0          | U-0           | R/W-0     | R/W-0  | R/W-0  |

|---------|-------------|------------------------------|----------------|----------------|---------------|-----------|--------|--------|

|         | RD16        | _                            | T1CKPS1        | T1CKPS0        | _             | T1SYNC    | TMR1CS | TMR10N |

|         | bit 7       |                              |                |                |               | I         |        | bit 0  |

|         |             |                              |                |                |               |           |        |        |

| bit 7   | RD16: 16-   | bit Read/W                   | /rite Mode Er  | nable bit      |               |           |        |        |

|         |             | •                            |                | Timer1 in on   |               |           |        |        |

|         | 0 = Enable  | es register                  | read/write of  | Timer1 in two  | o 8-bit opera | tions     |        |        |

| bit 6   | Unimplen    | nented: Re                   | ad as '0'      |                |               |           |        |        |

| bit 5-4 | T1CKPS1     | :T1CKPS0                     | : Timer1 Inpu  | ut Clock Pres  | cale Select I | bits      |        |        |

|         | -           | rescale va                   |                |                |               |           |        |        |

|         |             | Prescale val<br>Prescale val |                |                |               |           |        |        |

|         |             | rescale val<br>Prescale val  |                |                |               |           |        |        |

| bit 3   |             |                              | intain as '0'  |                |               |           |        |        |

| bit 2   |             |                              |                | nput Synchro   | nization Sal  | oct hit   |        |        |

| DILZ    | When TMI    |                              |                | nput Synchic   |               | ect bit   |        |        |

|         |             |                              | ze external c  | lock input     |               |           |        |        |

|         |             |                              | rnal clock inp |                |               |           |        |        |

|         | When TMI    | R1CS = 0:                    |                |                |               |           |        |        |

|         | This bit is | ignored. Tii                 | mer1 uses th   | e internal clo | ck when TM    | R1CS = 0. |        |        |

| bit 1   | TMR1CS:     | Timer1 Clo                   | ock Source S   | elect bit      |               |           |        |        |

|         | 1 = Extern  | al clock fro                 | m pin RC0/T    | 13CKI (on th   | e rising edge | e)        |        |        |

|         | 0 = Interna | al clock (Fo                 | sc/4)          |                |               |           |        |        |

| bit 0   | TMR10N:     | Timer1 Or                    | ı bit          |                |               |           |        |        |

|         | 1 = Enable  |                              |                |                |               |           |        |        |

|         | 0 = Stops   | Timer1                       |                |                |               |           |        |        |

|         | r           |                              |                |                |               |           |        |        |

|         | Legend:     |                              |                |                |               |           |        |        |

R = Readable bit

- n = Value at POR

W = Writable bit

'1' = Bit is set

x = Bit is unknown

### **REGISTER 16-4:** SSPCON1: MSSP CONTROL REGISTER 1 (I<sup>2</sup>C MODE)

| WCOL SSPOV SSPEN CKP SSPM3 SSPM2 SSPM1           | SSPM0 |             | 005140 | 000140 |       | 000511 |       |       |  |

|--------------------------------------------------|-------|-------------|--------|--------|-------|--------|-------|-------|--|

| R/VV-U R/VV-U R/VV-U R/VV-U R/VV-U R/VV-U R/VV-U | R/W-0 | R/W-0 R/W-0 | R/W-0  | R/W-0  | R/W-0 | R/W-0  | R/W-0 | R/W-0 |  |

- bit 7 WCOL: Write Collision Detect bit

- In Master Transmit mode:

- 1 = A write to the SSPBUF register was attempted while the I<sup>2</sup>C conditions were not valid for a transmission to be started (must be cleared in software)

- 0 = No collision

- In Slave Transmit mode:

- 1 = The SSPBUF register is written while it is still transmitting the previous word (must be cleared in software)

- $0 = No \ collision$

- In Receive mode (Master or Slave modes):

This is a "don't care" bit

#### bit 6 SSPOV: Receive Overflow Indicator bit

In Receive mode:

- 1 = A byte is received while the SSPBUF register is still holding the previous byte (must be cleared in software)

- 0 = No overflow

In Transmit mode:

This is a "don't care" bit in Transmit mode

#### bit 5 SSPEN: Synchronous Serial Port Enable bit

- 1 = Enables the serial port and configures the SDA and SCL pins as the serial port pins

- 0 = Disables serial port and configures these pins as I/O port pins

Note: When enabled, the SDA and SCL pins must be properly configured as input or output.

- bit 4 **CKP:** SCK Release Control bit

- In Slave mode:

- 1 = Release clock

- 0 = Holds clock low (clock stretch), used to ensure data setup time

- In Master mode:

Unused in this mode

- bit 3-0 SSPM3:SSPM0: Synchronous Serial Port Mode Select bits

- 1111 =  $I^2C$  Slave mode, 10-bit address with START and STOP bit interrupts enabled

- $1110 = I^2C$  Slave mode, 7-bit address with START and STOP bit interrupts enabled

- $1011 = I^2C$  Firmware Controlled Master mode (Slave IDLE)

- $1000 = I^2C$  Master mode, clock = FOSC / (4 \* (SSPADD+1))

- 0111 =  $I^2C$  Slave mode, 10-bit address

- $0110 = I^2C$  Slave mode, 7-bit address

- **Note:** Bit combinations not specifically listed here are either reserved, or implemented in SPI mode only.

| Legend:            |                  |                                        |  |

|--------------------|------------------|----------------------------------------|--|

| R = Readable bit   | W = Writable bit | U = Unimplemented bit, read as '0'     |  |

| - n = Value at POR | '1' = Bit is set | 0' = Bit is cleared x = Bit is unknown |  |

### 16.4.2 OPERATION

The MSSP module functions are enabled by setting MSSP Enable bit, SSPEN (SSPCON<5>).

The SSPCON1 register allows control of the I<sup>2</sup>C operation. Four mode selection bits (SSPCON<3:0>) allow one of the following I<sup>2</sup>C modes to be selected:

- I<sup>2</sup>C Master mode, clock = OSC/4 (SSPADD +1)

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address), with START and STOP bit interrupts enabled

- I<sup>2</sup>C Slave mode (10-bit address), with START and STOP bit interrupts enabled

- I<sup>2</sup>C Firmware controlled master operation, slave is IDLE

Selection of any I<sup>2</sup>C mode, with the SSPEN bit set, forces the SCL and SDA pins to be open drain, provided these pins are programmed to inputs by setting the appropriate TRISC bits. To ensure proper operation of the module, pull-up resistors must be provided externally to the SCL and SDA pins.

### 16.4.3 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The MSSP module will override the input state with the output data when required (slave-transmitter).

The I<sup>2</sup>C Slave mode hardware will always generate an interrupt on an address match. Through the mode select bits, the user can also choose to interrupt on START and STOP bits

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge ( $\overline{ACK}$ ) pulse and load the SSPBUF register with the received value currently in the SSPSR register.

Any combination of the following conditions will cause the MSSP module not to give this  $\overline{ACK}$  pulse:

- The buffer full bit BF (SSPSTAT<0>) was set before the transfer was received.

- The overflow bit SSPOV (SSPCON<6>) was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF (PIR1<3>) is set. The BF bit is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirement of the MSSP module, are shown in timing parameter 100 and parameter 101.

### 16.4.3.1 Addressing

Once the MSSP module has been enabled, it waits for a START condition to occur. Following the START condition, the 8-bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match, and the BF and SSPOV bits are clear, the following events occur:

- 1. The SSPSR register value is loaded into the SSPBUF register.

- 2. The buffer full bit BF is set.

- 3. An ACK pulse is generated.

- 4. MSSP interrupt flag bit, SSPIF (PIR1<3>) is set (interrupt is generated if enabled) on the falling edge of the ninth SCL pulse.

In 10-bit Address mode, two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit R/W (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '11110 A9 A8 0', where 'A9' and 'A8' are the two MSbs of the address. The sequence of events for 10-bit address is as follows, with steps 7 through 9 for the slave-transmitter:

- 1. Receive first (high) byte of Address (bits SSPIF, BF and bit UA (SSPSTAT<1>) are set).

- 2. Update the SSPADD register with second (low) byte of Address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 4. Receive second (low) byte of Address (bits SSPIF, BF, and UA are set).

- 5. Update the SSPADD register with the first (high) byte of Address. If match releases SCL line, this will clear bit UA.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive Repeated START condition.

- 8. Receive first (high) byte of Address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

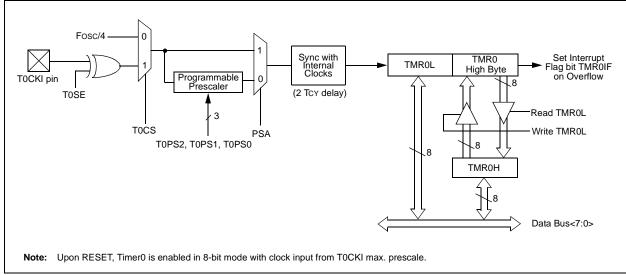

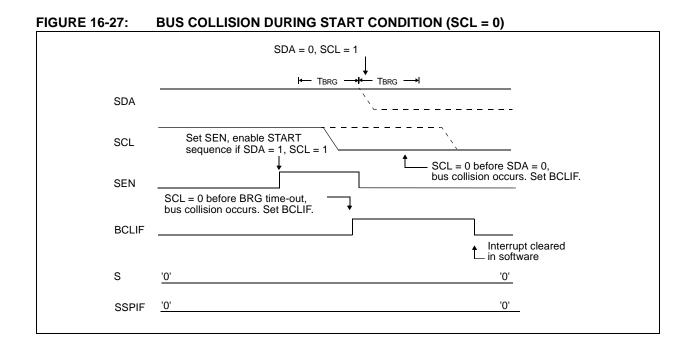

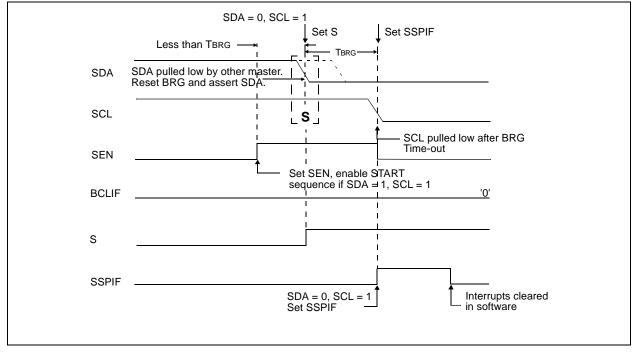

### FIGURE 16-28: BRG RESET DUE TO SDA ARBITRATION DURING START CONDITION

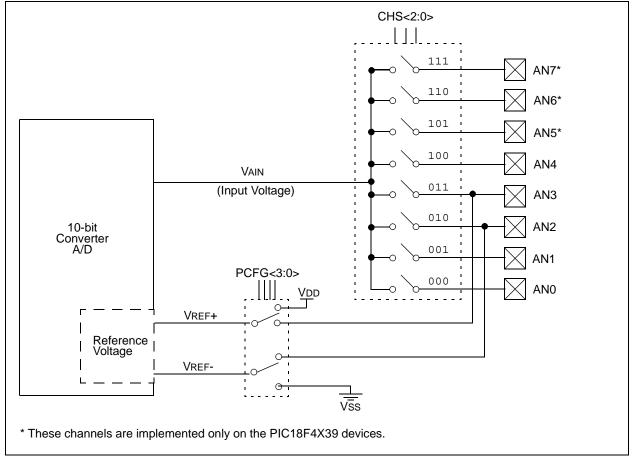

The analog reference voltage is software selectable to either the device's positive and negative supply voltage (VDD and Vss), or the voltage level on the RA3/AN3/ VREF+ pin and RA2/AN2/VREF- pin.

The A/D converter has a unique feature of being able to operate while the device is in SLEEP mode. To operate in SLEEP, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

The output of the sample and hold is the input into the converter, which generates the result via successive approximation.

A device RESET forces all registers to their RESET state. This forces the A/D module to be turned off and any conversion is aborted.

Each port pin associated with the A/D converter can be configured as an analog input (RA3 can also be a voltage reference) or as a digital I/O.

The ADRESH and ADRESL registers contain the result of the A/D conversion. When the A/D conversion is complete, the result is loaded into the ADRESH/ ADRESL registers, the GO/DONE bit (ADCON0<2>) is cleared, and A/D interrupt flag bit, ADIF is set. The block diagram of the A/D module is shown in Figure 18-1.

#### FIGURE 18-1: A/D BLOCK DIAGRAM

© 2002-2013 Microchip Technology Inc.

|                              | V                                                                  | Branch if                                                                                           | Branch if Not Overflow                                                                                                                                                                                                                                     |                                                         |  |  |  |

|------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--|--|--|

| Synt                         | ax:                                                                | [label] B                                                                                           | NOV n                                                                                                                                                                                                                                                      |                                                         |  |  |  |

| Ope                          | rands:                                                             | -128 ≤ n ≤                                                                                          | 127                                                                                                                                                                                                                                                        |                                                         |  |  |  |

| Ope                          | ration:                                                            | if overflow<br>(PC) + 2 +                                                                           |                                                                                                                                                                                                                                                            |                                                         |  |  |  |

| Statu                        | us Affected:                                                       | None                                                                                                |                                                                                                                                                                                                                                                            |                                                         |  |  |  |

| Enco                         | oding:                                                             | 1110                                                                                                | 0101 nn                                                                                                                                                                                                                                                    | nn nnnn                                                 |  |  |  |

| Des                          | cription:                                                          | program w<br>The 2's co<br>added to t<br>have incre<br>instruction                                  | If the Overflow bit is '0', then the<br>program will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will<br>have incremented to fetch the next<br>instruction, the new address will be<br>PC+2+2n. This instruction is then |                                                         |  |  |  |

| Wor                          | ds:                                                                | 1                                                                                                   |                                                                                                                                                                                                                                                            |                                                         |  |  |  |

| Cycl                         | es:                                                                | 1(2)                                                                                                |                                                                                                                                                                                                                                                            |                                                         |  |  |  |

|                              |                                                                    |                                                                                                     |                                                                                                                                                                                                                                                            |                                                         |  |  |  |

|                              | Cycle Activity:<br>ump:                                            | _                                                                                                   | 03                                                                                                                                                                                                                                                         | 04                                                      |  |  |  |

|                              | ump:<br>Q1                                                         | Q2                                                                                                  | Q3<br>Process                                                                                                                                                                                                                                              | Q4<br>Write to PC                                       |  |  |  |

|                              | ump:                                                               | _                                                                                                   | Q3<br>Process<br>Data                                                                                                                                                                                                                                      | Q4<br>Write to PC                                       |  |  |  |

|                              | Ump:<br>Q1<br>Decode<br>No                                         | Q2<br>Read literal<br>'n'<br>No                                                                     | Process<br>Data<br>No                                                                                                                                                                                                                                      | Write to PC                                             |  |  |  |

| lf Ju                        | Q1<br>Decode<br>No<br>operation                                    | Q2<br>Read literal<br>'n'                                                                           | Process<br>Data                                                                                                                                                                                                                                            | Write to PC                                             |  |  |  |

| lf Ju                        | Q1<br>Decode<br>No<br>operation<br>o Jump:                         | Q2<br>Read literal<br>'n'<br>No<br>operation                                                        | Process<br>Data<br>No<br>operation                                                                                                                                                                                                                         | Write to PC<br>No<br>operation                          |  |  |  |

| lf Ju                        | ump:<br>Q1<br>Decode<br>No<br>operation<br>o Jump:<br>Q1           | Q2<br>Read literal<br>'n'<br>No<br>operation<br>Q2                                                  | Process<br>Data<br>No<br>operation<br>Q3                                                                                                                                                                                                                   | Write to PC<br>No<br>operation<br>Q4                    |  |  |  |

| lf Ju                        | Q1<br>Decode<br>No<br>operation<br>o Jump:                         | Q2<br>Read literal<br>'n'<br>No<br>operation<br>Q2<br>Read literal                                  | Process<br>Data<br>No<br>operation<br>Q3<br>Process                                                                                                                                                                                                        | Write to PC<br>No<br>operation<br>Q4<br>No              |  |  |  |

| lf Ju                        | ump:<br>Q1<br>Decode<br>No<br>operation<br>o Jump:<br>Q1           | Q2<br>Read literal<br>'n'<br>No<br>operation<br>Q2                                                  | Process<br>Data<br>No<br>operation<br>Q3                                                                                                                                                                                                                   | Write to PC<br>No<br>operation<br>Q4                    |  |  |  |

| lf Ju                        | ump:<br>Q1<br>Decode<br>No<br>operation<br>o Jump:<br>Q1           | Q2<br>Read literal<br>'n'<br>No<br>operation<br>Q2<br>Read literal                                  | Process<br>Data<br>No<br>operation<br>Q3<br>Process                                                                                                                                                                                                        | Write to PC<br>No<br>operation<br>Q4<br>No              |  |  |  |

| lf Ju<br>lf N<br><u>Exar</u> | ump:<br>Q1<br>Decode<br>No<br>operation<br>o Jump:<br>Q1<br>Decode | Q2<br>Read literal<br>'n'<br>No<br>operation<br>Q2<br>Read literal<br>'n'<br>HERE<br>uction<br>= ad | Process<br>Data<br>No<br>operation<br>Q3<br>Process<br>Data                                                                                                                                                                                                | Write to PC<br>No<br>operation<br>Q4<br>No<br>operation |  |  |  |

| Synt  | ax:                                                                                                                                                                                                                                                                          | [ <i>label</i> ] B  | NZ n                                                 |      |                |  |  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------------------------------------|------|----------------|--|--|

| Ope   | rands:                                                                                                                                                                                                                                                                       | 128 ≤ n ≤           |                                                      |      |                |  |  |

| Ope   | ration:                                                                                                                                                                                                                                                                      |                     | if zero bit is '0'<br>(PC) + 2 + 2n $\rightarrow$ PC |      |                |  |  |

| Statu | us Affected:                                                                                                                                                                                                                                                                 | None                |                                                      |      |                |  |  |

| Enco  | oding:                                                                                                                                                                                                                                                                       | 1110                | 0001                                                 | nnnn | nnnn           |  |  |

|       | Description:<br>If the Zero bit is '0', then the<br>program will branch.<br>The 2's complement number '2<br>added to the PC. Since the PC<br>have incremented to fetch the<br>instruction, the new address wi<br>PC+2+2n. This instruction is th<br>a two-cycle instruction. |                     |                                                      |      |                |  |  |

| Wor   | ds:                                                                                                                                                                                                                                                                          | 1                   |                                                      |      |                |  |  |

| Cycl  | es:                                                                                                                                                                                                                                                                          | 1(2)                |                                                      |      |                |  |  |

|       | ycle Activity<br>ump:                                                                                                                                                                                                                                                        |                     |                                                      |      |                |  |  |

|       | Q1                                                                                                                                                                                                                                                                           | Q2                  | Q3                                                   |      | Q4             |  |  |

|       | Decode                                                                                                                                                                                                                                                                       | Read literal<br>'n' | Proces<br>Data                                       |      | rite to PC     |  |  |

|       | No<br>operation                                                                                                                                                                                                                                                              | No<br>operation     | No<br>operati                                        | on o | No<br>peration |  |  |

| If N  | o Jump:                                                                                                                                                                                                                                                                      |                     |                                                      |      |                |  |  |

|       | Q1                                                                                                                                                                                                                                                                           | Q2                  | Q3                                                   |      | Q4             |  |  |

|       | Decode                                                                                                                                                                                                                                                                       | Read literal<br>'n' | Proces<br>Data                                       |      | No<br>peration |  |  |

|       |                                                                                                                                                                                                                                                                              |                     |                                                      |      |                |  |  |

| FC                             | =           | address (HERE)                                 |

|--------------------------------|-------------|------------------------------------------------|

| After Instruction              |             |                                                |

| If Zero<br>PC<br>If Zero<br>PC | =<br>=<br>= | 0;<br>address (Jump)<br>1;<br>address (HERE+2) |

| BTF         | sc                                                    | Bit Test File, Skip if Clear                                                                                                                                           |                                                                                                                                   |                                                                                                        |                                                                              |  |  |

|-------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--|--|

| Synta       | ax:                                                   | [ <i>label</i> ] B                                                                                                                                                     | FSC f,b                                                                                                                           | [,a]                                                                                                   |                                                                              |  |  |

| Oper        | ands:                                                 | $\begin{array}{l} 0\leq f\leq 255\\ 0\leq b\leq 7\\ a\in [0,1] \end{array}$                                                                                            |                                                                                                                                   |                                                                                                        |                                                                              |  |  |

| Oper        | eration: skip if (f <b>) = 0</b>                      |                                                                                                                                                                        |                                                                                                                                   |                                                                                                        |                                                                              |  |  |

| Statu       | is Affected:                                          | None                                                                                                                                                                   |                                                                                                                                   |                                                                                                        |                                                                              |  |  |

| Enco        | oding:                                                | 1011                                                                                                                                                                   | bbba                                                                                                                              | ffff                                                                                                   | ffff                                                                         |  |  |

| Desc        | ription:                                              | If bit 'b' in r<br>next instru-<br>If bit 'b' is 0<br>fetched du<br>execution i<br>executed in<br>cycle instru<br>Access Ba<br>riding the E<br>the bank w<br>BSR value | ction is sk<br>), then the<br>ring the cu<br>is discarde<br>nstead, m<br>uction. If 'a<br>nk will be<br>3SR value<br>rill be sele | ipped.<br>a next ins<br>urrent ins<br>ed, and a<br>aking thi<br>a' is 0, th<br>selected<br>a. If 'a' = | struction<br>struction<br>a NOP is<br>is a two-<br>ie<br>d, over-<br>1, then |  |  |

| Word        | ds:                                                   | 1                                                                                                                                                                      | (,                                                                                                                                |                                                                                                        |                                                                              |  |  |

| Cycle       | es:                                                   |                                                                                                                                                                        | cycles if sk<br>a 2-word                                                                                                          | -                                                                                                      |                                                                              |  |  |

| QC          | ycle Activity:                                        | •                                                                                                                                                                      | 0.0                                                                                                                               |                                                                                                        | ~ /                                                                          |  |  |

|             | Q1<br>Decode                                          | Q2<br>Read                                                                                                                                                             | Q3<br>Process D                                                                                                                   | ata                                                                                                    | Q4<br>No                                                                     |  |  |

|             | Decode                                                | register 'f'                                                                                                                                                           | 1100000 D                                                                                                                         |                                                                                                        | eration                                                                      |  |  |

| lf sk       | ip:                                                   |                                                                                                                                                                        |                                                                                                                                   |                                                                                                        |                                                                              |  |  |

|             | Q1                                                    | Q2                                                                                                                                                                     | Q3                                                                                                                                |                                                                                                        | Q4                                                                           |  |  |

|             | No<br>operation                                       | No<br>operation                                                                                                                                                        | No<br>operatio                                                                                                                    | n op                                                                                                   | No<br>eration                                                                |  |  |

| lf sk       | ip and follow                                         |                                                                                                                                                                        |                                                                                                                                   |                                                                                                        |                                                                              |  |  |

|             | Q1                                                    | Q2                                                                                                                                                                     | Q3                                                                                                                                |                                                                                                        | Q4                                                                           |  |  |

|             | No                                                    | No                                                                                                                                                                     | No                                                                                                                                |                                                                                                        | No                                                                           |  |  |

|             | operation<br>No                                       | operation<br>No                                                                                                                                                        | operatio<br>No                                                                                                                    | n op                                                                                                   | eration<br>No                                                                |  |  |

|             | operation                                             | operation                                                                                                                                                              | operatio                                                                                                                          | n op                                                                                                   | eration                                                                      |  |  |

| <u>Exan</u> | nple:                                                 | HERE B'<br>FALSE :<br>TRUE :                                                                                                                                           | TFSC F                                                                                                                            | LAG, 1,                                                                                                | . 0                                                                          |  |  |

| I           | Before Instru<br>PC                                   |                                                                                                                                                                        | iress (HER                                                                                                                        | E)                                                                                                     |                                                                              |  |  |

| ,           | After Instructi<br>If FLAG<´<br>PC<br>If FLAG<´<br>PC | l> = 0;<br>= add<br>l> = 1;                                                                                                                                            | <b>iress</b> (TRU<br><b>iress</b> (FAI                                                                                            |                                                                                                        |                                                                              |  |  |

| BTFSS                                                                                                                                                                      | Bit Test File, Skip if Set                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                         |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                                                                                                                                                                    |                                                                                                                                                                                       | [label] BTFSS f,b[,a]                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                         |  |  |  |

| Operands:                                                                                                                                                                  | $0 \le f \le 255$                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                         |  |  |  |

|                                                                                                                                                                            | 0 ≤ b ≤ 7<br>a ∈ [0,1]                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                         |  |  |  |

| Operation                                                                                                                                                                  |                                                                                                                                                                                       | ) _ 1                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                         |  |  |  |

| Operation:                                                                                                                                                                 | skip if (f <b< td=""><td>&gt;) = 1</td><td></td></b<>                                                                                                                                 | >) = 1                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                         |  |  |  |

| Status Affected:                                                                                                                                                           | None                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                         |  |  |  |

| Encoding:                                                                                                                                                                  | 1010                                                                                                                                                                                  | bbba ff                                                                                                                                                                                                                                                                                                                                                                                                                                         | ff ffff                                                                                                 |  |  |  |

| Words:<br>Cycles:                                                                                                                                                          | If bit 'b' is 1<br>fetched dur<br>tion execut<br>NOP is exec<br>a two-cycle<br>Access Bar<br>riding the E<br>the bank w<br>BSR value<br>1<br>1(2)                                     | If bit 'b' in register 'f' is 1, then the<br>next instruction is skipped.<br>If bit 'b' is 1, then the next instruction<br>fetched during the current instruc-<br>tion execution, is discarded and a<br>NOP is executed instead, making this<br>a two-cycle instruction. If 'a' is 0, the<br>Access Bank will be selected, over-<br>riding the BSR value. If 'a' = 1, then<br>the bank will be selected as per the<br>BSR value (default).<br>1 |                                                                                                         |  |  |  |

|                                                                                                                                                                            | by                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                 | and followed                                                                                            |  |  |  |

|                                                                                                                                                                            | -                                                                                                                                                                                     | a 2-word ins                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                         |  |  |  |

| Q Cycle Activity:                                                                                                                                                          |                                                                                                                                                                                       | a 2-word ins                                                                                                                                                                                                                                                                                                                                                                                                                                    | truction.                                                                                               |  |  |  |

| Q Cycle Activity:<br>Q1<br>Decode                                                                                                                                          | -                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                         |  |  |  |

| Q1                                                                                                                                                                         | Q2                                                                                                                                                                                    | a 2-word ins<br>Q3                                                                                                                                                                                                                                                                                                                                                                                                                              | truction.<br>Q4                                                                                         |  |  |  |

| Q1                                                                                                                                                                         | Q2<br>Read                                                                                                                                                                            | a 2-word ins<br>Q3                                                                                                                                                                                                                                                                                                                                                                                                                              | truction.<br>Q4<br>No                                                                                   |  |  |  |

| Q1<br>Decode                                                                                                                                                               | Q2<br>Read                                                                                                                                                                            | a 2-word ins<br>Q3                                                                                                                                                                                                                                                                                                                                                                                                                              | truction.<br>Q4<br>No                                                                                   |  |  |  |

| Q1<br>Decode<br>If skip:<br>Q1<br>No                                                                                                                                       | Q2<br>Read<br>register 'f'<br>Q2<br>No                                                                                                                                                | a 2-word ins<br>Q3<br>Process Data<br>Q3<br>No                                                                                                                                                                                                                                                                                                                                                                                                  | truction.<br>Q4<br>No<br>operation<br>Q4<br>No                                                          |  |  |  |

| Q1<br>Decode<br>If skip:<br>Q1<br>No<br>operation                                                                                                                          | Q2<br>Read<br>register 'f'<br>Q2<br>No<br>operation                                                                                                                                   | a 2-word ins<br>Q3<br>Process Data<br>Q3<br>No<br>operation                                                                                                                                                                                                                                                                                                                                                                                     | truction.<br>Q4<br>No<br>operation<br>Q4                                                                |  |  |  |

| Q1<br>Decode<br>If skip:<br>Q1<br>No                                                                                                                                       | Q2<br>Read<br>register 'f'<br>Q2<br>No<br>operation                                                                                                                                   | a 2-word ins<br>Q3<br>Process Data<br>Q3<br>No<br>operation                                                                                                                                                                                                                                                                                                                                                                                     | truction.<br>Q4<br>No<br>operation<br>Q4<br>No                                                          |  |  |  |

| Q1<br>Decode<br>If skip:<br>Q1<br>No<br>operation<br>If skip and follow<br>Q1                                                                                              | Q2<br>Read<br>register 'f'<br>Q2<br>No<br>operation<br>red by 2-word<br>Q2                                                                                                            | a 2-word ins<br>Q3<br>Process Data<br>Q3<br>No<br>operation<br>instruction:<br>Q3                                                                                                                                                                                                                                                                                                                                                               | truction.<br>Q4<br>No<br>operation<br>Q4<br>No<br>operation<br>Q4                                       |  |  |  |