#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Detuns                     |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 21                                                                          |

| Program Memory Size        | 12KB (6K x 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 640 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 5x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf2439t-i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-2: | PIC18F2X39 PINOUT I/O DESCRIPTIONS (CONTINUED) | ) |

|------------|------------------------------------------------|---|

|------------|------------------------------------------------|---|

| Pin Name         | Pin N    | Pin Number |      | Buffer | Description                                               |  |  |  |

|------------------|----------|------------|------|--------|-----------------------------------------------------------|--|--|--|

| Pin Name         | DIP      | SOIC       | Туре | Туре   | Description                                               |  |  |  |

|                  |          |            |      |        | PORTB is a bi-directional I/O port. PORTB can be software |  |  |  |

|                  |          |            |      |        | programmed for internal weak pull-ups on all inputs.      |  |  |  |

| RB0/INT0         | 21       | 21         |      |        |                                                           |  |  |  |

| RB0              |          |            | I/O  | TTL    | Digital I/O.                                              |  |  |  |

| INT0             |          |            | I    | ST     | External interrupt 0.                                     |  |  |  |

| RB1/INT1         | 22       | 22         |      |        |                                                           |  |  |  |

| RB1              |          |            | I/O  | TTL    | Digital I/O.                                              |  |  |  |

| INT1             |          |            | I    | ST     | External interrupt 1.                                     |  |  |  |

| RB2/INT2         | 23       | 23         |      |        |                                                           |  |  |  |

| RB2              |          |            | I/O  | TTL    | Digital I/O.                                              |  |  |  |

| INT2             |          |            | I    | ST     | External interrupt 2.                                     |  |  |  |

| RB3              | 24       | 24         | I/O  | TTL    | Digital I/O.                                              |  |  |  |

| RB4              | 25       | 25         | I/O  | TTL    | Digital I/O.                                              |  |  |  |

|                  |          |            |      |        | Interrupt-on-change pin.                                  |  |  |  |

| RB5/PGM          | 26       | 26         |      |        |                                                           |  |  |  |

| RB5              |          |            | I/O  | TTL    | Digital I/O. Interrupt-on-change pin.                     |  |  |  |

| PGM              |          |            | I/O  | ST     | Low Voltage ICSP programming enable pin.                  |  |  |  |

| RB6/PGC          | 27       | 27         |      |        |                                                           |  |  |  |

| RB6              |          |            | I/O  | TTL    | Digital I/O. Interrupt-on-change pin.                     |  |  |  |

| PGC              |          |            | I/O  | ST     | In-Circuit Debugger and ICSP programming clock pin.       |  |  |  |

| RB7/PGD          | 28       | 28         |      |        |                                                           |  |  |  |

| RB7              |          |            | I/O  | TTL    | Digital I/O. Interrupt-on-change pin.                     |  |  |  |

| PGD              |          |            | I/O  | ST     | In-Circuit Debugger and ICSP programming data pin.        |  |  |  |

| Legend: TTL = TT | L compat | tible inp  | ut   |        | CMOS = CMOS compatible input or output                    |  |  |  |

ST = Schmitt Trigger input with CMOS levels O = Output OD = Open Drain (no P diode to VDD)

= Input

Р = Power

L

| TABLE 1-2: | PIC18F2X39 PINOUT I/O DESCRIPTIONS (CONTINUED) |

|------------|------------------------------------------------|

|------------|------------------------------------------------|

| Pin Name         | Pin N    | Pin Number |           | Buffer | Description                                                      |  |  |  |

|------------------|----------|------------|-----------|--------|------------------------------------------------------------------|--|--|--|

| Pin Name         | DIP      | SOIC       | Туре Туре |        | Description                                                      |  |  |  |

|                  |          |            |           |        | PORTC is a bi-directional I/O port.                              |  |  |  |

| RC0/T13CKI       | 11       | 11         |           |        |                                                                  |  |  |  |

| RC0              |          |            | I/O       | ST     | Digital I/O.                                                     |  |  |  |

| T13CKI           |          |            | I.        | ST     | Timer1/Timer3 external clock input.                              |  |  |  |

| RC3/SCK/SCL      | 14       | 14         |           |        |                                                                  |  |  |  |

| RC3              |          |            | I/O       | ST     | Digital I/O.                                                     |  |  |  |

| SCK              |          |            | I/O       | ST     | Synchronous serial clock input/output for SPI mode.              |  |  |  |

| SCL              |          |            | I/O       | ST     | Synchronous serial clock input/output for I <sup>2</sup> C mode. |  |  |  |

| RC4/SDI/SDA      | 15       | 15         |           |        |                                                                  |  |  |  |

| RC4              |          |            | I/O       | ST     | Digital I/O.                                                     |  |  |  |

| SDI              |          |            | I         | ST     | SPI Data in.                                                     |  |  |  |

| SDA              |          |            | I/O       | ST     | I <sup>2</sup> C Data I/O.                                       |  |  |  |

| RC5/SDO          | 16       | 16         |           |        |                                                                  |  |  |  |

| RC5              |          |            | I/O       | ST     | Digital I/O.                                                     |  |  |  |

| SDO              |          |            | 0         | _      | SPI Data out.                                                    |  |  |  |

| RC6/TX/CK        | 17       | 17         |           |        |                                                                  |  |  |  |

| RC6              |          |            | I/O       | ST     | Digital I/O.                                                     |  |  |  |

| ТХ               |          |            | 0         | _      | USART Asynchronous Transmit.                                     |  |  |  |

| CK               |          |            | I/O       | ST     | USART Synchronous Clock (see related RX/DT).                     |  |  |  |

| RC7/RX/DT        | 18       | 18         |           |        |                                                                  |  |  |  |

| RC7              |          |            | I/O       | ST     | Digital I/O.                                                     |  |  |  |

| RX               |          |            | Ι         | ST     | USART Asynchronous Receive.                                      |  |  |  |

| DT               |          |            | I/O       | ST     | USART Synchronous Data (see related TX/CK).                      |  |  |  |

| PWM1             | 13       | 13         | 0         |        | PWM Channel 1 (motor control) output.                            |  |  |  |

| PWM2             | 12       | 12         | 0         | —      | PWM Channel 2 (motor control) output.                            |  |  |  |

| Vss              | 8, 19    | 8, 19      | Р         |        | Ground reference for logic and I/O pins.                         |  |  |  |

| Vdd              | 20       | 20         | Р         |        | Positive supply for logic and I/O pins.                          |  |  |  |

| Legend: TTL = TT | L compat | tible inp  | ut        |        | CMOS = CMOS compatible input or output                           |  |  |  |

ST = Schmitt Trigger input with CMOS levels O = Output

I = Input = Power Ρ

OD = Open Drain (no P diode to VDD)

© 2002-2013 Microchip Technology Inc.

#### TABLE 1-3: PIC18F4X39 PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin Name          | Pin Number                         |             |         | Pin Buffer |             | Description                                                                                     |

|-------------------|------------------------------------|-------------|---------|------------|-------------|-------------------------------------------------------------------------------------------------|

| Pin Name          | DIP QFN TQFP Type Type Description |             |         |            | Description |                                                                                                 |

|                   |                                    |             |         |            |             | PORTE is a bi-directional I/O port.                                                             |

| RE0/RD/AN5        | 8                                  | 25          | 25      | I/O        |             |                                                                                                 |

| RE0               |                                    |             |         |            | ST          | Digital I/O.                                                                                    |

| RD                |                                    |             |         |            | TTL         | Read control for parallel slave port                                                            |

|                   |                                    |             |         |            |             | (see also $\overline{WR}$ and $\overline{CS}$ pins).                                            |

| AN5               |                                    |             |         |            | Analog      | Analog input 5.                                                                                 |

| RE1/WR/AN6        | 9                                  | 26          | 26      | I/O        |             |                                                                                                 |

| RE1               |                                    |             |         |            | ST          | Digital I/O.                                                                                    |

| WR                |                                    |             |         |            | TTL         | Write control for parallel slave port                                                           |

|                   |                                    |             |         |            |             | (see CS and RD pins).                                                                           |

| AN6               |                                    |             |         |            | Analog      | Analog input 6.                                                                                 |

| RE2/CS/AN7        | 10                                 | 27          | 27      | I/O        |             |                                                                                                 |

| RE2               |                                    |             |         |            | ST          | Digital I/O.                                                                                    |

| CS                |                                    |             |         |            | TTL         | Chip Select control for parallel slave port (see related $\overline{RD}$ and $\overline{WR}$ ). |

| AN7               |                                    |             |         |            | Analog      | Analog input 7.                                                                                 |

| Vss               | 12, 31                             | 6, 31       | 6, 29   | Р          | —           | Ground reference for logic and I/O pins.                                                        |

| Vdd               | 11, 32                             | 7, 28,      | 7, 28   | Р          | —           | Positive supply for logic and I/O pins.                                                         |

|                   |                                    | 29          |         |            |             |                                                                                                 |

| AVss              | _                                  | 30          |         | Р          |             | Ground reference for analog modules.                                                            |

| AVdd              | —                                  | 8           | —       | Р          |             | Positive supply for analog modules.                                                             |

| NC                | _                                  | 13          | 12, 13, | _          |             | These pins should be left unconnected.                                                          |

| Legend: TTL - TTL | ·                                  | 1. I.a. 1.a | 33, 34  |            |             | CMOS – CMOS compatible input or output                                                          |

Legend: TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

O = Output

OD = Open Drain (no P diode to VDD)

CMOS = CMOS compatible input or output

= Input

L

P = Power

#### TABLE 4-1: SPECIAL FUNCTION REGISTER MAP

| Address | Name                    | Address | Name                    | Address | Name                 | Address | Name                 |

|---------|-------------------------|---------|-------------------------|---------|----------------------|---------|----------------------|

| FFFh    | TOSU                    | FDFh    | INDF2 <sup>(3)</sup>    | FBFh    | CCPR1H               | F9Fh    | IPR1                 |

| FFEh    | TOSH                    | FDEh    | POSTINC2(3)             | FBEh    | CCPR1L*              | F9Eh    | PIR1                 |

| FFDh    | TOSL                    | FDDh    | POSTDEC2 <sup>(3)</sup> | FBDh    | CCP1CON <sup>*</sup> | F9Dh    | PIE1                 |

| FFCh    | STKPTR                  | FDCh    | PREINC2 <sup>(3)</sup>  | FBCh    | CCPR2H               | F9Ch    |                      |

| FFBh    | PCLATU                  | FDBh    | PLUSW2 <sup>(3)</sup>   | FBBh    | CCPR2L <sup>*</sup>  | F9Bh    |                      |

| FFAh    | PCLATH                  | FDAh    | FSR2H                   | FBAh    | CCP2CON <sup>*</sup> | F9Ah    |                      |

| FF9h    | PCL                     | FD9h    | FSR2L                   | FB9h    | —                    | F99h    |                      |

| FF8h    | TBLPTRU                 | FD8h    | STATUS                  | FB8h    | _                    | F98h    | —                    |

| FF7h    | TBLPTRH                 | FD7h    | TMR0H                   | FB7h    | —                    | F97h    | —                    |

| FF6h    | TBLPTRL                 | FD6h    | TMR0L                   | FB6h    | —                    | F96h    | TRISE <sup>(2)</sup> |

| FF5h    | TABLAT                  | FD5h    | TOCON                   | FB5h    | —                    | F95h    | TRISD <sup>(2)</sup> |

| FF4h    | PRODH                   | FD4h    | —                       | FB4h    | —                    | F94h    | TRISC <sup>(4)</sup> |

| FF3h    | PRODL                   | FD3h    | OSCCON <sup>*</sup>     | FB3h    | TMR3H                | F93h    | TRISB                |

| FF2h    | INTCON                  | FD2h    | LVDCON                  | FB2h    | TMR3L                | F92h    | TRISA                |

| FF1h    | INTCON2                 | FD1h    | WDTCON                  | FB1h    | T3CON                | F91h    |                      |

| FF0h    | INTCON3                 | FD0h    | RCON                    | FB0h    | —                    | F90h    |                      |

| FEFh    | INDF0 <sup>(3)</sup>    | FCFh    | TMR1H                   | FAFh    | SPBRG                | F8Fh    | —                    |

| FEEh    | POSTINC0 <sup>(3)</sup> | FCEh    | TMR1L                   | FAEh    | RCREG                | F8Eh    |                      |

| FEDh    | POSTDEC0 <sup>(3)</sup> | FCDh    | T1CON                   | FADh    | TXREG                | F8Dh    | LATE <sup>(2)</sup>  |

| FECh    | PREINC0 <sup>(3)</sup>  | FCCh    | TMR2 <sup>*</sup>       | FACh    | TXSTA                | F8Ch    | LATD <sup>(2)</sup>  |

| FEBh    | PLUSW0 <sup>(3)</sup>   | FCBh    | PR2 <sup>*</sup>        | FABh    | RCSTA                | F8Bh    | LATC <sup>(4)</sup>  |

| FEAh    | FSR0H                   | FCAh    | T2CON <sup>*</sup>      | FAAh    | —                    | F8Ah    | LATB                 |

| FE9h    | FSR0L                   | FC9h    | SSPBUF                  | FA9h    | EEADR                | F89h    | LATA                 |

| FE8h    | WREG                    | FC8h    | SSPADD                  | FA8h    | EEDATA               | F88h    | —                    |

| FE7h    | INDF1 <sup>(3)</sup>    | FC7h    | SSPSTAT                 | FA7h    | EECON2               | F87h    | —                    |

| FE6h    | POSTINC1 <sup>(3)</sup> | FC6h    | SSPCON1                 | FA6h    | EECON1               | F86h    | —                    |

| FE5h    | POSTDEC1 <sup>(3)</sup> | FC5h    | SSPCON2                 | FA5h    | —                    | F85h    | —                    |

| FE4h    | PREINC1 <sup>(3)</sup>  | FC4h    | ADRESH                  | FA4h    | —                    | F84h    | PORTE <sup>(2)</sup> |

| FE3h    | PLUSW1 <sup>(3)</sup>   | FC3h    | ADRESL                  | FA3h    | —                    | F83h    | PORTD <sup>(2)</sup> |

| FE2h    | FSR1H                   | FC2h    | ADCON0                  | FA2h    | IPR2                 | F82h    | PORTC <sup>(4)</sup> |

| FE1h    | FSR1L                   | FC1h    | ADCON1                  | FA1h    | PIR2                 | F81h    | PORTB                |

| FE0h    | BSR                     | FC0h    |                         | FA0h    | PIE2                 | F80h    | PORTA                |

\* These registers are retained to maintain compatibility with PIC18FXX2 devices; however, one or more bits are reserved in PIC18FXX39 devices. Users should not alter the values of these bits.

**Note 1:** Unimplemented registers are read as '0'.

2: This register is not available on PIC18F2X39 devices.

**3:** This is not a physical register.

4: Bits 1 and 2 are reserved; users should not alter their values.

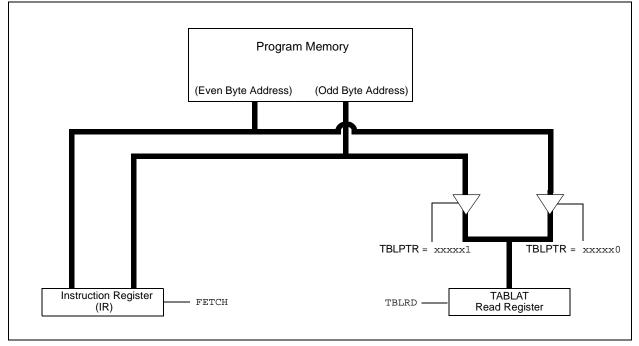

#### 5.3 Reading the FLASH Program Memory

The TBLRD instruction is used to retrieve data from program memory and place into data RAM. Table Reads from program memory are performed one byte at a time. TBLPTR points to a byte address in program space. Executing TBLRD places the byte pointed to into TABLAT. In addition, TBLPTR can be modified automatically for the next Table Read operation.

The internal program memory is typically organized by words. The Least Significant bit of the address selects between the high and low bytes of the word. Figure 5-4 shows the interface between the internal program memory and the TABLAT.

#### FIGURE 5-4: READS FROM FLASH PROGRAM MEMORY

#### EXAMPLE 5-1: READING A FLASH PROGRAM MEMORY WORD

|           | MOVLW CODE_ADDR_UPPER<br>MOVWF TBLPTRU<br>MOVLW CODE_ADDR_HIGH<br>MOVWF TBLPTRH<br>MOVLW CODE_ADDR_LOW<br>MOVWF TBLPTRL | ; Load TBLPTR with the base<br>; address of the word |

|-----------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| READ_WORD |                                                                                                                         |                                                      |

|           | TBLRD*+                                                                                                                 | ; read into TABLAT and increment                     |

|           | MOVF TABLAT, W                                                                                                          | ; get data                                           |

|           | MOVWF WORD_EVEN                                                                                                         |                                                      |

|           | TBLRD*+                                                                                                                 | ; read into TABLAT and increment                     |

|           | MOVF TABLAT, W                                                                                                          | ; get data                                           |

|           | MOVWF WORD_ODD                                                                                                          |                                                      |

|           |                                                                                                                         |                                                      |

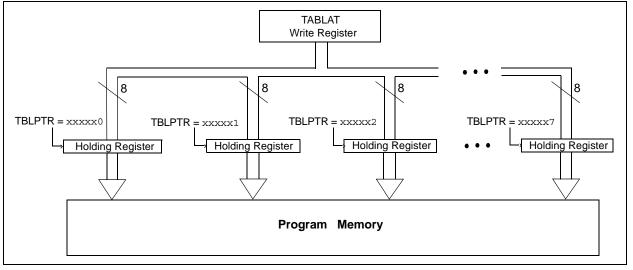

#### 5.5 Writing to FLASH Program Memory

The minimum programming block is 4 words or 8 bytes. Word or byte programming is not supported.

Table Writes are used internally to load the holding registers needed to program the FLASH memory. There are 8 holding registers used by the Table Writes for programming.

Since the Table Latch (TABLAT) is only a single byte, the TBLWT instruction has to be executed 8 times for each programming operation. All of the Table Write operations will essentially be short writes, because only the holding registers are written. At the end of updating 8 registers, the EECON1 register must be written to, to start the programming operation with a long write.

The long write is necessary for programming the internal FLASH. Instruction execution is halted while in a long write cycle. The long write will be terminated by the internal programming timer.

The EEPROM on-chip timer controls the write time. The write/erase voltages are generated by an on-chip charge pump rated to operate over the voltage range of the device for byte or word operations.

#### FIGURE 5-5: TABLE WRITES TO FLASH PROGRAM MEMORY

### 5.5.1 FLASH PROGRAM MEMORY WRITE SEQUENCE

The sequence of events for programming an internal program memory location should be:

- 1. Read 64 bytes into RAM.

- 2. Update data values in RAM as necessary.

- 3. Load Table Pointer with address being erased.

- 4. Do the row erase procedure.

- 5. Load Table Pointer with address of first byte being written.

- 6. Write the first 8 bytes into the holding registers with auto-increment (TBLWT\*+ or TBLWT+\*).

- Set EEPGD bit to point to program memory, clear the CFGS bit to access program memory, and set WREN to enable byte writes.

- 8. Disable interrupts.

- 9. Write 55h to EECON2.

- 10. Write AAh to EECON2.

- 11. Set the WR bit. This will begin the write cycle.

- 12. The CPU will stall for duration of the write (about 2 ms using internal timer).

- 13. Re-enable interrupts.

- 14. Repeat steps 6-14 seven times, to write 64 bytes.

- 15. Verify the memory (Table Read).

This procedure will require about 18 ms to update one row of 64 bytes of memory. An example of the required code is given in Example 5-3.

**Note:** Before setting the WR bit, the table pointer address needs to be within the intended address range of the 8 bytes in the holding registers.

### 9.0 I/O PORTS

Depending on the device selected, there are either three or five ports available. Some pins of the I/O ports are multiplexed with an alternate function from the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Each port has three registers for its operation. These registers are:

- TRIS register (data direction register)

- PORT register (reads the levels on the pins of the device)

- LAT register (output latch)

The data latch (LAT register) is useful for read-modifywrite operations on the value that the I/O pins are driving.

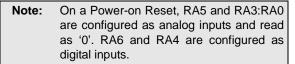

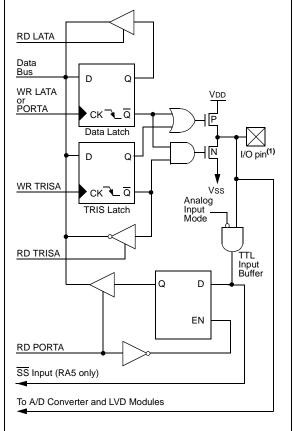

#### 9.1 PORTA, TRISA and LATA Registers

PORTA is a 7-bit wide, bi-directional port. The corresponding Data Direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a High Impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch.

The Data Latch register (LATA) is also memory mapped. Read-modify-write operations on the LATA register reads and writes the latched output value for PORTA.

The RA4 pin is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers.

The other PORTA pins are multiplexed with analog inputs and the analog VREF+ and VREF- inputs. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

#### EXAMPLE 9-1: INITIALIZING PORTA

| C | CLRF PORTA   | ; Initialize PORTA by<br>; clearing output |

|---|--------------|--------------------------------------------|

|   |              | , 5 1                                      |

|   |              | ; data latches                             |

| C | CLRF LATA    | ; Alternate method                         |

|   |              | ; to clear output                          |

|   |              | ; data latches                             |

| Ν | IOVLW 0x07   | ; Configure A/D                            |

| Ν | NOVWF ADCON1 | ; for digital inputs                       |

| Ν | NOVLW 0xCF   | ; Value used to                            |

|   |              | ; initialize data                          |

|   |              | ; direction                                |

| Ν | NOVWF TRISA  | ; Set RA<3:0> as inputs                    |

|   |              | ; RA<5:4> as outputs                       |

|   |              |                                            |

#### FIGURE 9-1:

#### BLOCK DIAGRAM OF RA3:RA0 AND RA5 PINS

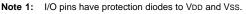

#### REGISTER 9-1: TRISE REGISTER

- n = Value at POR

|       | R-0                                          | R-0                                             | R/W-0                      | R/W-0                               | U-0        | R/W-1       | R/W-1          | R/W-1  |

|-------|----------------------------------------------|-------------------------------------------------|----------------------------|-------------------------------------|------------|-------------|----------------|--------|

|       | IBF                                          | OBF                                             | IBOV                       | PSPMODE                             |            | TRISE2      | TRISE1         | TRISE0 |

|       | bit 7                                        | ОЫ                                              | IDOV                       |                                     |            | TRIOLZ      | TRIOLT         | bit 0  |

|       |                                              |                                                 |                            |                                     |            |             |                | DILO   |

| bit 7 | 1 = A  word                                  | Buffer Full S<br>has been i<br>rd has beer      | eceived an                 | d waiting to be                     | read by th | e CPU       |                |        |

| bit 6 | 1 = The ou                                   | out Buffer Fu<br>itput buffer s<br>itput buffer | still holds a              | previously writ                     | ten word   |             |                |        |

| bit 5 | 1 = A write<br>(must                         |                                                 | /hen a prev<br>n software) | ct bit (in Micro<br>iously input wo |            | ,           |                |        |

| bit 4 | 1 = Paralle                                  | E: Parallel S<br>el Slave Por<br>al Purpose I   | t mode                     | lode Select bit                     |            |             |                |        |

| bit 3 | Unimplem                                     | nented: Rea                                     | ad as '0'                  |                                     |            |             |                |        |

| bit 2 | <b>TRISE2</b> : R<br>1 = Input<br>0 = Output | E2 Directio                                     | n Control bi               | t                                   |            |             |                |        |

| bit 1 | <b>TRISE1</b> : R<br>1 = Input<br>0 = Output | E1 Directio                                     | n Control bi               | t                                   |            |             |                |        |

| bit 0 |                                              | E0 Directio                                     | n Control bi               | t                                   |            |             |                |        |

|       | Legend:                                      |                                                 |                            |                                     |            |             |                |        |

|       | R = Reada                                    | able bit                                        | W = V                      | Nritable bit                        | U = Unim   | plemented I | bit, read as ' | 0'     |

|       | 1                                            |                                                 |                            |                                     |            |             |                |        |

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

TABLE 9-11: REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

| Name   | Bit 7        | Bit 6         | Bit 5     | Bit 4     | Bit 3 | Bit 2     | Bit 1         | Bit 0  | Value on<br>POR, BOR | Value on<br>All Other<br>RESETS |

|--------|--------------|---------------|-----------|-----------|-------|-----------|---------------|--------|----------------------|---------------------------------|

| PORTD  | Port Data    | Latch whe     | xxxx xxxx | uuuu uuuu |       |           |               |        |                      |                                 |

| LATD   | LATD Data    | a Output b    | its       |           |       |           |               |        | xxxx xxxx            | uuuu uuuu                       |

| TRISD  | PORTD D      | ata Directi   | on bits   |           |       |           |               |        | 1111 1111            | 1111 1111                       |

| PORTE  | —            | _             | —         | —         | _     | RE2       | RE1           | RE0    | 000                  | 000                             |

| LATE   | —            | _             | _         | _         | _     | LATE Data | a Output bits | 3      | xxx                  | uuu                             |

| TRISE  | IBF          | OBF           | IBOV      | PSPMODE   | _     | PORTE D   | ata Directio  | n bits | 0000 -111            | 0000 -111                       |

| INTCON | GIE/<br>GIEH | PEIE/<br>GIEL | TMR0IF    | INTOIE    | RBIE  | TMR0IF    | INTOIF        | RBIF   | 0000 000x            | 0000 000u                       |

| PIR1   | PSPIF        | ADIF          | RCIF      | TXIF      | SSPIF | _         | TMR2IF        | TMR1IF | 0000 0000            | 0000 0000                       |

| PIE1   | PSPIE        | ADIE          | RCIE      | TXIE      | SSPIE |           | TMR2IE        | TMR1IE | 0000 0000            | 0000 0000                       |

| IPR1   | PSPIP        | ADIP          | RCIP      | TXIP      | SSPIP | _         | TMR2IP        | TMR1IP | 0000 0000            | 0000 0000                       |

| ADCON1 | ADFM         | ADCS2         | —         | —         | PCFG3 | PCFG2     | PCFG1         | PCFG0  | 00 0000              | 00 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Parallel Slave Port.

| ER 16-5: | 33PCON                                                                                                                                                                                   | 2: 101559 CC                                      |               | EGISTER 2      |               | <b>'</b> ⊏)   |              |            |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|---------------|----------------|---------------|---------------|--------------|------------|--|

|          | R/W-0                                                                                                                                                                                    | R/W-0                                             | R/W-0         | R/W-0          | R/W-0         | R/W-0         | R/W-0        | R/W-0      |  |

|          | GCEN                                                                                                                                                                                     | ACKSTAT                                           | ACKDT         | ACKEN          | RCEN          | PEN           | RSEN         | SEN        |  |

|          | bit 7                                                                                                                                                                                    |                                                   |               |                |               |               |              | bit 0      |  |

| bit 7    | GCEN: G                                                                                                                                                                                  | eneral Call Er                                    | able bit (Sla | ve mode onl    | y)            |               |              |            |  |

|          |                                                                                                                                                                                          | e interrupt wh<br>al call addres                  |               | l call address | s (0000h) is  | received in   | the SSPSI    | २          |  |

| bit 6    | ACKSTAT                                                                                                                                                                                  | : Acknowledg                                      | e Status bit  | (Master Tran   | smit mode     | only)         |              |            |  |

|          |                                                                                                                                                                                          | wledge was r<br>wledge was r                      |               |                |               |               |              |            |  |

| bit 5    | ACKDT: A                                                                                                                                                                                 | kcknowledge                                       | Data bit (Ma  | ster Receive   | mode only)    |               |              |            |  |

|          | 1 = Not Ad<br>0 = Ackno                                                                                                                                                                  | cknowledge<br>wledge                              |               |                |               |               |              |            |  |

|          | Note:                                                                                                                                                                                    | Value that w the end of a                         |               | itted when th  | e user initia | tes an Ackı   | nowledge s   | equence at |  |

| bit 4    | ACKEN: A                                                                                                                                                                                 | Acknowledge                                       | Sequence E    | nable bit (Ma  | aster Receiv  | ve mode on    | ly)          |            |  |

|          | Autom                                                                                                                                                                                    | e Acknowledg<br>atically cleare                   | ed by hardwa  |                | SCL pins, a   | ind transmi   | t ACKDT da   | ata bit.   |  |

| hit 2    |                                                                                                                                                                                          | wledge seque                                      |               | modo only)     |               |               |              |            |  |

| bit 3    |                                                                                                                                                                                          | eceive Enable<br>es Receive m<br>ve IDLE          |               | mode only)     |               |               |              |            |  |

| bit 2    | PEN: STO                                                                                                                                                                                 | P Condition                                       | Enable bit (N | laster mode    | only)         |               |              |            |  |

|          |                                                                                                                                                                                          | e STOP condi<br>condition IDL                     |               | and SCL pin    | s. Automati   | cally cleare  | ed by hardw  | are.       |  |

| bit 1    | RSEN: Re                                                                                                                                                                                 | peated STAF                                       | T Condition   | Enabled bit    | (Master mod   | de only)      |              |            |  |

|          | Autom                                                                                                                                                                                    | e Repeated S                                      | ed by hardwa  | are.           | and SCL pin   | S.            |              |            |  |

| bit 0    | •                                                                                                                                                                                        | ated START c<br>.RT Condition                     |               |                | 1 L:+         |               |              |            |  |

| DILU     | In Master                                                                                                                                                                                |                                                   | Enabled/Str   | etch Enabled   |               |               |              |            |  |

|          | 1 = Initiate                                                                                                                                                                             | e START conc<br>T condition ID                    |               | A and SCL pi   | ns. Automa    | tically clear | ed by hard   | ware.      |  |

|          | In Slave m                                                                                                                                                                               |                                                   |               |                |               |               |              |            |  |

|          | <ul> <li>1 = Clock stretching is enabled for both Slave Transmit and Slave Receive (stretch en</li> <li>0 = Clock stretching is enabled for slave transmit only (Legacy mode)</li> </ul> |                                                   |               |                |               |               |              |            |  |

|          |                                                                                                                                                                                          | For bits ACK<br>mode, this bit<br>writes to the S |               |                |               |               |              |            |  |

|          | Legend:                                                                                                                                                                                  |                                                   |               |                |               |               |              |            |  |

|          | R = Reada                                                                                                                                                                                | able bit                                          | W = Wi        | ritable bit    | U = Unim      | plemented     | bit, read as | '0'        |  |

|          | 1                                                                                                                                                                                        |                                                   |               |                |               |               |              |            |  |

### REGISTER 16-5: SSPCON2: MSSP CONTROL REGISTER 2 (I<sup>2</sup>C MODE)

© 2002-2013 Microchip Technology Inc.

- n = Value at POR

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

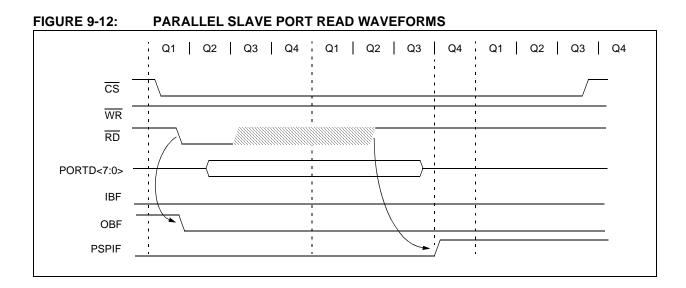

#### 17.3.2 USART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either enable bit SREN (RCSTA<5>), or enable bit CREN (RCSTA<4>). Data is sampled on the RC7/RX/DT pin on the falling edge of the clock. If enable bit SREN is set, only a single word is received. If enable bit CREN is set, the reception is continuous until CREN is cleared. If both bits are set, then CREN takes precedence.

To set up a Synchronous Master Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 17.1).

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- 4. If interrupts are desired, set enable bit RCIE.

- 5. If 9-bit reception is desired, set bit RX9.

- 6. If a single reception is required, set bit SREN. For continuous reception, set bit CREN.

- Interrupt flag bit RCIF will be set when reception is complete and an interrupt will be generated if the enable bit RCIE was set.

- 8. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREG register.

- 10. If any error occurred, clear the error by clearing bit CREN.

- 11. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

| Name   | Bit 7                | Bit 6         | Bit 5       | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>All Other<br>RESETS |

|--------|----------------------|---------------|-------------|--------|-------|--------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE/<br>GIEH         | PEIE/<br>GIEL | TMR0IE      | INTOIE | RBIE  | TMR0IF | INTOIF | RBIF   | 0000 000x            | 0000 000u                       |

| PIR1   | PSPIF <sup>(1)</sup> | ADIF          | RCIF        | TXIF   | SSPIF | -      | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| PIE1   | PSPIE <sup>(1)</sup> | ADIE          | RCIE        | TXIE   | SSPIE | -      | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| IPR1   | PSPIP <sup>(1)</sup> | ADIP          | RCIP        | TXIP   | SSPIP | _      | TMR2IP | TMR1IP | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN                 | RX9           | SREN        | CREN   | ADDEN | FERR   | OERR   | RX9D   | 0000 -00x            | 0000 -00x                       |

| RCREG  | USART R              | eceive Re     | egister     |        |       |        |        |        | 0000 0000            | 0000 0000                       |

| TXSTA  | CSRC                 | TX9           | TXEN        | SYNC   | _     | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

| SPBRG  | Baud Rate            | e Genera      | tor Registe | er     |       |        |        |        | 0000 0000            | 0000 0000                       |

#### TABLE 17-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for Synchronous Master Reception. **Note 1:** The PSPIF, PSPIE and PSPIP bits are reserved on the PIC18F2X39 devices; always maintain these bits clear.

#### FIGURE 17-8: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

#### 17.4.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical, except in the case of the SLEEP mode and bit SREN, which is a "don't care" in Slave mode.

If receive is enabled by setting bit CREN prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR register will transfer the data to the RCREG register, and if enable bit RCIE bit is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector.

To set up a Synchronous Slave Reception:

- Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. If interrupts are desired, set enable bit RCIE.

- 3. If 9-bit reception is desired, set bit RX9.

- 4. To enable reception, set enable bit CREN.

- Flag bit RCIF will be set when reception is complete. An interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing bit CREN.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

| Name   | Bit 7                  | Bit 6         | Bit 5      | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0     | Value on<br>POR, BOR | Value on<br>All Other<br>RESETS |

|--------|------------------------|---------------|------------|--------|-------|--------|--------|-----------|----------------------|---------------------------------|

| INTCON | GIE/<br>GIEH           | PEIE/<br>GIEL | TMR0IE     | INTOIE | RBIE  | TMR0IF | INTOIF | RBIF      | 0000 000x            | 0000 000u                       |

| PIR1   | PSPIF <sup>(1)</sup>   | ADIF          | RCIF       | TXIF   | SSPIF | -      | TMR2IF | TMR1IF    | 0000 0000            | 0000 0000                       |

| PIE1   | PSPIE <sup>(1)</sup>   | ADIE          | RCIE       | TXIE   | SSPIE | -      | TMR2IE | TMR1IE    | 0000 0000            | 0000 0000                       |

| IPR1   | PSPIP <sup>(1)</sup>   | ADIP          | RCIP       | TXIP   | SSPIP | -      | TMR2IP | TMR1IP    | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN                   | RX9           | SREN       | CREN   | ADDEN | FERR   | OERR   | RX9D      | 0000 -00x            | 0000 -00x                       |

| RCREG  | USART Receive Register |               |            |        |       |        |        | 0000 0000 | 0000 0000            |                                 |

| TXSTA  | CSRC                   | TX9           | TXEN       | SYNC   | —     | BRGH   | TRMT   | TX9D      | 0000 -010            | 0000 -010                       |

| SPBRG  | Baud Rate              | e Generat     | or Registe | r      |       |        |        |           | 0000 0000            | 0000 0000                       |

#### TABLE 17-11: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

Legend: x = unknown, - = unimplemented, read as '0'.

Shaded cells are not used for Synchronous Slave Reception.

Note 1: The PSPIF, PSPIE and PSPIP bits are reserved on the PIC18F2X39 devices; always maintain these bits clear.

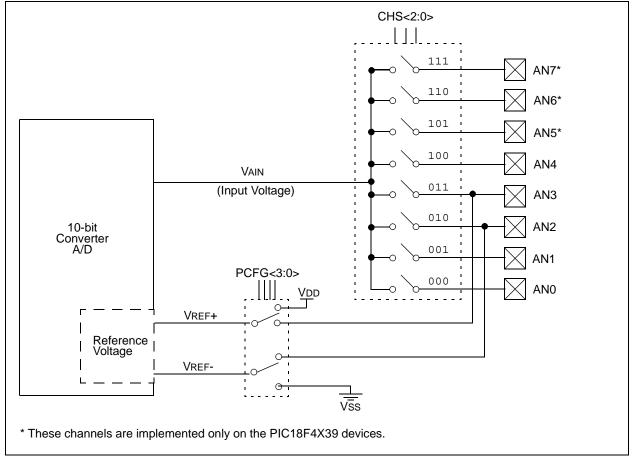

The analog reference voltage is software selectable to either the device's positive and negative supply voltage (VDD and Vss), or the voltage level on the RA3/AN3/ VREF+ pin and RA2/AN2/VREF- pin.

The A/D converter has a unique feature of being able to operate while the device is in SLEEP mode. To operate in SLEEP, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

The output of the sample and hold is the input into the converter, which generates the result via successive approximation.

A device RESET forces all registers to their RESET state. This forces the A/D module to be turned off and any conversion is aborted.

Each port pin associated with the A/D converter can be configured as an analog input (RA3 can also be a voltage reference) or as a digital I/O.

The ADRESH and ADRESL registers contain the result of the A/D conversion. When the A/D conversion is complete, the result is loaded into the ADRESH/ ADRESL registers, the GO/DONE bit (ADCON0<2>) is cleared, and A/D interrupt flag bit, ADIF is set. The block diagram of the A/D module is shown in Figure 18-1.

#### FIGURE 18-1: A/D BLOCK DIAGRAM

© 2002-2013 Microchip Technology Inc.

NOTES:

| File    | Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Default/<br>Unprogrammed<br>Value |

|---------|----------|-------|-------|-------|-------|--------|--------|--------|--------|-----------------------------------|

| 300001h | CONFIG1H | _     | _     | (1)   |       | —      | FOSC2  | FOSC1  | FOSC0  | 1010                              |

| 300002h | CONFIG2L | _     | _     | _     | _     | BORV1  | BORV0  | BOREN  | PWRTEN | 1111                              |

| 300003h | CONFIG2H | _     | _     | _     | _     | WDTPS2 | WDTPS1 | WDTPS0 | WDTEN  | 1111                              |

| 300005h | CONFIG3H | _     | —     | _     | _     | —      | —      | _      | _(1)   | 1                                 |

| 300006h | CONFIG4L | DEBUG | _     |       |       | —      | LVP    |        | STVREN | 11-1                              |

| 300008h | CONFIG5L | _     | _     | —     | -     | _(1)   | CP2    | CP1    | CP0    | 1111                              |

| 300009h | CONFIG5H | CPD   | CPB   | —     | -     | —      | —      | -      | —      | 11                                |

| 30000Ah | CONFIG6L | _     | _     | _     |       | _(1)   | WRT2   | WRT1   | WRT0   | 1111                              |

| 30000Bh | CONFIG6H | WRTD  | WRTB  | WRTC  | -     | —      | —      | -      | —      | 111                               |

| 30000Ch | CONFIG7L | _     | _     | —     | -     | _(1)   | EBTR2  | EBTR1  | EBTR0  | 1111                              |

| 30000Dh | CONFIG7H | _     | EBTRB | _     | _     | —      | _      | _      | —      | -1                                |

| 3FFFFEh | DEVID1   | DEV2  | DEV1  | DEV0  | REV4  | REV3   | REV2   | REV1   | REV0   | (2)                               |

| 3FFFFFh | DEVID2   | DEV10 | DEV9  | DEV8  | DEV7  | DEV6   | DEV5   | DEV4   | DEV3   | 0000 0100                         |

#### TABLE 20-1: CONFIGURATION BITS AND DEVICE IDS

Legend: x = unknown, u = unchanged, - = unimplemented. Shaded cells are unimplemented, read as '0'.

Note 1: Unimplemented, but reserved; maintain this bit set.

2: See Register 20-11 for DEVID1 values.

#### REGISTER 20-1: CONFIG1H: CONFIGURATION REGISTER 1 HIGH (BYTE ADDRESS 300001h)

| U-0   | U-0 | U-1 | U-0 | U-0 | R/P-0 | R/P-1 | R/P-0 |

|-------|-----|-----|-----|-----|-------|-------|-------|

| —     | —   | —   | —   | —   | FOSC2 | FOSC1 | FOSC0 |

| bit 7 |     |     |     |     |       |       | bit 0 |

- bit 7-6 Unimplemented: Read as '0'

- bit 5 Unimplemented and reserved: Maintain as '1'

- bit 4-3 Unimplemented: Read as '0'

- bit 2-0 FOSC2:FOSC0: Oscillator Selection bits

- 111 = Reserved

- 110 = HS oscillator with PLL enabled; clock frequency = (4 x Fosc)

- 101 = EC oscillator w/ OSC2 configured as RA6

- 100 = EC oscillator w/ OSC2 configured as divide-by-4 clock output

- 011 = Reserved

- 010 = HS oscillator

- 001 = Reserved

- 000 = Reserved

#### Legend:

| R = Readable bit        | P = Programmable bit | U = Unimplemented bit, read as '0'  |

|-------------------------|----------------------|-------------------------------------|

| - n = Value when device | e is unprogrammed    | u = Unchanged from programmed state |

### 20.2 Watchdog Timer (WDT)

The Watchdog Timer is a free running on-chip RC oscillator, which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKI pin. That means that the WDT will run, even if the clock on the OSC1/CLKI and OSC2/CLKO/RA6 pins of the device has been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset). If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The TO bit in the RCON register will be cleared upon a WDT time-out.

The Watchdog Timer is enabled/disabled by a device configuration bit. If the WDT is enabled, software execution may not disable this function. When the WDTEN configuration bit is cleared, the SWDTEN bit enables/ disables the operation of the WDT.

The WDT time-out period values may be found in the Electrical Specifications (Section 23.0) under parameter D031. Values for the WDT postscaler may be assigned using the configuration bits.

- Note 1: The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT and prevent it from timing out and generating a device RESET condition.

- 2: When a CLRWDT instruction is executed and the postscaler is assigned to the WDT, the postscaler count will be cleared, but the postscaler assignment is not changed.

#### 20.2.1 CONTROL REGISTER

Register 20-13 shows the WDTCON register. This is a readable and writable register, which contains a control bit that allows software to override the WDT enable configuration bit, only when the configuration bit has disabled the WDT.

#### REGISTER 20-13: WDTCON REGISTER

#### bit 7-1 Unimplemented: Read as '0'

bit 0

SWDTEN: Software Controlled Watchdog Timer Enable bit

- 1 = Watchdog Timer is on

- Watchdog Timer is turned off if the WDTEN configuration bit in the configuration register = 0

| Legend:                            |                    |

|------------------------------------|--------------------|

| R = Readable bit                   | W = Writable bit   |

| U = Unimplemented bit, read as '0' | - n = Value at POR |

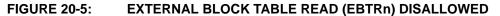

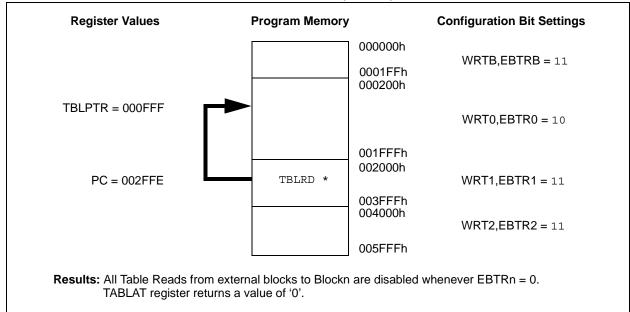

#### FIGURE 20-6: EXTERNAL BLOCK TABLE READ (EBTRn) ALLOWED

| Syntax:[ label ]IORLWkOperands: $0 \le k \le 255$ Operation:(W) .OR. $k \rightarrow W$ Status Affected:N, ZEncoding: $0000$ $1001$ $kkkk$ Description:The contents of W are OR'ed with the eight-bit literal 'k'. The result placed in W.Words:1 |                            |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--|--|--|--|--|

| Operation: $(W) \cdot OR. k \rightarrow W$ Status Affected:N, ZEncoding:0000 1001 kkkk kkkDescription:The contents of W are OR'ed with the eight-bit literal 'k'. The result placed in W.                                                        |                            |  |  |  |  |  |

| Status Affected:       N, Z         Encoding:       0000       1001       kkkk       kkkk         Description:       The contents of W are OR'ed with the eight-bit literal 'k'. The result placed in W.                                         |                            |  |  |  |  |  |

| Encoding:       0000       1001       kkkk       kkk         Description:       The contents of W are OR'ed with eight-bit literal 'k'. The result placed in W.                                                                                  | (W) .OR. $k \rightarrow W$ |  |  |  |  |  |

| Description: The contents of W are OR'ed wi<br>the eight-bit literal 'k'. The result<br>placed in W.                                                                                                                                             | N, Z                       |  |  |  |  |  |

| the eight-bit literal 'k'. The result placed in W.                                                                                                                                                                                               | k                          |  |  |  |  |  |

| Words: 1                                                                                                                                                                                                                                         |                            |  |  |  |  |  |

|                                                                                                                                                                                                                                                  |                            |  |  |  |  |  |

| Cycles: 1                                                                                                                                                                                                                                        | 1                          |  |  |  |  |  |

| Q Cycle Activity:                                                                                                                                                                                                                                |                            |  |  |  |  |  |

| Q1 Q2 Q3 Q4                                                                                                                                                                                                                                      |                            |  |  |  |  |  |

| Decode Read Process Write to V<br>literal 'k' Data                                                                                                                                                                                               | V                          |  |  |  |  |  |

| Example: IORLW 0x35                                                                                                                                                                                                                              |                            |  |  |  |  |  |

| Before Instruction                                                                                                                                                                                                                               |                            |  |  |  |  |  |

| W = 0x9A                                                                                                                                                                                                                                         |                            |  |  |  |  |  |

| After Instruction                                                                                                                                                                                                                                |                            |  |  |  |  |  |

| W = 0xBF                                                                                                                                                                                                                                         |                            |  |  |  |  |  |

| IORWF             | Inclusive                                           | OR W with                                                                                              | f                                              |

|-------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------------------------|

| Syntax:           | [label]                                             | ORWF f[                                                                                                | ,d [,a]                                        |

| Operands:         | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$ | 5                                                                                                      |                                                |

| Operation:        | (W) .OR. (                                          | f) $\rightarrow$ dest                                                                                  |                                                |

| Status Affected:  | N, Z                                                |                                                                                                        |                                                |

| Encoding:         | 0001                                                | 00da ff                                                                                                | ff ffff                                        |

|                   | register 'f'<br>Access Ba<br>riding the I           | esult is place<br>(default). If '<br>ank will be se<br>BSR value. I<br>vill be selecte<br>e (default). | a' is 0, the<br>elected, ove<br>f 'a' = 1, the |

| Words:            | 1                                                   |                                                                                                        |                                                |

| Cycles:           | 1                                                   |                                                                                                        |                                                |

| Q Cycle Activity: |                                                     |                                                                                                        |                                                |

|                   | Q2                                                  | Q3                                                                                                     | Q4                                             |

| Q1                |                                                     |                                                                                                        | Muite te                                       |

| Q1<br>Decode      | Read<br>register 'f'                                | Process<br>Data                                                                                        | Write to destination                           |

|                   | register 'f'                                        |                                                                                                        | destination                                    |

| RESULT         | =   | 0x13 |

|----------------|-----|------|

| W              | =   | 0x91 |

| After Instruct | ion |      |

| RESULT = | 0x13 |

|----------|------|

| W =      | 0x93 |

NOTES:

| Programming, Device Instructions2 | 11       |

|-----------------------------------|----------|

| PSP.See Parallel Slave Port.      |          |

| Pulse Width Modulation (PWM)1     | 23       |

| Pulse Width Modulation. See PWM.  |          |

| PUSH2                             | 40       |

| PWM                               |          |

| Associated Registers1             | 24       |

| CCPR1H:CCPR1L Registers1          | 23       |

|                                   | 20       |

| Duty Cycle1                       | 24       |

|                                   | 24       |

| Duty Cycle1                       | 24<br>23 |

### Q

| Q Clock |  | 124 |

|---------|--|-----|

|---------|--|-----|

| R                                                                                |              |

|----------------------------------------------------------------------------------|--------------|

| RAM. See Data Memory                                                             |              |

| RCALL                                                                            | 241          |

| RCSTA Register                                                                   |              |

| SPEN Bit                                                                         | 165          |

| Register File                                                                    |              |

| Registers                                                                        |              |

| ADCON0 (A/D Control 0)                                                           |              |

| ADCON1 (A/D Control 1)                                                           |              |

| CCP1CON and CCP2CON (PWM Control)                                                |              |

| CONFIG1H (Configuration 1 High)                                                  |              |

| CONFIG2H (Configuration 2 High)                                                  |              |

| CONFIG2L (Configuration 2 Low)                                                   |              |

| CONFIG4L (Configuration 4 Low)                                                   |              |

| CONFIG5H (Configuration 5 High)                                                  |              |

| CONFIG5L (Configuration 5 Low)                                                   |              |

| CONFIG6H (Configuration 6 High)                                                  |              |

| CONFIG6L (Configuration 6 Low)                                                   |              |

| CONFIG7H (Configuration 7 High)                                                  |              |

| CONFIG7L (Configuration 7 Low)                                                   |              |

| DEVID1 (Device ID 1)                                                             |              |

| DEVID2 (Device ID 2)                                                             |              |

| EECON1 (Data EEPROM Control 1)                                                   |              |

| File Summary                                                                     |              |

| INTCON (Interrupt Control)                                                       |              |

| INTCON2 (Interrupt Control 2)                                                    |              |

| INTCON3 (Interrupt Control 3)                                                    |              |

| IPR1 (Peripheral Interrupt Priority 1)<br>IPR2 (Peripheral Interrupt Priority 2) | 70           |

|                                                                                  |              |

| LVDCON (LVD Control)<br>PIE1 (Peripheral Interrupt Enable 1)                     |              |

| PIE2 (Peripheral Interrupt Enable 2)                                             |              |

|                                                                                  |              |

| PIR1 (Peripheral Interrupt Request 1)<br>PIR2 (Peripheral Interrupt Request 2)   |              |

| RCON (Register Control)                                                          | ۲۵۲۵<br>۵۵   |

| RCON (RESET Control)                                                             |              |

| RCSTA (Receive Status and Control)                                               |              |

| SSPCON1 (MSSP Control 1)                                                         | 107          |

| SPI Mode                                                                         | 127          |

| SSPCON1 (MSSP Control 1), I <sup>2</sup> C Mode                                  | ، 127<br>136 |

| SSPCON2 (MSSP Control 2), I <sup>2</sup> C Mode                                  | 130          |

| SSPSTAT (MSSP Status)                                                            |              |

| SPI Mode                                                                         | 126          |

| SSPSTAT (MSSP Status), I <sup>2</sup> C Mode                                     | 120          |

| STATUS                                                                           |              |

| STKPTR (Stack Pointer)                                                           | -            |

| T0CON (Timer0 Control)                                                           |              |

| T1CON (Timer 1 Control)                                                          |              |

| T2CON (Timer 2 Control)                                                          |              |

| T3CON (Timer3 Control)                                                           |              |

| TRISE                                                                            |              |

|                                                                                  |              |

| TXSTA (Transmit Status and Control) |         |

|-------------------------------------|---------|

| WDTCON (Watchdog Timer Control)     |         |

| RESET                               |         |

| Brown-out Reset (BOR)               |         |

| MCLR Reset (During SLEEP)           | 23      |

| MCLR Reset (Normal Operation)       |         |

| Oscillator Start-up Timer (OST)     |         |

| Power-on Reset (POR)                |         |

| Power-up Timer (PWRT)               | · · · · |

| Programmable Brown-out Reset (BOR)  |         |

| RESET Instruction                   |         |

| Stack Full Reset                    | -       |

| Stack Underflow Reset               |         |

| Watchdog Timer (WDT) Reset          |         |

| RETFIE                              |         |

| RETLW                               |         |

| RETURN                              |         |

| Return Address Stack                |         |

| Associated Registers                |         |

| Pointer (STKPTR)                    |         |

| Top-of-Stack Access                 |         |

| Revision History                    |         |

| ,                                   |         |

| RLCF                                |         |

| RLNCF                               |         |

| RRCF                                |         |

| RRNCF                               |         |

### S