Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I²C, SPI, UART/USART                                                      |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 32                                                                        |

| Program Memory Size        | 24KB (12K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 1408 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

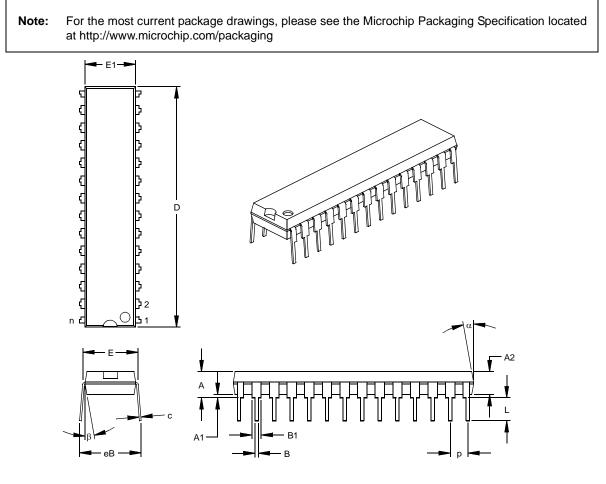

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf4539-i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-2: | PIC18F2X39 PINOUT I/O DESCRIPTIONS (CONTINUED) | ) |

|------------|------------------------------------------------|---|

|------------|------------------------------------------------|---|

| Pin Name         | Pin N    | umber     | Pin                        | Buffer | Description                                               |

|------------------|----------|-----------|----------------------------|--------|-----------------------------------------------------------|

| Pin Name         | DIP      | SOIC      | SOIC Type Type Description |        | Description                                               |

|                  |          |           |                            |        | PORTB is a bi-directional I/O port. PORTB can be software |

|                  |          |           |                            |        | programmed for internal weak pull-ups on all inputs.      |

| RB0/INT0         | 21       | 21        |                            |        |                                                           |

| RB0              |          |           | I/O                        | TTL    | Digital I/O.                                              |

| INT0             |          |           | I                          | ST     | External interrupt 0.                                     |

| RB1/INT1         | 22       | 22        |                            |        |                                                           |

| RB1              |          |           | I/O                        | TTL    | Digital I/O.                                              |

| INT1             |          |           | I                          | ST     | External interrupt 1.                                     |

| RB2/INT2         | 23       | 23        |                            |        |                                                           |

| RB2              |          |           | I/O                        | TTL    | Digital I/O.                                              |

| INT2             |          |           | I                          | ST     | External interrupt 2.                                     |

| RB3              | 24       | 24        | I/O                        | TTL    | Digital I/O.                                              |

| RB4              | 25       | 25        | I/O                        | TTL    | Digital I/O.                                              |

|                  |          |           |                            |        | Interrupt-on-change pin.                                  |

| RB5/PGM          | 26       | 26        |                            |        |                                                           |

| RB5              |          |           | I/O                        | TTL    | Digital I/O. Interrupt-on-change pin.                     |

| PGM              |          |           | I/O                        | ST     | Low Voltage ICSP programming enable pin.                  |

| RB6/PGC          | 27       | 27        |                            |        |                                                           |

| RB6              |          |           | I/O                        | TTL    | Digital I/O. Interrupt-on-change pin.                     |

| PGC              |          |           | I/O                        | ST     | In-Circuit Debugger and ICSP programming clock pin.       |

| RB7/PGD          | 28       | 28        |                            |        |                                                           |

| RB7              |          |           | I/O                        | TTL    | Digital I/O. Interrupt-on-change pin.                     |

| PGD              |          |           | I/O                        | ST     | In-Circuit Debugger and ICSP programming data pin.        |

| Legend: TTL = TT | L compat | tible inp | ut                         |        | CMOS = CMOS compatible input or output                    |

ST = Schmitt Trigger input with CMOS levels O = Output OD = Open Drain (no P diode to VDD)

= Input

Р = Power

L

#### 6.3 Reading the Data EEPROM Memory

To read a data memory location, the user must write the address to the EEADR register, clear the EEPGD control bit (EECON1<7>), clear the CFGS control bit

EXAMPLE 6-1: DATA EEPROM READ

| MOVLW | DATA_EE_ADDR  | ;                                            |

|-------|---------------|----------------------------------------------|

| MOVWF | EEADR         | ; Data Memory Address to read                |

| BCF   | EECON1, EEPGD | ; Point to DATA memory                       |

| BCF   | EECON1, CFGS  | ; Access program FLASH or Data EEPROM memory |

| BSF   | EECON1, RD    | ; EEPROM Read                                |

| MOVF  | EEDATA, W     | ; W = EEDATA                                 |

|       |               |                                              |

#### 6.4 Writing to the Data EEPROM Memory

To write an EEPROM data location, the address must first be written to the EEADR register and the data written to the EEDATA register. Then, the sequence in Example 6-2 must be followed to initiate the write cycle.

The write will not initiate if the above sequence is not exactly followed (write 55h to EECON2, write AAh to EECON2, then set WR bit) for each byte. It is strongly recommended that interrupts be disabled during this code segment.

Additionally, the WREN bit in EECON1 must be set to enable writes. This mechanism prevents accidental writes to data EEPROM due to unexpected code exe-

| cution (i.e., runaway programs). The WREN bit should |

|------------------------------------------------------|

| be kept clear at all times, except when updating the |

| EEPROM. The WREN bit is not cleared by hardware.     |

(EECON1<6>), and then set control bit RD

(EECON1<0>). The data is available for the very next

instruction cycle; therefore, the EEDATA register can

be read by the next instruction. EEDATA will hold this

value until another read operation, or until it is written to

by the user (during a write operation).

After a write sequence has been initiated, EECON1, EEADR and EDATA cannot be modified. The WR bit will be inhibited from being set unless the WREN bit is set. The WREN bit must be set on a previous instruction. Both WR and WREN cannot be set with the same instruction.

At the completion of the write cycle, the WR bit is cleared in hardware and the EEPROM Write Complete Interrupt Flag bit (EEIF) is set. The user may either enable this interrupt, or poll this bit. EEIF must be cleared by software.

|                      | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>BCF<br>BCF<br>BSF | EEADR<br>DATA_EE_DATA<br>EEDATA<br>EECON1, EEPGD<br>EECON1, CFGS<br>EECON1, WREN | ; Data Memory Value to write<br>; Point to DATA memory<br>; Access program FLASH or Data EEPROM memory<br>; Enable writes |

|----------------------|-------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Required<br>Sequence |                                                       | INTCON, GIE<br>55h<br>EECON2<br>AAh                                              | ; Disable interrupts<br>;<br>; Write 55h<br>;                                                                             |

|                      | MOVWF<br>BSF<br>BSF                                   |                                                                                  | ; Write AAh<br>; Set WR bit to begin write<br>; Enable interrupts                                                         |

|                      | •<br>•                                                |                                                                                  | ; user code execution                                                                                                     |

|                      | •<br>BCF                                              | EECON1, WREN                                                                     | ; Disable writes on write complete (EEIF set)                                                                             |

EXAMPLE 6-2: DATA EEPROM WRITE

Example 7-3 shows the sequence to do a 16 x 16 unsigned multiply. Equation 7-1 shows the algorithm that is used. The 32-bit result is stored in four registers, RES3:RES0.

#### EQUATION 7-1: 16 x 16 UNSIGNED MULTIPLICATION ALGORITHM

| RES3:RES0 |   | ARG1H:ARG1L • ARG2H:ARG2L                |

|-----------|---|------------------------------------------|

|           | = | $(ARG1H \bullet ARG2H \bullet 2^{16}) +$ |

|           |   | $(ARG1H \bullet ARG2L \bullet 2^8) +$    |

|           |   | $(ARG1L \bullet ARG2H \bullet 2^8) +$    |

|           |   | (ARG1L • ARG2L)                          |

#### EXAMPLE 7-3: 16 x 16 UNSIGNED MULTIPLY ROUTINE

|   | MOVF   | ARG1L, | W    |   |                  |

|---|--------|--------|------|---|------------------|

|   | MULWF  | -      |      | ; | ARG1L * ARG2L -> |

|   |        |        |      | ; | PRODH: PRODL     |

|   | MOVFF  | PRODH, | RES1 | ; |                  |

|   | MOVFF  | PRODL, | RES0 | ; |                  |

| ; |        |        |      |   |                  |

|   | MOVF   | ARG1H, | W    |   |                  |

|   | MULWF  | ARG2H  |      | ; | ARG1H * ARG2H -> |

|   |        |        |      | ; | PRODH: PRODL     |

|   | MOVFF  | PRODH, | RES3 | ; |                  |

|   | MOVFF  | PRODL, | RES2 | ; |                  |

| ; |        |        |      |   |                  |

|   | MOVF   | ARG1L, | W    |   |                  |

|   | MULWF  | ARG2H  |      |   | ARG1L * ARG2H -> |

|   |        |        |      | ; | PRODH: PRODL     |

|   |        | PRODL, |      | ; |                  |

|   |        | RES1,  |      | - | Add cross        |

|   |        | PRODH, |      |   | products         |

|   |        | RES2,  | F.   | ; |                  |

|   | CLRF   |        |      | ; |                  |

|   | ADDWFC | RES3,  | F.   | ; |                  |

| ; | MOVE   | 700111 | 147  |   |                  |

|   | MULWF  | ARG1H, | W    | ; | ARG1H * ARG2L -> |

|   | MOLWF  | AKGZL  |      | ' | PRODH: PRODL     |

|   | MOVF   | PRODL, | TAT  | ' | I KODII. FKODU   |

|   | ADDWF  | -      |      | ; | Add cross        |

|   | MOVF   |        |      |   | products         |

|   |        | RES2,  |      | ; | F = 1 20000      |

|   | CLRF   |        | -    | ; |                  |

|   |        | RES3,  | F    | ; |                  |

|   |        | /      | -    | ' |                  |

Example 7-4 shows the sequence to do a 16 x 16 signed multiply. Equation 7-2 shows the algorithm used. The 32-bit result is stored in four registers, RES3:RES0. To account for the sign bits of the arguments, each argument pairs Most Significant bit (MSb) is tested and the appropriate subtractions are done.

#### EQUATION 7-2: 16 x 16 SIGNED MULTIPLICATION ALGORITHM

#### RES3:RES0

- = ARG1H:ARG1L ARG2H:ARG2L

- =  $(ARG1H \bullet ARG2H \bullet 2^{16}) +$  $(ARG1H \bullet ARG2L \bullet 2^{8}) +$  $(ARG1L \bullet ARG2H \bullet 2^{8}) +$  $(ARG1L \bullet ARG2L) +$  $(-1 \bullet ARG2H < 7 > \bullet ARG1H: ARG1L \bullet 2^{16}) +$  $(-1 \bullet ARG1H < 7 > \bullet ARG2H: ARG2L \bullet 2^{16})$

### EXAMPLE 7-4: 16 x 16 SIGNED

### MULTIPLY ROUTINE

|     | MOVF     | ARG1L,           | W    |   |                   |

|-----|----------|------------------|------|---|-------------------|

|     | MULWF    | ARG2L            |      | ; | ARG1L * ARG2L ->  |

|     |          |                  |      | ; | PRODH: PRODL      |

|     | MOVFF    | PRODH,           | RES1 | ; |                   |

|     | MOVFF    | PRODL,           | RES0 | ; |                   |

| ;   |          |                  |      |   |                   |

|     | MOVF     | ARG1H,           | W    |   |                   |

|     | MULWF    | ARG2H            |      | ; | ARG1H * ARG2H ->  |

|     |          |                  |      | ; | PRODH: PRODL      |

|     | MOVFF    | PRODH,           | RES3 | ; |                   |

|     | MOVFF    | PRODL,           | RES2 |   |                   |

| ;   |          |                  |      | - |                   |

|     | MOVF     | ARG1L,           | W    |   |                   |

|     | MULWF    | ARG2H            |      | ; | ARG1L * ARG2H ->  |

|     |          |                  |      |   | PRODH: PRODL      |

|     | MOVF     | PRODL,           | W    | ; |                   |

|     | ADDWF    | RES1,            |      |   | Add cross         |

|     | MOVF     | PRODH,           |      |   | products          |

|     |          | RES2,            |      | ; | F                 |

|     | CLRF     | WREG             | -    | ; |                   |

|     |          | RES3,            | F    | ; |                   |

|     | 11DDm1 C | ныст,            | 1    | ' |                   |

| ;   | MOVF     | ARG1H,           | TAT. |   |                   |

|     | MULWF    | ARG111,<br>ARG2L | **   | ; | ARG1H * ARG2L ->  |

|     | MOTIML   | AKGZU            |      |   | PRODH: PRODL      |

|     | MOVF     | זמסממ            | TAT  |   | PRODH: PRODL      |

|     | ADDWF    | PRODL,<br>RES1,  |      | ; | Add cross         |

|     | MOVF     | PRODH,           |      |   |                   |

|     |          |                  |      |   | products          |

|     | CLRF     | RES2,<br>WREG    | г    | ; |                   |

|     |          | RES3,            | 77   | ; |                   |

|     | ADDWFC   | RESS,            | г    | ; |                   |

| ;   | DWRCC    | ADCOLL           | 7    |   | ADCOIL ADCOL DOCO |

|     | BTFSS    | ARG2H,           |      |   | ARG2H:ARG2L neg?  |

|     | BRA      | SIGN_AF          |      |   | no, check ARG1    |

|     | MOVF     | ARG1L,           | W    | ; |                   |

|     | SUBWF    | RES2             |      | ; |                   |

|     | MOVF     | ARG1H,           | W    | ; |                   |

|     | SUBWFB   | KES3             |      |   |                   |

| ;   | NI NDO1  |                  |      |   |                   |

| SIG | N_ARG1   | 10011            | -    |   |                   |

|     |          | ARG1H,           |      |   | ARG1H:ARG1L neg?  |

|     | BRA      | CONT_CC          |      | ; | no, done          |

|     | MOVF     | ARG2L,           | W    | ; |                   |

|     | SUBWF    | RES2             |      | ; |                   |

|     | MOVF     | ARG2H,           | W    | ; |                   |

|     | SUBWFB   | RES3             |      |   |                   |

| ;   |          |                  |      |   |                   |

| CON | T_CODE   |                  |      |   |                   |

|     | :        |                  |      |   |                   |

|     |          |                  |      | _ |                   |

#### 8.4 IPR Registers

bit

bit

bit

bit

bit

bit bit

bit

The IPR registers contain the individual priority bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are two Peripheral Interrupt Priority registers (IPR1, IPR2). The operation of the priority bits requires that the Interrupt Priority Enable (IPEN) bit be set.

For PIC18FXX39 devices, the Motor Control kernel requires that the Timer2 to PR2 match interrupt be the only high priority interrupt. Failure to do this may result in unpredictable operation of the kernel or the entire microcontroller.

In practical terms, this means:

- Interrupt priority levels are enabled (IPEN = 1);

- High priority interrupts are enabled (INTCON<7> = 1);

- Timer2 interrupt is enabled and set as high priority (PIE1<1> and IPR<1> = 1); and

- all other interrupts are disabled (INTCON or PIR bits = 0), or set as low priority (IPR bits = 0).

- Note: Configuring the interrupts is automatically done by the API method void ProMPT\_Init (PWMfrequency). It is the user's responsibility to make certain that this method is called at the very beginning of the application.

#### REGISTER 8-8: IPR1: PERIPHERAL INTERRUPT PRIORITY REGISTER 1

| R/W-1                                             | R/W-1                                 | R/W-1               | R/W-1               | R/W-1                | U-1   | R/W-1                 | R/W-1                 |

|---------------------------------------------------|---------------------------------------|---------------------|---------------------|----------------------|-------|-----------------------|-----------------------|

| PSPIP <sup>(1</sup>                               | <sup>2)</sup> ADIP <sup>(2)</sup>     | RCIP <sup>(2)</sup> | TXIP <sup>(2)</sup> | SSPIP <sup>(2)</sup> | _     | TMR2IP <sup>(3)</sup> | TMR1IP <sup>(2)</sup> |

| bit 7                                             |                                       |                     |                     |                      |       |                       | bit 0                 |

| <b>PSPIP<sup>(1,</sup></b><br>1 = High<br>0 = Low |                                       | ave Port Rea        | d/Write Inte        | errupt Priority      | / bit |                       |                       |

|                                                   | A/D Converte<br>priority              | r Interrupt Pi      | iority bit          |                      |       |                       |                       |

| <b>RCIP<sup>(2)</sup>:</b><br>1 = High<br>0 = Low |                                       | ive Interrupt       | Priority bit        |                      |       |                       |                       |

| <b>TXIP<sup>(2)</sup>:</b><br>1 = High<br>0 = Low |                                       | mit Interrupt       | Priority bit        |                      |       |                       |                       |

| <b>SSPIP<sup>(2)</sup></b><br>1 = High<br>0 = Low |                                       | hronous Ser         | ial Port Inte       | errupt Priority      | v bit |                       |                       |

| Unimple                                           | mented: Rea                           | d as '1'            |                     |                      |       |                       |                       |

| -                                                 | <sup>3)</sup> : TMR2 to P<br>priority |                     | terrupt Prio        | rity bit             |       |                       |                       |

| <b>TMR1IP</b><br>1 = High<br>0 = Low              | • •                                   | rflow Interru       | ot Priority b       | it                   |       |                       |                       |

| Note                                              | 1: This bit is r                      | eserved on          | PIC18F2X3           | 9 devices.           |       |                       |                       |

|                                                   | 2: Maintain th                        | is bit cleared      | d (= 0).            |                      |       |                       |                       |

|                                                   |                                       | eserved for u       |                     |                      |       |                       |                       |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented I  | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

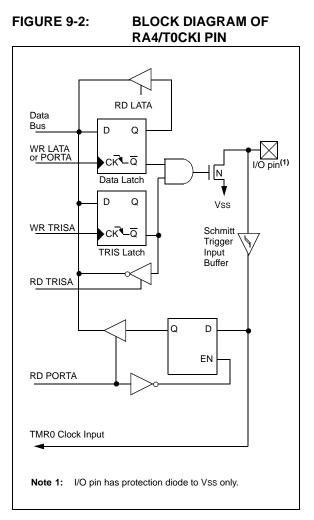

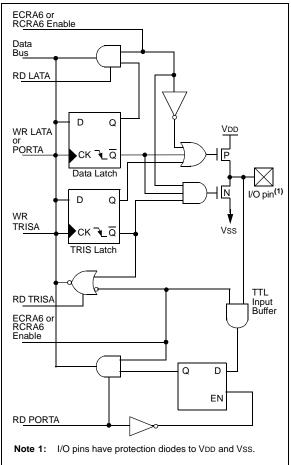

#### FIGURE 9-3: BLOCK DIAGRAM OF RA6 PIN

#### 16.4.4 CLOCK STRETCHING

Both 7- and 10-bit Slave modes implement automatic clock stretching during a transmit sequence.

The SEN bit (SSPCON2<0>) allows clock stretching to be enabled during receives. Setting SEN will cause the SCL pin to be held low at the end of each data receive sequence.

#### 16.4.4.1 Clock Stretching for 7-bit Slave Receive Mode (SEN = 1)

In 7-bit Slave Receive mode, <u>on the falling edge of the</u> ninth clock at the end of the ACK sequence, if the BF bit is set, the CKP bit in the SSPCON1 register is automatically cleared, forcing the SCL output to be held low. The CKP being cleared to '0' will assert the SCL line low. The CKP bit must be set in the user's ISR before reception is allowed to continue. By holding the SCL line low, the user has time to service the ISR and read the contents of the SSPBUF before the master device can initiate another receive sequence. This will prevent buffer overruns from occurring (see Figure 16-13).

- Note 1: If the user reads the contents of the SSPBUF before the falling edge of the ninth clock, thus clearing the BF bit, the CKP bit will not be cleared and clock stretching will not occur.

- 2: The CKP bit can be set in software, regardless of the state of the BF bit. The user should be careful to clear the BF bit in the ISR before the next receive sequence, in order to prevent an overflow condition.

#### 16.4.4.2 Clock Stretching for 10-bit Slave Receive Mode (SEN = 1)

In 10-bit Slave Receive mode, during the address sequence, clock stretching automatically takes place but CKP is not cleared. During this time, if the UA bit is set after the ninth clock, clock stretching is initiated. The UA bit is set after receiving the upper byte of the 10-bit address, and following the receive of the second byte of the 10-bit address with the R/W bit cleared to '0'. The release of the clock line occurs upon updating SSPADD. Clock stretching will occur on each data receive sequence, as described in 7-bit mode.

**Note:** If the user polls the UA bit and clears it by updating the SSPADD register before the falling edge of the ninth clock occurs, and if the user hasn't cleared the BF bit by reading the SSPBUF register before that time, then the CKP bit will still NOT be asserted low. Clock stretching on the basis of the state of the BF bit only occurs during a data sequence, not an address sequence.

#### 16.4.4.3 Clock Stretching for 7-bit Slave Transmit Mode

7-bit Slave Transmit mode implements clock stretching by clearing the CKP bit after the falling edge of the ninth clock, if the BF bit is clear. This occurs, regardless of the state of the SEN bit.

The user's ISR must set the CKP bit before transmission is allowed to continue. By holding the SCL line low, the user has time to service the ISR and load the contents of the SSPBUF before the master device can initiate another transmit sequence (see Figure 16-9).

| Note 1: If the user loads the contents of SSPBUF,                             |

|-------------------------------------------------------------------------------|

| setting the BF bit before the falling edge of                                 |

| the ninth clock, the CKP bit will not be                                      |

| cleared and clock stretching will not occur.                                  |

| 2: The CKP bit can be set in software, regardless of the state of the BF bit. |

#### 16.4.4.4 Clock Stretching for 10-bit Slave Transmit Mode

In 10-bit Slave Transmit mode, clock stretching is controlled during the first two address sequences by the state of the UA bit, just as it is in 10-bit Slave Receive mode. The first two addresses are followed by a third address sequence, which contains the high order bits of the 10-bit address and the R/W bit set to '1'. After the third address sequence is performed, the UA bit is not set, the module is now configured in Transmit mode, and clock stretching is controlled by the BF flag, as in 7-bit Slave Transmit mode (see Figure 16-11).

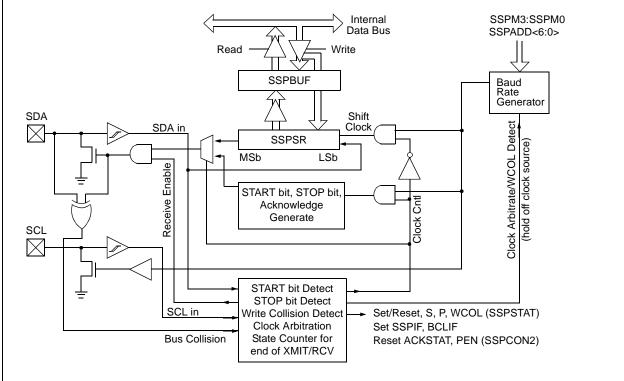

#### 16.4.6 MASTER MODE

Master mode is enabled by setting and clearing the appropriate SSPM bits in SSPCON1 and by setting the SSPEN bit. In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware.

Master mode of operation is supported by interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared from a RESET or when the MSSP module is disabled. Control of the  $l^2C$  bus may be taken when the P bit is set or the bus is IDLE, with both the S and P bits clear.

In Firmware Controlled Master mode, user code conducts all  $I^2C$  bus operations based on START and STOP bit conditions.

Once Master mode is enabled, the user has six options.

- 1. Assert a START condition on SDA and SCL.

- 2. Assert a Repeated START condition on SDA and SCL.

- 3. Write to the SSPBUF register initiating transmission of data/address.

- 4. Configure the  $I^2C$  port to receive data.

- 5. Generate an Acknowledge condition at the end of a received byte of data.

- 6. Generate a STOP condition on SDA and SCL.

Note: The MSSP Module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a START condition and immediately write the SSPBUF register to initiate transmission before the START condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur.

The following events will cause SSP interrupt flag bit, SSPIF, to be set (SSP interrupt if enabled):

- START condition

- STOP condition

- · Data transfer byte transmitted/received

- Acknowledge Transmit

- Repeated START

### FIGURE 16-16: MSSP BLOCK DIAGRAM (I<sup>2</sup>C MASTER MODE)

© 2002-2013 Microchip Technology Inc.

#### 16.4.6.1 I<sup>2</sup>C Master Mode Operation

The master device generates all of the serial clock pulses and the START and STOP conditions. A transfer is ended with a STOP condition, or with a Repeated START condition. Since the Repeated START condition is also the beginning of the next serial transfer, the  $I^2C$  bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an Acknowledge bit is received. START and STOP conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the R/W bit. In this case, the R/W bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate the receive bit. Serial data is received via SDA, while SCL outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an Acknowledge bit is transmitted. START and STOP conditions indicate the beginning and end of transmission.

The baud rate generator used for the SPI mode operation is used to set the SCL clock frequency for either 100 kHz, 400 kHz or 1 MHz  $I^2C$  operation. See Section 16.4.7 ("Baud Rate Generator"), for more detail. A typical transmit sequence would go as follows:

- 1. The user generates a START condition by setting the START enable bit, SEN (SSPCON2<0>).

- SSPIF is set. The MSSP module will wait the required start time before any other operation takes place.

- 3. The user loads the SSPBUF with the slave address to transmit.

- 4. Address is shifted out the SDA pin until all 8 bits are transmitted.

- 5. The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register (SSPCON2<6>).

- 6. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- 7. The user loads the SSPBUF with eight bits of data.

- 8. Data is shifted out the SDA pin until all 8 bits are transmitted.

- The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register (SSPCON2<6>).

- 10. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- 11. The user generates a STOP condition by setting the STOP enable bit PEN (SSPCON2<2>).

- 12. Interrupt is generated once the STOP condition is complete.

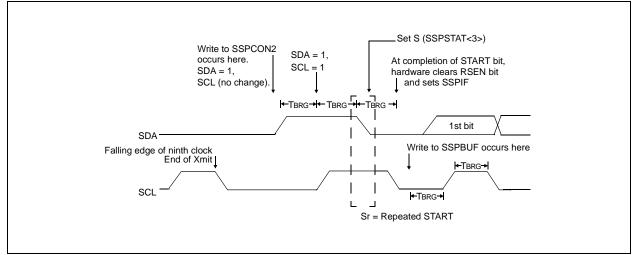

#### 16.4.9 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated START condition occurs when the RSEN bit (SSPCON2<1>) is programmed high and the  $I^2C$ logic module is in the IDLE state. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the baud rate generator is loaded with the contents of SSPADD<5:0> and begins counting. The SDA pin is released (brought high) for one baud rate generator count (TBRG). When the baud rate generator times out, if SDA is sampled high, the SCL pin will be de-asserted (brought high). When SCL is sampled high, the baud rate generator is reloaded with the contents of SSPADD<6:0> and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG while SCL is high. Following this, the RSEN bit (SSPCON2<1>) will be automatically cleared and the baud rate generator will not be reloaded, leaving the SDA pin held low. As soon as a START condition is detected on the SDA and SCL pins, the S bit (SSPSTAT<3>) will be set. The SSPIF bit will not be set until the baud rate generator has timed out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- 2: A bus collision during the Repeated START condition occurs if:

- SDA is sampled low when SCL goes from low to high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data "1".

Immediately following the SSPIF bit getting set, the user may write the SSPBUF with the 7-bit address in 7-bit mode, or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional eight bits of address (10-bit mode) or eight bits of data (7-bit mode).

#### 16.4.9.1 WCOL Status Flag

If the user writes the SSPBUF when a Repeated START sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing of the lower 5 bits of SSPCON2 is disabled until the Repeated START condition is complete.

#### FIGURE 16-20: REPEAT START CONDITION WAVEFORM

#### 16.4.17.3 Bus Collision During a STOP Condition

Bus collision occurs during a STOP condition if:

- a) After the SDA pin has been de-asserted and allowed to float high, SDA is sampled low after the BRG has timed out.

- b) After the SCL pin is de-asserted, SCL is sampled low before SDA goes high.

The STOP condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the baud rate generator is loaded with SSPADD<6:0> and counts down to '0'. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 16-31). If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 16-32).

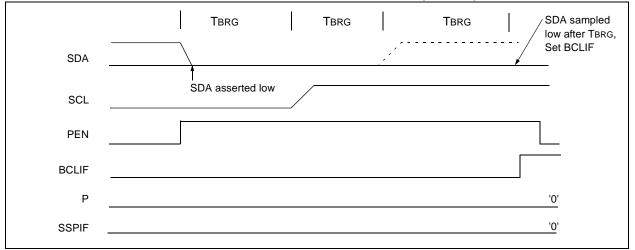

#### FIGURE 16-31: BUS COLLISION DURING A STOP CONDITION (CASE 1)

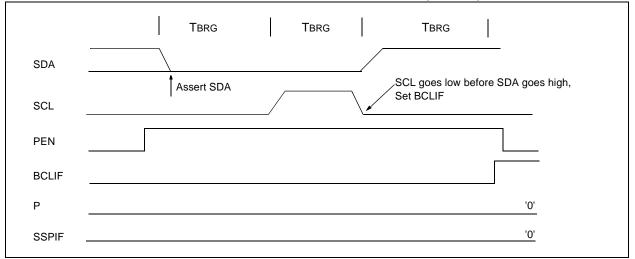

#### FIGURE 16-32: BUS COLLISION DURING A STOP CONDITION (CASE 2)

#### 17.1 USART Baud Rate Generator (BRG)

The BRG supports both the Asynchronous and Synchronous modes of the USART. It is a dedicated 8-bit baud rate generator. The SPBRG register controls the period of a free running 8-bit timer. In Asynchronous mode, bit BRGH (TXSTA<2>) also controls the baud rate. In Synchronous mode, bit BRGH is ignored. Table 17-1 shows the formula for computation of the baud rate for different USART modes, which only apply in Master mode (internal clock).

Given the desired baud rate and FOSC, the nearest integer value for the SPBRG register can be calculated using the formula in Table 17-1. From this, the error in baud rate can be determined. Example 17-1 shows the calculation of the baud rate error for the following conditions:

- Fosc = 16 MHz

- Desired Baud Rate = 9600

- BRGH = 0

- SYNC = 0

It may be advantageous to use the high baud rate (BRGH = 1) even for slower baud clocks. This is because the FOSC/(16(X + 1)) equation can reduce the baud rate error in some cases.

Writing a new value to the SPBRG register causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

#### 17.1.1 SAMPLING

The data on the RC7/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin.

#### EXAMPLE 17-1: CALCULATING BAUD RATE ERROR

| Desired Baud Rate    | = Fosc / (64 (X + 1))                                                                                                                    |                                                                                                                                                                                                                                                                                |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Solving for X:       |                                                                                                                                          |                                                                                                                                                                                                                                                                                |

| X<br>X<br>X          | = ((Fosc / Desired Baud Rate) / 64) - 1<br>= ((16000000 / 9600) / 64) - 1<br>= [25.042] = 25                                             |                                                                                                                                                                                                                                                                                |

| Calculated Baud Rate | = 1600000 / (64 (25 + 1)) = 9615                                                                                                         |                                                                                                                                                                                                                                                                                |

| Error                | <ul> <li><u>(Calculated Baud Rate – Desired Baud Rate)</u><br/>Desired Baud Rate</li> <li>(9615 – 9600) / 9600</li> <li>0.16%</li> </ul> |                                                                                                                                                                                                                                                                                |

|                      | Solving for X:<br>X<br>X<br>X<br>Calculated Baud Rate                                                                                    | Solving for X:<br>X = ((Fosc / Desired Baud Rate) / 64) - 1 $X = ((16000000 / 9600) / 64) - 1$ $X = [25.042] = 25$ Calculated Baud Rate = 16000000 / (64 (25 + 1))<br>= 9615<br>Error = (Calculated Baud Rate - Desired Baud Rate)<br>Desired Baud Rate = (9615 - 9600) / 9600 |

#### TABLE 17-1: BAUD RATE FORMULA

| SYNC | BRGH = 0 (Low Speed)                      | BRGH = 1 (High Speed)      |

|------|-------------------------------------------|----------------------------|

| 0    | (Asynchronous) Baud Rate = FOSC/(64(X+1)) | Baud Rate = Fosc/(16(X+1)) |

| 1    | (Synchronous) Baud Rate = Fosc/(4(X+1))   | N/A                        |

Legend: X = value in SPBRG (0 to 255)

#### TABLE 17-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Name  | Bit 7                              | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1     | Bit 0     | Value on<br>POR, BOR | Value on<br>All Other<br>RESETS |

|-------|------------------------------------|-------|-------|-------|-------|-------|-----------|-----------|----------------------|---------------------------------|

| TXSTA | CSRC                               | TX9   | TXEN  | SYNC  | _     | BRGH  | TRMT      | TX9D      | 0000 -010            | 0000 -010                       |

| RCSTA | SPEN                               | RX9   | SREN  | CREN  | ADDEN | FERR  | OERR      | RX9D      | 0000 -00x            | 0000 -00x                       |

| SPBRG | SPBRG Baud Rate Generator Register |       |       |       |       |       | 0000 0000 | 0000 0000 |                      |                                 |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used by the BRG.

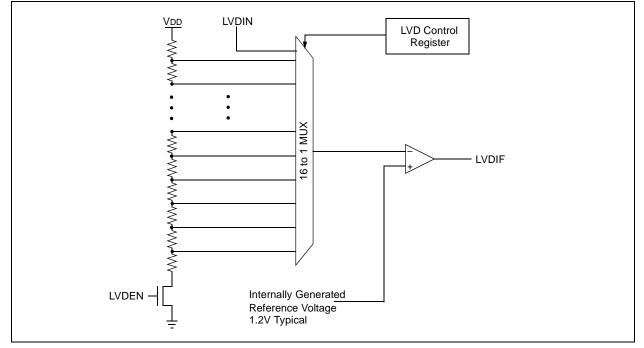

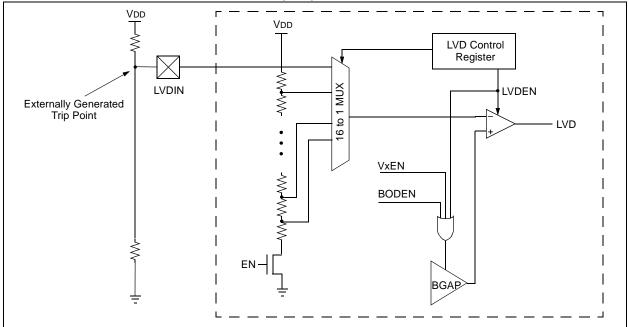

#### FIGURE 19-2: LOW VOLTAGE DETECT (LVD) BLOCK DIAGRAM

The LVD module has an additional feature that allows the user to supply the trip voltage to the module from an external source. This mode is enabled when bits LVDL3:LVDL0 are set to '1111'. In this state, the comparator input is multiplexed from the external input pin, LVDIN (Figure 19-3). This gives users flexibility, because it allows them to configure the Low Voltage Detect interrupt to occur at any voltage in the valid operating range.

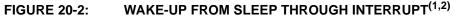

| `Q1   Q2  Q3  Q4<br>  OSC1 /                | Q1 Q2 Q3 Q4;Q1 <br>~_^ |             | Q1 Q2 Q3 Q4; | Q1 Q2 Q3 Q4;      | Q1 Q2 Q3 Q4;   | Q1 Q2 Q3 Q4; |

|---------------------------------------------|------------------------|-------------|--------------|-------------------|----------------|--------------|

| CLKO <sup>(4)</sup>                         |                        | Tost(2)     |              | \'                | <u> </u>       | '            |

| INT pin                                     | 1                      |             | I            |                   |                |              |

| INTF Flag<br>(INTCON<1>)                    |                        | <u> </u>    |              | Interrupt Latency | 3)             |              |

| GIEH bit<br>(INTCON<7>)                     | Proces<br>SLE          |             |              |                   | <br> <br> <br> |              |

| INSTRUCTION FLOW                            | I<br>I                 |             |              |                   | 1              | 1            |

| PC X PC                                     | PC+2 X                 | PC+4        | PC+4         | PC + 4            | (0008h)        | ( 000Ah      |

| Instruction [<br>Fetched ] Inst(PC) = SLEEP | Inst(PC + 2)           | 1           | Inst(PC + 4) |                   | Inst(0008h)    | Inst(000Ah)  |

| Instruction∫<br>Executed I Inst(PC - 1)     | SLEEP                  | 1<br>1<br>1 | Inst(PC + 2) | Dummy Cycle       | Dummy Cycle    | Inst(0008h)  |

**Note 1:** XT, HS or LP Oscillator mode assumed.

2: GIE = 1 assumed. In this case, after wake-up, the processor jumps to the interrupt routine. If GIE = 0, execution will continue in-line.

3: TOST = 1024 TOSC (drawing not to scale). This delay will not occur for RC and EC Osc modes.

4: CLKO is not available in these Osc modes, but shown here for timing reference.

#### 20.4 Program Verification and Code Protection

The overall structure of the code protection on the PIC18 FLASH devices differs significantly from other PIC devices. The user program memory is divided on binary boundaries into individual blocks, each of which has three separate code protection bits associated with it:

- Code Protect bit (CPn)

- Write Protect bit (WRTn)

- External Block Table Read bit (EBTRn)

The code protection bits are located in Configuration Registers 5L through 7H. Their locations within the registers are summarized in Table 20-3.

In the PIC18FXX39 family, program memory is divided into segments of 8 Kbytes. The first block in turn divided into a boot block of 512 bytes and a separately protected remainder (Block 0) of 7.5 Kbytes. This means for PIC18FXX39 devices, that there may be up to five blocks, depending on the program memory size. The organization of the blocks and their associated code protection bits are shown in Figure 20-3. For PIC18FX439 devices, program memory is divided into three blocks: a boot block, Block 0 (7.5 Kbytes) and Block 1 (8 Kbytes). Block 1 is further divided in half; the upper portion above 3000h is reserved, and unavailable to user applications. The entire block can be protected as a whole by bits CP1, WRT1 and EBTR1. By default, Block 1 is not code protected.

For PIC18FX539 devices, program memory is divided into five blocks: the boot block, Block 0 (7.5 Kbytes), and Blocks 1 through 3 (8 Kbytes). Code protection is implemented for the boot block and Blocks 0 through 2. There is no provision for code protection for Block 3.

Note: The reserved segments of the program memory space are used by the Motor Control kernel. For the kernel to function properly, this area must not be write protected. If users are developing applications that require code protection for PIC18FX439 devices, they should restrict program code (or at least those sections requiring protection) to below the 1FFFh memory boundary.

| CPF              | SGT                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Compare                                  | f with W, sk         | ip if f > W     |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|----------------------|-----------------|--|--|

| Synta            | ax:                                                                                                                                                                                                                                                                                                                                                                                                                                                   | [label] C                                | PFSGT f[             | ,a]             |  |  |

| Oper             | ands:                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0 ≤ f ≤ 255<br>a ∈ [0,1]                 |                      |                 |  |  |

| Oper             | ation:                                                                                                                                                                                                                                                                                                                                                                                                                                                | (f) – (W),<br>skip if (f) ><br>(unsigned | · (W)<br>comparison) |                 |  |  |

| Statu            | s Affected:                                                                                                                                                                                                                                                                                                                                                                                                                                           | None                                     |                      |                 |  |  |

| Enco             | ding:                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0110                                     | 010a fff             | f ffff          |  |  |

| Desc             | Description:<br>Compares the contents of data<br>memory location 'f' to the contents<br>of the W by performing an<br>unsigned subtraction.<br>If the contents of 'f' are greater tha<br>the contents of WREG, then the<br>fetched instruction is discarded ar<br>a NOP is executed instead, makin<br>this a two-cycle instruction. If 'a' is<br>0, the Access Bank will be<br>selected, overriding the BSR value<br>If 'a' = 1, then the bank will be |                                          |                      |                 |  |  |

| Word             | le ·                                                                                                                                                                                                                                                                                                                                                                                                                                                  | (default).<br>1                          |                      |                 |  |  |

| Cycle            |                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1(2)<br>Note: 3 c                        | •                    | and followed    |  |  |

|                  | volo Activity                                                                                                                                                                                                                                                                                                                                                                                                                                         | •                                        | a 2-word ins         | truction.       |  |  |

|                  | ycle Activity:<br>Q1                                                                                                                                                                                                                                                                                                                                                                                                                                  | Q2                                       | Q3                   | Q4              |  |  |

| Γ                | Decode                                                                                                                                                                                                                                                                                                                                                                                                                                                | Read                                     | Process              | No              |  |  |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                       | register 'f'                             | Data                 | operation       |  |  |

| lf sk            | · .                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 00                                       | 02                   | 04              |  |  |

| Г                | Q1<br>No                                                                                                                                                                                                                                                                                                                                                                                                                                              | Q2<br>No                                 | Q3<br>No             | Q4<br>No        |  |  |

|                  | operation                                                                                                                                                                                                                                                                                                                                                                                                                                             | operation                                | operation            | operation       |  |  |

| lf sk            | ip and follow                                                                                                                                                                                                                                                                                                                                                                                                                                         | ed by 2-word                             | d instruction:       |                 |  |  |

| F                | Q1                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Q2                                       | Q3                   | Q4              |  |  |

|                  | No                                                                                                                                                                                                                                                                                                                                                                                                                                                    | No                                       | No                   | No              |  |  |

| -                | operation<br>No                                                                                                                                                                                                                                                                                                                                                                                                                                       | operation<br>No                          | operation<br>No      | operation<br>No |  |  |

|                  | operation                                                                                                                                                                                                                                                                                                                                                                                                                                             | operation                                | operation            | operation       |  |  |

| <u>Example</u> : |                                                                                                                                                                                                                                                                                                                                                                                                                                                       | HERE<br>NGREATER<br>GREATER              | NGREATER :           |                 |  |  |

| E                | Before Instru                                                                                                                                                                                                                                                                                                                                                                                                                                         | iction                                   |                      |                 |  |  |

| PC               |                                                                                                                                                                                                                                                                                                                                                                                                                                                       | = Ad                                     | dress (HERE)         | )               |  |  |

|                  | W                                                                                                                                                                                                                                                                                                                                                                                                                                                     | = ?                                      |                      |                 |  |  |

| ŀ                | After Instruct                                                                                                                                                                                                                                                                                                                                                                                                                                        | ion                                      |                      |                 |  |  |

|                  | lf REG<br>PC                                                                                                                                                                                                                                                                                                                                                                                                                                          | > W;                                     |                      | \               |  |  |

|                  | If REG                                                                                                                                                                                                                                                                                                                                                                                                                                                | = Ad<br>≤ W;                             | dress (GREAT         | PER)            |  |  |

| CPF                | SLT             | Compare                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | f with W, sk                                             | ip if f < W     |  |  |  |  |

|--------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------|--|--|--|--|

| Synt               | tax:            | [label] C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CPFSLT f[,                                               | a]              |  |  |  |  |

| Ope                | rands:          | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5                                                        |                 |  |  |  |  |

| 000                | ration          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          |                 |  |  |  |  |

| Ope                | ration:         | skip if (f) <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | (f) – (W),<br>skip if (f) < (W)<br>(unsigned comparison) |                 |  |  |  |  |

| State              | us Affected:    | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          |                 |  |  |  |  |

| Enc                | oding:          | 0110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 000a fff                                                 | f ffff          |  |  |  |  |

| Des<br>Wor<br>Cycl |                 | Compares the contents of data<br>memory location 'f' to the contents<br>of W by performing an unsigned<br>subtraction.<br>If the contents of 'f' are less than<br>the contents of W, then the fetcher<br>instruction is discarded and a NOF<br>is executed instead, making this a<br>two-cycle instruction. If 'a' is 0, the<br>Access Bank will be selected. If 'a<br>is 1, the BSR will not be overridde<br>(default).<br>1<br>1(2)<br>Note: 3 cycles if skip and follower<br>by a 2-word instruction. |                                                          |                 |  |  |  |  |

| QC                 | Cycle Activity: |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          |                 |  |  |  |  |

|                    | Q1              | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Q3                                                       | Q4              |  |  |  |  |

|                    | Decode          | Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Process                                                  | No              |  |  |  |  |

|                    |                 | register 'f'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Data                                                     | operation       |  |  |  |  |

| lf sl              |                 | 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 00                                                       | 04              |  |  |  |  |

|                    | Q1<br>No        | Q2<br>No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Q3<br>No                                                 | Q4<br>No        |  |  |  |  |

|                    | operation       | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | operation                                                | operation       |  |  |  |  |

| lf sl              | kip and follow  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | d instruction:                                           | <u> </u>        |  |  |  |  |

|                    | Q1              | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Q3                                                       | Q4              |  |  |  |  |

|                    | No              | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | No                                                       | No              |  |  |  |  |

|                    | operation       | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | operation                                                | operation       |  |  |  |  |

|                    | No<br>operation | No<br>operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | No<br>operation                                          | No<br>operation |  |  |  |  |

| <u>Exa</u>         | mple:           | NLESS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CPFSLT REG,                                              | 1               |  |  |  |  |

|                    | Before Instru   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          |                 |  |  |  |  |

|                    | PC<br>W         | = Ad<br>= ?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | dress (HERE)                                             | )               |  |  |  |  |

|                    | After Instruct  | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                          |                 |  |  |  |  |

|                    | If REG          | < W;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          |                 |  |  |  |  |