Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 32                                                                         |

| Program Memory Size        | 24KB (12K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1408 × 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf4539-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.5 Effects of SLEEP Mode on the On-Chip Oscillator

When the device executes a SLEEP instruction, the oscillator is turned off and the device is held at the beginning of an instruction cycle (Q1 state). With the oscillator off, the OSC1 and OSC2 signals will stop oscillating. Since all the transistor switching currents have been removed, SLEEP mode achieves the lowest current consumption of the device (only leakage currents). Enabling any on-chip feature that will operate during SLEEP will increase the current consumed during SLEEP. The user can wake from SLEEP through external RESET, Watchdog Timer Reset, or through an interrupt.

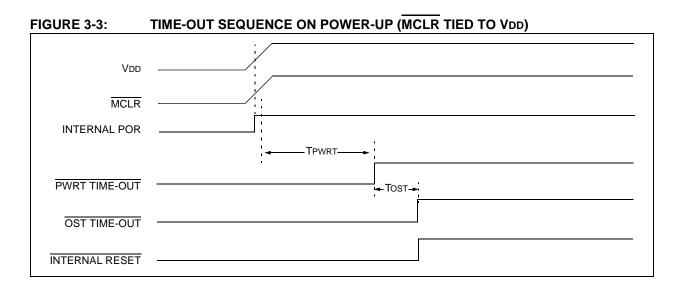

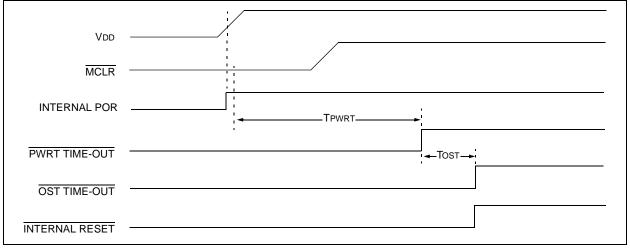

### 2.6 Power-up Delays

Power-up delays are controlled by two timers, so that no external RESET circuitry is required for most applications. The delays ensure that the device is kept in RESET, until the device power supply and clock are stable. For additional information on RESET operation, see Section 3.0. The first timer is the Power-up Timer (PWRT), which optionally provides a fixed delay of 72 ms (nominal) on power-up only (POR and BOR). The second timer is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable.

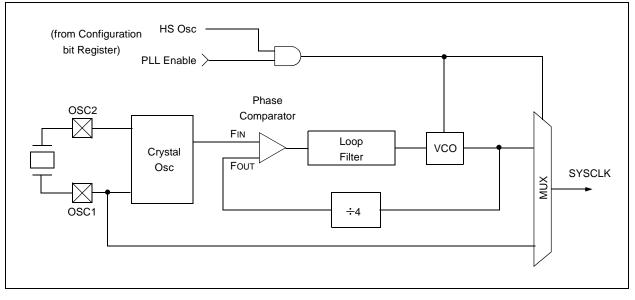

With the PLL enabled (HS/PLL Oscillator mode), the time-out sequence following a Power-on Reset is different from other Oscillator modes. The time-out sequence is as follows:

- 1. The PWRT time-out is invoked after a POR time delay has expired.

- 2. The Oscillator Start-up Timer (OST) is invoked. However, this is still not a sufficient amount of time to allow the PLL to lock at high frequencies.

- 3. The PWRT timer is used to provide an additional fixed 2 ms (nominal) time-out to allow the PLL ample time to lock to the incoming clock frequency.

### TABLE 2-2: OSC1 AND OSC2 PIN STATES IN SLEEP MODE

| OSC Mode | OSC1 Pin                                               | OSC2 Pin                                                  |

|----------|--------------------------------------------------------|-----------------------------------------------------------|

| ECIO     | Floating                                               | Configured as PORTA, bit 6                                |

| EC       | Floating                                               | At logic low                                              |

| HS       | Feedback inverter disabled, at quiescent voltage level | Feedback inverter disabled, at quiescent<br>voltage level |

**Note:** See Table 3-1 in the "**Reset**" section, for time-outs due to SLEEP and MCLR Reset.

<sup>© 2002-2013</sup> Microchip Technology Inc.

### FIGURE 3-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

##

### 4.0 MEMORY ORGANIZATION

There are three memory blocks in Enhanced MCU devices. These memory blocks are:

- Program Memory

- Data RAM

- Data EEPROM

Data and program memory use separate busses, which allows for concurrent access of these blocks.

Additional detailed information for FLASH program memory and Data EEPROM is provided in Section 5.0 and Section 6.0, respectively.

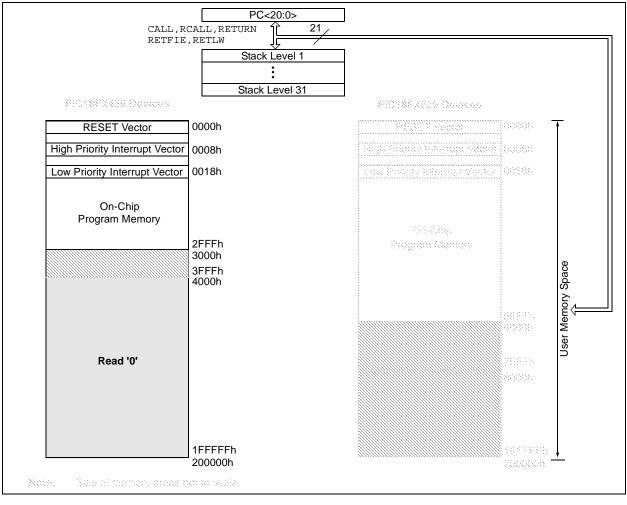

### 4.1 Program Memory Organization

A 21-bit program counter is capable of addressing the 2-Mbyte program memory space. Accessing a location between the physically implemented memory and the top of the 2-MByte range will cause a read of all '0's (a NOP instruction).

The PIC18F2539 and PIC18F4539 each have a total of 24 Kbytes, or 12K of single word instructions of FLASH memory, from addresses 0000h to 5FFFh. The next 8 Kbytes beyond this space (from 6000h to 7FFFh) are reserved for the Motor Control kernel; accessing locations in this range will return random information.

The PIC18F2439 and PIC18F4439 each have 12 Kbytes, or 6K of single word instructions of FLASH memory, from addresses 0000h to 2FFFh. The next 4 Kbytes of this space (from 3000h to 3FFFh) are reserved for the Motor Control kernel; accessing locations in this range will return random information.

The RESET vector address for all devices is at 0000h, and the interrupt vector addresses are at 0008h and 0018h.

The memory maps for the PIC18FX439 and PIC18FX539 devices are shown in Figure 4-1.

Note: The ProMPT Motor Control kernel is identical for all PIC18FXX39 devices, regardless of the difference in reserved block size between PIC18FX439 and PIC18FX539 devices

### FIGURE 4-1: PROGRAM MEMORY MAP AND STACK FOR PIC18FXX39 DEVICES

### 5.0 FLASH PROGRAM MEMORY

The FLASH Program Memory is readable, writable, and erasable during normal operation over the entire VDD range.

A read from program memory is executed on one byte at a time. A write to program memory is executed on blocks of 8 bytes at a time. Program memory is erased in blocks of 64 bytes at a time. A bulk erase operation may not be issued from user code.

Writing or erasing program memory will cease instruction fetches until the operation is complete. The program memory cannot be accessed during the write or erase, therefore, code cannot execute. An internal programming timer terminates program memory writes and erases.

A value written to program memory does not need to be a valid instruction. Executing a program memory location that forms an invalid instruction results in a NOP.

### 5.1 Table Reads and Table Writes

In order to read and write program memory, there are two operations that allow the processor to move bytes between the program memory space and the data RAM:

- Table Read (TBLRD)

- Table Write (TBLWT)

The program memory space is 16-bits wide, while the data RAM space is 8-bits wide. Table Reads and Table Writes move data between these two memory spaces through an 8-bit register (TABLAT).

Table Read operations retrieve data from program memory and places it into the data RAM space. Figure 5-1 shows the operation of a Table Read with program memory and data RAM.

Table Write operations store data from the data memory space into holding registers in program memory. The procedure to write the contents of the holding registers into program memory is detailed in Section 5.5, "Writing to FLASH Program Memory". Figure 5-2 shows the operation of a Table Write with program memory and data RAM.

Table operations work with byte entities. A table block containing data, rather than program instructions, is not required to be word aligned. Therefore, a table block can start and end at any byte address. If a Table Write is being used to write executable code into program memory, program instructions will need to be word aligned.

# FIGURE 5-1: TABLE READ OPERATION

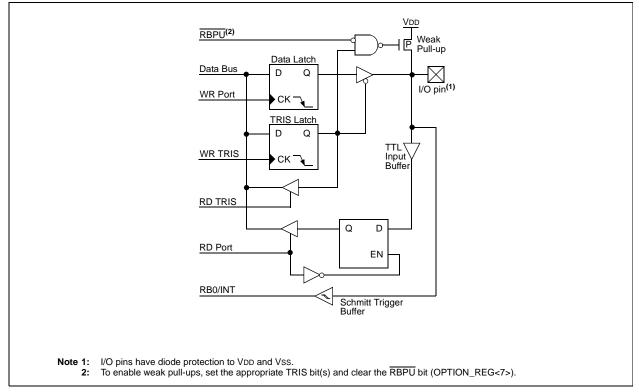

### FIGURE 9-5: BLOCK DIAGRAM OF RB2:RB0 PINS

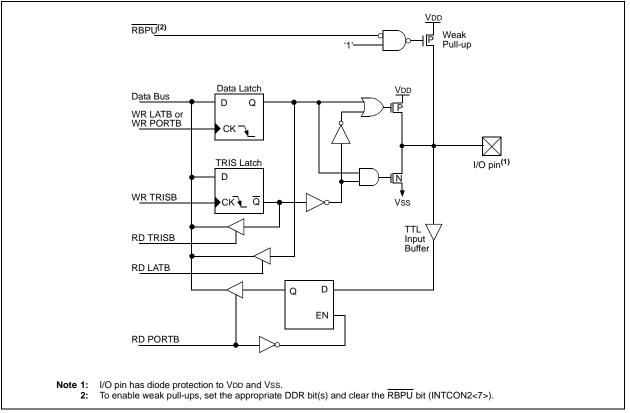

### FIGURE 9-6: BLOCK DIAGRAM OF RB3 PIN

### TABLE 9-7:PORTD FUNCTIONS

| Name     | Bit# | Buffer Type           | Function                                           |

|----------|------|-----------------------|----------------------------------------------------|

| RD0/PSP0 | bit0 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit0. |

| RD1/PSP1 | bit1 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit1. |

| RD2/PSP2 | bit2 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit2. |

| RD3/PSP3 | bit3 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit3. |

| RD4/PSP4 | bit4 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit4. |

| RD5/PSP5 | bit5 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit5. |

| RD6/PSP6 | bit6 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit6. |

| RD7/PSP7 | bit7 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit7. |

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

### TABLE 9-8: SUMMARY OF REGISTERS ASSOCIATED WITH PORTD

| Name  | Bit 7                         | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2   | Bit 1       | Bit 0     | Value on<br>POR, BOR | Value on<br>All Other<br>RESETS |

|-------|-------------------------------|-------|-------|---------|-------|---------|-------------|-----------|----------------------|---------------------------------|

| PORTD | RD7                           | RD6   | RD5   | RD4     | RD3   | RD2     | RD1         | RD0       | xxxx xxxx            | uuuu uuuu                       |

| LATD  | LATD Data Output Register     |       |       |         |       |         |             | xxxx xxxx | uuuu uuuu            |                                 |

| TRISD | PORTD Data Direction Register |       |       |         |       |         |             | 1111 1111 | 1111 1111            |                                 |

| TRISE | IBF                           | OBF   | IBOV  | PSPMODE |       | PORTE D | ata Directi | on bits   | 0000 -111            | 0000 -111                       |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTD.

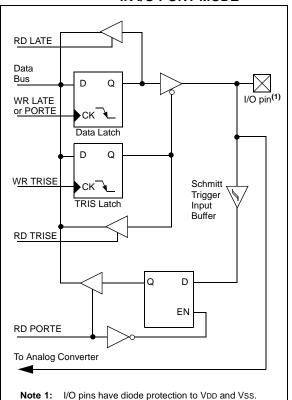

### 9.5 PORTE, TRISE and LATE Registers

This section is only applicable to the PIC18F4X39 devices.

PORTE is a 3-bit wide, bi-directional port. The corresponding Data Direction register is TRISE. Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., put the corresponding output driver in a High Impedance mode). Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATE) is also memory mapped. Read-modify-write operations on the LATE register reads and writes the latched output value for PORTE.

PORTE has three pins (RE0/AN5/RD, RE1/AN6/WR and RE2/AN7/CS) which are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers.

Register 9-1 shows the TRISE register, which also controls the parallel slave port operation.

PORTE pins are multiplexed with analog inputs. When selected as an analog input, these pins will read as '0's.

TRISE controls the direction of the RE pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

Note: On a Power-on Reset, these pins are configured as analog inputs.

### EXAMPLE 9-5: INITIALIZING PORTE

| CLRF  | PORTE  | ; Initialize PORTE by<br>; clearing output |

|-------|--------|--------------------------------------------|

|       |        | 5 1                                        |

|       |        | ; data latches                             |

| CLRF  | LATE   | ; Alternate method                         |

|       |        | ; to clear output                          |

|       |        | ; data latches                             |

| MOVLW | 0x07   | ; Configure A/D                            |

| MOVWF | ADCON1 | ; for digital inputs                       |

| MOVLW | 0x05   | ; Value used to                            |

|       |        | ; initialize data                          |

|       |        | ; direction                                |

| MOVWF | TRISE  | ; Set RE<0> as inputs                      |

|       |        | ; RE<1> as outputs                         |

|       |        | ; RE<2> as inputs                          |

|       |        |                                            |

### FIGURE 9-9:

### PORTE BLOCK DIAGRAM IN I/O PORT MODE

© 2002-2013 Microchip Technology Inc.

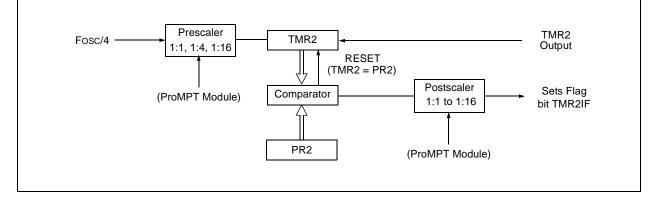

### 12.0 TIMER2 MODULE

The Timer2 module is an 8-bit timer with a selectable 8-bit period. It has the following features:

- Input from system clock at Fosc/4 with programmable input prescaler

- Interrupt on timer-to-period match with programmable postscaler

The module has three registers: the TMR2 counter, the PR2 period register, and the T2CON control register. The general operation of Timer2 is shown in Figure 12-1.

Additional information on the use of Timer2 as a time-base is available in Section 15.0 (PWM Modules).

Note: In PIC18FXX39 devices, Timer2 is used exclusively as a time-base for the PWM modules in motor control applications. As such, it is not available to users as a resource. Although their locations are shown on the device data memory maps, none of the Timer2 registers are directly accessible. Users should not alter the values of these registers.

### 16.4.3.2 Reception

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register and the SDA line is held low (ACK).

When the address byte overflow condition exists, then the no Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set, or bit SSPOV (SSPCON1<6>) is set.

An MSSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

If SEN is enabled (SSPCON1<0> = 1), RC3/SCK/SCL will be held low (clock stretch) following each data transfer. The clock must be released by setting bit CKP (SSPCON<4>). See Section 16.4.4 ("Clock Stretching"), for more detail.

### 16.4.3.3 Transmission

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit and pin RC3/SCK/SCL is held low, regardless of SEN (see "Clock Stretching", Section 16.4.4, for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data. The transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then, pin RC3/ SCK/SCL should be enabled by setting bit CKP (SSPCON1<4>). The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 16-9).

The ACK pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line is high (not ACK), then the data transfer is complete. In this case, when the ACK is latched by the slave, the slave logic is reset (resets SSPSTAT register) and the slave monitors for another occurrence of the START bit. If the SDA line was low (ACK), the next transmit data must be loaded into the SSPBUF register. Again, pin RC3/SCK/SCL must be enabled by setting bit CKP.

An MSSP interrupt is generated for each data transfer byte. The SSPIF bit must be cleared in software and the SSPSTAT register is used to determine the status of the byte. The SSPIF bit is set on the falling edge of the ninth clock pulse.

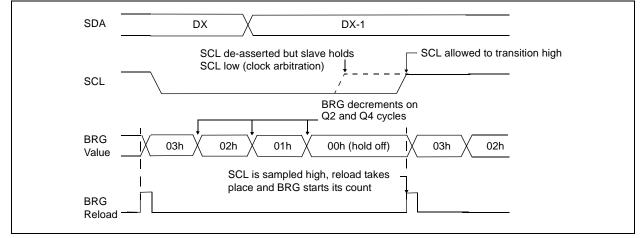

### 16.4.7.1 Clock Arbitration

Clock arbitration occurs when the master, during any receive, transmit or Repeated START/STOP condition, de-asserts the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the baud rate generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the SCL pin is

sampled high, the baud rate generator is reloaded with the contents of SSPADD<6:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count, in the event that the clock is held low by an external device (Figure 16-18).

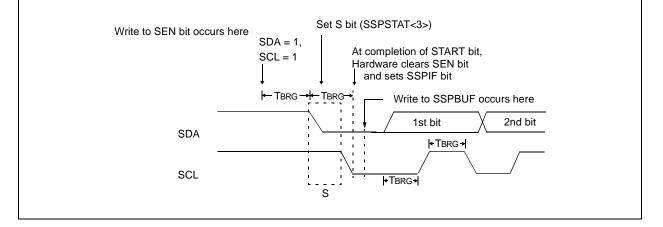

### 16.4.8 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a START condition, the user sets the START condition enable bit, SEN (SSPCON2<0>). If the SDA and SCL pins are sampled high, the baud rate generator is reloaded with the contents of SSPADD<6:0> and starts its count. If SCL and SDA are both sampled high when the baud rate generator times out (TBRG), the SDA pin is driven low. The action of the SDA being driven low, while SCL is high, is the START condition and causes the S bit (SSPSTAT<3>) to be set. Following this, the baud rate generator is reloaded with the contents of SSPADD<6:0> and resumes its count. When the baud rate generator times out (TBRG), the SEN bit (SSPCON2<0>) will be automatically cleared by hardware, the baud rate generator is suspended, leaving the SDA line held low and the START condition is complete.

**Note:** If at the beginning of the START condition, the SDA and SCL pins are already sampled low, or if during the START condition the SCL line is sampled low before the SDA line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCLIF is set, the START condition is aborted, and the I<sup>2</sup>C module is reset into its IDLE state.

### FIGURE 16-19: FIRST START BIT TIMING

### 16.4.8.1 WCOL Status Flag

If the user writes the SSPBUF when a START sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing to the lower 5 bits of SSPCON2 is disabled until the START condition is complete.

|       |                                                |                                                  |              |              |             | ••=•       |              |        |

|-------|------------------------------------------------|--------------------------------------------------|--------------|--------------|-------------|------------|--------------|--------|

|       | R/W-0                                          | R/W-0                                            | R/W-0        | R/W-0        | U-0         | R/W-0      | R-1          | R/W-0  |

|       | CSRC                                           | TX9                                              | TXEN         | SYNC         | —           | BRGH       | TRMT         | TX9D   |

|       | bit 7                                          |                                                  |              |              |             |            |              | bit 0  |

| bit 7 | CSRC: Clo<br>Asynchrone<br>Don't care          | ock Source S<br>ous mode:                        | elect bit    |              |             |            |              |        |

|       | <u>Synchrono</u><br>1 = Master                 | <u>us mode:</u><br>mode (clock<br>node (clock    |              |              | om BRG)     |            |              |        |

| bit 6 | 1 = Selects                                    | Transmit Ena<br>s 9-bit transm<br>s 8-bit transm | nission      |              |             |            |              |        |

| bit 5 | <b>TXEN</b> : Tran<br>1 = Transm<br>0 = Transm |                                                  | e bit        |              |             |            |              |        |

|       | Note:                                          | SREN/CRE                                         | N overrides  | TXEN in SY   | NC mode.    |            |              |        |

| bit 4 | 1 = Synchr                                     | ART Mode S<br>onous mode<br>nronous mod          | •            |              |             |            |              |        |

| bit 3 | -                                              | ented: Read                                      |              |              |             |            |              |        |

| bit 2 | BRGH: Hig                                      | h Baud Rate                                      | e Select bit |              |             |            |              |        |

|       | Asynchrono<br>1 = High sp<br>0 = Low sp        | beed                                             |              |              |             |            |              |        |

|       | <u>Synchrono</u><br>Unused in                  |                                                  |              |              |             |            |              |        |

| bit 1 | <b>TRMT</b> : Tran<br>1 = TSR er<br>0 = TSR fu |                                                  | egister Stat | us bit       |             |            |              |        |

| bit 0 |                                                | bit of Transn<br>dress/Data b                    |              | / bit        |             |            |              |        |

|       | Legend:                                        |                                                  |              |              |             |            |              |        |

|       | R = Reada                                      | ble bit                                          | W = W        | /ritable bit | U = Unin    | nplemented | bit, read as | '0'    |

|       | - n = Value                                    | at POR                                           | '1' = B      | it is set    | '0' = Bit i | s cleared  | x = Bit is u | nknown |

### REGISTER 17-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER

### 20.3 Power-down Mode (SLEEP)

Power-down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If enabled, the Watchdog Timer will be cleared, but keeps running, the  $\overline{PD}$  bit (RCON<3>) is cleared, the  $\overline{TO}$  (RCON<4>) bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, low or hi-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD or VSS, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D and disable external clocks. Pull all I/O pins that are hi-impedance inputs, high or low externally, to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC).

### 20.3.1 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. External RESET input on MCLR pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change or a Peripheral Interrupt.

The following peripheral interrupts can wake the device from SLEEP:

- 1. PSP read or write.

- 2. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 3. TMR3 interrupt. Timer3 must be operating as an asynchronous counter.

- 4. CCP Capture mode interrupt.

- 5. Special event trigger (Timer1 in Asynchronous mode using an external clock).

- 6. MSSP (START/STOP) bit detect interrupt.

- MSSP transmit or receive in Slave mode (SPI/I<sup>2</sup>C).

- 8. USART RX or TX (Synchronous Slave mode).

- 9. A/D conversion (when A/D clock source is RC).

- 10. EEPROM write operation complete.

- 11. LVD interrupt.

Other peripherals cannot generate interrupts, since during SLEEP, no on-chip clocks are present.

External MCLR Reset will cause a device RESET. All other events are considered a continuation of program execution and will cause a "wake-up". The TO and PD bits in the RCON register can be used to determine the cause of the device RESET. The PD bit, which is set on power-up, is cleared when SLEEP is invoked. The TO bit is cleared, if a WDT time-out occurred (and caused wake-up).

When the SLEEP instruction is being executed, the next instruction (PC + 2) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

### 20.3.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If an interrupt condition (interrupt flag bit and interrupt enable bits are set) occurs before the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt condition occurs during or after the execution of a SLEEP instruction, the device will immediately wake-up from SLEEP. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

| MULLW                                | Multiply I                                                                                                         | Literal with                                                          | N                                                                          | MULWF                      | Multiply \                                                                                                                           | N with f                                                                                                                                                                                   |                                                                                                                                      |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                              | [ label ]                                                                                                          | MULLW k                                                               |                                                                            | Syntax:                    | [ label ]                                                                                                                            | MULWF f                                                                                                                                                                                    | [,a]                                                                                                                                 |

| Operands:                            | $0 \le k \le 255$                                                                                                  |                                                                       | Operands:                                                                  | $0 \le f \le 255$          | 5                                                                                                                                    |                                                                                                                                                                                            |                                                                                                                                      |

| Operation:                           | (W) x k $\rightarrow$ PRODH:PRODL                                                                                  |                                                                       |                                                                            | a ∈ [0,1]                  |                                                                                                                                      |                                                                                                                                                                                            |                                                                                                                                      |

| Status Affected:                     | None                                                                                                               |                                                                       | Operation:                                                                 | (W) x (f) –                | → PRODH:P                                                                                                                            | RODL                                                                                                                                                                                       |                                                                                                                                      |

| Encoding:                            | 0000                                                                                                               | 1101 kk                                                               | kk kkkk                                                                    | Status Affected:           | None                                                                                                                                 |                                                                                                                                                                                            |                                                                                                                                      |

| Description:                         | An unsign                                                                                                          | ed multiplica                                                         | ition is car-                                                              | Encoding:                  | 0000                                                                                                                                 | 001a ff:                                                                                                                                                                                   | ff ffff                                                                                                                              |

|                                      | W and the<br>16-bit rest<br>PRODH:F<br>PRODH c<br>W is unch<br>None of th<br>affected.<br>Note that<br>carry is po | ne status flag<br>neither overf<br>ossible in this<br>ro result is po | k'. The<br>in<br>ter pair.<br>high byte.<br>gs are<br>flow nor<br>s opera- | Description:               | ried out be<br>W and the<br>The 16-bit<br>PRODH C<br>Both W ar<br>None of th<br>affected.<br>Note that<br>carry is po<br>tion. A zer | ed multiplica<br>etween the c<br>register file<br>t result is sto<br>PRODL regis<br>ontains the l<br>nd 'f' are unc<br>ne status flag<br>neither over<br>ossible in this<br>o result is po | contents of<br>location 'f'.<br>ored in the<br>ster pair.<br>high byte.<br>changed.<br>gs are<br>flow nor<br>s opera-<br>ossible but |

| Words:                               | 1                                                                                                                  |                                                                       |                                                                            |                            |                                                                                                                                      | ed. If 'a' is 0                                                                                                                                                                            |                                                                                                                                      |

| Cycles:                              | 1                                                                                                                  |                                                                       |                                                                            |                            |                                                                                                                                      | ank will be s<br>the BSR va                                                                                                                                                                | ,                                                                                                                                    |

| Q Cycle Activity:                    |                                                                                                                    |                                                                       |                                                                            |                            | -                                                                                                                                    | en the bank                                                                                                                                                                                |                                                                                                                                      |

| Q1                                   | Q2                                                                                                                 | Q3                                                                    | Q4                                                                         |                            |                                                                                                                                      | as per the BS                                                                                                                                                                              | SR value                                                                                                                             |

| Decode                               | Read                                                                                                               | Process                                                               | Write                                                                      | NA / 1                     | (default).                                                                                                                           |                                                                                                                                                                                            |                                                                                                                                      |

|                                      | literal 'k'                                                                                                        | Data                                                                  | registers<br>PRODH:                                                        | Words:                     | 1                                                                                                                                    |                                                                                                                                                                                            |                                                                                                                                      |

|                                      |                                                                                                                    |                                                                       | PRODL                                                                      | Cycles:                    | 1                                                                                                                                    |                                                                                                                                                                                            |                                                                                                                                      |

|                                      |                                                                                                                    |                                                                       |                                                                            | Q Cycle Activity           |                                                                                                                                      | 00                                                                                                                                                                                         | 04                                                                                                                                   |

| Example:                             |                                                                                                                    | 0xC4                                                                  |                                                                            | Q1<br>Decode               | Q2<br>Read                                                                                                                           | Q3<br>Process                                                                                                                                                                              | Q4<br>Write                                                                                                                          |

| Before Instru<br>W<br>PRODH<br>PRODL |                                                                                                                    | E2                                                                    |                                                                            |                            | register 'f'                                                                                                                         | Data                                                                                                                                                                                       | registers<br>PRODH:<br>PRODL                                                                                                         |

| After Instruct                       |                                                                                                                    |                                                                       |                                                                            |                            |                                                                                                                                      |                                                                                                                                                                                            |                                                                                                                                      |

| W                                    | = 0x                                                                                                               | E2                                                                    |                                                                            | Example:                   |                                                                                                                                      | REG, 1                                                                                                                                                                                     |                                                                                                                                      |

| PRODH<br>PRODL                       | -                                                                                                                  | AD<br>08                                                              |                                                                            | Before Instr               |                                                                                                                                      |                                                                                                                                                                                            |                                                                                                                                      |

|                                      | _ 04                                                                                                               |                                                                       |                                                                            | W<br>REG<br>PRODH<br>PRODL | = 0x<br>= ?                                                                                                                          | C4<br>B5                                                                                                                                                                                   |                                                                                                                                      |

|                                      |                                                                                                                    |                                                                       |                                                                            | After Instruc              | ction                                                                                                                                |                                                                                                                                                                                            |                                                                                                                                      |

|                                      |                                                                                                                    |                                                                       |                                                                            |                            | _                                                                                                                                    | <b>.</b> .                                                                                                                                                                                 |                                                                                                                                      |

| W     | = | 0xC4 |

|-------|---|------|

| REG   | = | 0xB5 |

| PRODH | = | 0x8A |

| PRODL | = | 0x94 |

|       |   |      |

| SUBWFB                      | Subtract                                                                                        | W from f witl                                                                                                                                                                 | h Borrow                                                                                       |  |  |

|-----------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|--|

| Syntax:                     | [label]                                                                                         | SUBWFB f[                                                                                                                                                                     | ,d [,a]                                                                                        |  |  |

| Operands:                   | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                             | 5                                                                                                                                                                             |                                                                                                |  |  |

| Operation:                  | (f) – (W) -                                                                                     | $-(\overline{C}) \rightarrow dest$                                                                                                                                            |                                                                                                |  |  |

| Status Affected:            | N, OV, C, DC, Z                                                                                 |                                                                                                                                                                               |                                                                                                |  |  |

| Encoding:                   | 0101                                                                                            | 10da fff                                                                                                                                                                      | f ffff                                                                                         |  |  |

| Description:                | row) from<br>method). I<br>in W. If 'd'<br>back in re-<br>the Acces<br>overriding<br>then the b | V and the carn<br>register 'f' (2's<br>f 'd' is 0, the re-<br>is 1, the result<br>gister 'f' (defau<br>s Bank will be<br>the BSR value<br>ank will be sel-<br>alue (default). | complement<br>sult is stored<br>is stored<br>lt). If 'a' is 0,<br>selected,<br>e. If 'a' is 1, |  |  |

| Words:                      | 1                                                                                               |                                                                                                                                                                               |                                                                                                |  |  |

| Cycles:                     | 1                                                                                               |                                                                                                                                                                               |                                                                                                |  |  |

| Q Cycle Activity:           |                                                                                                 |                                                                                                                                                                               |                                                                                                |  |  |

| Q1                          | Q2                                                                                              | Q3                                                                                                                                                                            | Q4                                                                                             |  |  |

| Decode                      | Read<br>register 'f'                                                                            | Process<br>Data                                                                                                                                                               | Write to destination                                                                           |  |  |

| Example 1:                  | SUBWFB                                                                                          | REG, 1, 0                                                                                                                                                                     |                                                                                                |  |  |

| Before Instru               |                                                                                                 |                                                                                                                                                                               |                                                                                                |  |  |

| REG<br>w                    | = 0x19<br>= 0x0D                                                                                | (0001 100)                                                                                                                                                                    |                                                                                                |  |  |

| С                           | = 1                                                                                             | (0000 110                                                                                                                                                                     | /_/                                                                                            |  |  |

| After Instruct<br>REG       | = 0x0C                                                                                          | (0000 101                                                                                                                                                                     | 1)                                                                                             |  |  |

| W                           | = 0x0D                                                                                          | (0000 110                                                                                                                                                                     |                                                                                                |  |  |

| C<br>Z<br>N                 | = 1<br>= 0                                                                                      |                                                                                                                                                                               |                                                                                                |  |  |

|                             | = 0                                                                                             | ; result is po                                                                                                                                                                | ositive                                                                                        |  |  |

| Example 2:<br>Before Instru | SUBWFB                                                                                          | REG, 0, 0                                                                                                                                                                     |                                                                                                |  |  |

| REG                         | = 0x1B                                                                                          | (0001 101                                                                                                                                                                     | .1)                                                                                            |  |  |

| W<br>C                      | = 0x1A<br>= 0                                                                                   | (0001 101                                                                                                                                                                     | .0)                                                                                            |  |  |

| After Instruct              | -                                                                                               |                                                                                                                                                                               |                                                                                                |  |  |

| REG<br>W                    | = 0x1B<br>= 0x00                                                                                | (0001 101                                                                                                                                                                     | 1)                                                                                             |  |  |

| C                           | = 1                                                                                             |                                                                                                                                                                               |                                                                                                |  |  |

| Z<br>N                      | = 1<br>= 0                                                                                      | ; result is ze                                                                                                                                                                | ero                                                                                            |  |  |

| Example 3:                  | SUBWFB                                                                                          | REG, 1, 0                                                                                                                                                                     |                                                                                                |  |  |

| Before Instru               |                                                                                                 |                                                                                                                                                                               |                                                                                                |  |  |

| REG<br>w                    | = 0x03<br>= 0x0E                                                                                | (0000 001                                                                                                                                                                     |                                                                                                |  |  |

| C                           | = 1                                                                                             |                                                                                                                                                                               | ,                                                                                              |  |  |

| After Instruct<br>REG       | ion<br>= 0xF5                                                                                   | (1111 010                                                                                                                                                                     |                                                                                                |  |  |

| W                           | = 0x0E                                                                                          | ; [2's comp]<br>(0000 110                                                                                                                                                     |                                                                                                |  |  |

| C<br>Z                      | = 0<br>= 0                                                                                      |                                                                                                                                                                               |                                                                                                |  |  |

| N                           | = 1                                                                                             | ; result is ne                                                                                                                                                                | egative                                                                                        |  |  |

| Syntax:[ label ]SWAPF f [,d [,a]Operands: $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$ Operation:(f<3:0>) $\rightarrow$ dest<7:4>,<br>(f<7:4>) $\rightarrow$ dest<3:0>Status Affected:NoneEncoding: $0011$ $10da$ ffffDescription:The upper and lower nibbles of register 'f' are exchanged. If 'd' is 0, the<br>result is placed in register 'f'<br>(default). If 'a' is 0, the Access<br>Bank will be selected, overriding<br>the BSR value. If 'a' is 1, then the<br>bank will be selected as per the<br>BSR value (default).Words:1Cycles:1Q Cycle Activity:Q1Q2Q3Q4DecodeRead<br>register 'f'DetailRead<br>register 'f'Before Instruction<br>REG= 0x53<br>After Instruction<br>REGREG= 0x35                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $d \in [0,1] \\ a \in [0,1]$ $a \in [0,1]$ $a \in [0,1]$ $Operation: (f<3:0>) \rightarrow dest<7:4>, (f<7:4>) \rightarrow dest<3:0>$ Status Affected: None Encoding: $0011  10da  ffff  ffff$ Description: The upper and lower nibbles of register 'f' are exchanged. If 'd' is 0, the result is placed in W. If 'd' is 1, the result is placed in W. If 'd' is 1, the result is placed in W. If 'd' is 1, the result is placed in register 'f' (default). If 'a' is 0, the Access Bank will be selected, overriding the BSR value. If 'a' is 1, then the bank will be selected as per the BSR value (default). Words: 1 Cycles: 1 Q Cycle Activity: $Q1  Q2  Q3  Q4$ $\boxed{Decode  Read  Process  Write to \ register 'f'  Data  destination}$ Example: SWAPF REG, 1, 0 Before Instruction REG = 0x53 After Instruction |

| (f<7:4>) → dest<3:0>         Status Affected:       None         Encoding:       0011       10da       ffff       ffff         Description:       The upper and lower nibbles of register 'f' are exchanged. If 'd' is 0, the result is placed in register 'f' (default). If 'a' is 0, the Access Bank will be selected, overriding the BSR value. If 'a' is 1, then the bank will be selected as per the BSR value (default).         Words:       1         Cycles:       1         Q Cycle Activity:       Q1       Q2       Q3       Q4         Decode       Read       Process       Write to destination         Example:       SWAPF       REG, 1, 0         Before Instruction       REG       = 0x53         After Instruction       REG       1, 0                                                               |

| Encoding:       0011       10da       ffff       ffff         Description:       The upper and lower nibbles of register 'f' are exchanged. If 'd' is 0, the result is placed in W. If 'd' is 1, the result is placed in register 'f' (default). If 'a' is 0, the Access Bank will be selected, overriding the BSR value. If 'a' is 1, then the bank will be selected as per the BSR value (default).         Words:       1         Cycles:       1         Q Cycle Activity:       Q1       Q2       Q3       Q4         Decode       Read       Process       Write to destination         Example:       SWAPF       REG, 1, 0         Before Instruction       REG       = 0x53         After Instruction       After Instruction                                                                                     |

| Description:<br>The upper and lower nibbles of register 'f' are exchanged. If 'd' is 0, the result is placed in W. If 'd' is 1, the result is placed in register 'f' (default). If 'a' is 0, the Access Bank will be selected, overriding the BSR value. If 'a' is 1, then the bank will be selected as per the BSR value (default).<br>Words:<br>1<br>Q Cycle Activity:<br>Q1<br>Q2<br>Q3<br>Q4<br>Decode<br>Read<br>register 'f'<br>Data<br>Market of destination<br>Example:<br>SWAPF<br>REG, 1, 0<br>Before Instruction<br>REG = 0x53<br>After Instruction                                                                                                                                                                                                                                                             |

| ister 'f' are exchanged. If 'd' is 0, the<br>result is placed in W. If 'd' is 1, the<br>result is placed in register 'f'<br>(default). If 'a' is 0, the Access<br>Bank will be selected, overriding<br>the BSR value. If 'a' is 1, then the<br>bank will be selected as per the<br>BSR value (default).<br>Words: 1<br>Cycles: 1<br>Q Cycle Activity:<br>Q1 Q2 Q3 Q4<br>Decode Read Process Write to<br>register 'f' Data destination<br>Example: SWAPF REG, 1, 0<br>Before Instruction<br>REG = 0x53<br>After Instruction                                                                                                                                                                                                                                                                                                 |

| Cycles: 1<br>Q Cycle Activity:<br>Q1 Q2 Q3 Q4<br>Decode Read Process Write to<br>register 'f' Data destination<br>Example: SWAPF REG, 1, 0<br>Before Instruction<br>REG = 0x53<br>After Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Q Cycle Activity:<br>Q1 Q2 Q3 Q4<br>Decode Read Process Write to<br>register 'f' Data destination<br>Example: SWAPF REG, 1, 0<br>Before Instruction<br>REG = 0x53<br>After Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Q1     Q2     Q3     Q4       Decode     Read<br>register 'f'     Process<br>Data     Write to<br>destination       Example:     SWAPF     REG, 1, 0       Before Instruction<br>REG     =     0x53       After Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Q1     Q2     Q3     Q4       Decode     Read<br>register 'f'     Process<br>Data     Write to<br>destination       Example:     SWAPF     REG, 1, 0       Before Instruction<br>REG     =     0x53       After Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| register 'f'     Data     destination       Example:     SWAPF     REG, 1, 0       Before Instruction     REG     = 0x53       After Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Before Instruction<br>REG = 0x53<br>After Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Before Instruction<br>REG = 0x53<br>After Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

NOTES:

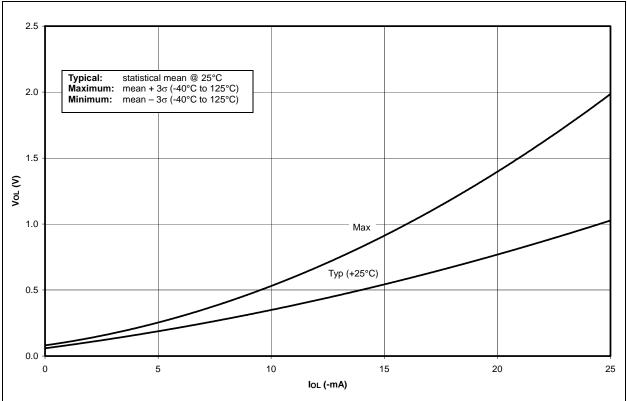

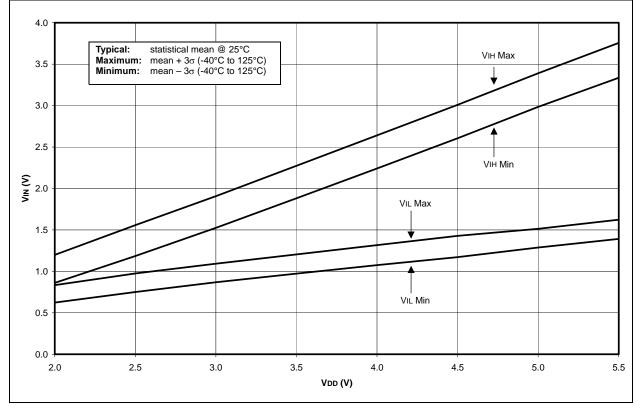

### 23.2 DC Characteristics: PIC18FXX39 (Industrial, Extended) PIC18LFXX39 (Industrial)

| DC CHARACTERISTICS |        |                                            | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \end{array}$ |                    |        |                                                                                                                             |  |

|--------------------|--------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------|-----------------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No.       | Symbol | ol Characteristic Min Max Units            |                                                                                                                                                                                                                                                                 |                    |        | Conditions                                                                                                                  |  |

|                    | VIL    | Input Low Voltage                          |                                                                                                                                                                                                                                                                 |                    |        |                                                                                                                             |  |

|                    |        | I/O ports:                                 |                                                                                                                                                                                                                                                                 |                    |        |                                                                                                                             |  |

| D030               |        | with TTL buffer                            | Vss                                                                                                                                                                                                                                                             | 0.15 Vdd           | V      | Vdd < 4.5V                                                                                                                  |  |

| D030A              |        |                                            | —                                                                                                                                                                                                                                                               | 0.8                | V      | $4.5V \le VDD \le 5.5V$                                                                                                     |  |