Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                               |

|----------------------------|---------------------------------------------------------------|

| Product Status             | Obsolete                                                      |

| Core Processor             | HC08                                                          |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 8MHz                                                          |

| Connectivity               | SCI                                                           |

| Peripherals                | LED, LVD, POR, PWM                                            |

| Number of I/O              | 26                                                            |

| Program Memory Size        | 8KB (8K x 8)                                                  |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | -                                                             |

| RAM Size                   | 256 x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                   |

| Data Converters            | A/D 13x8b                                                     |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                             |

| Mounting Type              | Through Hole                                                  |

| Package / Case             | 32-SDIP (0.400", 10.16mm)                                     |

| Supplier Device Package    | 32-SDIP                                                       |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc68hc908jl8cspe |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Chapter 6 Oscillator (OSC)

| 6.1   | Introduction                                        | 79        |

|-------|-----------------------------------------------------|-----------|

| 6.2   | Oscillator Selection                                | 79        |

| 6.2.1 | XTAL Oscillator                                     | 80        |

| 6.2.2 | RC Oscillator                                       |           |

| 6.3   | Internal Oscillator                                 | 81        |

| 6.4   | I/O Signals                                         | 82        |

| 6.4.1 | Crystal Amplifier Input Pin (OSC1)                  |           |

| 6.4.2 | Crystal Amplifier Output Pin (OSC2/RCCLK/PTA6/KBI6) |           |

| 6.4.3 | Oscillator Enable Signal (SIMOSCEN)                 |           |

| 6.4.4 | XTAL Oscillator Clock (XTALCLK)                     |           |

| 6.4.5 | RC Oscillator Clock (RCCLK)                         |           |

| 6.4.6 | Oscillator Out 2 (20SCOUT)                          |           |

| 6.4.7 | Oscillator Out (OSCOUT)                             | 83        |

| 6.4.8 | Internal Oscillator Clock (ICLK)                    | 83        |

| 6.5   | Low Power Modes                                     | 83        |

| 6.5.1 | Wait Mode                                           | 83        |

| 6.5.2 | Stop Mode                                           | 83        |

| 6.6   | Oscillator During Break Mode                        | 83        |

|       | Chantas 7                                           |           |

|       | Chapter 7 Monitor ROM (MON)                         |           |

| 7.1   | Introduction                                        | 85        |

| 7.2   | Features                                            |           |

| 7.3   | Functional Description                              |           |

| 7.3.1 | Entering Monitor Mode                               |           |

| 7.3.2 | Baud Rate                                           |           |

| 7.3.3 | Data Format                                         |           |

| 7.3.4 | Echoing                                             |           |

| 7.3.5 | Break Signal                                        |           |

| 7.3.6 | Commands                                            |           |

| 7.4   | Security                                            |           |

| 7.5   | ROM-Resident Routines                               |           |

| 7.5.1 | PRGRNGE                                             |           |

| 7.5.2 | ERARNGE                                             |           |

| 7.5.3 | LDRNGE                                              |           |

| 7.5.4 | MON_PRGRNGE                                         |           |

| 7.5.5 |                                                     |           |

| 7.0.0 | MON_ERARNGE                                         |           |

| 7.5.6 |                                                     | 99        |

|       | MON_ERARNGE                                         | 99<br>100 |

#### **Table of Contents**

# Chapter 11 Input/Output (I/O) Ports

| 11.1             | Introduction                             | 151 |

|------------------|------------------------------------------|-----|

| 11.2             | Port A                                   | 153 |

| 11.2.1           | Port A Data Register (PTA)               | 153 |

| 11.2.2           | Data Direction Register A (DDRA)         |     |

| 11.2.3           | Port A Input Pull-Up Enable Registers    |     |

| 11.3             | Port B                                   |     |

| 11.3.1           | Port B Data Register (PTB)               |     |

| 11.3.2           | Data Direction Register B (DDRB)         |     |

| 11.4             | Port D                                   |     |

| 11.4.1<br>11.4.2 | Port D Data Register (PTD)               |     |

| 11.4.2           | Port D Control Register (PDCR)           |     |

| 11.5             | Port E                                   |     |

| 11.5.1           | Port E Data Register (PTE)               |     |

| 11.5.2           | Data Direction Register E (DDRE)         |     |

|                  |                                          |     |

|                  | Chapter 12                               |     |

|                  | External Interrupt (IRQ)                 |     |

| 12.1             | Introduction                             |     |

| 12.2             | Features                                 |     |

| 12.3             | Functional Description                   |     |

| 12.3.1           | IRQ Pin.                                 |     |

| 12.4             | IRQ Module During Break Interrupts       |     |

| 12.5             | IRQ Status and Control Register (INTSCR) | 166 |

|                  | Chapter 13                               |     |

|                  | Keyboard Interrupt Module (KBI)          |     |

| 13.1             | Introduction                             | 167 |

| 13.2             | Features                                 | 167 |

| 13.3             | I/O Pins                                 | 167 |

| 13.4             | Functional Description                   | 168 |

| 13.4.1           | Keyboard Initialization                  | 169 |

| 13.5             | Keyboard Interrupt Registers             | 169 |

| 13.5.1           | Keyboard Status and Control Register     |     |

| 13.5.2           | Keyboard Interrupt Enable Register       |     |

| 13.6             | Low-Power Modes                          |     |

| 13.6.1           | Wait Mode                                |     |

| 13.6.2           | Stop Mode                                |     |

| 13.7             | Keyboard Module During Break Interrupts  | 171 |

|                  | Chapter 14                               |     |

|                  | Computer Operating Properly (COP)        |     |

| 14.1             | Introduction                             | 173 |

| 14.2             | Functional Description                   |     |

|                  |                                          |     |

MC68HC908JL8/JK8 • MC68HC08JL8/JK8 • MC68HC908KL8 Data Sheet, Rev. 3.1

#### **Table of Contents**

# Chapter 17 Electrical Specifications

| 17.1        | Introduction                                           | 185 |

|-------------|--------------------------------------------------------|-----|

| 17.2        | Absolute Maximum Ratings                               | 185 |

| 17.3        | Functional Operating Range                             | 186 |

| 17.4        | Thermal Characteristics                                | 186 |

| 17.5        | 5V DC Electrical Characteristics                       | 187 |

| 17.6        | 5V Control Timing                                      | 188 |

| 17.7        | 5V Oscillator Characteristics                          | 188 |

| 17.8        | 3V DC Electrical Characteristics                       | 189 |

| 17.9        | 3V Control Timing                                      | 190 |

| 17.10       | 3V Oscillator Characteristics                          | 191 |

| 17.11       | Typical Supply Currents                                |     |

| 17.12       | Timer Interface Module Characteristics                 | 193 |

| 17.13       | ADC Characteristics                                    |     |

| 17.14       | Memory Characteristics                                 | 194 |

|             | Chapter 18                                             |     |

|             | Mechanical Specifications                              |     |

| 18.1        | Introduction                                           | 195 |

| 18.2        | 20-Pin Plastic Dual In-Line Package (PDIP)             | 195 |

| 18.3        | 20-Pin Small Outline Integrated Circuit Package (SOIC) | 196 |

| 18.4        | 28-Pin Plastic Dual In-Line Package (PDIP)             |     |

| 18.5        | 28-Pin Small Outline Integrated Circuit Package (SOIC) | 197 |

| 18.6        | 32-Pin Shrink Dual In-Line Package (SDIP)              | 197 |

| 18.7        | 32-Pin Low-Profile Quad Flat Pack (LQFP)               | 198 |

|             | Chapter 19                                             |     |

|             | Ordering Information                                   |     |

| 19.1        | Introduction                                           | 199 |

| 19.2        | MC Order Numbers                                       |     |

|             |                                                        |     |

|             | Appendix A                                             |     |

| A.1         | MC68HC08JL8 Introduction                               | 201 |

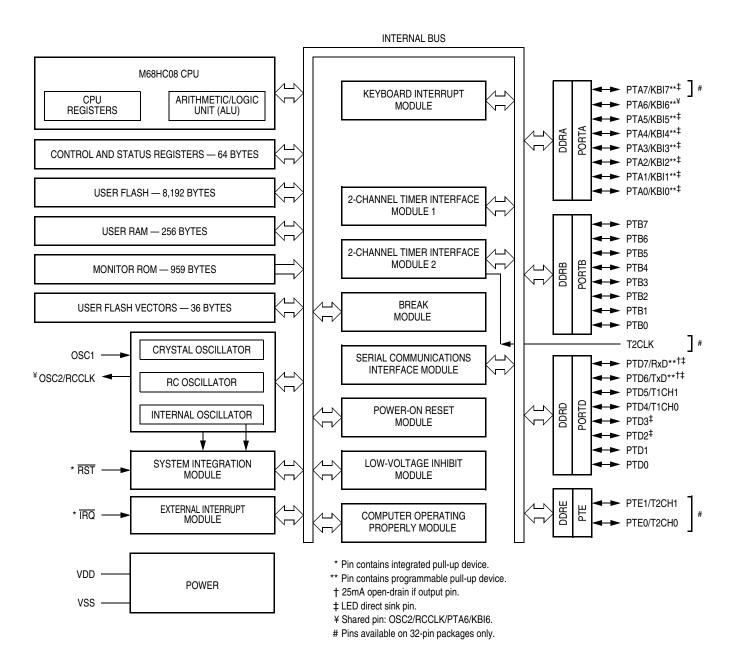

| A.2         | MCU Block Diagram                                      |     |

| A.3         | Memory Map                                             |     |

| A.4         | Reserved Registers                                     |     |

| A.5         | Mask Option Register                                   |     |

| A.6         | Monitor ROM                                            |     |

| A.7         | Electrical Specifications                              |     |

| A.7.1       | DC Electrical Characteristics.                         |     |

| A.8         | Memory Characteristics                                 |     |

| <b>A</b> .9 | MC68HC08JL8 Order Numbers                              |     |

|             |                                                        |     |

MC68HC908JL8/JK8 • MC68HC08JL8/JK8 • MC68HC908KL8 Data Sheet, Rev. 3.1

#### **Table 1-2. Pin Functions (Continued)**

| PIN NAME  | PIN DESCRIPTION                 | IN/OUT | VOLTAGE<br>LEVEL |

|-----------|---------------------------------|--------|------------------|

| PTE0-PTE1 | 2-bit general purpose I/O port. | In/Out | VDD              |

|           | PTE0 as T2CH0 of TIM2.          | In/Out | VDD              |

|           | PTE1 as T2CH1 of TIM2.          | In/Out | VDD              |

#### NOTE

Devices in 28-pin packages, the following pins are not available: PTA7/KBI7, PTE0/T2CH0, PTE1/T2CH1, and ADC12/T2CLK.

Devices in 20-pin packages, the following pins are not available: PTA0/KBI0-PTA5/KBI5, PTD0/ADC11, PTD1/ADC10, PTA7/KBI7, PTE0/T2CH0, PTE1/T2CH1, and ADC12/T2CLK.

The resultant 16-bit address is used for specifying the start address of the FLASH memory for block protection. The FLASH is protected from this start address to the end of FLASH memory, at \$FFFF. With this mechanism, the protect start address can be XX00, XX40, XX80, or XXC0 (at page boundaries — 64 bytes) within the FLASH memory.

#### Examples of protect start address:

| BPR[7:0]                                         | Start of Address of Protect Range <sup>(1)</sup> |

|--------------------------------------------------|--------------------------------------------------|

| \$00–\$70                                        | The entire FLASH memory is protected.            |

| \$71<br>(0111 0001) \$DC40 (1101 1100 0100 0000) |                                                  |

| \$72<br>( <b>0111 0010</b> )                     | \$DC80 (11 <b>01 1100 10</b> 00 0000)            |

| \$73<br>( <b>0111 0011</b> )                     | \$DCC0 (11 <b>01 1100 11</b> 00 0000)            |

| and so on                                        |                                                  |

| \$FD<br>( <b>1111 1101</b> )                     | \$FF40 (11 <b>11 1111 01</b> 00 0000)            |

| \$FE<br>(1111 1110)                              | \$FF80 (11 <b>11 1111 10</b> 00 0000)            |

| \$FF                                             | The entire FLASH memory is not protected.        |

<sup>1.</sup> The end address of the protected range is always \$FFFF.

Freescale Semiconductor 39

MC68HC908JL8/JK8 • MC68HC08JL8/JK8 • MC68HC908KL8 Data Sheet, Rev. 3.1

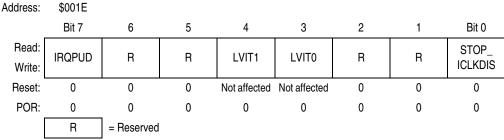

## 3.4 Configuration Register 2 (CONFIG2)

One-time writable register after each reset. LVIT1 and LVIT0 reset to logic 0 by a power-on reset (POR) only.

Figure 3-2. Configuration Register 2 (CONFIG2)

#### IRQPUD — IRQ Pin Pull-Up Disable Bit

IRQPUD disconnects the internal pull-up on the IRQ pin.

- 1 = Internal pull-up is disconnected

- 0 = Internal pull-up is connected between  $\overline{IRQ}$  pin and  $V_{DD}$

#### LVIT1, LVIT0 — LVI Trip Voltage Selection Bits

Detail description of trip voltage selection is given in Chapter 15 Low Voltage Inhibit (LVI).

#### STOP\_ICLKDIS — Internal Oscillator Stop Mode Disable Bit

Setting STOP\_ICLKDIS disables the internal oscillator during stop mode. When this bit is cleared, the internal oscillator continues to operate in stop mode. Reset clears this bit.

- 1 = Internal oscillator disabled during stop mode

- 0 = Internal oscillator enabled during stop mode

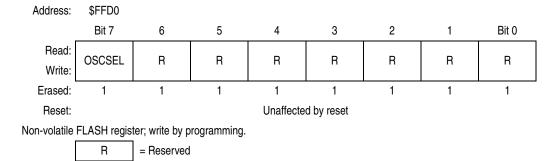

## 3.5 Mask Option Register (MOR)

The mask option register (MOR) is implemented as a byte within the FLASH memory, and therefore can only be written during a programming sequence of the FLASH memory. This register is read after a power-on reset to determine the type of oscillator selected. (See Chapter 6 Oscillator (OSC).)

Figure 3-3. Mask Option Register (MOR)

#### OSCSEL — Oscillator Select Bit

OSCSEL selects the oscillator type for the MCU. The erased or unprogrammed state of this bit is logic 1, selecting the crystal oscillator option. This bit is unaffected by reset.

- 1 = Crystal oscillator

- 0 = RC oscillator

MC68HC908JL8/JK8 • MC68HC08JL8/JK8 • MC68HC908KL8 Data Sheet, Rev. 3.1

**Configuration and Mask Option Registers (CONFIG & MOR)**

Bits 6-0 — Should be left as logic 1's.

#### NOTE

When Crystal oscillator is selected, the OSC2/RCCLK/PTA6/KBI6 pin is used as OSC2; other functions such as PTA6/KBI6 will not be available.

**Central Processor Unit (CPU)**

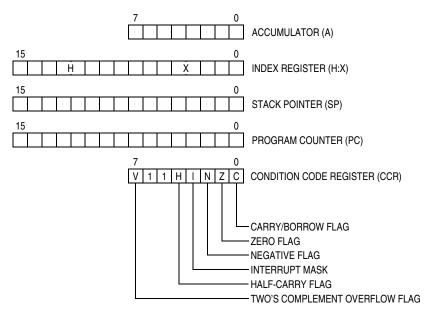

## 4.3 CPU Registers

Figure 4-1 shows the five CPU registers. CPU registers are not part of the memory map.

Figure 4-1. CPU Registers

#### 4.3.1 Accumulator

The accumulator is a general-purpose 8-bit register. The CPU uses the accumulator to hold operands and the results of arithmetic/logic operations.

Figure 4-2. Accumulator (A)

#### 4.3.2 Index Register

The 16-bit index register allows indexed addressing of a 64-Kbyte memory space. H is the upper byte of the index register, and X is the lower byte. H:X is the concatenated 16-bit index register.

In the indexed addressing modes, the CPU uses the contents of the index register to determine the conditional address of the operand.

The index register can serve also as a temporary data storage location.

After the I bit is cleared, the highest-priority interrupt request is serviced first.

A return-from-interrupt (RTI) instruction pulls the CPU registers from the stack and restores the interrupt mask from the stack. After any reset, the interrupt mask is set and can be cleared only by the clear interrupt mask software instruction (CLI).

#### N — Negative flag

The CPU sets the negative flag when an arithmetic operation, logic operation, or data manipulation produces a negative result, setting bit 7 of the result.

- 1 = Negative result

- 0 = Non-negative result

#### Z — Zero flag

The CPU sets the zero flag when an arithmetic operation, logic operation, or data manipulation produces a result of \$00.

- 1 = Zero result

- 0 = Non-zero result

#### C — Carry/Borrow Flag

The CPU sets the carry/borrow flag when an addition operation produces a carry out of bit 7 of the accumulator or when a subtraction operation requires a borrow. Some instructions — such as bit test and branch, shift, and rotate — also clear or set the carry/borrow flag.

- 1 = Carry out of bit 7

- 0 = No carry out of bit 7

## 4.4 Arithmetic/Logic Unit (ALU)

The ALU performs the arithmetic and logic operations defined by the instruction set.

Refer to the *CPU08 Reference Manual* (Freescale document order number CPU08RM/AD) for a description of the instructions and addressing modes and more detail about the architecture of the CPU.

#### 4.5 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

#### 4.5.1 Wait Mode

The WAIT instruction:

- Clears the interrupt mask (I bit) in the condition code register, enabling interrupts. After exit from wait mode by interrupt, the I bit remains clear. After exit by reset, the I bit is set.

- Disables the CPU clock

#### 4.5.2 Stop Mode

The STOP instruction:

- Clears the interrupt mask (I bit) in the condition code register, enabling external interrupts. After exit from stop mode by external interrupt, the I bit remains clear. After exit by reset, the I bit is set.

- Disables the CPU clock

After exiting stop mode, the CPU clock begins running after the oscillator stabilization delay.

MC68HC908JL8/JK8 • MC68HC08JL8/JK8 • MC68HC908KL8 Data Sheet, Rev. 3.1

#### **System Integration Module (SIM)**

#### SBSW — SIM Break Stop/Wait

This status bit is useful in applications requiring a return to wait or stop mode after exiting from a break interrupt. Clear SBSW by writing a logic zero to it. Reset clears SBSW.

- 1 = Stop mode or wait mode was exited by break interrupt

- 0 = Stop mode or wait mode was not exited by break interrupt

SBSW can be read within the break state SWI routine. The user can modify the return address on the stack by subtracting one from it. The following code is an example of this. Writing zero to the SBSW bit clears it.

```

; This code works if the H register has been pushed onto the stack in the break

; service routine software. This code should be executed at the end of the

; break service routine software.

5

HIBYTE

EOU

LOBYTE

EQU

6

If not SBSW, do RTI

SBSW, BSR, RETURN

; See if wait mode or stop mode was exited

; by break.

TST

LOBYTE, SP

; If RETURNLO is not zero,

; then just decrement low byte.

BNE

DOLO

DEC

HIBYTE, SP

; Else deal with high byte, too.

DOLO

DEC

LOBYTE, SP

; Point to WAIT/STOP opcode.

RETURN

PIII.H

; Restore H register.

RTI

```

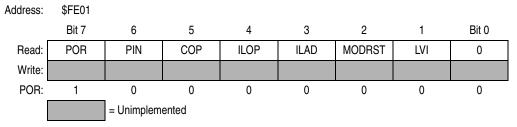

## 5.7.2 Reset Status Register (RSR)

This register contains six flags that show the source of the last reset. Clear the SIM reset status register by reading it. A power-on reset sets the POR bit and clears all other bits in the register.

Figure 5-21. Reset Status Register (RSR)

#### POR — Power-On Reset Bit

- 1 = Last reset caused by POR circuit

- 0 = Read of RSR

# Chapter 7 Monitor ROM (MON)

#### 7.1 Introduction

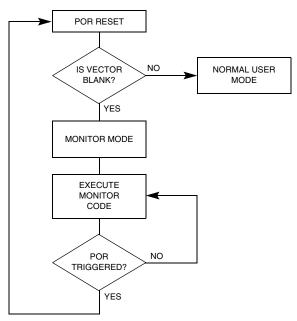

This section describes the monitor ROM (MON) and the monitor mode entry methods. The monitor ROM allows complete testing of the MCU through a single-wire interface with a host computer. This mode is also used for programming and erasing of FLASH memory in the MCU. Monitor mode entry can be achieved without use of the higher test voltage, V<sub>TST</sub>, as long as vector addresses \$FFFE and \$FFFF are blank, thus reducing the hardware requirements for in-circuit programming.

#### 7.2 Features

Features of the monitor ROM include the following:

- Normal user-mode pin functionality

- One pin dedicated to serial communication between monitor ROM and host computer

- Standard mark/space non-return-to-zero (NRZ) communication with host computer

- Execution of code in RAM or FLASH

- FLASH memory security feature<sup>(1)</sup>

- FLASH memory programming interface

- 959 bytes monitor ROM code size

- Monitor mode entry without high voltage, V<sub>TST</sub>, if reset vector is blank (\$FFFE and \$FFFF contain \$FF)

- Standard monitor mode entry if high voltage, V<sub>TST</sub>, is applied to IRQ

- Resident routines for FLASH programming and EEPROM emulation

## 7.3 Functional Description

The monitor ROM receives and executes commands from a host computer. Figure 7-1 shows a example circuit used to enter monitor mode and communicate with a host computer via a standard RS-232 interface.

Simple monitor commands can access any memory address. In monitor mode, the MCU can execute host-computer code in RAM while most MCU pins retain normal operating mode functions. All communication between the host computer and the MCU is through the PTB0 pin. A level-shifting and multiplexing interface is required between PTB0 and the host computer. PTB0 is used in a wired-OR configuration and requires a pull-up resistor.

MC68HC908JL8/JK8 • MC68HC08JL8/JK8 • MC68HC908KL8 Data Sheet, Rev. 3.1

<sup>1.</sup> No security feature is absolutely secure. However, Motorola's strategy is to make reading or copying the FLASH difficult for unauthorized users.

#### Monitor ROM (MON)

including the PTB3 frequency divisor selection, are not in effect. This is to reduce circuit requirements when performing in-circuit programming.

Entering monitor mode with the reset vector being blank, the COP is always disabled regardless of the state of IRQ or the RST.

Figure 7-2. shows a simplified diagram of the monitor mode entry when the reset vector is blank and  $\overline{IRQ}$  =  $V_{DD}$ . An OSC1 frequency of 9.8304MHz is required for a baud rate of 9600.

Figure 7-2. Low-Voltage Monitor Mode Entry Flowchart

Enter monitor mode with the pin configuration shown above by pulling  $\overline{RST}$  low and then high. The rising edge of  $\overline{RST}$  latches monitor mode. Once monitor mode is latched, the values on the specified pins can change.

Once out of reset, the MCU waits for the host to send eight security bytes. (See **7.4 Security**.) After the security bytes, the MCU sends a break signal (10 consecutive logic zeros) to the host, indicating that it is ready to receive a command. The break signal also provides a timing reference to allow the host to determine the necessary baud rate.

In monitor mode, the MCU uses different vectors for reset, SWI, and break interrupt. The alternate vectors are in the \$FE page instead of the \$FF page and allow code execution from the internal monitor firmware instead of user code.

Table 7-2 is a summary of the vector differences between user mode and monitor mode.

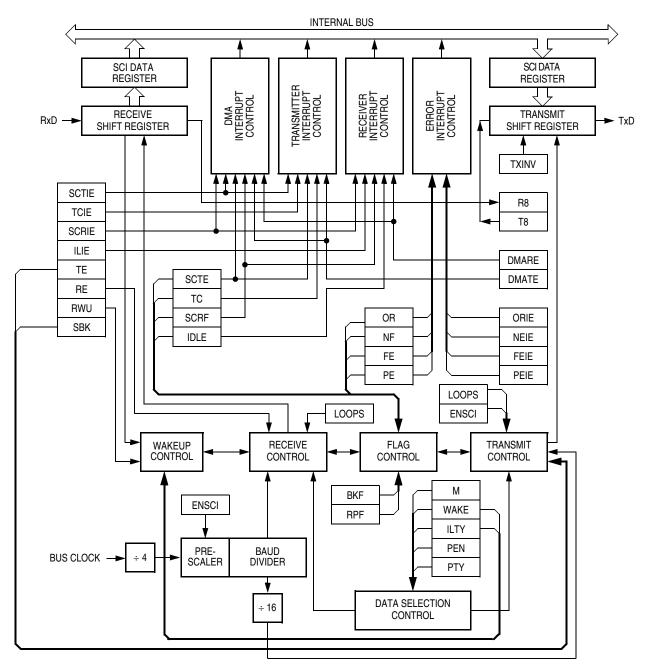

#### **Serial Communications Interface (SCI)**

The generic pin names appear in the text of this section.

**Table 9-1. Pin Name Conventions**

| Generic Pin Names: | RxD      | TxD      |  |

|--------------------|----------|----------|--|

| Full Pin Names:    | PTD7/RxD | PTD6/TxD |  |

Figure 9-1. SCI Module Block Diagram

#### **NEIE** — Receiver Noise Error Interrupt Enable Bit

This read/write bit enables SCI error CPU interrupt requests generated by the noise error bit, NE. Reset clears NEIE.

- 1 = SCI error CPU interrupt requests from NE bit enabled

- 0 = SCI error CPU interrupt requests from NE bit disabled

#### FEIE — Receiver Framing Error Interrupt Enable Bit

This read/write bit enables SCI error CPU interrupt requests generated by the framing error bit, FE. Reset clears FEIE.

- 1 = SCI error CPU interrupt requests from FE bit enabled

- 0 = SCI error CPU interrupt requests from FE bit disabled

#### PEIE — Receiver Parity Error Interrupt Enable Bit

This read/write bit enables SCI error CPU interrupt requests generated by the parity error bit, PE.

(See 9.8.4 SCI Status Register 1.) Reset clears PEIE.

- 1 = SCI error CPU interrupt requests from PE bit enabled

- 0 = SCI error CPU interrupt requests from PE bit disabled

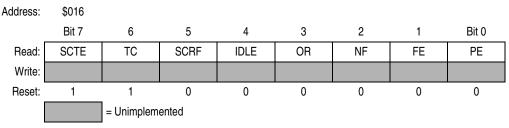

#### 9.8.4 SCI Status Register 1

SCI status register 1 (SCS1) contains flags to signal these conditions:

- Transfer of SCDR data to transmit shift register complete

- Transmission complete

- Transfer of receive shift register data to SCDR complete

- Receiver input idle

- Receiver overrun

- Noisy data

- Framing error

- Parity error

Figure 9-12. SCI Status Register 1 (SCS1)

#### **SCTE** — **SCI** Transmitter Empty Bit

This clearable, read-only bit is set when the SCDR transfers a character to the transmit shift register. SCTE can generate an SCI transmitter CPU interrupt request. When the SCTIE bit in SCC2 is set, SCTE generates an SCI transmitter CPU interrupt request. In normal operation, clear the SCTE bit by reading SCS1 with SCTE set and then writing to SCDR. Reset sets the SCTE bit.

- 1 = SCDR data transferred to transmit shift register

- 0 = SCDR data not transferred to transmit shift register

**Serial Communications Interface (SCI)**

#### 9.8.5 SCI Status Register 2

SCI status register 2 contains flags to signal the following conditions:

- Break character detected

- Incoming data

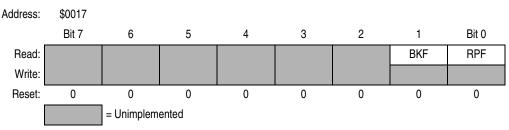

Figure 9-14. SCI Status Register 2 (SCS2)

#### **BKF** — Break Flag Bit

This clearable, read-only bit is set when the SCI detects a break character on the RxD pin. In SCS1, the FE and SCRF bits are also set. In 9-bit character transmissions, the R8 bit in SCC3 is cleared. BKF does not generate a CPU interrupt request. Clear BKF by reading SCS2 with BKF set and then reading the SCDR. Once cleared, BKF can become set again only after logic 1s again appear on the RxD pin followed by another break character. Reset clears the BKF bit.

- 1 = Break character detected

- 0 = No break character detected

#### RPF — Reception in Progress Flag Bit

This read-only bit is set when the receiver detects a logic 0 during the RT1 time period of the start bit search. RPF does not generate an interrupt request. RPF is reset after the receiver detects false start bits (usually from noise or a baud rate mismatch) or when the receiver detects an idle character. Polling RPF before disabling the SCI module or entering stop mode can show whether a reception is in progress.

- 1 = Reception in progress

- 0 = No reception in progress

#### 9.8.6 SCI Data Register

The SCI data register (SCDR) is the buffer between the internal data bus and the receive and transmit shift registers. Reset has no effect on data in the SCI data register.

| Address: | \$0018 |    |    |           |            |    |    |       |

|----------|--------|----|----|-----------|------------|----|----|-------|

|          | Bit 7  | 6  | 5  | 4         | 3          | 2  | 1  | Bit 0 |

| Read:    | R7     | R6 | R5 | R4        | R3         | R2 | R1 | R0    |

| Write:   | T7     | T6 | T5 | T4        | T3         | T2 | T1 | T0    |

| Reset:   |        |    |    | Unaffecte | d by reset |    |    |       |

Figure 9-15. SCI Data Register (SCDR)

#### R7/T7-R0/T0 — Receive/Transmit Data Bits

Reading the SCDR accesses the read-only received data bits, R[7:0]. Writing to the SCDR writes the data to be transmitted, T[7:0]. Reset has no effect on the SCDR.

#### NOTE

Do not use read/modify/write instructions on the SCI data register.

MC68HC908JL8/JK8 • MC68HC08JL8/JK8 • MC68HC908KL8 Data Sheet, Rev. 3.1

#### Analog-to-Digital Converter (ADC)

#### 10.5.2 **Stop Mode**

The ADC module is inactive after the execution of a STOP instruction. Any pending conversion is aborted. ADC conversions resume when the MCU exits stop mode. Allow one conversion cycle to stabilize the analog circuitry before attempting a new ADC conversion after exiting stop mode.

## 10.6 I/O Signals

The ADC module has 12 channels that are shared with I/O port B and port D, and one channel on ADC12/T2CLK pin.

#### 10.6.1 ADC Voltage In (ADCVIN)

ADCVIN is the input voltage signal from one of the 13 ADC channels to the ADC module.

## 10.7 I/O Registers

These I/O registers control and monitor ADC operation:

- ADC status and control register (ADSCR)

- ADC data register (ADR)

- ADC clock register (ADICLK)

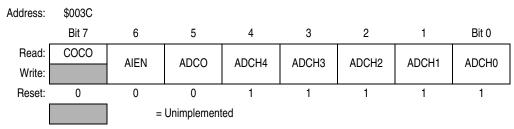

#### 10.7.1 ADC Status and Control Register

The following paragraphs describe the function of the ADC status and control register.

Figure 10-3. ADC Status and Control Register (ADSCR)

#### **COCO** — Conversions Complete Bit

When the AIEN bit is a logic 0, the COCO is a read-only bit which is set each time a conversion is completed. This bit is cleared whenever the ADC status and control register is written or whenever the ADC data register is read. Reset clears this bit.

- 1 = Conversion completed (AIEN = 0)

- 0 = Conversion not completed (AIEN = 0)

When the AIEN bit is a logic 1 (CPU interrupt enabled), the COCO is a read-only bit, and will always be logic 0 when read.

#### AIEN — ADC Interrupt Enable Bit

When this bit is set, an interrupt is generated at the end of an ADC conversion. The interrupt signal is cleared when the data register is read or the status/control register is written. Reset clears the AIEN bit.

- 1 = ADC interrupt enabled

- 0 = ADC interrupt disabled

MC68HC908JL8/JK8 • MC68HC08JL8/JK8 • MC68HC908KL8 Data Sheet, Rev. 3.1

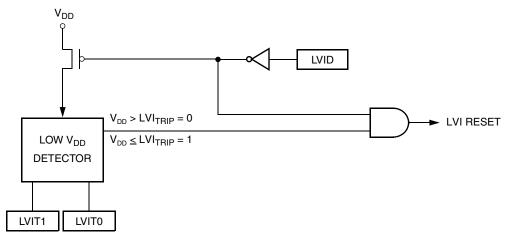

## Chapter 15 Low Voltage Inhibit (LVI)

#### 15.1 Introduction

This section describes the low-voltage inhibit module (LVI), which monitors the voltage on the  $V_{DD}$  pin and generates a reset when the  $V_{DD}$  voltage falls to the LVI trip (LVI<sub>TRIP</sub>) voltage.

#### 15.2 Features

Features of the LVI module include the following:

- Selectable LVI trip voltage

- Selectable LVI circuit disable

## 15.3 Functional Description

Figure 15-1 shows the structure of the LVI module. The LVI is enabled after a reset. The LVI module contains a bandgap reference circuit and comparator. Setting LVI disable bit (LVID) disables the LVI to monitor  $V_{DD}$  voltage. The LVI trip voltage selection bits (LVIT1, LVIT0) determine at which  $V_{DD}$  level the LVI module should take actions.

The LVI module generates one output signal:

**LVI Reset** — an reset signal will be generated to reset the CPU when V<sub>DD</sub> drops to below the set trip point.

Figure 15-1. LVI Module Block Diagram

MC68HC908JL8/JK8 • MC68HC08JL8/JK8 • MC68HC908KL8 Data Sheet, Rev. 3.1

#### **Electrical Specifications**

## 17.14 Memory Characteristics

**Table 17-12. Memory Characteristics**

| Characteristic                             | Symbol                             | Min | Max | Unit   |

|--------------------------------------------|------------------------------------|-----|-----|--------|

| RAM data retention voltage                 | V <sub>RDR</sub>                   | 1.3 | _   | V      |

| FLASH program bus clock frequency          | _                                  | 1   | _   | MHz    |

| FLASH read bus clock frequency             | f <sub>read</sub> <sup>(1)</sup>   | 32k | 8M  | Hz     |

| FLASH page erase time                      | t <sub>erase</sub> (2)             | 4   | _   | ms     |

| FLASH mass erase time                      | t <sub>merase</sub> <sup>(3)</sup> | 4   | _   | ms     |

| FLASH PGM/ERASE to HVEN set up time        | t <sub>nvs</sub>                   | 10  | _   | μs     |

| FLASH high-voltage hold time               | t <sub>nvh</sub>                   | 5   | _   | μs     |

| FLASH high-voltage hold time (mass erase)  | t <sub>nvhl</sub>                  | 100 | _   | μS     |

| FLASH program hold time                    | t <sub>pgs</sub>                   | 5   | _   | μs     |

| FLASH program time                         | t <sub>prog</sub>                  | 30  | 40  | μs     |

| FLASH return to read time                  | t <sub>rcv</sub> <sup>(4)</sup>    | 1   | _   | μs     |

| FLASH cumulative program hv period         | t <sub>HV</sub> <sup>(5)</sup>     | _   | 4   | ms     |

| FLASH row erase endurance <sup>(6)</sup>   | _                                  | 10k | _   | cycles |

| FLASH row program endurance <sup>(7)</sup> | _                                  | 10k | _   | cycles |

| FLASH data retention time <sup>(8)</sup>   |                                    | 10  | _   | years  |

- 1.  $f_{read}$  is defined as the frequency range for which the FLASH memory can be read.

- 2. If the page erase time is longer than t<sub>erase</sub> (Min), there is no erase-disturb, but it reduces the endurance of the FLASH

- 3. If the mass erase time is longer than t<sub>merase</sub> (Min), there is no erase-disturb, but it reduces the endurance of the FLASH

- 4. t<sub>rcv</sub> is defined as the time it needs before the FLASH can be read after turning off the high voltage charge pump, by clearing HVEN to logic 0.

- $5.\ t_{HV}$  is defined as the cumulative high voltage programming time to the same row before next erase.

- $t_{HV}$  must satisfy this condition:  $t_{nvs} + t_{nvh} + t_{pgs} + (t_{prog} \times 32) \le t_{HV}$  max. 6. The minimum row endurance value specifies each row of the FLASH memory is guaranteed to work for at least this many erase / program cycles.

- 7. The minimum row endurance value specifies each row of the FLASH memory is guaranteed to work for at least this many erase / program cycles.

- 8. The FLASH is guaranteed to retain data over the entire operating temperature range for at least the minimum time specified.

MC68HC908JL8/JK8 • MC68HC08JL8/JK8 • MC68HC908KL8 Data Sheet, Rev. 3.1 194 Freescale Semiconductor

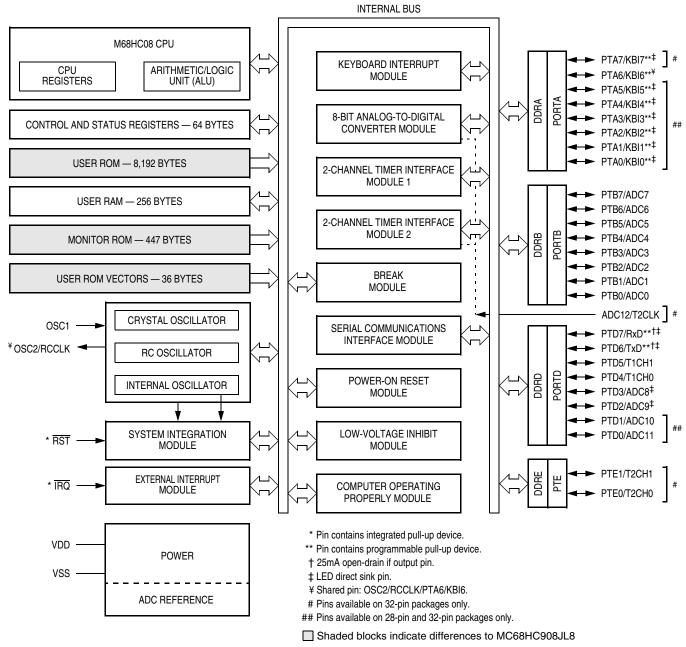

Figure A-1. MC68HC08JL8 Block Diagram

## A.4 Reserved Registers

The two registers at \$FE08 and \$FFCF are reserved locations on the MC68HC08JL8.

On the MC68HC908JL8, these two locations are the FLASH control register and the FLASH block protect register respectively.

Figure B-1. MC68HC908KL8 Block Diagram