Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Active                                                    |

| Core Processor             | HC08                                                      |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 8MHz                                                      |

| Connectivity               | SCI                                                       |

| Peripherals                | LED, LVD, POR, PWM                                        |

| Number of I/O              | 15                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                               |

| Data Converters            | A/D 13x8b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                         |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | 20-SOIC                                                   |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc908jk8cdwe |

## **Table of Contents**

## Chapter 17 Electrical Specifications

| 17.1         | Introduction                                           | 185 |

|--------------|--------------------------------------------------------|-----|

| 17.2         | Absolute Maximum Ratings                               | 185 |

| 17.3         | Functional Operating Range                             | 186 |

| 17.4         | Thermal Characteristics                                | 186 |

| 17.5         | 5V DC Electrical Characteristics                       | 187 |

| 17.6         | 5V Control Timing                                      | 188 |

| 17.7         | 5V Oscillator Characteristics                          | 188 |

| 17.8         | 3V DC Electrical Characteristics                       | 189 |

| 17.9         | 3V Control Timing                                      | 190 |

| 17.10        | 3V Oscillator Characteristics                          | 191 |

| 17.11        | Typical Supply Currents                                | 192 |

| 17.12        | Timer Interface Module Characteristics                 | 193 |

| 17.13        | ADC Characteristics                                    |     |

| 17.14        | Memory Characteristics                                 | 194 |

|              | Chapter 18                                             |     |

|              | Mechanical Specifications                              |     |

| 18.1         | Introduction                                           | 195 |

| 18.2         | 20-Pin Plastic Dual In-Line Package (PDIP)             | 195 |

| 18.3         | 20-Pin Small Outline Integrated Circuit Package (SOIC) |     |

| 18.4         | 28-Pin Plastic Dual In-Line Package (PDIP)             |     |

| 18.5         | 28-Pin Small Outline Integrated Circuit Package (SOIC) | 197 |

| 18.6         | 32-Pin Shrink Dual In-Line Package (SDIP)              | 197 |

| 18.7         | 32-Pin Low-Profile Quad Flat Pack (LQFP)               | 198 |

|              | Chapter 19                                             |     |

|              | Ordering Information                                   |     |

| 19.1         | Introduction                                           | 199 |

| 19.2         | MC Order Numbers                                       |     |

|              |                                                        |     |

|              | Appendix A                                             |     |

| Λ -1         | MC68HC08JL8                                            | 001 |

| A.1          | Introduction                                           |     |

| A.2<br>A.3   | MCU Block Diagram                                      |     |

| A.3<br>A.4   | Memory Map                                             |     |

| A.4<br>A.5   | Reserved Registers                                     |     |

| A.6          | Monitor ROM                                            |     |

| A.6<br>A.7   | Electrical Specifications                              |     |

| A.7<br>A.7.1 | DC Electrical Characteristics                          |     |

| A.8          | Memory Characteristics                                 |     |

| A.9          | MC68HC08JL8 Order Numbers                              |     |

|              |                                                        | _50 |

MC68HC908JL8/JK8 • MC68HC08JL8/JK8 • MC68HC908KL8 Data Sheet, Rev. 3.1

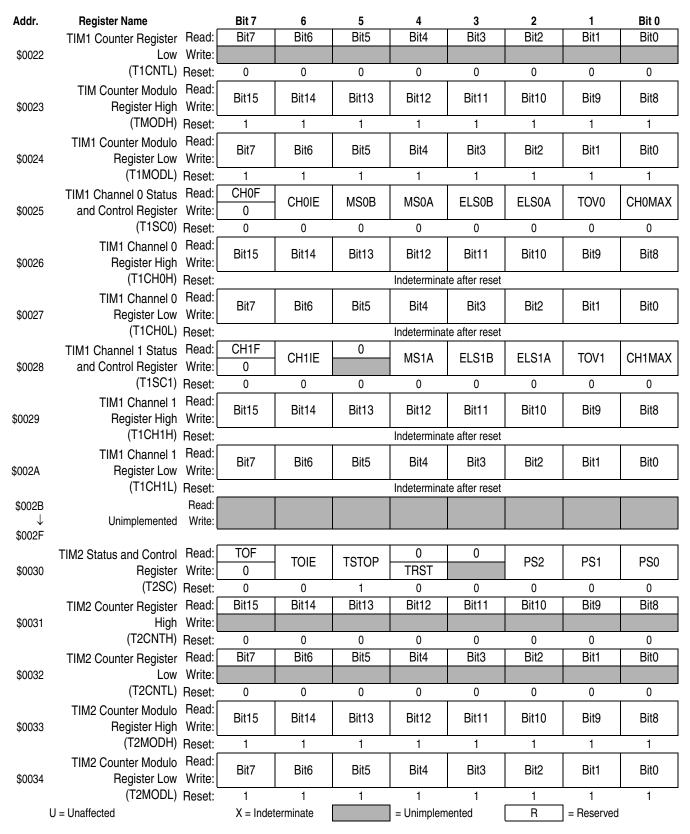

Figure 2-2. Control, Status, and Data Registers (Sheet 3 of 5)

MC68HC908JL8/JK8 • MC68HC08JL8/JK8 • MC68HC908KL8 Data Sheet, Rev. 3.1

## 2.4 Random-Access Memory (RAM)

Addresses \$0060 through \$015F are RAM locations. The location of the stack RAM is programmable. The 16-bit stack pointer allows the stack to be anywhere in the 64-Kbyte memory space.

#### NOTE

For correct operation, the stack pointer must point only to RAM locations.

Within page zero are 160 bytes of RAM. Because the location of the stack RAM is programmable, all page zero RAM locations can be used for I/O control and user data or code. When the stack pointer is moved from its reset location at \$00FF, direct addressing mode instructions can access efficiently all page zero RAM locations. Page zero RAM, therefore, provides ideal locations for frequently accessed global variables.

Before processing an interrupt, the CPU uses five bytes of the stack to save the contents of the CPU registers.

#### NOTE

For M6805 compatibility, the H register is not stacked.

During a subroutine call, the CPU uses two bytes of the stack to store the return address. The stack pointer decrements during pushes and increments during pulls.

#### NOTE

Be careful when using nested subroutines. The CPU may overwrite data in the RAM during a subroutine or during the interrupt stacking operation.

## 2.5 FLASH Memory

This sub-section describes the operation of the embedded FLASH memory. The FLASH memory can be read, programmed, and erased from a single external supply. The program and erase operations are enabled through the use of an internal charge pump.

## 2.6 Functional Description

The FLASH memory consists of an array of 8,192 bytes for user memory plus a block of 36 bytes for user interrupt vectors. *An erased bit reads as logic 1 and a programmed bit reads as a logic 0.* The FLASH memory page size is defined as 64 bytes, and is the minimum size that can be erased in a page erase operation. Program and erase operations are facilitated through control bits in FLASH control register (FLCR).

The address ranges for the FLASH memory are:

- \$DC00-\$FBFF; user memory; 12,288 bytes

- \$FFDC-\$FFFF; user interrupt vectors; 36 bytes

Programming tools are available from Freescale. Contact your local Freescale representative for more information.

#### NOTE

A security feature prevents viewing of the FLASH contents. (1)

MC68HC908JL8/JK8 • MC68HC08JL8/JK8 • MC68HC908KL8 Data Sheet, Rev. 3.1

<sup>1.</sup> No security feature is absolutely secure. However, Motorola's strategy is to make reading or copying the FLASH difficult for unauthorized users.

#### Memory

- 8. Wait for time,  $t_{prog}$  (30 $\mu$ s).

- 9. Repeat steps 7 and 8 until all bytes within the row are programmed.

- 10. Clear the PGM bit.

- 11. Wait for time,  $t_{nvh}$  (5 $\mu$ s).

- 12. Clear the HVEN bit.

- 13. After time,  $t_{rcv}$  (1 $\mu$ s), the memory can be accessed in read mode again.

This program sequence is repeated throughout the memory until all data is programmed.

#### NOTE

The time between each FLASH address change (step 7 to step 7), or the time between the last FLASH addressed programmed to clearing the PGM bit (step 7 to step 10), must not exceed the maximum programming time,  $t_{prog}$  max.

#### **NOTE**

Programming and erasing of FLASH locations cannot be performed by code being executed from the FLASH memory. While these operations must be performed in the order shown, other unrelated operations may occur between the steps.

Memory

MC68HC908JL8/JK8 • MC68HC08JL8/JK8 • MC68HC908KL8 Data Sheet, Rev. 3.1

## **Table 4-1. Instruction Set Summary**

| Source                                                                                          | Operation                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    | Ef |    | ct ( | on        |    | Address<br>Mode                              | Opcode                                           | Operand                                         | Cycles                               |

|-------------------------------------------------------------------------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|----|------|-----------|----|----------------------------------------------|--------------------------------------------------|-------------------------------------------------|--------------------------------------|

| Form                                                                                            |                           | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ٧  | Н  | I  | N    | Z         | С  | Ad                                           | o                                                | o                                               | ે                                    |

| STX opr<br>STX opr,<br>STX opr,X<br>STX opr,X<br>STX ,X<br>STX opr,SP<br>STX opr,SP             | Store X in M              | M ← (X)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0  | _  | _  | \$   | \$        | _  | DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | BF<br>CF<br>DF<br>EF<br>FF<br>9EEF<br>9EDF       | dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff       | 3<br>4<br>4<br>3<br>2<br>4<br>5      |

| SUB #opr<br>SUB opr<br>SUB opr,X<br>SUB opr,X<br>SUB opr,X<br>SUB,X<br>SUB opr,SP<br>SUB opr,SP | Subtract                  | $A \leftarrow (A) - (M)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | \$ | _  | _  | \$   | <b>\$</b> | \$ | IMM DIR EXT IX2 IX1 IX SP1 SP2               | A0<br>B0<br>C0<br>D0<br>E0<br>F0<br>9EE0<br>9ED0 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| SWI                                                                                             | Software Interrupt        | $\begin{array}{c} \text{PC} \leftarrow (\text{PC}) + 1;  \text{Push (PCL)} \\ \text{SP} \leftarrow (\text{SP}) - 1;  \text{Push (PCH)} \\ \text{SP} \leftarrow (\text{SP}) - 1;  \text{Push (X)} \\ \text{SP} \leftarrow (\text{SP}) - 1;  \text{Push (A)} \\ \text{SP} \leftarrow (\text{SP}) - 1;  \text{Push (CCR)} \\ \text{SP} \leftarrow (\text{SP}) - 1;  \text{I} \leftarrow 1 \\ \text{PCH} \leftarrow \text{Interrupt Vector High Byte} \\ \text{PCL} \leftarrow \text{Interrupt Vector Low Byte} \end{array}$ | _  | _  | 1  | _    | _         | _  | INH                                          | 83                                               |                                                 | 9                                    |

| TAP                                                                                             | Transfer A to CCR         | CCR ← (A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | \$ | \$ | \$ | \$   | \$        | \$ | INH                                          | 84                                               |                                                 | 2                                    |

| TAX                                                                                             | Transfer A to X           | X ← (A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _  | _  | _  | -    | _         | -  | INH                                          | 97                                               |                                                 | 1                                    |

| TPA                                                                                             | Transfer CCR to A         | A ← (CCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -  | _  | _  | -    | -         | -  | INH                                          | 85                                               |                                                 | 1                                    |

| TST opr<br>TSTA<br>TSTX<br>TST opr,X<br>TST ,X<br>TST opr,SP                                    | Test for Negative or Zero | (A) – \$00 or (X) – \$00 or (M) – \$00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0  | _  | _  | \$   | \$        | _  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1        | 3D<br>4D<br>5D<br>6D<br>7D<br>9E6D               | dd<br>ff<br>ff                                  | 3<br>1<br>1<br>3<br>2<br>4           |

| TSX                                                                                             | Transfer SP to H:X        | H:X ← (SP) + 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -  | _  | _  | -    | _         | -  | INH                                          | 95                                               |                                                 | 2                                    |

| TXA                                                                                             | Transfer X to A           | A ← (X)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -  | _  | _  | _    | _         | _  | INH                                          | 9F                                               |                                                 | 1                                    |

| TXS                                                                                             | Transfer H:X to SP        | (SP) ← (H:X) – 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -  | _  | _  | -    | -         | -  | INH                                          | 94                                               |                                                 | 2                                    |

#### **System Integration Module (SIM)**

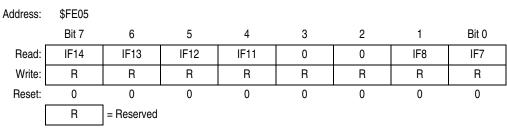

#### 5.5.2.2 Interrupt Status Register 2

Figure 5-13. Interrupt Status Register 2 (INT2)

## IF7, IF8, IF11 to F14 — Interrupt Flags

This flag indicates the presence of interrupt requests from the sources shown in Table 5-3.

- 1 = Interrupt request present

- 0 = No interrupt request present

## Bit 2 and 3 — Always read 0

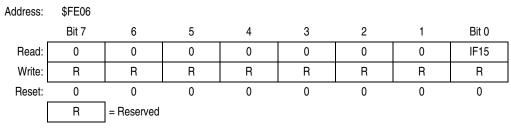

### 5.5.2.3 Interrupt Status Register 3

Figure 5-14. Interrupt Status Register 3 (INT3)

#### IF15 — Interrupt Flags

These flags indicate the presence of interrupt requests from the sources shown in Table 5-3.

- 1 = Interrupt request present

- 0 = No interrupt request present

## Bit 1 to 7 — Always read 0

#### 5.5.3 Reset

All reset sources always have equal and highest priority and cannot be arbitrated.

## 5.5.4 Break Interrupts

The break module can stop normal program flow at a software-programmable break point by asserting its break interrupt output. (See Chapter 16 Break Module (BREAK).) The SIM puts the CPU into the break state by forcing it to the SWI vector location. Refer to the break interrupt subsection of each module to see how each module is affected by the break state.

## 7.3.1 Entering Monitor Mode

Table 7-1 shows the pin conditions for entering monitor mode. As specified in the table, monitor mode may be entered after a POR.

Communication at 9600 baud will be established provided one of the following sets of conditions is met:

- 1. If  $\overline{IRQ} = V_{TST}$ :

- Clock on OSC1 is 4.9125MHz

- PTB3 = low

- 2. If  $\overline{IRQ} = V_{TST}$ :

- Clock on OSC1 is 9.8304MHz

- PTB3 = high

- 3. If \$FFFE and \$FFFF are blank (contain \$FF):

- Clock on OSC1 is 9.8304MHz

- $-\overline{IRQ} = V_{DD}$

Table 7-1. Monitor Mode Entry Requirements and Options

| ĪRQ                             | \$FFFE<br>and<br>\$FFFF    | PTB3 | PTB2 | PTB1 | PTB0 | OSC1 Clock <sup>(1)</sup> | Bus Frequency | Comments                                                                                                           |

|---------------------------------|----------------------------|------|------|------|------|---------------------------|---------------|--------------------------------------------------------------------------------------------------------------------|

| V <sub>TST</sub> <sup>(2)</sup> | Х                          | 0    | 0    | 1    | 1    | 4.9152MHz                 | 2.4576MHz     | High voltage entry to monitor mode.                                                                                |

| V <sub>TST</sub> <sup>(1)</sup> | Х                          | 1    | 0    | 1    | 1    | 9.8304MHz                 | 2.4576MHz     | 9600 baud communication on PTB0. COP disabled.                                                                     |

| V <sub>DD</sub>                 | BLANK<br>(contain<br>\$FF) | х    | х    | х    | 1    | 9.8304MHz                 | 2.4576MHz     | Blank reset vector<br>(low-voltage) entry to monitor<br>mode.<br>9600 baud communication on<br>PTB0. COP disabled. |

| V <sub>DD</sub>                 | NOT<br>BLANK               | Х    | Х    | Х    | Х    | Х                         | OSC1 ÷ 4      | Enters User mode.                                                                                                  |

- 1. RC oscillator cannot be used for monitor mode; must use either external oscillator or XTAL oscillator circuit.

- 2. See Table 17-4 for V<sub>TST</sub> voltage level requirements.

If  $V_{TST}$  is applied to  $\overline{IRQ}$  and PTB3 is low upon monitor mode entry (Table 7-1 condition set 1), the bus frequency is a divide-by-two of the clock input to OSC1. If PTB3 is high with  $V_{TST}$  applied to  $\overline{IRQ}$  upon monitor mode entry (Table 7-1 condition set 2), the bus frequency is a divide-by-four of the clock input to OSC1. Holding the PTB3 pin low when entering monitor mode causes a bypass of a divide-by-two stage at the oscillator *only if*  $V_{TST}$  is applied to  $\overline{IRQ}$ . In this event, the OSCOUT frequency is equal to the 2OSCOUT frequency, and OSC1 input directly generates internal bus clocks. In this case, the OSC1 signal must have a 50% duty cycle at maximum bus frequency.

Entering monitor mode with  $V_{TST}$  on  $\overline{IRQ}$ , the COP is disabled as long as  $V_{TST}$  is applied to either  $\overline{IRQ}$  or  $\overline{RST}$ . (See Chapter 5 System Integration Module (SIM) for more information on modes of operation.)

If entering monitor mode without high voltage on IRQ and reset vector being blank (\$FFFE and \$FFFF) (Table 7-1 condition set 3, where applied voltage is  $V_{DD}$ ), then all port B pin requirements and conditions,

MC68HC908JL8/JK8 • MC68HC08JL8/JK8 • MC68HC908KL8 Data Sheet, Rev. 3.1

**Timer Interface Module (TIM)**

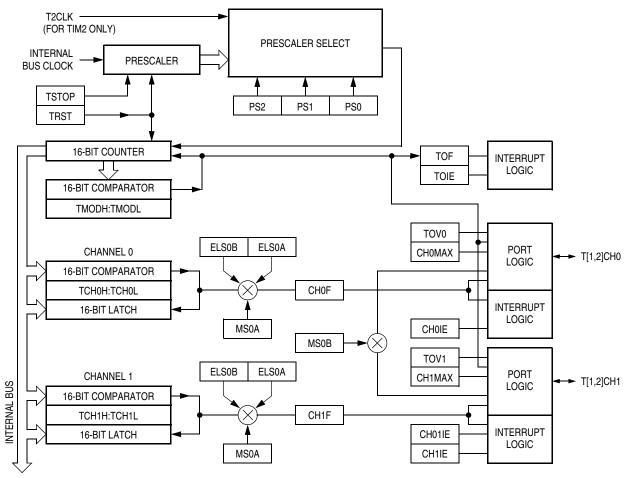

## 8.4 Functional Description

Figure 8-1 shows the structure of the TIM. The central component of the TIM is the 16-bit TIM counter that can operate as a free-running counter or a modulo up-counter. The TIM counter provides the timing reference for the input capture and output compare functions. The TIM counter modulo registers, TMODH:TMODL, control the modulo value of the TIM counter. Software can read the TIM counter value at any time without affecting the counting sequence.

The two TIM channels (per timer) are programmable independently as input capture or output compare channels.

Figure 8-1. TIM Block Diagram

Figure 8-2 summarizes the timer registers.

#### NOTE

References to either timer 1 or timer 2 may be made in the following text by omitting the timer number. For example, TSC may generically refer to both T1SC and T2SC.

MC68HC908JL8/JK8 • MC68HC08JL8/JK8 • MC68HC908KL8 Data Sheet, Rev. 3.1

#### **Timer Interface Module (TIM)**

Setting MS0B disables the channel 1 status and control register and reverts TCH1 to general-purpose I/O.

Reset clears the MSxB bit.

- 1 = Buffered output compare/PWM operation enabled

- 0 = Buffered output compare/PWM operation disabled

#### MSxA — Mode Select Bit A

When ELSxB:ELSxA  $\neq$  0:0, this read/write bit selects either input capture operation or unbuffered output compare/PWM operation.

See Table 8-3.

- 1 = Unbuffered output compare/PWM operation

- 0 = Input capture operation

When ELSxB:ELSxA = 0:0, this read/write bit selects the initial output level of the TCHx pin. See Table 8-3. Reset clears the MSxA bit.

- 1 = Initial output level low

- 0 = Initial output level high

#### NOTE

Before changing a channel function by writing to the MSxB or MSxA bit, set the TSTOP and TRST bits in the TIM status and control register (TSC).

## ELSxB and ELSxA — Edge/Level Select Bits

When channel x is an input capture channel, these read/write bits control the active edge-sensing logic on channel x.

When channel x is an output compare channel, ELSxB and ELSxA control the channel x output behavior when an output compare occurs.

When ELSxB and ELSxA are both clear, channel x is not connected to an I/O port, and pin TCHx is available as a general-purpose I/O pin. Table 8-3 shows how ELSxB and ELSxA work. Reset clears the ELSxB and ELSxA bits.

Table 8-3. Mode, Edge, and Level Selection

| MSxB:MSxA | ELSxB:ELSxA | Mode                     | Configuration                                        |

|-----------|-------------|--------------------------|------------------------------------------------------|

| X0        | 00          | Output procet            | Pin under port control;<br>initial output level high |

| X1        | 00          | Output preset            | Pin under port control;<br>initial output level low  |

| 00        | 01          |                          | Capture on rising edge only                          |

| 00        | 10          | Input capture            | Capture on falling edge only                         |

| 00        | 11          |                          | Capture on rising or falling edge                    |

| 01        | 01          | _                        | Toggle output on compare                             |

| 01        | 10          | Output compare<br>or PWM | Clear output on compare                              |

| 01        | 11          | 0                        | Set output on compare                                |

| 1X        | 01          | Buffered output          | Toggle output on compare                             |

| 1X        | 10          | compare or               | Clear output on compare                              |

| 1X        | 11          | buffered PWM             | Set output on compare                                |

MC68HC908JL8/JK8 • MC68HC08JL8/JK8 • MC68HC908KL8 Data Sheet, Rev. 3.1

#### **Timer Interface Module (TIM)**

Address: T1CH0H, \$0026 and T2CH0H, \$0036

|                 | Bit 7  | 6  | 5  | 4  | 3  | 2  | 1 | Bit 0 |

|-----------------|--------|----|----|----|----|----|---|-------|

| Read:<br>Write: | Bit 15 | 14 | 13 | 12 | 11 | 10 | 9 | Bit 8 |

Reset: Indeterminate after reset

Figure 8-12. TIM Channel 0 Register High (TCH0H)

Address: T1CH0L, \$0027 and T2CH0L \$0037

|                 | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

|-----------------|-------|---|---|---|---|---|---|-------|

| Read:<br>Write: | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

Reset: Indeterminate after reset

Figure 8-13. TIM Channel 0 Register Low (TCH0L)

Address: T1CH1H, \$0029 and T2CH1H, \$0039

|                 | Bit 7  | 6  | 5  | 4            | 3              | 2  | 1 | Bit 0 |

|-----------------|--------|----|----|--------------|----------------|----|---|-------|

| Read:<br>Write: | Bit 15 | 14 | 13 | 12           | 11             | 10 | 9 | Bit 8 |

| Reset:          |        |    |    | Indeterminat | te after reset |    |   |       |

Figure 8-14. TIM Channel 1 Register High (TCH1H)

Address: T1CH1L, \$002A and T2CH1L, \$003A

|                 | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

|-----------------|-------|---|---|---|---|---|---|-------|

| Read:<br>Write: | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

Reset: Indeterminate after reset

Figure 8-15. TIM Channel 1 Register Low (TCH1L)

## **Chapter 9 Serial Communications Interface (SCI)**

## 9.1 Introduction

This section describes the serial communications interface (SCI) module, which allows high-speed asynchronous communications with peripheral devices and other MCUs.

## 9.2 Features

Features of the SCI module include the following:

- Full-duplex operation

- Standard mark/space non-return-to-zero (NRZ) format

- 32 programmable baud rates

- Programmable 8-bit or 9-bit character length

- Separately enabled transmitter and receiver

- Separate receiver and transmitter CPU interrupt requests

- Programmable transmitter output polarity

- Two receiver wakeup methods:

- Idle line wakeup

- Address mark wakeup

- Interrupt-driven operation with eight interrupt flags:

- Transmitter empty

- Transmission complete

- Receiver full

- Idle receiver input

- Receiver overrun

- Noise error

- Framing error

- Parity error

- Receiver framing error detection

- Hardware parity checking

- 1/16 bit-time noise detection

- Bus clock as baud rate clock source

## 9.3 Pin Name Conventions

The generic names of the SCI I/O pins are:

- RxD (receive data)

- TxD (transmit data)

The SCI I/O (input/output) lines are dedicated pins for the SCI module. Table 9-1 shows the full names and the generic names of the SCI I/O pins.

MC68HC908JL8/JK8 • MC68HC08JL8/JK8 • MC68HC908KL8 Data Sheet, Rev. 3.1

#### TE — Transmitter Enable Bit

Setting this read/write bit begins the transmission by sending a preamble of 10 or 11 logic 1s from the transmit shift register to the TxD pin. If software clears the TE bit, the transmitter completes any transmission in progress before the TxD returns to the idle condition (logic 1). Clearing and then setting TE during a transmission queues an idle character to be sent after the character currently being transmitted. Reset clears the TE bit.

- 1 = Transmitter enabled

- 0 = Transmitter disabled

#### NOTE

Writing to the TE bit is not allowed when the enable SCI bit (ENSCI) is clear. ENSCI is in SCI control register 1.

#### RE — Receiver Enable Bit

Setting this read/write bit enables the receiver. Clearing the RE bit disables the receiver but does not affect receiver interrupt flag bits. Reset clears the RE bit.

- 1 = Receiver enabled

- 0 = Receiver disabled

#### NOTE

Writing to the RE bit is not allowed when the enable SCI bit (ENSCI) is clear. ENSCI is in SCI control register 1.

## RWU — Receiver Wakeup Bit

This read/write bit puts the receiver in a standby state during which receiver interrupts are disabled. The WAKE bit in SCC1 determines whether an idle input or an address mark brings the receiver out of the standby state and clears the RWU bit. Reset clears the RWU bit.

- 1 = Standby state

- 0 = Normal operation

#### SBK — Send Break Bit

Setting and then clearing this read/write bit transmits a break character followed by a logic 1. The logic 1 after the break character guarantees recognition of a valid start bit. If SBK remains set, the transmitter continuously transmits break characters with no logic 1s between them. Reset clears the SBK bit.

- 1 = Transmit break characters

- 0 = No break characters being transmitted

#### NOTE

Do not toggle the SBK bit immediately after setting the SCTE bit. Toggling SBK before the preamble begins causes the SCI to send a break character instead of a preamble.

## **NEIE** — Receiver Noise Error Interrupt Enable Bit

This read/write bit enables SCI error CPU interrupt requests generated by the noise error bit, NE. Reset clears NEIE.

- 1 = SCI error CPU interrupt requests from NE bit enabled

- 0 = SCI error CPU interrupt requests from NE bit disabled

## FEIE — Receiver Framing Error Interrupt Enable Bit

This read/write bit enables SCI error CPU interrupt requests generated by the framing error bit, FE. Reset clears FEIE.

- 1 = SCI error CPU interrupt requests from FE bit enabled

- 0 = SCI error CPU interrupt requests from FE bit disabled

## PEIE — Receiver Parity Error Interrupt Enable Bit

This read/write bit enables SCI error CPU interrupt requests generated by the parity error bit, PE.

(See 9.8.4 SCI Status Register 1.) Reset clears PEIE.

- 1 = SCI error CPU interrupt requests from PE bit enabled

- 0 = SCI error CPU interrupt requests from PE bit disabled

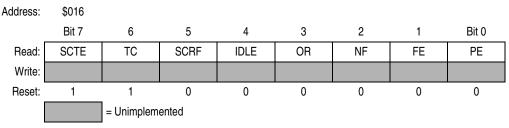

## 9.8.4 SCI Status Register 1

SCI status register 1 (SCS1) contains flags to signal these conditions:

- Transfer of SCDR data to transmit shift register complete

- Transmission complete

- Transfer of receive shift register data to SCDR complete

- Receiver input idle

- Receiver overrun

- Noisy data

- Framing error

- Parity error

Figure 9-12. SCI Status Register 1 (SCS1)

## **SCTE** — **SCI** Transmitter Empty Bit

This clearable, read-only bit is set when the SCDR transfers a character to the transmit shift register. SCTE can generate an SCI transmitter CPU interrupt request. When the SCTIE bit in SCC2 is set, SCTE generates an SCI transmitter CPU interrupt request. In normal operation, clear the SCTE bit by reading SCS1 with SCTE set and then writing to SCDR. Reset sets the SCTE bit.

- 1 = SCDR data transferred to transmit shift register

- 0 = SCDR data not transferred to transmit shift register

## FE — Receiver Framing Error Bit

This clearable, read-only bit is set when a logic 0 is accepted as the stop bit. FE generates an SCI error CPU interrupt request if the FEIE bit in SCC3 also is set. Clear the FE bit by reading SCS1 with FE set and then reading the SCDR. Reset clears the FE bit.

- 1 = Framing error detected

- 0 = No framing error detected

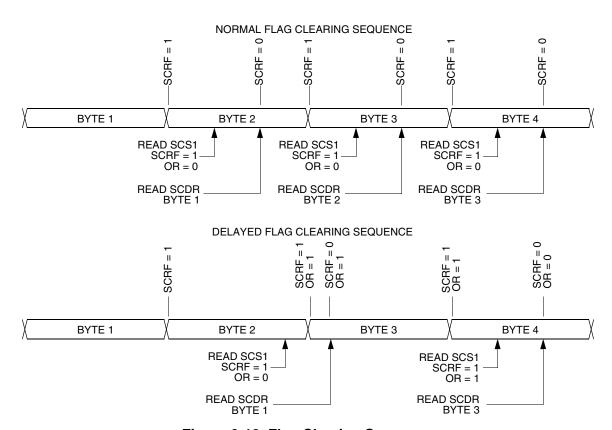

Figure 9-13. Flag Clearing Sequence

#### PE — Receiver Parity Error Bit

This clearable, read-only bit is set when the SCI detects a parity error in incoming data. PE generates an SCI error CPU interrupt request if the PEIE bit in SCC3 is also set. Clear the PE bit by reading SCS1 with PE set and then reading the SCDR. Reset clears the PE bit.

- 1 = Parity error detected

- 0 = No parity error detected

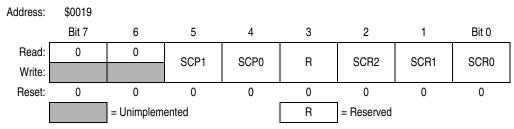

## 9.8.7 SCI Baud Rate Register

The baud rate register (SCBR) selects the baud rate for both the receiver and the transmitter.

Figure 9-16. SCI Baud Rate Register (SCBR)

### SCP1 and SCP0 — SCI Baud Rate Prescaler Bits

These read/write bits select the baud rate prescaler divisor as shown in Table 9-6. Reset clears SCP1 and SCP0.

Table 9-6. SCI Baud Rate Prescaling

| SCP1 and SCP0 | Prescaler Divisor (PD) |

|---------------|------------------------|

| 00            | 1                      |

| 01            | 3                      |

| 10            | 4                      |

| 11            | 13                     |

## SCR2-SCR0 — SCI Baud Rate Select Bits

These read/write bits select the SCI baud rate divisor as shown in Table 9-7. Reset clears SCR2–SCR0.

**Table 9-7. SCI Baud Rate Selection**

| SCR2, SCR1, and SCR0 | Baud Rate Divisor (BD) |

|----------------------|------------------------|

| 000                  | 1                      |

| 001                  | 2                      |

| 010                  | 4                      |

| 011                  | 8                      |

| 100                  | 16                     |

| 101                  | 32                     |

| 110                  | 64                     |

| 111                  | 128                    |

#### Use this formula to calculate the SCI baud rate:

baud rate =

$$\frac{SCI \text{ clock source}}{64 \times PD \times BD}$$

#### where:

SCI clock source = bus clock

PD = prescaler divisor

BD = baud rate divisor

Table 9-8 shows the SCI baud rates that can be generated with a 4.9152MHz bus clock.

MC68HC908JL8/JK8 • MC68HC08JL8/JK8 • MC68HC908KL8 Data Sheet, Rev. 3.1

#### Input/Output (I/O) Ports

When DDREx is a logic 1, reading address \$0008 reads the PTEx data latch. When DDREx is a logic 0, reading address \$0008 reads the voltage level on the pin. The data latch can always be written, regardless of the state of its data direction bit. Table 11-5 summarizes the operation of the port E pins.

**Table 11-5. Port E Pin Functions**

| DDRE Bit | PTE Bit          | I/O Pin Mode               | Accesses to DDRE | Access   | es to PTE               |

|----------|------------------|----------------------------|------------------|----------|-------------------------|

| DDNE BIL | PIEBIL           | 70 Fill Wode               | Read/Write       | Read     | Write                   |

| 0        | X <sup>(1)</sup> | Input, Hi-Z <sup>(2)</sup> | DDRE[1:0]        | Pin      | PTE[1:0] <sup>(3)</sup> |

| 1        | Х                | Output                     | DDRE[1:0]        | PTE[1:0] | PTE[1:0]                |

<sup>1.</sup> X = don't care.

<sup>2.</sup> Hi-Z = high impedance.

<sup>3.</sup> Writing affects data register, but does not affect the input.

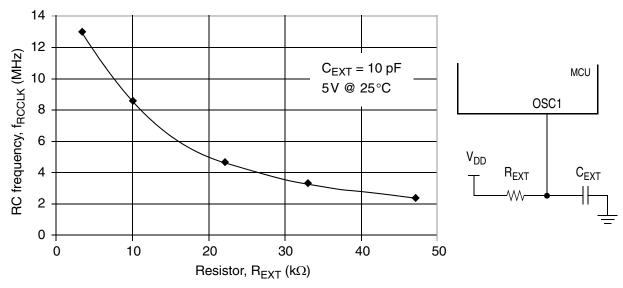

Figure 17-2. RC vs. Frequency (5V @25°C)

## 17.8 3V DC Electrical Characteristics

Table 17-7. DC Electrical Characteristics (3V)

| Characteristic <sup>(1)</sup>                                                                                                                                                                                                                                                              | Symbol          | Min                   | Typ <sup>(2)</sup>             | Max                           | Unit                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------|--------------------------------|-------------------------------|----------------------------|

| Output high voltage (I <sub>LOAD</sub> = -1.0mA)<br>PTA0-PTA7, PTB0-PTB7, PTD0-PTD7, PTE0-PTE1                                                                                                                                                                                             | V <sub>OH</sub> | V <sub>DD</sub> -0.4  | _                              | _                             | V                          |

| Output low voltage (I <sub>LOAD</sub> = 0.8mA) PTA6, PTB0-PTB7, PTD0, PTD1, PTD4, PTD5, PTE0-PTE1                                                                                                                                                                                          | V <sub>OL</sub> | _                     | _                              | 0.4                           | V                          |

| Output low voltage (I <sub>LOAD</sub> = 20mA)<br>PTD6, PTD7                                                                                                                                                                                                                                | V <sub>OL</sub> | _                     | _                              | 0.5                           | V                          |

| LED drives (V <sub>OL</sub> = 1.8V)<br>PTA0-PTA5, PTA7, PTD2, PTD3, PTD6, PTD7                                                                                                                                                                                                             | I <sub>OL</sub> | 3                     | 8                              | 12                            | mA                         |

| Input high voltage PTA0-PTA7, PTB0-PTB7, PTD0-PTD7, PTE0-PTE1, RST, IRQ, OSC1                                                                                                                                                                                                              | V <sub>IH</sub> | $0.7 \times V_{DD}$   | _                              | V <sub>DD</sub>               | V                          |

| Input low voltage PTA0-PTA7, PTB0-PTB7, PTD0-PTD7, PTE0-PTE1, RST, IRQ, OSC1                                                                                                                                                                                                               | V <sub>IL</sub> | V <sub>SS</sub>       | _                              | $0.3 \times V_{DD}$           | V                          |

| V <sub>DD</sub> supply current, f <sub>OP</sub> = 4MHz Run <sup>(3)</sup> XTAL oscillator option RC oscillator option Wait <sup>(4)</sup> XTAL oscillator option RC oscillator option Stop <sup>(5)</sup> (-40°C to 85°C) XTAL oscillator option RC oscillator option RC oscillator option | I <sub>DD</sub> | _<br>_<br>_<br>_<br>_ | 3<br>4<br>1<br>2<br>0.5<br>0.3 | 8<br>10<br>4.5<br>6<br>5<br>2 | mA<br>mA<br>mA<br>mA<br>μA |

| Digital I/O ports Hi-Z leakage current                                                                                                                                                                                                                                                     | I <sub>IL</sub> | _                     | _                              | ± 10                          | μΑ                         |

| Input current                                                                                                                                                                                                                                                                              | I <sub>IN</sub> | _                     | _                              | ± 1                           | μА                         |

## MC68HC908JL8/JK8 • MC68HC08JL8/JK8 • MC68HC908KL8 Data Sheet, Rev. 3.1

# **Chapter 19 Ordering Information**

## 19.1 Introduction

This section contains ordering numbers for the MC68HC908JL8.

## 19.2 MC Order Numbers

**Table 19-1. MC Order Numbers**

| MC Order Number | Operating<br>Temperature Range | Package       |  |

|-----------------|--------------------------------|---------------|--|

| MC68HC908JK8CP  | −40 °C to +85 °C               | 20-pin PDIP   |  |

| MC68HC908JK8MP  | -40 °C to +125 °C              |               |  |

| MC68HC908JK8CDW | −40 °C to +85 °C               | 20-pin SOIC   |  |

| MC68HC908JK8MDW | −40 °C to +125 °C              |               |  |

| MC68HC908JL8CP  | −40 °C to +85 °C               | - 28-pin PDIP |  |

| MC68HC908JL8MP  | −40 °C to +125 °C              |               |  |

| MC68HC908JL8CDW | -40 °C to +85 °C               | 28-pin SOIC   |  |

| MC68HC908JL8MDW | −40 °C to +125 °C              |               |  |

| MC68HC908JL8CSP | −40 °C to +85 °C               | 32-pin SDIP   |  |

| MC68HC908JL8MSP | −40 °C to +125 °C              |               |  |

| MC68HC908JL8CFA | −40 °C to +85 °C               | 32-pin LQFP   |  |

| MC68HC908JL8MFA | −40 °C to +125 °C              |               |  |

NOTE: Temperature grade "M" is available for  $V_{DD}$  = 5V only.

| \$0000                | I/O REGISTERS                              |

|-----------------------|--------------------------------------------|

| ↓<br>\$003F           | 64 BYTES                                   |

| \$0040                | RESERVED                                   |

| ↓<br>\$005F           | 32 BYTES                                   |

| \$0060                | RAM                                        |

| ↓<br>\$015F           | 256 BYTES                                  |

| \$0160                | UNIMPLEMENTED                              |

| ↓<br>\$DBFF           | 55,968 BYTES                               |

| \$DC00                | ROM                                        |

| ↓<br>\$FBFF           | 8,192 BYTES                                |

| \$FC00                | UNIMPLEMENTED                              |

| ↓<br>\$FDFF           | 512 BYTES                                  |

| \$FE00                | BREAK STATUS REGISTER (BSR)                |

| \$FE01                | RESET STATUS REGISTER (RSR)                |

| \$FE02                | RESERVED                                   |

| \$FE03                | BREAK FLAG CONTROL REGISTER (BFCR)         |

| \$FE04                | INTERRUPT STATUS REGISTER 1 (INT1)         |

| \$FE05                | INTERRUPT STATUS REGISTER 2 (INT2)         |

| \$FE06                | INTERRUPT STATUS REGISTER 3 (INT3)         |

| \$FE07                | RESERVED                                   |

| \$FE08                | RESERVED                                   |

| \$FE09<br>↓<br>\$FF0B | RESERVED                                   |

| \$FE0C                | BREAK ADDRESS HIGH REGISTER (BRKH)         |

| \$FE0D                | BREAK ADDRESS LOW REGISTER (BRKL)          |

| \$FE0E                | BREAK STATUS AND CONTROL REGISTER (BRKSCR) |

| \$FE0F                | RESERVED                                   |

| \$FE10<br>↓           | MONITOR ROM                                |

| \$FFCE                | 447 BYTES                                  |

| \$FFCF                | RESERVED                                   |

| \$FFD0                | MASK OPTION REGISTER (MOR) — READ ONLY     |

| \$FFD1                | RESERVED                                   |

| ↓<br>\$FFDB           | 11 BYTES                                   |

| \$FFDC                | USER ROM VECTORS                           |

| ↓<br>\$FFFF           | 36 BYTES                                   |

|                       |                                            |

Figure A-2. MC68HC08JL8 Memory Map

MC68HC908JL8/JK8 • MC68HC08JL8/JK8 • MC68HC908KL8 Data Sheet, Rev. 3.1