Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                     |

|----------------------------|---------------------------------------------------------------------|

| Product Status             | Obsolete                                                            |

| Core Processor             | HC08                                                                |

| Core Size                  | 8-Bit                                                               |

| Speed                      | 8MHz                                                                |

| Connectivity               | SCI                                                                 |

| Peripherals                | LED, LVD, POR, PWM                                                  |

| Number of I/O              | 23                                                                  |

| Program Memory Size        | 8KB (8K x 8)                                                        |

| Program Memory Type        | FLASH                                                               |

| EEPROM Size                | -                                                                   |

| RAM Size                   | 256 x 8                                                             |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                         |

| Data Converters            | A/D 13x8b                                                           |

| Oscillator Type            | Internal                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                   |

| Mounting Type              | Through Hole                                                        |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                            |

| Supplier Device Package    | 28-PDIP                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908jl8cpe |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

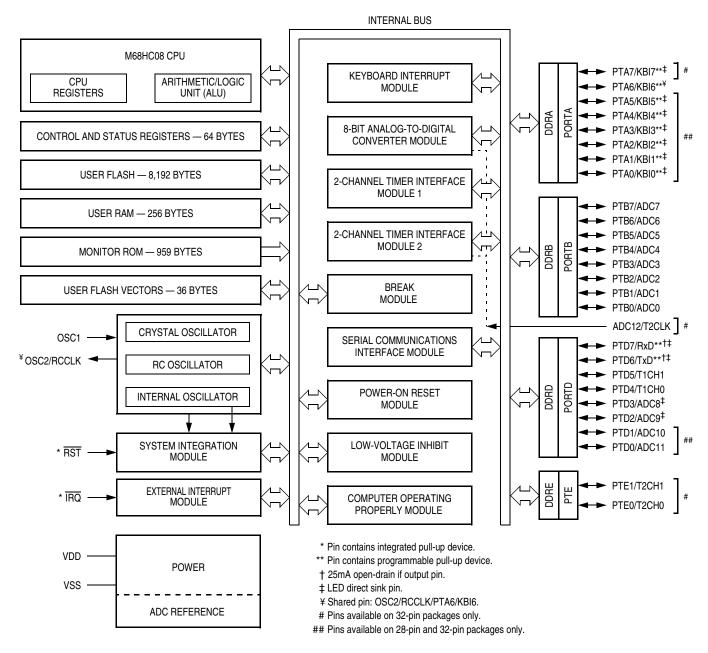

Figure 1-1. MC68HC908JL8 Block Diagram

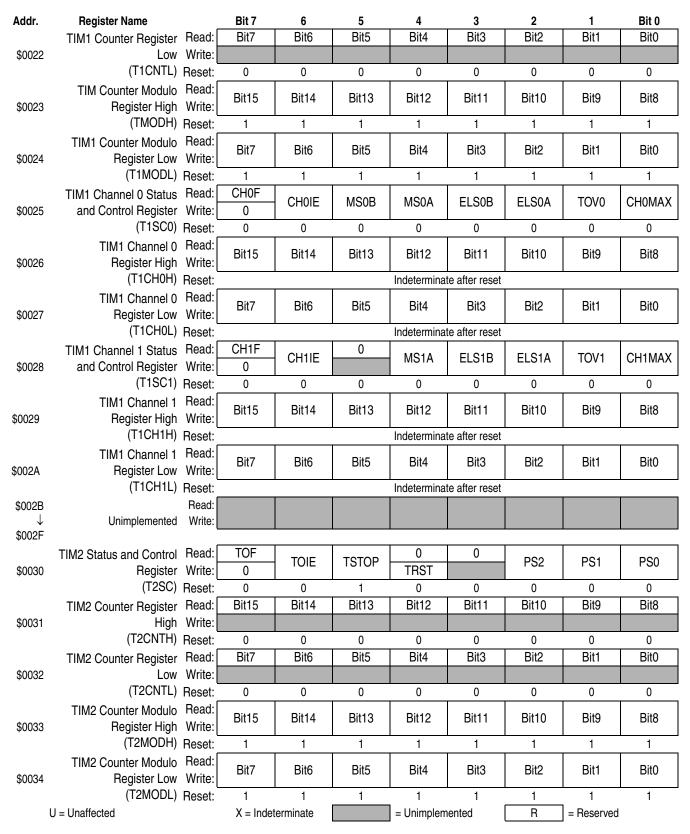

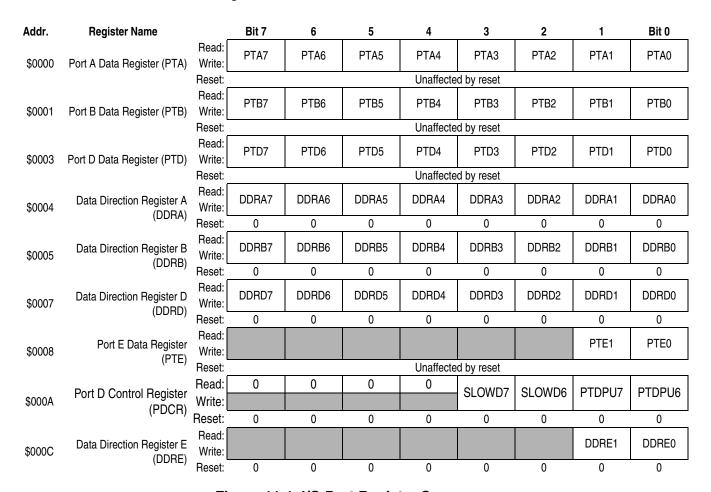

Figure 2-2. Control, Status, and Data Registers (Sheet 3 of 5)

MC68HC908JL8/JK8 • MC68HC08JL8/JK8 • MC68HC908KL8 Data Sheet, Rev. 3.1

#### **Central Processor Unit (CPU)**

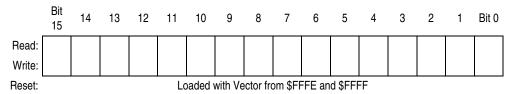

Figure 4-5. Program Counter (PC)

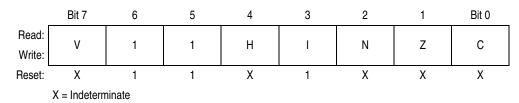

# 4.3.5 Condition Code Register

The 8-bit condition code register contains the interrupt mask and five flags that indicate the results of the instruction just executed. Bits 6 and 5 are set permanently to logic 1. The following paragraphs describe the functions of the condition code register.

Figure 4-6. Condition Code Register (CCR)

# V — Overflow Flag

The CPU sets the overflow flag when a two's complement overflow occurs. The signed branch instructions BGT, BGE, BLE, and BLT use the overflow flag.

- 1 = Overflow

- 0 = No overflow

## H — Half-Carry Flag

The CPU sets the half-carry flag when a carry occurs between accumulator bits 3 and 4 during an add-without-carry (ADD) or add-with-carry (ADC) operation. The half-carry flag is required for binary-coded decimal (BCD) arithmetic operations. The DAA instruction uses the states of the H and C flags to determine the appropriate correction factor.

- 1 = Carry between bits 3 and 4

- 0 = No carry between bits 3 and 4

## I — Interrupt Mask

When the interrupt mask is set, all maskable CPU interrupts are disabled. CPU interrupts are enabled when the interrupt mask is cleared. When a CPU interrupt occurs, the interrupt mask is set automatically after the CPU registers are saved on the stack, but before the interrupt vector is fetched.

- 1 = Interrupts disabled

- 0 = Interrupts enabled

### NOTE

To maintain M6805 Family compatibility, the upper byte of the index register (H) is not stacked automatically. If the interrupt service routine modifies H, then the user must stack and unstack H using the PSHH and PULH instructions.

**Central Processor Unit (CPU)**

#### **System Integration Module (SIM)**

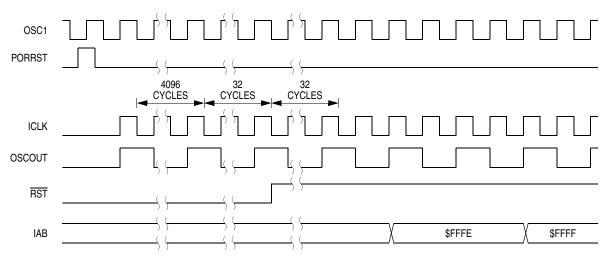

Figure 5-7. POR Recovery

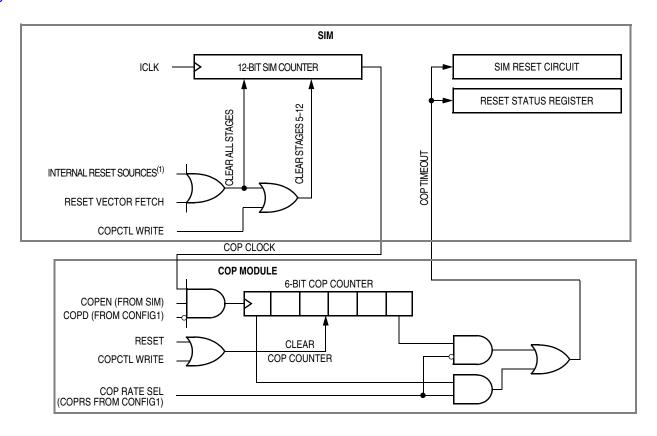

# 5.3.2.2 Computer Operating Properly (COP) Reset

An input to the SIM is reserved for the COP reset signal. The overflow of the COP counter causes an internal reset and sets the COP bit in the reset status register (RSR). The SIM actively pulls down the RST pin for all internal reset sources.

To prevent a COP module time-out, write any value to location \$FFFF. Writing to location \$FFFF clears the COP counter and stages 12 through 5 of the SIM counter. The SIM counter output, which occurs at least every  $(2^{12} - 2^4)$  ICLK cycles, drives the COP counter. The COP should be serviced as soon as possible out of reset to guarantee the maximum amount of time before the first time-out.

The COP module is disabled if the  $\overline{RST}$  pin or the  $\overline{IRQ}$  pin is held at  $V_{TST}$  while the MCU is in monitor mode. The COP module can be disabled only through combinational logic conditioned with the high voltage signal on the  $\overline{RST}$  or the  $\overline{IRQ}$  pin. This prevents the COP from becoming disabled as a result of external noise. During a break state,  $V_{TST}$  on the  $\overline{RST}$  pin disables the COP module.

## 5.3.2.3 Illegal Opcode Reset

The SIM decodes signals from the CPU to detect illegal instructions. An illegal instruction sets the ILOP bit in the reset status register (RSR) and causes a reset.

If the stop enable bit, STOP, in the mask option register is logic zero, the SIM treats the STOP instruction as an illegal opcode and causes an illegal opcode reset. The SIM actively pulls down the RST pin for all internal reset sources.

# 5.3.2.4 Illegal Address Reset

An opcode fetch from an unmapped address generates an illegal address reset. The SIM verifies that the CPU is fetching an opcode prior to asserting the ILAD bit in the reset status register (RSR) and resetting the MCU. A data fetch from an unmapped address does not generate a reset. The SIM actively pulls down the RST pin for all internal reset sources.

# 5.3.2.5 Low-Voltage Inhibit (LVI) Reset

The low-voltage inhibit module (LVI) asserts its output to the SIM when the  $V_{DD}$  voltage falls to the LVI trip voltage  $V_{TRIP}$ . The LVI bit in the reset status register (RSR) is set, and the external reset pin (RST) is

MC68HC908JL8/JK8 • MC68HC08JL8/JK8 • MC68HC908KL8 Data Sheet, Rev. 3.1

| Routine Name | Routine Description                                                   | Call Address | Stack Used <sup>(1)</sup><br>(bytes) |

|--------------|-----------------------------------------------------------------------|--------------|--------------------------------------|

| PRGRNGE      | Program a range of locations                                          | \$FC06       | 15                                   |

| ERARNGE      | Erase a page or the entire array                                      | \$FCBE       | 9                                    |

| LDRNGE       | Loads data from a range of locations                                  | \$FF30       | 9                                    |

| MON_PRGRNGE  | Program a range of locations in monitor mode                          | \$FF28       | 17                                   |

| MON_ERARNGE  | Erase a page or the entire array in monitor mode                      | \$FF2C       | 11                                   |

| MON_LDRNGE   | Loads data from a range of locations in monitor mode                  | \$FF24       | 11                                   |

| EE_WRITE     | Emulated EEPROM write. Data size ranges from 2 to 15 bytes at a time. | \$FD3F       | 24                                   |

| EE_READ      | Emulated EEPROM read. Data size ranges from 2 to 15 bytes at a time.  | \$FDD0       | 16                                   |

**Table 7-10. Summary of ROM-Resident Routines**

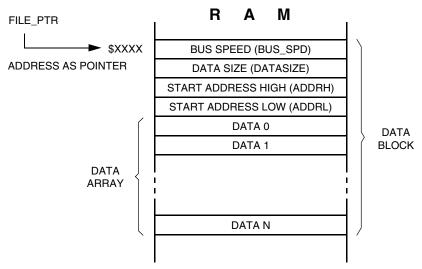

The routines are designed to be called as stand-alone subroutines in the user program or monitor mode. The parameters that are passed to a routine are in the form of a contiguous data block, stored in RAM. The index register (H:X) is loaded with the address of the first byte of the data block (acting as a pointer), and the subroutine is called (JSR). Using the start address as a pointer, multiple data blocks can be used, any area of RAM be used. A data block has the control and data bytes in a defined order, as shown in Figure 7-8.

During the software execution, it does not consume any dedicated RAM location, the run-time heap will extend the system stack, all other RAM location will not be affected.

Figure 7-8. Data Block Format for ROM-Resident Routines

MC68HC908JL8/JK8 • MC68HC08JL8/JK8 • MC68HC908KL8 Data Sheet, Rev. 3.1

<sup>1.</sup> The listed stack size excludes the 2 bytes used by the calling instruction, JSR.

**Monitor ROM (MON)**

# 7.5.6 MON\_LDRNGE

In monitor mode, LDRNGE is used to load the data array in RAM with data from a range of FLASH locations.

Table 7-16. ICP\_LDRNGE Routine

| Routine Name        | MON_LDRNGE                                                                                   |

|---------------------|----------------------------------------------------------------------------------------------|

| Routine Description | Loads data from a range of locations, in monitor mode                                        |

| Calling Address     | \$FF24                                                                                       |

| Stack Used          | 11 bytes                                                                                     |

| Data Block Format   | Bus speed Data size Starting address (high byte) Starting address (low byte) Data 1 : Data N |

The MON\_LDRNGE routine is designed to be used in monitor mode. It performs the same function as the LDRNGE routine (see 7.5.3 LDRNGE), except that MON\_LDRNGE returns to the main program via an SWI instruction. After a MON\_LDRNGE call, the SWI instruction will return the control back to the monitor code.

# 7.5.7 EE WRITE

EE\_WRITE is used to write a set of data from the data array to FLASH.

Table 7-17. EE\_WRITE Routine

| Routine Name        | EE_WRITE                                                                                                                                                |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Routine Description | Emulated EEPROM write. Data size ranges from 2 to 15 bytes at a time.                                                                                   |

| Calling Address     | \$FD3F                                                                                                                                                  |

| Stack Used          | 24 bytes                                                                                                                                                |

| Data Block Format   | Bus speed (BUS_SPD) Data size (DATASIZE) <sup>(1)</sup> Starting address (ADDRH) <sup>(2)</sup> Starting address (ADDRL) <sup>(1)</sup> Data 1 : Data N |

<sup>1.</sup> The minimum data size is 2 bytes. The maximum data size is 15 bytes.

The start location of the FLASH to be programmed is specified by the address ADDRH:ADDRL and the number of bytes in the data array is specified by DATASIZE. The minimum number of bytes that can be

MC68HC908JL8/JK8 • MC68HC08JL8/JK8 • MC68HC908KL8 Data Sheet, Rev. 3.1

<sup>2.</sup> The start address must be a page boundary start address: \$xx00, \$xx40, \$xx80, or \$00C0.

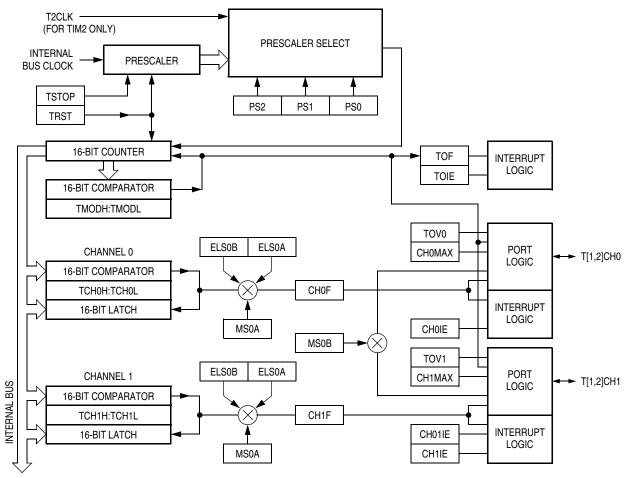

**Timer Interface Module (TIM)**

# 8.4 Functional Description

Figure 8-1 shows the structure of the TIM. The central component of the TIM is the 16-bit TIM counter that can operate as a free-running counter or a modulo up-counter. The TIM counter provides the timing reference for the input capture and output compare functions. The TIM counter modulo registers, TMODH:TMODL, control the modulo value of the TIM counter. Software can read the TIM counter value at any time without affecting the counting sequence.

The two TIM channels (per timer) are programmable independently as input capture or output compare channels.

Figure 8-1. TIM Block Diagram

Figure 8-2 summarizes the timer registers.

## NOTE

References to either timer 1 or timer 2 may be made in the following text by omitting the timer number. For example, TSC may generically refer to both T1SC and T2SC.

MC68HC908JL8/JK8 • MC68HC08JL8/JK8 • MC68HC908KL8 Data Sheet, Rev. 3.1

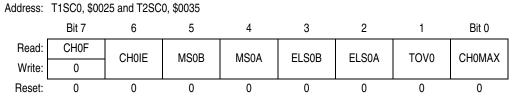

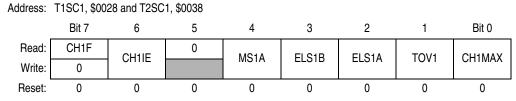

# 8.9.4 TIM Channel Status and Control Registers

Each of the TIM channel status and control registers:

- Flags input captures and output compares

- Enables input capture and output compare interrupts

- Selects input capture, output compare, or PWM operation

- Selects high, low, or toggling output on output compare

- · Selects rising edge, falling edge, or any edge as the active input capture trigger

- Selects output toggling on TIM overflow

- Selects 0% and 100% PWM duty cycle

- Selects buffered or unbuffered output compare/PWM operation

Figure 8-9. TIM Channel 0 Status and Control Register (TSC0)

Figure 8-10. TIM Channel 1 Status and Control Register (TSC1)

# CHxF — Channel x Flag Bit

When channel x is an input capture channel, this read/write bit is set when an active edge occurs on the channel x pin. When channel x is an output compare channel, CHxF is set when the value in the TIM counter registers matches the value in the TIM channel x registers.

When TIM CPU interrupt requests are enabled (CHxIE = 1), clear CHxF by reading TIM channel x status and control register with CHxF set and then writing a logic 0 to CHxF. If another interrupt request occurs before the clearing sequence is complete, then writing logic 0 to CHxF has no effect. Therefore, an interrupt request cannot be lost due to inadvertent clearing of CHxF.

Reset clears the CHxF bit. Writing a logic 1 to CHxF has no effect.

- 1 = Input capture or output compare on channel x

- 0 = No input capture or output compare on channel x

# **CHxIE** — Channel x Interrupt Enable Bit

This read/write bit enables TIM CPU interrupt service requests on channel x.

Reset clears the CHxIE bit.

- 1 = Channel x CPU interrupt requests enabled

- 0 = Channel x CPU interrupt requests disabled

#### MSxB — Mode Select Bit B

This read/write bit selects buffered output compare/PWM operation. MSxB exists only in the TIM1 channel 0 and TIM2 channel 0 status and control registers.

MC68HC908JL8/JK8 • MC68HC08JL8/JK8 • MC68HC908KL8 Data Sheet, Rev. 3.1

## **Timer Interface Module (TIM)**

Address: T1CH0H, \$0026 and T2CH0H, \$0036

|                 | Bit 7  | 6  | 5  | 4  | 3  | 2  | 1 | Bit 0 |

|-----------------|--------|----|----|----|----|----|---|-------|

| Read:<br>Write: | Bit 15 | 14 | 13 | 12 | 11 | 10 | 9 | Bit 8 |

Reset: Indeterminate after reset

Figure 8-12. TIM Channel 0 Register High (TCH0H)

Address: T1CH0L, \$0027 and T2CH0L \$0037

|                 | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

|-----------------|-------|---|---|---|---|---|---|-------|

| Read:<br>Write: | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

Reset: Indeterminate after reset

Figure 8-13. TIM Channel 0 Register Low (TCH0L)

Address: T1CH1H, \$0029 and T2CH1H, \$0039

|                 | Bit 7                         | 6  | 5  | 4  | 3  | 2  | 1 | Bit 0 |

|-----------------|-------------------------------|----|----|----|----|----|---|-------|

| Read:<br>Write: | Bit 15                        | 14 | 13 | 12 | 11 | 10 | 9 | Bit 8 |

| Reset:          | et: Indeterminate after reset |    |    |    |    |    |   |       |

Figure 8-14. TIM Channel 1 Register High (TCH1H)

Address: T1CH1L, \$002A and T2CH1L, \$003A

|                 | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

|-----------------|-------|---|---|---|---|---|---|-------|

| Read:<br>Write: | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

Reset: Indeterminate after reset

Figure 8-15. TIM Channel 1 Register Low (TCH1L)

#### **Serial Communications Interface (SCI)**

#### NOTE

When queueing an idle character, return the TE bit to logic 1 before the stop bit of the current character shifts out to the TxD pin. Setting TE after the stop bit appears on TxD causes data previously written to the SCDR to be lost.

Toggle the TE bit for a queued idle character when the SCTE bit becomes set and just before writing the next byte to the SCDR.

# 9.4.2.5 Inversion of Transmitted Output

The transmit inversion bit (TXINV) in SCI control register 1 (SCC1) reverses the polarity of transmitted data. All transmitted values, including idle, break, start, and stop bits, are inverted when TXINV is at logic 1. (See 9.8.1 SCI Control Register 1.)

# 9.4.2.6 Transmitter Interrupts

These conditions can generate CPU interrupt requests from the SCI transmitter:

- SCI transmitter empty (SCTE) The SCTE bit in SCS1 indicates that the SCDR has transferred

a character to the transmit shift register. SCTE can generate a transmitter CPU interrupt request.

Setting the SCI transmit interrupt enable bit, SCTIE, in SCC2 enables the SCTE bit to generate

transmitter CPU interrupt requests.

- Transmission complete (TC) The TC bit in SCS1 indicates that the transmit shift register and the SCDR are empty and that no break or idle character has been generated. The transmission complete interrupt enable bit, TCIE, in SCC2 enables the TC bit to generate transmitter CPU interrupt requests.

## 9.4.3 Receiver

Figure 9-5 shows the structure of the SCI receiver.

# 9.4.3.1 Character Length

The receiver can accommodate either 8-bit or 9-bit data. The state of the M bit in SCI control register 1 (SCC1) determines character length. When receiving 9-bit data, bit R8 in SCI control register 2 (SCC2) is the ninth bit (bit 8). When receiving 8-bit data, bit R8 is a copy of the eighth bit (bit 7).

# 9.4.3.2 Character Reception

During an SCI reception, the receive shift register shifts characters in from the RxD pin. The SCI data register (SCDR) is the read-only buffer between the internal data bus and the receive shift register.

After a complete character shifts into the receive shift register, the data portion of the character transfers to the SCDR. The SCI receiver full bit, SCRF, in SCI status register 1 (SCS1) becomes set, indicating that the received byte can be read. If the SCI receive interrupt enable bit, SCRIE, in SCC2 is also set, the SCRF bit generates a receiver CPU interrupt request.

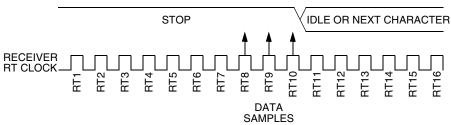

# **Fast Data Tolerance**

Figure 9-8 shows how much a fast received character can be misaligned without causing a noise error or a framing error. The fast stop bit ends at RT10 instead of RT16 but is still there for the stop bit data samples at RT8, RT9, and RT10.

Figure 9-8. Fast Data

For an 8-bit character, data sampling of the stop bit takes the receiver 9 bit times  $\times$  16 RT cycles + 10 RT cycles = 154 RT cycles.

With the misaligned character shown in Figure 9-8, the receiver counts 154 RT cycles at the point when the count of the transmitting device is

10 bit times  $\times$  16 RT cycles = 160 RT cycles.

The maximum percent difference between the receiver count and the transmitter count of a fast 8-bit character with no errors is

$$\left| \frac{154 - 160}{154} \right| \times 100 = 3.90\%$$

For a 9-bit character, data sampling of the stop bit takes the receiver 10 bit times  $\times$  16 RT cycles + 10 RT cycles = 170 RT cycles.

With the misaligned character shown in Figure 9-8, the receiver counts 170 RT cycles at the point when the count of the transmitting device is

11 bit times  $\times$  16 RT cycles = 176 RT cycles.

The maximum percent difference between the receiver count and the transmitter count of a fast 9-bit character with no errors is

$$\left| \frac{170 - 176}{170} \right| \times 100 = 3.53\%$$

## 9.4.3.6 Receiver Wakeup

So that the MCU can ignore transmissions intended only for other receivers in multiple-receiver systems, the receiver can be put into a standby state. Setting the receiver wakeup bit, RWU, in SCC2 puts the receiver into a standby state during which receiver interrupts are disabled.

Depending on the state of the WAKE bit in SCC1, either of two conditions on the RxD pin can bring the receiver out of the standby state:

# **Serial Communications Interface (SCI)**

**Table 9-8. SCI Baud Rate Selection Examples**

| SCP1 and SCP0 | Prescaler<br>Divisor (PD) | SCR2, SCR1,<br>and SCR0 | Baud Rate<br>Divisor (BD) | Baud Rate<br>(BUS CLOCK=4.9152MHz) |

|---------------|---------------------------|-------------------------|---------------------------|------------------------------------|

| 00            | 1                         | 000                     | 1                         | 76,800                             |

| 00            | 1                         | 001                     | 2                         | 38,400                             |

| 00            | 1                         | 010                     | 4                         | 19,200                             |

| 00            | 1                         | 011                     | 8                         | 9,600                              |

| 00            | 1                         | 100                     | 16                        | 4,800                              |

| 00            | 1                         | 101                     | 32                        | 2,400                              |

| 00            | 1                         | 110                     | 64                        | 1,200                              |

| 00            | 1                         | 111                     | 128                       | 600                                |

| 01            | 3                         | 000                     | 1                         | 25,600                             |

| 01            | 3                         | 001                     | 2                         | 12,800                             |

| 01            | 3                         | 010                     | 4                         | 6,400                              |

| 01            | 3                         | 011                     | 8                         | 3,200                              |

| 01            | 3                         | 100                     | 16                        | 1,600                              |

| 01            | 3                         | 101                     | 32                        | 800                                |

| 01            | 3                         | 110                     | 64                        | 400                                |

| 01            | 3                         | 111                     | 128                       | 200                                |

| 10            | 4                         | 000                     | 1                         | 19,200                             |

| 10            | 4                         | 001                     | 2                         | 9,600                              |

| 10            | 4                         | 010                     | 4                         | 4,800                              |

| 10            | 4                         | 011                     | 8                         | 2,400                              |

| 10            | 4                         | 100                     | 16                        | 1,200                              |

| 10            | 4                         | 101                     | 32                        | 600                                |

| 10            | 4                         | 110                     | 64                        | 300                                |

| 10            | 4                         | 111                     | 128                       | 150                                |

| 11            | 13                        | 000                     | 1                         | 5,908                              |

| 11            | 13                        | 001                     | 2                         | 2,954                              |

| 11            | 13                        | 010                     | 4                         | 1,477                              |

| 11            | 13                        | 011                     | 8                         | 739                                |

| 11            | 13                        | 100                     | 16                        | 369                                |

| 11            | 13                        | 101                     | 32                        | 185                                |

| 11            | 13                        | 110                     | 64                        | 92                                 |

| 11            | 13                        | 111                     | 128                       | 46                                 |

### Analog-to-Digital Converter (ADC)

# 10.5.2 **Stop Mode**

The ADC module is inactive after the execution of a STOP instruction. Any pending conversion is aborted. ADC conversions resume when the MCU exits stop mode. Allow one conversion cycle to stabilize the analog circuitry before attempting a new ADC conversion after exiting stop mode.

# 10.6 I/O Signals

The ADC module has 12 channels that are shared with I/O port B and port D, and one channel on ADC12/T2CLK pin.

# 10.6.1 ADC Voltage In (ADCVIN)

ADCVIN is the input voltage signal from one of the 13 ADC channels to the ADC module.

# 10.7 I/O Registers

These I/O registers control and monitor ADC operation:

- ADC status and control register (ADSCR)

- ADC data register (ADR)

- ADC clock register (ADICLK)

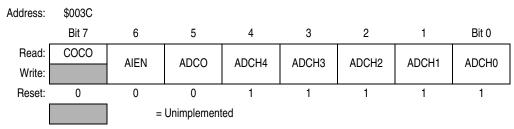

# 10.7.1 ADC Status and Control Register

The following paragraphs describe the function of the ADC status and control register.

Figure 10-3. ADC Status and Control Register (ADSCR)

## **COCO** — Conversions Complete Bit

When the AIEN bit is a logic 0, the COCO is a read-only bit which is set each time a conversion is completed. This bit is cleared whenever the ADC status and control register is written or whenever the ADC data register is read. Reset clears this bit.

- 1 = Conversion completed (AIEN = 0)

- 0 = Conversion not completed (AIEN = 0)

When the AIEN bit is a logic 1 (CPU interrupt enabled), the COCO is a read-only bit, and will always be logic 0 when read.

## AIEN — ADC Interrupt Enable Bit

When this bit is set, an interrupt is generated at the end of an ADC conversion. The interrupt signal is cleared when the data register is read or the status/control register is written. Reset clears the AIEN bit.

- 1 = ADC interrupt enabled

- 0 = ADC interrupt disabled

MC68HC908JL8/JK8 • MC68HC08JL8/JK8 • MC68HC908KL8 Data Sheet, Rev. 3.1

# Chapter 11 Input/Output (I/O) Ports

# 11.1 Introduction

Twenty six (26) bidirectional input-output (I/O) pins form four parallel ports. All I/O pins are programmable as inputs or outputs.

## NOTE

Connect any unused I/O pins to an appropriate logic level, either  $V_{DD}$  or  $V_{SS}$ . Although the I/O ports do not require termination for proper operation, termination reduces excess current consumption and the possibility of electrostatic damage.

Figure 11-1. I/O Port Register Summary

# 13.6 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

## 13.6.1 Wait Mode

The keyboard modules remain active in wait mode. Clearing the IMASKK bit in the keyboard status and control register enables keyboard interrupt requests to bring the MCU out of wait mode.

# 13.6.2 **Stop Mode**

The keyboard module remains active in stop mode. Clearing the IMASKK bit in the keyboard status and control register enables keyboard interrupt requests to bring the MCU out of stop mode.

# 13.7 Keyboard Module During Break Interrupts

The system integration module (SIM) controls whether the keyboard interrupt latch can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear status bits during the break state.

To allow software to clear the keyboard interrupt latch during a break interrupt, write a logic 1 to the BCFE bit. If a latch is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect the latch during the break state, write a logic 0 to the BCFE bit. With BCFE at logic 0 (its default state), writing to the keyboard acknowledge bit (ACKK) in the keyboard status and control register during the break state has no effect.

# **Chapter 14 Computer Operating Properly (COP)**

# 14.1 Introduction

The computer operating properly (COP) module contains a free-running counter that generates a reset if allowed to overflow. The COP module helps software recover from runaway code. Prevent a COP reset by clearing the COP counter periodically. The COP module can be disabled through the COPD bit in the CONFIG1 register.

# 14.2 Functional Description

Figure 14-1 shows the structure of the COP module.

NOTE: See SIM section for more details.

Figure 14-1. COP Block Diagram

#### **Electrical Specifications**

# Table 17-7. DC Electrical Characteristics (3V)

| Characteristic <sup>(1)</sup>                                            | Symbol                               | Min                 | Typ <sup>(2)</sup> | Max       | Unit     |

|--------------------------------------------------------------------------|--------------------------------------|---------------------|--------------------|-----------|----------|

| Capacitance Ports (as input or output)                                   | C <sub>OUT</sub><br>C <sub>IN</sub>  |                     | _                  | 12<br>8   | pF       |

| POR rearm voltage <sup>(6)</sup>                                         | V <sub>POR</sub>                     | 0                   | _                  | 100       | mV       |

| POR rise time ramp rate <sup>(7)</sup>                                   | R <sub>POR</sub>                     | 0.035               | _                  | _         | V/ms     |

| Monitor mode entry voltage                                               | V <sub>TST</sub>                     | $1.5 \times V_{DD}$ | _                  | 8.5       | V        |

| Pullup resistors <sup>(8)</sup> PTD6, PTD7 RST, IRQ, PTA0-PTA7           | R <sub>PU1</sub><br>R <sub>PU2</sub> | 1.8<br>16           | 3.3<br>26          | 4.8<br>36 | kΩ<br>kΩ |

| Low-voltage inhibit, trip voltage (No hysteresis implemented for 3V LVI) | V <sub>LVI3</sub>                    | 2.18                | 2.49               | 2.68      | V        |

- 1.  $V_{DD}$  = 2.7 to 3.3 Vdc,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ , unless otherwise noted.

- 2. Typical values reflect average measurements at midpoint of voltage range, 25 °C only.

- 3. Run (operating)  $I_{DD}$  measured using external square wave clock source ( $f_{OP} = 4$ MHz). All inputs 0.2V from rail. No dc loads. Less than 100 pF on all outputs.  $C_L = 20$  pF on OSC2. All ports configured as inputs. OSC2 capacitance linearly affects run  $I_{DD}$ . Measured with all modules enabled.

- 4. Wait  $I_{DD}$  measured using external square wave clock source ( $f_{OP} = 4$ MHz). All inputs 0.2V from rail. No dc loads. Less than 100 pF on all outputs.  $C_1 = 20$  pF on OSC2. All ports configured as inputs. OSC2 capacitance linearly affects wait  $I_{DD}$ .

- 5. Stop I<sub>DD</sub> measured with OSC1 grounded; no port pins sourcing current. LVI is disabled.

- 6. Maximum is highest voltage that POR is guaranteed.

- 7. If minimum  $V_{DD}$  is not reached before the internal POR reset is released,  $\overline{RST}$  must be driven low externally until minimum  $V_{DD}$  is reached.

- 8.  $R_{PU1}$  and  $R_{PU2}$  are measured at  $V_{DD} = 5.0 \text{ V}$ .

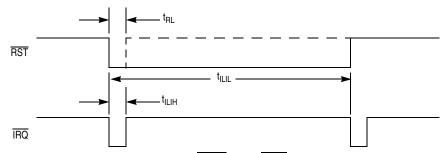

# 17.9 3V Control Timing

Table 17-8. Control Timing (3V)

| Characteristic <sup>(1)</sup>                                 | Symbol             | Min                 | Max | Unit             |

|---------------------------------------------------------------|--------------------|---------------------|-----|------------------|

| Internal operating frequency                                  | f <sub>OP</sub>    | _                   | 4   | MHz              |

| RST input pulse width low <sup>(2)</sup>                      | t <sub>RL</sub>    | 1.5                 | _   | μS               |

| TIM2 external clock input                                     | f <sub>T2CLK</sub> | _                   | 2   | MHz              |

| IRQ interrupt pulse width low (edge-triggered) <sup>(3)</sup> | t <sub>ILIH</sub>  | 200                 | _   | ns               |

| IRQ interrupt pulse period <sup>(3)</sup>                     | t <sub>ILIL</sub>  | Note <sup>(4)</sup> | _   | t <sub>CYC</sub> |

- 1. V<sub>DD</sub> = 2.7 to 3.3 Vdc, V<sub>SS</sub> = 0 Vdc, T<sub>A</sub> = T<sub>L</sub> to T<sub>H</sub>; timing shown with respect to 20% V<sub>DD</sub> and 70% V<sub>DD</sub>, unless otherwise noted.

- 2. Minimum pulse width reset is guaranteed to be recognized. It is possible for a smaller pulse width to cause a reset.

- 3. Values are based on characterization results, not tested in production.

- 4. The minimum period is the number of cycles it takes to execute the interrupt service routine plus 1 t<sub>CYC</sub>.

Figure 17-3. RST and IRQ Timing

MC68HC908JL8/JK8 • MC68HC08JL8/JK8 • MC68HC908KL8 Data Sheet, Rev. 3.1

# 17.12 Timer Interface Module Characteristics

Table 17-10. Timer Interface Module Characteristics (5V and 3V)

| Characteristic                              | Symbol                                | Min                        | Max | Unit |

|---------------------------------------------|---------------------------------------|----------------------------|-----|------|

| Input capture pulse width                   | t <sub>TIH,</sub> t <sub>TIL</sub>    | 1/f <sub>OP</sub>          | _   |      |

| Input clock pulse width (T2CLK pulse width) | t <sub>LMIN</sub> , t <sub>HMIN</sub> | (1/f <sub>OP</sub> ) + 5ns | _   |      |

# 17.13 ADC Characteristics

Table 17-11. ADC Characteristics (5V and 3V)

| Characteristic                             | Symbol            | Min                          | Max                          | Unit                    | Comments                                                         |

|--------------------------------------------|-------------------|------------------------------|------------------------------|-------------------------|------------------------------------------------------------------|

| Supply voltage                             | $V_{DDAD}$        | 2.7<br>(V <sub>DD</sub> min) | 5.5<br>(V <sub>DD</sub> max) | V                       |                                                                  |

| Input voltages                             | V <sub>ADIN</sub> | $V_{SS}$                     | $V_{DD}$                     | V                       |                                                                  |

| Resolution                                 | B <sub>AD</sub>   | 8                            | 8                            | Bits                    |                                                                  |

| Absolute accuracy                          | A <sub>AD</sub>   | ± 0.5                        | ± 1.5                        | LSB                     | Includes quantization                                            |

| ADC internal clock                         | f <sub>ADIC</sub> | 0.5                          | 1.048                        | MHz                     | t <sub>AIC</sub> = 1/f <sub>ADIC</sub> , tested only<br>at 1 MHz |

| Conversion range                           | R <sub>AD</sub>   | V <sub>SS</sub>              | $V_{DD}$                     | V                       |                                                                  |

| Power-up time                              | t <sub>ADPU</sub> | 16                           |                              | t <sub>AIC</sub> cycles |                                                                  |

| Conversion time                            | t <sub>ADC</sub>  | 14                           | 15                           | t <sub>AIC</sub> cycles |                                                                  |

| Sample time <sup>(1)</sup>                 | t <sub>ADS</sub>  | 5                            | _                            | t <sub>AIC</sub> cycles |                                                                  |

| Zero input reading <sup>(2)</sup>          | Z <sub>ADI</sub>  | 00                           | 01                           | Hex                     | $V_{IN} = V_{SS}$                                                |

| Full-scale reading <sup>(3)</sup>          | F <sub>ADI</sub>  | FE                           | FF                           | Hex                     | $V_{IN} = V_{DD}$                                                |

| Input capacitance                          | C <sub>ADI</sub>  | _                            | (20) 8                       | pF                      | Not tested                                                       |

| Input leakage <sup>(3)</sup> Port B/port D | _                 | _                            | ± 1                          | μА                      |                                                                  |

<sup>1.</sup> Source impedances greater than 10  $k\Omega$  adversely affect internal RC charging time during input sampling.

<sup>2.</sup> Zero-input/full-scale reading requires sufficient decoupling measures for accurate conversions.

<sup>3.</sup> The external system error caused by input leakage current is approximately equal to the product of R source and input current.

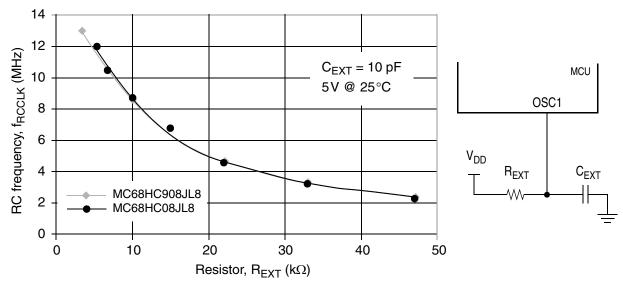

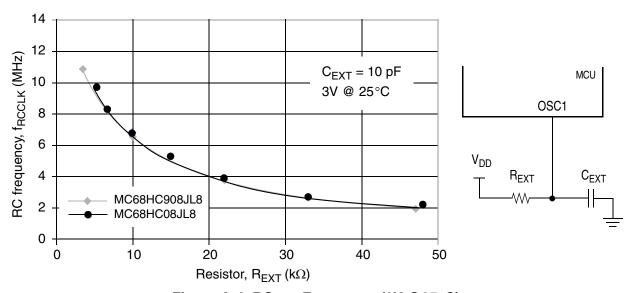

Figure A-3. RC vs. Frequency (5V @25°C)

Figure A-4. RC vs. Frequency (3V @25°C)

# **A.8 Memory Characteristics**

**Table A-4. Memory Characteristics**

| Characteristic             | Symbol    | Min | Max | Unit |

|----------------------------|-----------|-----|-----|------|

| RAM data retention voltage | $V_{RDR}$ | 1.3 | _   | V    |

Notes:

Since MC68HC08JL8 is a ROM device, FLASH memory electrical characteristics do not apply.