Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 72MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                    |

| Number of I/O              | 19                                                                      |

| Program Memory Size        | 64KB (64K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 16K × 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                            |

| Data Converters            | A/D 11x12b; D/A 1x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 49-UFBGA, WLCSP                                                         |

| Supplier Device Package    | 49-WLCSP                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f318c8y6tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **3** Functional overview

# 3.1 ARM<sup>®</sup> Cortex<sup>®</sup>-M4 core with FPU, embedded Flash and SRAM

The ARM<sup>®</sup> Cortex<sup>®</sup>-M4 processor with FPU is the latest generation of ARM processors for embedded systems. It was developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced response to interrupts.

The ARM<sup>®</sup> Cortex<sup>®</sup>-M4 32-bit RISC processor with FPU features exceptional codeefficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

The processor supports a set of DSP instructions which allow efficient signal processing and complex algorithm execution. Its single-precision FPU speeds up software development by using metalanguage development tools while avoiding saturation.

With its embedded ARM core, the STM32F318x8 family is compatible with all ARM tools and software.

*Figure 1* shows the general block diagram of the STM32F318x8 family devices.

#### 3.2 Memories

#### 3.2.1 Embedded Flash memory

All STM32F318x8 devices feature 64 Kbyte of embedded Flash memory available for storing programs and data. The Flash memory access time is adjusted to the CPU clock frequency (0 wait state from 0 to 24 MHz, 1 wait state from 24 to 48 MHz and 2 wait states above).

#### 3.2.2 Embedded SRAM

STM32F318x8 devices feature 16 Kbyte of embedded SRAM.

#### 3.3 Boot modes

At startup, BOOT0 pin and BOOT1 option bit are used to select one of three boot options:

- Boot from user Flash

- Boot from system memory

- Boot from embedded SRAM

The boot loader is located in system memory. It is used to reprogram the Flash memory by using USART1 (PA9/PA10) or USART2 (PA2/Pa3) or I2C1 (PB6/PB7) or I2C3 (PA8, PB5).

## 3.17 Inter-integrated circuit interfaces (I<sup>2</sup>C)

The devices feature three  $I^2C$  bus interfaces which can operate in multimaster and slave mode. Each I2C interface can support standard (up to 100 kHz), fast (up to 400 kHz) and fast mode + (up to 1 MHz) modes.

All I<sup>2</sup>C interfaces support 7-bit and 10-bit addressing modes, multiple 7-bit slave addresses (2 addresses, 1 with configurable mask). They also include programmable analog and digital noise filters.

|                                     | Analog filter                                         | Digital filter                                                                                       |

|-------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Pulse width of<br>suppressed spikes | ≥ 50 ns                                               | Programmable length from 1 to 15<br>I2C peripheral clocks                                            |

| Benefits                            | Available in Stop mode                                | <ol> <li>Extra filtering capability vs.<br/>standard requirements.</li> <li>Stable length</li> </ol> |

| Drawbacks                           | Variations depending on temperature, voltage, process | Wakeup from Stop on address<br>match is not available when digital<br>filter is enabled.             |

#### Table 5. Comparison of I2C analog and digital filters

In addition, it provides hardware support for SMBUS 2.0 and PMBUS 1.1: ARP capability, Host notify protocol, hardware CRC (PEC) generation/verification, timeouts verifications and ALERT protocol management. It also has a clock domain independent from the CPU clock, allowing the I2Cx (x=1,3) to wake up the MCU from Stop mode on address match.

The I2C interfaces can be served by the DMA controller.

Refer to Table 6 for the features available in I2C1, I2C2 and I2C3.

#### Table 6. STM32F318x8 I<sup>2</sup>C implementation

| I2C features <sup>(1)</sup>                                 | I2C1 | I2C2 | I2C3 |

|-------------------------------------------------------------|------|------|------|

| 7-bit addressing mode                                       | Х    | Х    | Х    |

| 10-bit addressing mode                                      | Х    | Х    | Х    |

| Standard mode (up to 100 kbit/s)                            | Х    | Х    | Х    |

| Fast mode (up to 400 kbit/s)                                | Х    | Х    | Х    |

| Fast Mode Plus with 20mA output drive I/Os (up to 1 Mbit/s) | Х    | Х    | Х    |

| Independent clock                                           | Х    | Х    | Х    |

| SMBus                                                       | Х    | Х    | Х    |

| Wakeup from STOP                                            | Х    | Х    | Х    |

1. X = supported.

# 3.18 Universal synchronous/asynchronous receiver transmitter (USART)

The STM32F318x8 devices have three embedded universal synchronous receiver transmitters (USART1, USART2 and USART3).

The USART interfaces are able to communicate at speeds of up to 9 Mbit/s.

All USARTs support hardware management of the CTS and RTS signals, multiprocessor communication mode, single-wire half-duplex communication mode and synchronous mode.

USART1 supports SmartCard mode, IrDA SIR ENDEC, LIN Master capability and autobaudrate detection.

All USART interfaces can be served by the DMA controller.

Refer to *Table 7* for the features available in all USARTs interfaces.

| USART modes/features <sup>(1)</sup>         | USART1 | USART2 | USART3 |

|---------------------------------------------|--------|--------|--------|

| Hardware flow control for modem             | Х      | Х      | Х      |

| Continuous communication using DMA          | Х      | Х      | Х      |

| Multiprocessor communication                | Х      | Х      | Х      |

| Synchronous mode                            | Х      | Х      | Х      |

| SmartCard mode                              | Х      | -      | -      |

| Single-wire half-duplex communication       | Х      | Х      | Х      |

| IrDA SIR ENDEC block                        | Х      | -      | -      |

| LIN mode                                    | Х      | -      | -      |

| Dual clock domain and wakeup from Stop mode | Х      | -      | -      |

| Receiver timeout interrupt                  | Х      | -      | -      |

| Modbus communication                        | Х      | -      | -      |

| Auto baud rate detection                    | Х      | -      | -      |

| Driver Enable                               | Х      | Х      | Х      |

#### Table 7. USART features

1. X = supported.

# 3.19 Serial peripheral interfaces (SPI)/Inter-integrated sound interfaces (I2S)

Two SPI interfaces (SPI2 and SPI3) allow communication up to 18 Mbit/s in slave and master modes in full-duplex and simplex modes. The 3-bit prescaler gives 8 master mode frequencies and the frame size is configurable from 4 bits to 16 bits.

Two standard I2S interfaces (multiplexed with SPI2 and SPI3) are available, that can be operated in master or slave mode. These interfaces can be configured to operate with 16/32 bit resolution, as input or output channels. Audio sampling frequencies from 8 kHz up to 192 kHz are supported. When either or both of the I2S interfaces is/are configured in master

#### 3.21 Infrared transmitter

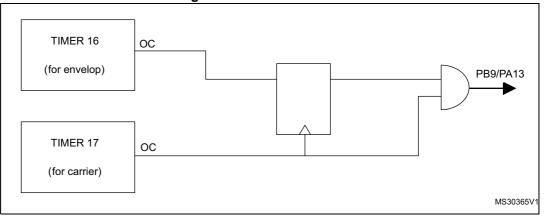

The STM32F318x8 devices provide an infrared transmitter solution. The solution is based on internal connections between TIM16 and TIM17 as shown in the figure below.

TIM17 is used to provide the carrier frequency and TIM16 provides the main signal to be sent. The infrared output signal is available on PB9 or PA13.

To generate the infrared remote control signals, TIM16 channel 1 and TIM17 channel 1 must be properly configured to generate correct waveforms. All standard IR pulse modulation modes can be obtained by programming the two timers output compare channels.

Figure 3. Infrared transmitter

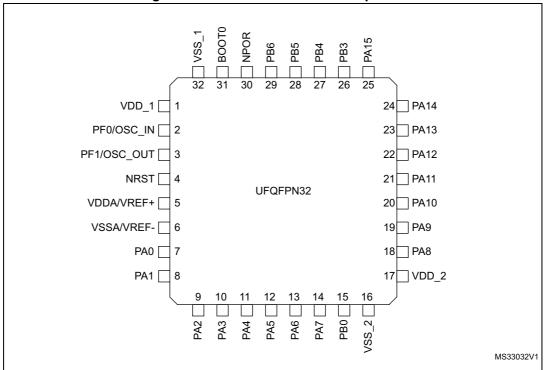

## 4 Pinouts and pin description

| ω        |

|----------|

| 8        |

| 1        |

| <u>N</u> |

| ΰĭ       |

|          |

DocID026294 Rev 5

| 2 |  |

|---|--|

|   |  |

|        | Table 12. STM32F318x8 pin definitions (continued) |         |                                    |          |               |       |                                                                                                        |                         |

|--------|---------------------------------------------------|---------|------------------------------------|----------|---------------|-------|--------------------------------------------------------------------------------------------------------|-------------------------|

| ngFN32 | n Num<br>Muu n<br>Muu n                           | WLCSP49 | Pin name<br>(function after reset) | Pin type | I/O structure | Notes | Alternate<br>functions                                                                                 | Additional<br>functions |

| 23     | 34                                                | B3      | PA13                               | I/O      | FT            | -     | SWDIO, TIM16_CH1N, TSC_G4_IO3,<br>IR-OUT, USART3_CTS, EVENTOUT                                         | -                       |

| -      | 35                                                | B1      | VSS_3                              | S        | -             | -     | Digital gro                                                                                            | bund                    |

| -      | 36                                                | B2      | VDD_3                              | S        | -             | -     | Digital powe                                                                                           | r supply                |

| 24     | 37                                                | A1      | PA14                               | I/O      | FTf           | -     | SWCLK-JTCK, TSC_G4_IO4,<br>I2C1_SDA, TIM1_BKIN, USART2_TX,<br>EVENTOUT                                 | -                       |

| 25     | 38                                                | A2      | PA15                               | I/O      | FTf           | -     | JTDI, TIM2_CH1/TIM2_ETR,<br>TSC_SYNC, I2C1_SCL,<br>SPI3_NSS/I2S3_WS, USART2_RX,<br>TIM1_BKIN, EVENTOUT | -                       |

| 26     | 39                                                | A3      | PB3                                | I/O      | FT            | -     | JTDO-TRACESWO, TIM2_CH2,<br>TSC_G5_IO1, SPI3_SCK/I2S3_CK,<br>USART2_TX, EVENTOUT                       | -                       |

| 27     | 40                                                | A4      | PB4                                | I/O      | FT            | -     | JTRST, TIM16_CH1, TSC_G5_IO2,<br>SPI3_MISO/I2S3ext_SD, USART2_RX,<br>TIM17_BKIN, EVENTOUT              | -                       |

| 28     | 41                                                | B4      | PB5                                | I/O      | FT            | -     | TIM16_BKIN, I2C1_SMBAI,<br>SPI3_MOSI/I2S3_SD, USART2_CK,<br>I2C3_SDA, TIM17_CH1, EVENTOUT              | -                       |

| 29     | 42                                                | C4      | PB6                                | I/O      | FTf           | -     | TIM16_CH1N, TSC_G5_IO3, I2C1_SCL,<br>USART1_TX, EVENTOUT                                               | -                       |

| -      | 43                                                | D4      | PB7                                | I/O      | FTf           | -     | TIM17_CH1N, TSC_G5_IO4, I2C1_SDA, USART1_RX, EVENTOUT                                                  | -                       |

| 30     | 20                                                | G3      | NPOR                               | I        | POR           | -     | Device power-or                                                                                        | reset input             |

| 4/12 |  |

|------|--|

| 25   |  |

|                       |        |                                      | Table 1                  | 5. Alternate func | tions for Port F               |                                      |                                           |                                      |

|-----------------------|--------|--------------------------------------|--------------------------|-------------------|--------------------------------|--------------------------------------|-------------------------------------------|--------------------------------------|

| Dout 9                | AF0    | AF1                                  | AF2                      | AF3               | AF4                            | AF5                                  | AF6                                       | AF7                                  |

| Port &<br>pin<br>name | SYS_AF | TIM2/TIM15/<br>TIM16/TIM17/<br>EVENT | I2C3/TIM1/TIM2/<br>TIM15 | I2C3/TIM15/TSC    | I2C1/I2C2/TIM1/<br>TIM16/TIM17 | SPI2/I2S2/<br>SPI3/I2S3/<br>Infrared | SPI2/I2S2/SPI3/<br>I2S3/TIM1/<br>Infrared | USART1/USAR<br>T2/USART3/<br>GPCOMP6 |

| PF0                   | -      | -                                    | -                        | -                 | I2C2_SDA                       | SPI2_NSS/<br>I2S2_WS                 | TIM1_CH3N                                 | -                                    |

| PF1                   | -      | -                                    | -                        | -                 | I2C2_SCL                       | SPI2_SCK/<br>I2S2_CK                 | -                                         | -                                    |

### 6 Electrical characteristics

#### 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

#### 6.1.1 Minimum and maximum values

Unless otherwise specified, the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\sigma$ ).

#### 6.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = 1.8$  V, $V_{DDA} = 3.3$  V. They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\sigma$ ).

#### 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

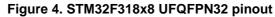

#### 6.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in *Figure 8*.

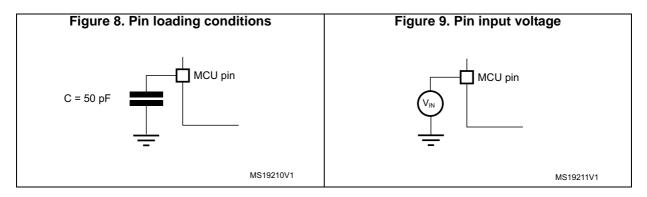

#### 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in Figure 9.

DocID026294 Rev 5

### 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 17: Voltage characteristics*, *Table 18: Current characteristics*, and *Table 19: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                             | Ratings                                                                       | Min                                   | Max                    | Unit |

|------------------------------------|-------------------------------------------------------------------------------|---------------------------------------|------------------------|------|

| V <sub>DD</sub> –V <sub>SS</sub>   | External main supply voltage (including $V_{\text{DD}}$ and $V_{\text{BAT}})$ | -0.3                                  | 1.95                   | V    |

| V <sub>DDA</sub> -V <sub>SS</sub>  | External main supply voltage                                                  | -0.3                                  | 4.0                    | V    |

| V <sub>DD</sub> –V <sub>DDA</sub>  | Allowed voltage difference for $V_{DD} > V_{DDA}$                             | -                                     | 0.4                    | V    |

|                                    | Input voltage on FT and FTf pins                                              | V <sub>SS</sub> - 0.3                 | V <sub>DD</sub> + 4.0  |      |

|                                    | Input voltage on TTa and TT pins                                              | V <sub>SS</sub> - 0.3                 | 4.0                    | v    |

| V <sub>IN</sub> <sup>(2)</sup>     | Input voltage on POR pin                                                      | V <sub>SS</sub> - 0.3                 | V <sub>DDA</sub> + 4.0 |      |

|                                    | Input voltage on any other pin                                                | $V_{SS}-0.3$                          | 4.0                    |      |

|                                    | Input voltage on Boot0 pin                                                    | 0                                     | 9                      |      |

| ΔV <sub>DDx</sub>                  | Variations between different V <sub>DD</sub> power pins                       | -                                     | 50                     | m\/  |

| V <sub>SSX</sub> – V <sub>SS</sub> | Variations between all the different ground pins                              | -                                     | 50                     | - mV |

| V <sub>ESD(HBM)</sub>              | Electrostatic discharge voltage (human body model)                            | see Section 6.3.<br>sensitivity chara |                        | V    |

All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range. The following relationship must be respected between V<sub>DDA</sub> and V<sub>DD</sub>: V<sub>DDA</sub> must power on before or at the same time as V<sub>DD</sub> in the power up sequence. V<sub>DDA</sub> must be greater than or equal to V<sub>DD</sub>.

2. V<sub>IN</sub> maximum must always be respected. Refer to *Table 18: Current characteristics* for the maximum allowed injected current values.

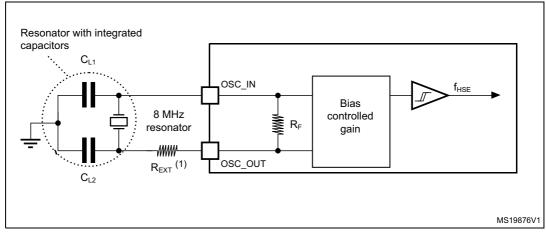

For C<sub>L1</sub> and C<sub>L2</sub>, it is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (Typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 15*). C<sub>L1</sub> and C<sub>L2</sub> are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of C<sub>L1</sub> and C<sub>L2</sub>. PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing C<sub>L1</sub> and C<sub>L2</sub>.

Note: For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

1. R<sub>EXT</sub> value depends on the crystal characteristics.

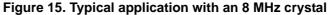

Figure 16. Typical application with a 32.768 kHz crystal

Note: An external resistor is not required between OSC32\_IN and OSC32\_OUT and it is forbidden to add one.

#### Low-speed internal (LSI) RC oscillator

| Table 39. LS | loscillator | characteristics <sup>(1)</sup> |

|--------------|-------------|--------------------------------|

|--------------|-------------|--------------------------------|

| Symbol                              | Parameter                        | Min | Тур  | Max | Unit |

|-------------------------------------|----------------------------------|-----|------|-----|------|

| f <sub>LSI</sub>                    | Frequency                        | 30  | 40   | 50  | kHz  |

| t <sub>su(LSI)</sub> <sup>(2)</sup> | LSI oscillator startup time      | -   | -    | 85  | μs   |

| I <sub>DD(LSI)</sub> <sup>(2)</sup> | LSI oscillator power consumption | -   | 0.75 | 1.2 | μΑ   |

1. V<sub>DDA</sub> = 3.3 V, T<sub>A</sub> = –40 to 105 °C unless otherwise specified.

2. Guaranteed by design, not tested in production.

#### 6.3.8 PLL characteristics

The parameters given in *Table 40* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 20*.

|                      |                                | Value             |     |                    |      |

|----------------------|--------------------------------|-------------------|-----|--------------------|------|

| Symbol               | Parameter                      | Min               | Тур | Мах                | Unit |

| 4                    | PLL input clock <sup>(1)</sup> | 1 <sup>(2)</sup>  | -   | 24 <sup>(2)</sup>  | MHz  |

| f <sub>PLL_IN</sub>  | PLL input clock duty cycle     | 40 <sup>(2)</sup> | -   | 60 <sup>(2)</sup>  | %    |

| f <sub>PLL_OUT</sub> | PLL multiplier output clock    | 16 <sup>(2)</sup> | -   | 72                 | MHz  |

| t <sub>LOCK</sub>    | PLL lock time                  | -                 | -   | 200 <sup>(2)</sup> | μs   |

| Jitter               | Cycle-to-cycle jitter          | -                 | -   | 300 <sup>(2)</sup> | ps   |

#### Table 40. PLL characteristics

1. Take care of using the appropriate multiplier factors so as to have PLL input clock values compatible with the range defined by f\_PLL\_OUT.

2. Guaranteed by design, not tested in production.

#### SPI/I<sup>2</sup>S characteristics

Unless otherwise specified, the parameters given in *Table 57* for SPI or in *Table 58* for I<sup>2</sup>S are derived from tests performed under ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 20*.

Refer to Section 6.3.13: I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI and WS, CK, SD for I<sup>2</sup>S).

| Symbol                                       | Parameter                | Conditions                                            | Min         | Тур   | Max               | Unit |

|----------------------------------------------|--------------------------|-------------------------------------------------------|-------------|-------|-------------------|------|

|                                              |                          | Master mode                                           | -           | -     | 18                | MHz  |

| f <sub>scк</sub>                             | SPI clock frequency      | Slave mode                                            | -           | -     | 18                |      |

| 1/t <sub>c(SCK)</sub>                        |                          | Slave mode transmitter/full duplex                    | -           | -     | 13 <sup>(2)</sup> |      |

| t <sub>su(NSS)</sub>                         | NSS setup time           | Slave mode, SPI presc = 2                             | 4*Tpcl<br>k | -     | -                 |      |

| t <sub>h(NSS)</sub>                          | NSS hold time            | Slave mode, SPI presc = 2                             | 2*Tpcl<br>k | -     | -                 |      |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time    | Master mode, f <sub>PCLK</sub> = 36<br>MHz, presc = 4 | Tpclk-<br>2 | Tpclk | Tpclk+<br>2       |      |

| t <sub>su(MI)</sub>                          | Dete insut estus time    | Master mode                                           | 0           | -     | -                 |      |

| t <sub>su(SI)</sub>                          | Data input setup time    | Slave mode                                            | 1           | -     | -                 |      |

| t <sub>h(MI)</sub>                           | Data input hold time     | Master mode                                           | 6.5         | -     | -                 |      |

| t <sub>h(SI)</sub>                           |                          | Slave mode                                            | 2.5         | -     | -                 | ns   |

| t <sub>a(SO)</sub>                           | Data output access time  | Slave mode                                            | 8           | -     | 40                |      |

| t <sub>dis(SO)</sub>                         | Data output disable time | Slave mode                                            | 8           | -     | 14                |      |

| t <sub>v(SO)</sub>                           | Data output valid time   | Slave mode                                            | -           | 23    | 38                |      |

| t <sub>v(MO)</sub>                           |                          | Master mode                                           | -           | 1.5   | 4                 |      |

| t <sub>h(SO)</sub>                           | Data output hold time    | Slave mode                                            | 9.5         | -     | -                 |      |

| t <sub>h(MO)</sub>                           |                          | Master mode                                           | 0           | -     | -                 |      |

| Table 57. SPI characteristics <sup>(1)</sup> | ) |

|----------------------------------------------|---|

|----------------------------------------------|---|

1. Data based on characterization results, not tested in production.

2. Maximum frequency in Slave transmitter mode is determined by the sum of tv(SO) and tsu(MI) which has to fit into SCK low or high phase preceding the SCK sampling edge. This value can be achieved when the SPI communicates with a master having tsu(MI) = 0 while Duty(SCK) = 50%.

#### STM32F318C8 STM32F318K8

|            | Sampling          | Sampling              | R <sub>AIN</sub> max (kΩ)       |                  |                                  |  |

|------------|-------------------|-----------------------|---------------------------------|------------------|----------------------------------|--|

| Resolution | cycle @<br>72 MHz | time [ns] @<br>72 MHz | Fast<br>channels <sup>(2)</sup> | Slow<br>channels | Other<br>channels <sup>(3)</sup> |  |

|            | 1.5               | 20.83                 | 0.018                           | NA               | NA                               |  |

|            | 2.5               | 34.72                 | 0.150                           | NA               | 0.022                            |  |

|            | 4.5               | 62.50                 | 0.470                           | 0.220            | 0.180                            |  |

| 10.1.1.    | 7.5               | 104.17                | 0.820                           | 0.560            | 0.470                            |  |

| 12 bits    | 19.5              | 270.83                | 2.70                            | 1.80             | 1.50                             |  |

|            | 61.5              | 854.17                | 8.20                            | 6.80             | 4.70                             |  |

|            | 181.5             | 2520.83               | 22.0                            | 18.0             | 15.0                             |  |

|            | 601.5             | 8354.17               | 82.0                            | 68.0             | 47.0                             |  |

|            | 1.5               | 20.83                 | 0.082                           | NA               | NA                               |  |

|            | 2.5               | 34.72                 | 0.270                           | 0.082            | 0.100                            |  |

|            | 4.5               | 62.50                 | 0.560                           | 0.390            | 0.330                            |  |

|            | 7.5               | 104.17                | 1.20                            | 0.82             | 0.68                             |  |

| 10 bits    | 19.5              | 270.83                | 3.30                            | 2.70             | 2.20                             |  |

|            | 61.5              | 854.17                | 10.0                            | 8.2              | 6.8                              |  |

|            | 181.5             | 2520.83               | 33.0                            | 27.0             | 22.0                             |  |

|            | 601.5             | 8354.17               | 100.0                           | 82.0             | 68.0                             |  |

|            | 1.5               | 20.83                 | 0.150                           | NA               | 0.039                            |  |

|            | 2.5               | 34.72                 | 0.390                           | 0.180            | 0.180                            |  |

|            | 4.5               | 62.50                 | 0.820                           | 0.560            | 0.470                            |  |

|            | 7.5               | 104.17                | 1.50                            | 1.20             | 1.00                             |  |

| 8 bits     | 19.5              | 270.83                | 3.90                            | 3.30             | 2.70                             |  |

|            | 61.5              | 854.17                | 12.00                           | 12.00            | 8.20                             |  |

|            | 181.5             | 2520.83               | 39.00                           | 33.00            | 27.00                            |  |

|            | 601.5             | 8354.17               | 100.00                          | 100.00           | 82.00                            |  |

|            | 1.5               | 20.83                 | 0.270                           | 0.100            | 0.150                            |  |

|            | 2.5               | 34.72                 | 0.560                           | 0.390            | 0.330                            |  |

|            | 4.5               | 62.50                 | 1.200                           | 0.820            | 0.820                            |  |

|            | 7.5               | 104.17                | 2.20                            | 1.80             | 1.50                             |  |

| 6 bits     | 19.5              | 270.83                | 5.60                            | 4.70             | 3.90                             |  |

|            | 61.5              | 854.17                | 18.0                            | 15.0             | 12.0                             |  |

|            | 181.5             | 2520.83               | 56.0                            | 47.0             | 39.0                             |  |

|            | 601.5             | 8354.17               | 100.00                          | 100.0            | 100.0                            |  |

Table 60. Maximum ADC  $R_{AIN}$  <sup>(1)</sup>

1. Data based on characterization results, not tested in production.

2. All fast channels, expect channel on PA6.

#### 3. Channel available on PA6.

| Symbol                | Parameter              | Conditions               |                                                      |                     | Min<br>(3) | Тур  | Max<br>(3) | Unit  |

|-----------------------|------------------------|--------------------------|------------------------------------------------------|---------------------|------------|------|------------|-------|

|                       |                        |                          |                                                      | Fast channel 5.1 Ms | -          | ±4   | ±4.5       |       |

| ET                    | Total<br>unadjusted    |                          | Single ended                                         | Slow channel 4.8 Ms | -          | ±5.5 | ±6         |       |

|                       | error                  |                          | Differential                                         | Fast channel 5.1 Ms | -          | ±3.5 | ±4         |       |

|                       |                        |                          | Dillerential                                         | Slow channel 4.8 Ms | -          | ±3.5 | ±4         |       |

|                       |                        |                          | Single ended                                         | Fast channel 5.1 Ms | -          | ±2   | ±2         |       |

| EO                    | Offset error           |                          |                                                      | Slow channel 4.8 Ms | -          | ±1.5 | ±2         |       |

| LO                    | Olisetenoi             |                          | Differential                                         | Fast channel 5.1 Ms | -          | ±1.5 | ±2         |       |

|                       |                        |                          | Dillerential                                         | Slow channel 4.8 Ms | -          | ±1.5 | ±2         |       |

|                       |                        |                          | Single ended                                         | Fast channel 5.1 Ms | -          | ±3   | ±4         |       |

| EG                    | Gain error             |                          |                                                      | Slow channel 4.8 Ms | -          | ±5   | ±5.5       | LSB   |

| EG                    | Gainentoi              |                          | Differential                                         | Fast channel 5.1 Ms | -          | ±3   | ±3         |       |

|                       |                        |                          |                                                      | Slow channel 4.8 Ms | -          | ±3   | ±3.5       |       |

|                       |                        | ADC clock freg. < 72 MHz | ADC clock freq. $\leq 72 \text{ MHz}$   Single ended | Fast channel 5.1 Ms | -          | ±1   | ±1         |       |

| ED                    | Differential linearity |                          |                                                      | Slow channel 4.8 Ms | -          | ±1   | ±1         |       |

| LD                    | error                  |                          | Differential                                         | Fast channel 5.1 Ms | -          | ±1   | ±1         |       |

|                       |                        |                          |                                                      | Slow channel 4.8 Ms | -          | ±1   | ±1         |       |

|                       |                        |                          | Single ended                                         | Fast channel 5.1 Ms | -          | ±1.5 | ±2         |       |

| EL                    | Integral<br>linearity  |                          |                                                      | Slow channel 4.8 Ms | -          | ±2   | ±3         |       |

|                       | error                  |                          | Differential                                         | Fast channel 5.1 Ms | -          | ±1.5 | ±1.5       |       |

|                       |                        |                          |                                                      | Slow channel 4.8 Ms | -          | ±1.5 | ±2         |       |

|                       |                        |                          | Single ended                                         | Fast channel 5.1 Ms | 10.8       | 10.8 | -          | - bit |

| ENOB                  | Effective number of    |                          |                                                      | Slow channel 4.8 Ms | 10.8       | 10.8 | -          |       |

| (4) humber of<br>bits |                        |                          | Differential                                         | Fast channel 5.1 Ms | 11.2       | 11.3 | -          |       |

|                       |                        |                          | Differential                                         | Slow channel 4.8 Ms | 11.2       | 11.3 | -          |       |

| Cirpolto              | Signal-to-             |                          | Single ended                                         | Fast channel 5.1 Ms | 66         | 67   | -          | - dB  |

| SINAD                 | noise and              |                          | Single ended                                         | Slow channel 4.8 Ms | 66         | 67   | -          |       |

| (4)                   | distortion<br>ratio    |                          | Differential                                         | Fast channel 5.1 Ms | 69         | 70   | -          |       |

| L                     |                        |                          | Differnial                                           | Slow channel 4.8 Ms | 69         | 70   | -          |       |

| Table 61. ADC accuracy - | limited test conditions <sup>(1)(2)</sup> |

|--------------------------|-------------------------------------------|

|--------------------------|-------------------------------------------|

96/125

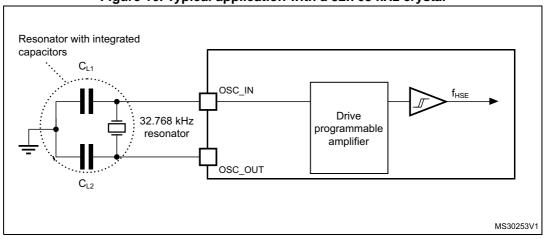

Figure 32. OPAMP Voltage Noise versus Frequency

| Symbol            |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|-------------------|-------|-------------|-------|--------|-----------------------|--------|

| Symbol            | Min   | Тур         | Max   | Min    | Тур                   | Max    |

| A                 | 0.525 | 0.555       | 0.585 | 0.0207 | 0.0219                | 0.0230 |

| A1                | -     | 0.175       | -     | -      | 0.0069                | -      |

| A2                | -     | 0.380       | -     | -      | 0.0150                | -      |

| A3 <sup>(2)</sup> | -     | 0.025       | -     | -      | 0.0010                | -      |

| b <sup>(3)</sup>  | 0.220 | 0.250       | 0.280 | 0.0087 | 0.0098                | 0.0110 |

| D                 | 3.382 | 3.417       | 3.452 | 0.1331 | 0.1345                | 0.1359 |

| E                 | 3.116 | 3.151       | 3.186 | 0.1227 | 0.1241                | 0.1254 |

| е                 | -     | 0.400       | -     | -      | 0.0157                | -      |

| e1                | -     | 2.400       | -     | -      | 0.0945                | -      |

| e2                | -     | 2.400       | -     | -      | 0.0945                | -      |

| F                 | -     | 0.5085      | -     | -      | 0.0200                | -      |

| G                 | -     | 0.3755      | -     | -      | 0.0148                | -      |

| aaa               | -     | -           | 0.100 | -      | -                     | 0.0039 |

| bbb               | -     | -           | 0.100 | -      | -                     | 0.0039 |

| CCC               | -     | -           | 0.100 | -      | -                     | 0.0039 |

| ddd               | -     | -           | 0.050 | -      | -                     | 0.0020 |

| eee               | -     | -           | 0.050 | -      | -                     | 0.0020 |

## Table 70. WLCSP49 - 49-pin, 3.417 x 3.151 mm, 0.4 mm pitch wafer level chip scalepackage mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Back side coating

3. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

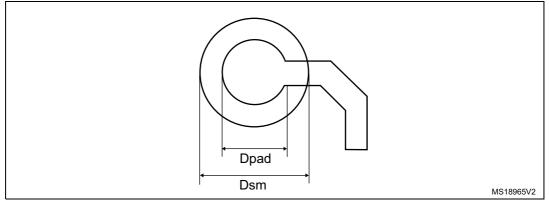

## Figure 34. WLCSP49 - 49-pin, 3.417 x 3.151 mm, 0.4 mm pitch wafer level chip scale package recommended footprint

| Dimension      | Recommended values                             |  |  |

|----------------|------------------------------------------------|--|--|

| Pitch          | 0.4                                            |  |  |

| Dpad           | 260 µm max. (circular)                         |  |  |

| Dpau           | 220 µm recommended                             |  |  |

| Dsm            | 300 µm min. (for 260 µm diameter pad)          |  |  |

| PCB pad design | Non-solder mask defined via underbump allowed. |  |  |

Table 71. WLCSP49 recommended PCB design rules (0.4 mm pitch)

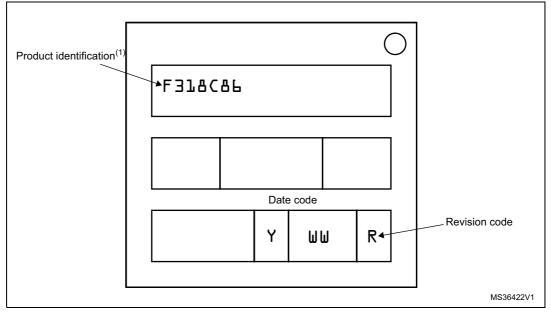

#### **Device marking**

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Figure 35. WLCSP49 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

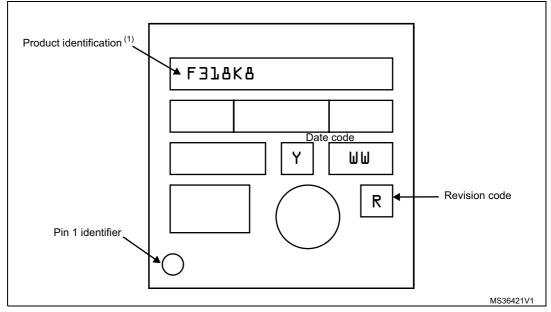

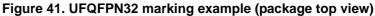

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2015 STMicroelectronics – All rights reserved

DocID026294 Rev 5