Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART, USB OTG            |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 51                                                                               |

| Program Memory Size        | 256KB (85.5K x 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 12K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 24x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-VQFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256mu806-e-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

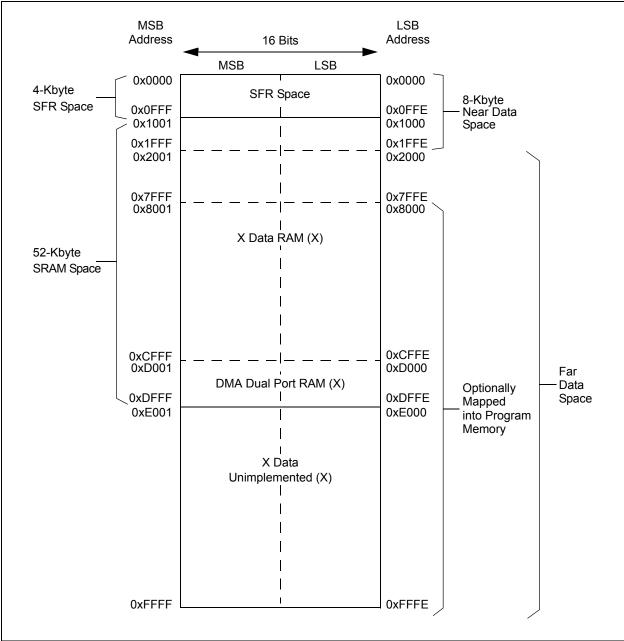

## FIGURE 4-5: DATA MEMORY MAP FOR dsPIC33EP256MU806/810/814 DEVICES WITH 28-KBYTE RAM

# TABLE 4-25: ADC1 and ADC2 REGISTER MAP (CONTINUED)

| File Name | Addr. | Bit 15 | Bit 14              | Bit 13 | Bit 12                          | Bit 11 | Bit 10   | Bit 9   | Bit 8       | Bit 7    | Bit 6     | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1    | Bit 0   | All<br>Resets |

|-----------|-------|--------|---------------------|--------|---------------------------------|--------|----------|---------|-------------|----------|-----------|-------|-------|--------|--------|----------|---------|---------------|

| ADC2BUF9  | 0352  |        |                     |        |                                 |        |          |         | ADCx Data E | Buffer 9 |           |       |       |        |        |          |         | XXXX          |

| ADC2BUFA  | 0354  |        |                     |        |                                 |        |          |         | ADCx Data B | uffer 10 |           |       |       |        |        |          |         | XXXX          |

| ADC2BUFB  | 0356  |        |                     |        |                                 |        |          |         | ADCx Data B | uffer 11 |           |       |       |        |        |          |         | XXXX          |

| ADC2BUFC  | 0358  |        | ADCx Data Buffer 12 |        |                                 |        |          |         |             |          |           | XXXX  |       |        |        |          |         |               |

| ADC2BUFD  | 035A  |        | ADCx Data Buffer 13 |        |                                 |        |          |         |             |          |           | XXXX  |       |        |        |          |         |               |

| ADC2BUFE  | 035C  |        | ADCx Data Buffer 14 |        |                                 |        |          |         |             |          | XXXX      |       |       |        |        |          |         |               |

| ADC2BUFF  | 035E  |        |                     |        |                                 |        |          |         | ADCx Data B | uffer 15 |           |       |       |        |        |          |         | XXXX          |

| AD2CON1   | 0360  | ADON   | _                   | ADSIDL | ADDMABM                         | —      |          | FOR     | M<1:0>      | 5        | SSRC<2:0> | •     | SSRCG | SIMSAM | ASAM   | SAMP     | DONE    | 0000          |

| AD2CON2   | 0362  | Ň      | VCFG<2:0            | >      | —                               | —      | CSCNA    | CHP     | S<1:0>      | BUFS     |           |       | SMP   | l<3:0> |        | BUFM     | ALTS    | 0000          |

| AD2CON3   | 0364  | ADRC   |                     |        |                                 |        | SAMC<4:0 | >       |             |          |           |       | ADCS  | S<7:0> |        |          |         | 0000          |

| AD2CHS123 | 0366  | —      |                     | _      | _                               | _      | CH123N   | NB<1:0> | CH123SB     |          | _         | _     | _     | _      | CH123N | IA<1:0>  | CH123SA | 0000          |

| AD2CHS0   | 0368  | CH0NB  |                     | _      | CH0SB<4:0> CH0NA — — CH0SA<4:0> |        |          |         |             |          | 0000      |       |       |        |        |          |         |               |

| AD2CSSL   | 0270  | CSS15  | CSS14               | CSS13  | CSS12                           | CSS11  | CSS10    | CSS9    | CSS8        | CSS7     | CSS6      | CSS5  | CSS4  | CSS3   | CSS2   | CSS1     | CSS0    | 0000          |

| AD2CON4   | 0272  | —      | _                   |        | _                               | —      |          | —       | ADDMAEN     | _        |           |       |       | —      | C      | MABL<2:0 | )>      | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These bits are not available on dsPIC33EP256MU806 devices.

| File<br>Name | Addr. | Bit 15 | Bit 14      | Bit 13      | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6      | Bit 5      | Bit 4     | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Rese<br>s |

|--------------|-------|--------|-------------|-------------|--------|------------|--------|-------|-------|-------|------------|------------|-----------|------------|-------|-------|-------|------------------|

| RPINR0       | 06A0  |        |             |             |        | INT1R<6:02 | >      | •     | •     | _     | _          | _          | _         | —          | _     | _     | _     | 0000             |

| RPINR1       | 06A2  | _      |             |             |        | INT3R<6:03 | >      |       |       | _     | INT2R<6:0> |            |           |            |       | 0000  |       |                  |

| RPINR2       | 06A4  | _      | _           | _           |        | _          | _      | —     | —     | _     |            |            |           | INT4R<6:0> | >     |       |       | 0000             |

| RPINR3       | 06A6  | _      |             |             |        | T3CKR<6:0  | >      |       |       | _     |            |            |           | T2CKR<6:0  | >     |       |       | 000              |

| RPINR4       | 06A8  | _      |             | T5CKR<6:0>  |        |            |        |       |       | _     |            |            |           | T4CKR<6:0  | >     |       |       | 0000             |

| RPINR5       | 06AA  | _      |             | T7CKR<6:0>  |        |            |        |       |       | _     |            |            |           | T6CKR<6:0  | >     |       |       | 0000             |

| RPINR6       | 06AC  | _      |             | T9CKR<6:0>  |        |            |        |       |       | _     |            |            |           | T8CKR<6:0  | >     |       |       | 0000             |

| RPINR7       | 06AE  | _      |             | IC2R<6:0>   |        |            |        |       |       | —     |            |            |           | IC1R<6:0>  |       |       |       | 0000             |

| RPINR8       | 06B0  | _      |             | IC4R<6:0>   |        |            |        |       |       | _     |            |            |           | IC3R<6:0>  |       |       |       | 0000             |

| RPINR9       | 06B2  | _      | IC6R<6:0>   |             |        |            |        |       | —     |       |            |            | IC5R<6:0> |            |       |       | 0000  |                  |

| RPINR10      | 06B4  | _      |             | IC8R<6:0>   |        |            |        |       |       | _     | IC7R<6:0>  |            |           |            |       | 0000  |       |                  |

| RPINR11      | 06B6  | _      |             | OCFBR<6:0>  |        |            |        |       |       | _     |            |            | (         | OCFAR<6:0  | >     |       |       | 0000             |

| RPINR18      | 06C4  | _      |             | U1CTSR<6:0> |        |            |        |       |       | _     |            |            | I         | J1RXR<6:0  | >     |       |       | 0000             |

| RPINR19      | 06C6  | _      | U2CTSR<6:0> |             |        |            |        | _     |       |       | I          | J2RXR<6:0  | >         |            |       | 0000  |       |                  |

| RPINR20      | 06C8  | _      | SCK1R<6:0>  |             |        |            |        | _     |       |       |            | SDI1R<6:0> | >         |            |       | 0000  |       |                  |

| RPINR21      | 06CA  | _      | _           | _           | _      | _          | _      | _     | _     | _     | SS1R<6:0>  |            |           |            |       | 0000  |       |                  |

| RPINR23      | 06CE  | —      | _           | _           |        | _          |        | —     | —     | —     |            |            |           | SS2R<6:0>  |       |       |       | 0000             |

| RPINR26      | 06D4  | —      |             |             |        | C2RXR<6:0  | >      |       |       | —     |            |            | (         | C1RXR<6:0  | >     |       |       | 0000             |

| RPINR27      | 06D6  | —      |             |             | I      | J3CTSR<6:( | )>     |       |       | —     | U3RXR<6:0> |            |           |            |       |       | 0000  |                  |

| RPINR28      | 06D8  | —      |             |             | I      | J4CTSR<6:( | )>     |       |       | —     | U4RXR<6:0> |            |           |            |       |       | 0000  |                  |

| RPINR29      | 06DA  | —      |             |             |        | SCK3R<6:0  | >      |       |       | —     |            |            |           | SDI3R<6:0> | >     |       |       | 0000             |

| RPINR30      | 06DC  | —      | _           | _           |        | _          |        | —     | —     | —     |            |            |           | SS3R<6:0>  |       |       |       | 0000             |

| RPINR31      | 06DE  | —      |             |             |        | SCK4R<6:0  | >      |       |       | _     |            |            |           | SDI4R<6:0> | >     |       |       | 0000             |

| RPINR32      | 06E0  | _      | —           | —           | —      | —          | —      | —     | —     | _     |            |            |           | SS4R<6:0>  |       |       |       | 0000             |

| RPINR33      | 06E2  | _      |             |             |        | IC10R<6:0> | >      |       |       | _     |            |            |           | IC9R<6:0>  |       |       |       | 0000             |

| RPINR34      | 06E4  | _      |             |             |        | IC12R<6:0> | >      |       |       | _     | IC11R<6:0> |            |           |            |       | 0000  |       |                  |

| RPINR35      | 06E6  | _      |             | IC14R<6:0>  |        |            |        |       |       | _     | IC13R<6:0> |            |           |            |       | 0000  |       |                  |

| RPINR36      | 06E8  | —      |             |             |        | IC16R<6:0> | >      |       |       | —     | IC15R<6:0> |            |           |            |       | 0000  |       |                  |

| RPINR37      | 06EA  | _      | _           | _           | _      | _          | _      | _     | _     | _     |            |            | (         | OCFCR<6:0  | >     |       |       | 0000             |

## TABLE 4-43: PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR PIC24EPXXXGU810/814 DEVICES ONLY

dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

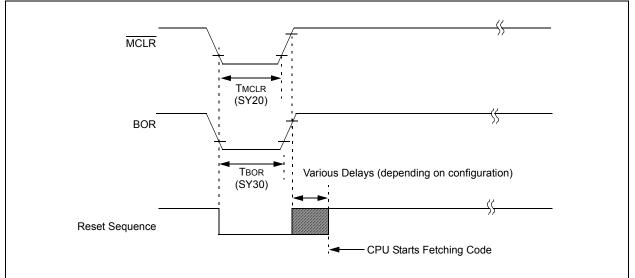

# 6.0 RESETS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXX(GP/MC/MU)806/ 810/814 and PIC24EPXXX(GP/GU)810/ 814 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Reset" (DS70602) of the *"dsPIC33E/PIC24E Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDTO: Watchdog Timer Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- · IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state and some are unaffected.

Note: Refer to the specific peripheral section or Section 4.0 "Memory Organization" of this manual for register Reset states.

# FIGURE 6-1: **RESET SYSTEM BLOCK DIAGRAM RESET** Instruction Glitch Filter WDT Module Sleep or Idle BOR Internal Regulator SYSRST POR VDD Rise Detect Trap Conflict Illegal Opcode Uninitialized W Register Security Reset Configuration Mismatch

#### © 2009-2012 Microchip Technology Inc.

# **REGISTER 9-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,3)</sup> (CONTINUED)

| bit 3 | <b>CF:</b> Clock Fail Detect bit (read/clear by application)<br>1 = FSCM has detected clock failure<br>0 = FSCM has not detected clock failure |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 2 | Unimplemented: Read as '0'                                                                                                                     |

| bit 1 | LPOSCEN: Secondary (LP) Oscillator Enable bit                                                                                                  |

|       | <ul><li>1 = Enables Secondary Oscillator</li><li>0 = Disables Secondary Oscillator</li></ul>                                                   |

- bit 0 OSWEN: Oscillator Switch Enable bit

- 1 = Requests oscillator switch to selection specified by NOSC<2:0> bits

- 0 = Oscillator switch is complete

- **Note 1:** Writes to this register require an unlock sequence. Refer to **Section 7. "Oscillator"** (DS70580) in the *"dsPIC33E/PIC24E Family Reference Manual"* (available from the Microchip web site) for details.

- 2: Direct clock switches between any Primary Oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

- **3:** This register resets only on a Power-on Reset (POR).

| U-0                                | U-0   | U-0   | U-0                                 | U-0                                | U-0   | U-0   | U-0   |  |

|------------------------------------|-------|-------|-------------------------------------|------------------------------------|-------|-------|-------|--|

| _                                  |       | —     |                                     | —                                  | _     | —     | —     |  |

| bit 15                             |       |       |                                     |                                    |       |       | bit 8 |  |

|                                    |       |       |                                     |                                    |       |       |       |  |

| U-0                                | R/W-0 | R/W-0 | R/W-0                               | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |

| —                                  |       |       |                                     | FLT7R<6:0>                         |       |       |       |  |

| bit 7                              |       |       |                                     |                                    |       |       | bit 0 |  |

|                                    |       |       |                                     |                                    |       |       |       |  |

| Legend:                            |       |       |                                     |                                    |       |       |       |  |

| R = Readable bit W = Writable bit  |       |       |                                     | U = Unimplemented bit, read as '0' |       |       |       |  |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cleared x = Bit is unk |                                    |       | nown  |       |  |

| •                                  |       |       |                                     |                                    |       |       |       |  |

bit 15-7Unimplemented: Read as '0'bit 6-0FLT7R<6:0>: Assign PWM Fault 7 to 1

bit 6-0

FLT7R<6:0>: Assign PWM Fault 7 to the Corresponding RPn/RPIn Pin bits (see Table 11-2 for input pin selection numbers)

1111111 = Input tied to RP127

.

.

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

REGISTER 11-44: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| U-0                       | U-0 | R/W-0        | R/W-0 | R/W-0                              | R/W-0  | R/W-0              | R/W-0 |  |  |

|---------------------------|-----|--------------|-------|------------------------------------|--------|--------------------|-------|--|--|

| _                         | _   |              |       | RP65F                              | ₹<5:0> |                    |       |  |  |

| bit 15                    |     |              |       |                                    |        |                    | bit 8 |  |  |

| U-0                       | U-0 | R/W-0        | R/W-0 | R/W-0                              | R/W-0  | R/W-0              | R/W-0 |  |  |

| _                         | -   |              |       | RP64F                              |        |                    |       |  |  |

| bit 7                     |     |              |       |                                    |        |                    | bit 0 |  |  |

| Legend:                   |     |              |       |                                    |        |                    |       |  |  |

| R = Readable              | bit | W = Writable | bit   | U = Unimplemented bit, read as '0' |        |                    |       |  |  |

| -n = Value at POR '1' = B |     |              |       | '0' = Bit is clea                  | red    | x = Bit is unknown |       |  |  |

bit 13-8**RP65R<5:0>:** Peripheral Output Function is Assigned to RP65 Output Pin bits<br/>(see Table 11-3 for peripheral function numbers)bit 7-6**Unimplemented:** Read as '0'

bit 5-0 **RP64R<5:0>:** Peripheral Output Function is Assigned to RP64 Output Pin bits (see Table 11-3 for peripheral function numbers)

#### **REGISTER 15-2:** OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2 (CONTINUED)

| bit 4-0 | SYNCSEL<4:0>: Trigger/Synchronization Source Selection bit        | s |

|---------|-------------------------------------------------------------------|---|

|         | 11111 = No Sync or Trigger source for OCx                         |   |

|         | 11110 = INT2 pin synchronizes or triggers OCx                     |   |

|         | 11101 = INT1 pin synchronizes or triggers OCx                     |   |

|         | 11100 = Reserved                                                  |   |

|         | 11011 = ADC1 module synchronizes or triggers OCx                  |   |

|         | 11010 = CMP3 module synchronizes or triggers OCx                  |   |

|         | 11001 = CMP2 module synchronizes or triggers OCx                  |   |

|         | 11000 = CMP1 module synchronizes or triggers OCx                  |   |

|         | 10111 = IC8 module synchronizes or triggers OCx                   |   |

|         | 10110 = IC7 module synchronizes or triggers OCx                   |   |

|         | 10101 = IC6 module synchronizes or triggers OCx                   |   |

|         | 10100 = IC5 module synchronizes or triggers OCx                   |   |

|         | 10011 = IC4 module synchronizes or triggers OCx                   |   |

|         | 10010 = IC3 module synchronizes or triggers OCx                   |   |

|         | 10001 = IC2 module synchronizes or triggers OCx                   |   |

|         | 10000 = IC1 module synchronizes or triggers OCx                   |   |

|         | 01111 = Timer5 synchronizes or triggers OCx                       |   |

|         | 01110 = Timer4 synchronizes or triggers OCx                       |   |

|         | 01101 = Timer3 synchronizes or triggers OCx                       |   |

|         | 01100 = Timer2 synchronizes or triggers OCx (default)             |   |

|         | 01011 = Timer1 synchronizes or triggers OCx                       |   |

|         | 01010 = No Sync or Trigger source for OCx                         |   |

|         | 01001 = OC9 module synchronizes or triggers $OCx^{(1,2)}$         |   |

|         | 01000 = OC8 module synchronizes or triggers $OCx^{(1,2)}$         |   |

|         | 00111 = OC7 module synchronizes or triggers $OCx^{(1,2)}$         |   |

|         | 00110 = OC6 module synchronizes or triggers $OCx^{(1,2)}$         |   |

|         | 00101 = OC5 module synchronizes or triggers $OCx^{(1,2)}$         |   |

|         | 00100 = OC4 module synchronizes or triggers $OCx^{(1,2)}$         |   |

|         | 00011 = OC3 module synchronizes or triggers $OCx^{(1,2)}$         |   |

|         | 00010 = OC2 module synchronizes or triggers $OCx^{(1,2)}$         |   |

|         | $00001 = OC1 \text{ module synchronizes or triggers OCx}^{(1,2)}$ |   |

|         | 00000 = No Sync or Trigger source for OCx                         |   |

- **Note 1:** Do not use the OCx module as its own Sync or Trigger source.

- 2: When the OCy module is turned OFF, it sends a trigger out signal. If the OCx module uses the OCy module as a Trigger source, the OCy module must be unselected as a Trigger source prior to disabling it.

#### REGISTER 16-21: FCLCONx: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER (CONTINUED)

bit 7-3

FLTSRC<4:0>: Fault Control Signal Source Select bits for PWM Generator #<sup>(2,3)</sup>

- 11111 = Reserved

- 00100 = Fault 5 00011 = Fault 4

- 00010 = Fault 3

- 00001 = Fault 2

- 00000 = Fault 1

bit 2 **FLTPOL:** Fault Polarity bit for PWM Generator #<sup>(1)</sup>

- 1 = The selected Fault source is active-low

- 0 = The selected Fault source is active-high

#### bit 1-0 FLTMOD<1:0>: Fault Mode bits for PWM Generator #

- 11 = Fault input is disabled

- 10 = Reserved

- 01 = The selected Fault source forces PWMxH, PWMxL pins to FLTDAT values (cycle)

- 00 = The selected Fault source forces PWMxH, PWMxL pins to FLTDAT values (latched condition)

- **Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

- 2: When Independent Fault mode is enabled (IFLTMOD = 1) and Fault 1 is used for Fault mode (FLTSRC<4:0> = 01000), the Current-Limit Control Source Select bits (CLSRC<4:0>) should be set to an unused current-limit source to prevent the current-limit source from disabling both the PWMxH and PWMxL outputs.

- 3: When Independent Fault mode is enabled (IFLTMOD = 1) and Fault 1 is used for Current-Limit mode (CLSRC<4:0> = 01000), the Fault Control Source Select bits (FLTSRC<4:0>) should be set to an unused Fault source to prevent Fault 1 from disabling both the PWMxL and PWMxH outputs.

## **REGISTER 17-7: VELXCNT: VELOCITY COUNTER x REGISTER**

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                                  | R/W-0 | R/W-0 | R/W-0 |  |  |

|------------------------------------|-------|-------|-------|----------------------------------------|-------|-------|-------|--|--|

|                                    |       |       | VELCI | NT<15:8>                               |       |       |       |  |  |

| bit 15                             |       |       |       |                                        |       |       | bit 8 |  |  |

|                                    |       |       |       |                                        |       |       |       |  |  |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                                  | R/W-0 | R/W-0 | R/W-0 |  |  |

|                                    |       |       | VELC  | NT<7:0>                                |       |       |       |  |  |

| bit 7                              |       |       |       |                                        |       |       | bit 0 |  |  |

|                                    |       |       |       |                                        |       |       |       |  |  |

| Legend:                            |       |       |       |                                        |       |       |       |  |  |

| R = Readable bit W = Writable bit  |       |       |       | U = Unimplemented bit, read as '0'     |       |       |       |  |  |

| -n = Value at POR '1' = Bit is set |       |       |       | '0' = Bit is cleared x = Bit is unknow |       |       |       |  |  |

bit 15-0 VELCNT<15:0>: Velocity Counter bits

## REGISTER 17-8: INDXxCNTH: INDEX COUNTER x HIGH WORD REGISTER

| R/W-0          | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|----------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| INDXCNT<31:24> |       |       |       |       |       |       |       |  |  |

| bit 15 bit 8   |       |       |       |       |       |       |       |  |  |

| R/W-0          | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|----------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| INDXCNT<23:16> |       |       |       |       |       |       |       |  |  |

| bit 7 bit 0    |       |       |       |       |       |       |       |  |  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-0 INDXCNT<31:16>: High Word Used to Form 32-Bit Index Counter Register (INDXxCNT) bits

#### REGISTER 17-9: INDXxCNTL: INDEX COUNTER x LOW WORD REGISTER

| R/W-0                                                                   | R/W-0 | R/W-0          | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|-------------------------------------------------------------------------|-------|----------------|-------|------------------------------------|-------|-------|-------|

|                                                                         |       |                | INDXC | NT<15:8>                           |       |       |       |

| bit 15                                                                  |       |                |       |                                    |       |       | bit 8 |

|                                                                         |       |                |       |                                    |       |       |       |

| R/W-0                                                                   | R/W-0 | R/W-0          | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|                                                                         |       |                | INDXC | NT<7:0>                            |       |       |       |

| bit 7                                                                   |       |                |       |                                    |       |       | bit 0 |

|                                                                         |       |                |       |                                    |       |       |       |

| Legend:                                                                 |       |                |       |                                    |       |       |       |

| R = Readable                                                            | bit   | W = Writable b | oit   | U = Unimplemented bit, read as '0' |       |       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unkr |       |                | nown  |                                    |       |       |       |

bit 15-0 INDXCNT<15:0>: Low Word Used to Form 32-Bit Index Counter Register (INDXxCNT) bits

NOTES:

| R/W-0           | R/W-0                                                                                                                                                                                                                             | R/W-0                                                                                                                                   | U-0                                                                                       | R/W-0, HC                                                           | R/W-0                                    | R-0               | R-1            |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------|-------------------|----------------|

| UTXISEL1        | UTXINV                                                                                                                                                                                                                            | UTXISEL0                                                                                                                                | —                                                                                         | UTXBRK                                                              | UTXEN <sup>(1)</sup>                     | UTXBF             | TRMT           |

| bit 15          |                                                                                                                                                                                                                                   |                                                                                                                                         |                                                                                           |                                                                     |                                          |                   | bit 8          |

|                 |                                                                                                                                                                                                                                   |                                                                                                                                         |                                                                                           |                                                                     |                                          |                   |                |

| R/W-0           | R/W-0                                                                                                                                                                                                                             | R/W-0                                                                                                                                   | R-1                                                                                       | R-0                                                                 | R-0                                      | R/C-0             | R-0            |

| URXISE          | L<1:0>                                                                                                                                                                                                                            | ADDEN                                                                                                                                   | RIDLE                                                                                     | PERR                                                                | FERR                                     | OERR              | URXDA          |

| bit 7           |                                                                                                                                                                                                                                   |                                                                                                                                         |                                                                                           |                                                                     |                                          |                   | bit (          |

|                 |                                                                                                                                                                                                                                   |                                                                                                                                         |                                                                                           |                                                                     |                                          |                   |                |

| Legend:         |                                                                                                                                                                                                                                   | HC = Hardware                                                                                                                           | Clearable bit                                                                             | C = Clearabl                                                        |                                          |                   |                |

| R = Readable    | bit                                                                                                                                                                                                                               | W = Writable bit                                                                                                                        |                                                                                           | U = Unimple                                                         | mented bit, rea                          | id as '0'         |                |

| -n = Value at F | POR                                                                                                                                                                                                                               | '1' = Bit is set                                                                                                                        |                                                                                           | '0' = Bit is cle                                                    | eared                                    | x = Bit is unk    | nown           |

| bit 15,13       | 11 = Reserv<br>10 = Interrup<br>transmi<br>01 = Interrup<br>operatio<br>00 = Interrup<br>least or                                                                                                                                 | <b>0&gt;:</b> UARTx Transed; do not use of when a character buffer becomes of when the last cross are complete of when a character oper | er is transferre<br>empty<br>haracter is shit<br>d<br>ter is transferr<br>n in the transm | d to the Transn<br>fted out of the<br>ed to the Trans<br>it buffer) | nit Shift Registe<br>Transmit Shift F    | Register; all tra | ansmit         |

| bit 14          | UTXINV: UARTx Transmit Polarity Inversion bit<br>If IREN = 0:<br>1 = UxTX Idle state is '0'<br>0 = UxTX Idle state is '1'<br>If IREN = 1:<br>1 = IrDA encoded, UxTX Idle state is '1'<br>0 = IrDA encoded, UxTX Idle state is '0' |                                                                                                                                         |                                                                                           |                                                                     |                                          |                   |                |

| bit 12          | Unimplemen                                                                                                                                                                                                                        | ted: Read as '0'                                                                                                                        |                                                                                           |                                                                     |                                          |                   |                |

| bit 11          | UTXBRK: UA                                                                                                                                                                                                                        | ARTx Transmit Br                                                                                                                        | eak bit                                                                                   |                                                                     |                                          |                   |                |

|                 | cleared b                                                                                                                                                                                                                         | ync Break on nex<br>by hardware upor<br>eak transmission                                                                                | o completion                                                                              |                                                                     | wed by twelve                            | '0' bits, followe | ed by Stop bit |

| bit 10          | UTXEN: UAF                                                                                                                                                                                                                        | RTx Transmit Ena                                                                                                                        | ble bit <sup>(1)</sup>                                                                    |                                                                     |                                          |                   |                |

|                 | <ul> <li>1 = Transmit is enabled, UxTX pin is controlled by UARTx</li> <li>0 = Transmit is disabled, any pending transmission is aborted and the buffer is reset; UxTX controlled by port</li> </ul>                              |                                                                                                                                         |                                                                                           |                                                                     |                                          |                   |                |

| bit 9           | UTXBF: UAF                                                                                                                                                                                                                        | RTx Transmit Buff                                                                                                                       | er Full Status I                                                                          | oit (read-only)                                                     |                                          |                   |                |

|                 | 1 = Transmit<br>0 = Transmit                                                                                                                                                                                                      | : buffer is full<br>: buffer is not full,                                                                                               | at least one m                                                                            | ore character                                                       | can be written                           |                   |                |

| bit 8           | 1 = Transmit                                                                                                                                                                                                                      | mit Shift Register<br>Shift Register is e<br>Shift Register is                                                                          | empty and tran                                                                            | smit buffer is e                                                    |                                          |                   | as completed   |

| bit 7-6         |                                                                                                                                                                                                                                   | 0>: UARTx Rece                                                                                                                          |                                                                                           |                                                                     |                                          |                   |                |

|                 | 11 = Interrup<br>10 = Interrup<br>0x = Interrup                                                                                                                                                                                   | ot is set on UxRSI<br>ot is set on UxRSI<br>ot is set when any<br>receive buffer has                                                    | R transfer mak<br>R transfer mak<br>y character is                                        | ing the receive<br>ing the receive<br>received and t                | e buffer full (i.e.<br>e buffer 3/4 full | (i.e., has 3 dat  | a characters   |

**Note 1:** Refer to **Section 17. "UART"** (DS70582) in the *"dsPIC33E/PIC24E Family Reference Manual"* for information on enabling the UARTx module for transmit operation.

# 21.0 ENHANCED CAN (ECAN™) MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXX(GP/MC/MU)806/ 810/814 and PIC24EPXXX(GP/GU)810/ 814 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 21. "Enhanced Controller Area Network (ECAN™)" (DS70353) of the "dsPIC33E/ PIC24E Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

# 21.1 Overview

The Enhanced Controller Area Network (ECAN) module is a serial interface, useful for communicating with other CAN modules or microcontroller devices. This interface/protocol was designed to allow communications within noisy environments. The dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814 devices contain two ECAN modules.

The ECANx module is a communication controller implementing the CAN 2.0 A/B protocol, as defined in the BOSCH CAN Specification. The module supports CAN 1.2, CAN 2.0A, CAN 2.0B Passive and CAN 2.0B Active versions of the protocol. The module implementation is a full CAN system. The CAN Specification is not covered within this data sheet. The reader can refer to the BOSCH CAN specification for further details. The ECANx module features are as follows:

- Implementation of the CAN Protocol, CAN 1.2, CAN 2.0A and CAN 2.0B

- · Standard and Extended Data Frames

- 0-8 Bytes Data Length

- Programmable Bit Rate up to 1 Mbit/sec

- Automatic Response to Remote Transmission Requests

- Up to 8 Transmit Buffers with Application-Specific Prioritization and Abort Capability (each buffer can contain up to 8 bytes of data)

- Up to 32 Receive Buffers (each buffer can contain up to 8 bytes of data)

- Up to 16 Full (standard/extended identifier) Acceptance Filters

- Three Full Acceptance Filter Masks

- DeviceNet<sup>™</sup> Addressing Support

- Programmable Wake-up Functionality with Integrated Low-Pass Filter

- Programmable Loopback mode Supports Self-Test Operation

- Signaling via Interrupt Capabilities for all CAN Receiver and Transmitter Error States

- · Programmable Clock Source

- Programmable Link to Input Capture Module (IC2 for the ECAN1 and ECAN2 modules) for Time-Stamping and Network Synchronization

- · Low-Power Sleep and Idle mode

The CAN bus module consists of a protocol engine and message buffering/control. The CAN protocol engine handles all functions for receiving and transmitting messages on the CAN bus. Messages are transmitted by first loading the appropriate data registers. Status and errors can be checked by reading the appropriate registers. Any message detected on the CAN bus is checked for errors and then matched against filters to see if it should be received and stored in one of the receive registers.

| R/W-0                                                                 | R/W-0                                                                                                                                                             | R/W-0                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| F15MSK<1:0>                                                           |                                                                                                                                                                   | K<1:0>                                                                                                                                                                                                                                                                                                                                                                                              | F13MS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SK<1:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | F12MSK<1:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|                                                                       |                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                                                                       |                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |