Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 60 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART, USB OTG             |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                     |

| Number of I/O              | 51                                                                                |

| Program Memory Size        | 256КВ (85.5К х 24)                                                                |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 12K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x10/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

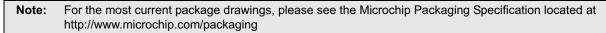

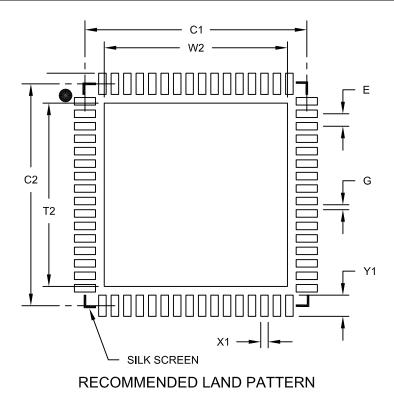

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-VQFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256mu806t-i-mr |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1      |             | Pin     | Buffer    |     |                                                 |  |  |  |  |  |  |

|--------------|-------------|---------|-----------|-----|-------------------------------------------------|--|--|--|--|--|--|

| Pin          | Name        | Туре    | Туре      | PPS | Description                                     |  |  |  |  |  |  |

| T1CK         |             | I       | ST        | No  | Timer1 external clock input.                    |  |  |  |  |  |  |

| T2CK         |             | 1       | ST        | Yes | Timer2 external clock input.                    |  |  |  |  |  |  |

| T3CK         |             | 1       | ST        | Yes | Timer3 external clock input.                    |  |  |  |  |  |  |

| T4CK         |             | I       | ST        | Yes | Timer4 external clock input.                    |  |  |  |  |  |  |

| T5CK         |             | I       | ST        | Yes | Timer5 external clock input.                    |  |  |  |  |  |  |

| T6CK         |             | 1       | ST        | Yes | Timer6 external clock input.                    |  |  |  |  |  |  |

| T7CK         |             | 1       | ST        | Yes | Timer7 external clock input.                    |  |  |  |  |  |  |

| T8CK         |             | I       | ST        | Yes | Timer8 external clock input.                    |  |  |  |  |  |  |

| T9CK         |             | I       | ST        | Yes | Timer9 external clock input.                    |  |  |  |  |  |  |

| U1CTS        |             | I       | ST        | Yes | UART1 Clear-to-Send.                            |  |  |  |  |  |  |

| U1RTS        |             | 0       | —         | Yes | UART1 Ready-to-Send.                            |  |  |  |  |  |  |

| U1RX         |             | I       | ST        | Yes | UART1 receive.                                  |  |  |  |  |  |  |

| U1TX         |             | 0       | —         | Yes | UART1 transmit.                                 |  |  |  |  |  |  |

| U2CTS        |             | I       | ST        | Yes | UART2 Clear-to-Send.                            |  |  |  |  |  |  |

| U2RTS        |             | 0       | —         | Yes | UART2 Ready-to-Send.                            |  |  |  |  |  |  |

| U2RX         |             | I       | ST        | Yes | UART2 receive.                                  |  |  |  |  |  |  |

| U2TX         |             | 0       |           | Yes | UART2 transmit.                                 |  |  |  |  |  |  |

| U3CTS        |             | I       | ST        | Yes | UART3 Clear-to-Send.                            |  |  |  |  |  |  |

| <b>U3RTS</b> |             | 0       | —         | Yes | UART3 Ready-to-Send.                            |  |  |  |  |  |  |

| U3RX         |             | I       | ST        | Yes | UART3 receive.                                  |  |  |  |  |  |  |

| U3TX         |             | 0       |           | Yes | UART3 transmit.                                 |  |  |  |  |  |  |

| U4CTS        |             | I       | ST        | Yes | UART4 Clear-to-Send.                            |  |  |  |  |  |  |

| U4RTS        |             | 0       | —         | Yes | UART4 Ready-to-Send.                            |  |  |  |  |  |  |

| U4RX         |             | I       | ST        | Yes | UART4 receive.                                  |  |  |  |  |  |  |

| U4TX         |             | 0       | —         | Yes | UART4 transmit.                                 |  |  |  |  |  |  |

| SCK1         |             | I/O     | ST        | Yes | Synchronous serial clock input/output for SPI1. |  |  |  |  |  |  |

| SDI1         |             | I       | ST        | Yes | SPI1 data in.                                   |  |  |  |  |  |  |

| SDO1         |             | 0       | —         | Yes | SPI1 data out.                                  |  |  |  |  |  |  |

| SS1          |             | I/O     | ST        | Yes | SPI1 slave synchronization or frame pulse I/O.  |  |  |  |  |  |  |

| SCK2         |             | I/O     | ST        | No  | Synchronous serial clock input/output for SPI2. |  |  |  |  |  |  |

| SDI2         |             | I       | ST        | No  | SPI2 data in.                                   |  |  |  |  |  |  |

| SDO2         |             | 0       |           | No  | SPI2 data out.                                  |  |  |  |  |  |  |

| SS2          |             | I/O     | ST        | Yes | SPI2 slave synchronization or frame pulse I/O.  |  |  |  |  |  |  |

| SCK3         |             | I/O     | ST        | Yes | Synchronous serial clock input/output for SPI3. |  |  |  |  |  |  |

| SDI3         |             |         | ST        |     | SPI3 data in.                                   |  |  |  |  |  |  |

| SDO3         |             | 0       |           | Yes | SPI3 data out.                                  |  |  |  |  |  |  |

| SS3          |             | I/O     | ST        | Yes | SPI3 slave synchronization or frame pulse I/O.  |  |  |  |  |  |  |

| SCK4         |             | I/O     | ST        | Yes | Synchronous serial clock input/output for SPI4. |  |  |  |  |  |  |

| SDI4         |             | I       | ST        | Yes | SPI4 data in.                                   |  |  |  |  |  |  |

| SDO4         |             | 0       | —         | Yes | SPI4 data out.                                  |  |  |  |  |  |  |

| SS4          |             | I/O     | ST        | Yes | SPI4 slave synchronization or frame pulse I/O.  |  |  |  |  |  |  |

| Legend:      | CMOS = CN   |         |           |     |                                                 |  |  |  |  |  |  |

|              | ST = Schmit |         |           |     |                                                 |  |  |  |  |  |  |

|              | PPS = Perip | heral F | Pin Selec | t   | TTL = TTL input buffer                          |  |  |  |  |  |  |

#### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: This pin is available on dsPIC33EPXXX(MC/MU)806/810/814 devices only.

- **2:** AVDD must be connected at all times.

- 3: These pins are input only on dsPIC33EPXXXMU8XX and PIC24EPXXXGU8XX devices.

- 4: These pins are only available on dsPIC33EPXXXMU8XX and PIC24EPXXXGU8XX devices.

- 5: The availability of I<sup>2</sup>C<sup>™</sup> interfaces varies by device. Refer to the "Pin Diagrams" section for availability. Selection (SDAx/SCLx or ASDAx/ASCLx) is made using the device Configuration bits, ALTI2C1 and ALTI2C2 (FPOR<5:4>). See Section 29.0 "Special Features" for more information.

- 6: Analog functionality is activated by enabling the USB module and is not controlled by the ANSEL register.

#### 4.2.5 X AND Y DATA SPACES

The dsPIC33EPXXX(GP/MC/MU)806/810/814 core has two data spaces, X and Y. These data spaces can be considered either separate (for some DSP instructions), or as one unified linear address range (for MCU instructions). The data spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms such as Finite Impulse Response (FIR) filtering and Fast Fourier Transform (FFT).

The PIC24EPXXX(GP/GU)806/810/814 devices do not have a Y data space and a Y AGU. For these devices, the entire data space is treated as X data space.

The X data space is used by all instructions and supports all addressing modes. X data space has separate read and write data buses. The X read data bus is the read data path for all instructions that view data space as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class).

The Y data space is used in concert with the X data space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths.

Both the X and Y data spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to X data space. Modulo Addressing and Bit-Reversed Addressing are not present in PIC24EPXXX(GP/ GU)806/810/814 devices.

All data memory writes, including in DSP instructions, view data space as combined X and Y address space. The boundary between the X and Y data spaces is device-dependent and is not user-programmable.

#### 4.2.6 DMA RAM

Each dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814 device contains 4 Kbytes of dual ported DMA RAM located at the end of Y data RAM and is part of Y data space. Memory locations in the DMA RAM space are accessible simultaneously by the CPU and the DMA Controller module. DMA RAM is utilized by the DMA controller to store data to be transferred to various peripherals using DMA, as well as data transferred from various peripherals using DMA. The DMA RAM can be accessed by the DMA controller without having to steal cycles from the CPU. When the CPU and the DMA controller attempt to concurrently write to the same DMA RAM location, the hardware ensures that the CPU is given precedence in accessing the DMA RAM location. Therefore, the DMA RAM provides a reliable means of transferring DMA data without ever having to stall the CPU.

| Note 1: | DMA                                      | RAM | can | be | used | for | general |  |  |  |  |

|---------|------------------------------------------|-----|-----|----|------|-----|---------|--|--|--|--|

|         | purpose data storage if the DMA function |     |     |    |      |     |         |  |  |  |  |

|         | is not required in an application.       |     |     |    |      |     |         |  |  |  |  |

2: On PIC24EPXXX(GP/GU)806/810/814 devices, DMA RAM is located at the end of X data RAM and is part of X data space.

#### 4.3 Program Memory Resources

Many useful resources related to the Program Memory are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en554310                                        |

#### 4.3.1 KEY RESOURCES

- Section 4. "Program Memory" (DS70612) in the "dsPIC33E/PIC24E Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related *"dsPIC33E/PIC24E Family Reference Manual"* Sections

- Development Tools

#### 4.4 Special Function Register Maps

Table 4-1 through Table 4-72 provide mapping tables for all Special Function Registers (SFRs).

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12     | Bit 11     | Bit 10 | Bit 9 | Bit 8   | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|--------|------------|------------|--------|-------|---------|-------|-------|-------|--------|-------|-------|-------|-------|---------------|

| N0        | 0000  |        |        |        |            | •          | •      |       | W0 (WR  | EG)   |       |       |        | •     |       |       | •     | 0000          |

| W1        | 0002  |        |        |        |            |            |        |       | W1      |       |       |       |        |       |       |       |       | 0000          |

| W2        | 0004  |        |        |        |            |            |        |       | W2      |       |       |       |        |       |       |       |       | 0000          |

| W3        | 0006  |        |        |        |            |            |        |       | W3      |       |       |       |        |       |       |       |       | 0000          |

| W4        | 8000  |        |        |        |            |            |        |       | W4      |       |       |       |        |       |       |       |       | 0000          |

| W5        | 000A  |        | W5     |        |            |            |        |       |         |       |       |       |        | 0000  |       |       |       |               |

| W6        | 000C  |        | W6     |        |            |            |        |       |         |       |       |       |        | 0000  |       |       |       |               |

| W7        | 000E  |        | W7     |        |            |            |        |       |         |       |       |       |        | 0000  |       |       |       |               |

| W8        | 0010  |        |        |        |            |            |        |       | W8      |       |       |       |        |       |       |       |       | 0000          |

| W9        | 0012  |        |        |        |            |            |        |       | W9      |       |       |       |        |       |       |       |       | 0000          |

| W10       | 0014  |        |        |        |            |            |        |       | W10     |       |       |       |        |       |       |       |       | 0000          |

| W11       | 0016  |        |        |        |            |            |        |       | W11     |       |       |       |        |       |       |       |       | 0000          |

| W12       | 0018  |        |        |        |            |            |        |       |         |       |       |       | 0000   |       |       |       |       |               |

| W13       | 001A  |        |        |        |            |            |        |       | W13     |       |       |       |        |       |       |       |       | 0000          |

| W14       | 001C  |        | W14 0  |        |            |            |        |       |         |       |       |       | 0000   |       |       |       |       |               |

| W15       | 001E  |        | W15    |        |            |            |        |       |         |       |       |       | 1000   |       |       |       |       |               |

| SPLIM     | 0020  |        |        |        |            |            |        |       | SPLIN   | Λ     |       |       |        |       |       |       |       | 0000          |

| ACCAL     | 0022  |        |        |        |            |            |        |       | ACCA    | L     |       |       |        |       |       |       |       | 0000          |

| ACCAH     | 0024  |        |        |        |            |            |        |       | ACCA    | Н     |       |       |        |       |       |       |       | 0000          |

| ACCAU     | 0026  |        |        | Sig    | n-Extensio | n of ACCA< | 39>    |       |         |       |       |       | AC     | CAU   |       |       |       | 0000          |

| ACCBL     | 0028  |        |        |        |            |            |        |       | ACCB    | L     |       |       |        |       |       |       |       | 0000          |

| ACCBH     | 002A  |        |        |        |            |            |        |       | ACCB    | Н     |       |       |        |       |       |       |       | 0000          |

| ACCBU     | 002C  |        |        | Sig    | n-Extensio | n of ACCB< | 39>    |       |         |       |       |       | AC     | CBU   |       |       |       | 0000          |

| PCL       | 002E  |        |        |        |            |            |        |       | PCL     |       |       |       |        |       |       |       | —     | 0000          |

| PCH       | 0030  | _      | _      | _      | _          | _          | _      | _     | —       | _     |       |       |        | PCH   |       |       |       | 0000          |

| DSRPAG    | 0032  | _      | _      | _      | _          | —          | _      |       |         |       |       | DSRP  | AG     |       |       |       |       | 0001          |

| DSWPAG    | 0034  | _      | _      | _      | _          | —          | _      | —     |         |       |       | [     | DSWPAG |       |       |       |       | 0001          |

| RCOUNT    | 0036  |        |        |        |            |            |        |       | RCOUN   | ΝT    |       |       |        |       |       |       |       | 0000          |

| DCOUNT    | 0038  |        |        |        |            |            |        |       | DCOUN   | NT    |       |       |        |       |       |       |       | 0000          |

| DOSTARTL  | 003A  |        |        |        |            |            |        | D     | OSTARTL |       |       |       |        |       |       |       | —     | 0000          |

| DOSTARTH  | 003C  | —      | _      | —      | —          | —          | —      | —     | —       | —     | —     |       |        | DOST  | ARTH  |       |       | 0000          |

| DOENDL    | 003E  |        |        |        |            |            |        |       | DOENDL  |       |       | •     |        |       |       |       | —     | 0000          |

| DOENDH    | 0040  | _      | _      | _      | _          | _          | _      | _     | _       | _     | _     |       |        | DOE   | NDH   |       |       | 0000          |

#### TABLE 4-1: CPU CORE REGISTER MAP FOR dsPIC33EPXXX(GP/MC/MU)806/810/814 DEVICES ONLY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| IABLE        | 4-41. | FER    |             |            |        | INFUT      | REGIST |       |       | 5610331 |             |            |           |            | 1     |       |       |               |  |  |  |  |  |  |  |

|--------------|-------|--------|-------------|------------|--------|------------|--------|-------|-------|---------|-------------|------------|-----------|------------|-------|-------|-------|---------------|--|--|--|--|--|--|--|

| File<br>Name | Addr. | Bit 15 | Bit 14      | Bit 13     | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7   | Bit 6       | Bit 5      | Bit 4     | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |  |  |  |  |  |  |  |

| RPINR0       | 06A0  | _      |             |            |        | INT1R<6:0  | >      |       |       | _       | —           | -          | —         | —          | —     | —     | —     | 0000          |  |  |  |  |  |  |  |

| RPINR1       | 06A2  | —      |             |            |        | INT3R<6:0  | >      |       |       | —       |             |            |           | INT2R<6:0> | >     |       |       | 0000          |  |  |  |  |  |  |  |

| RPINR2       | 06A4  | —      | —           | —          | —      |            | —      | _     | —     | —       | INT4R<6:0>  |            |           |            |       |       | 0000  |               |  |  |  |  |  |  |  |

| RPINR3       | 06A6  | —      |             | T3CKR<6:0> |        |            |        |       |       | —       |             |            |           | T2CKR<6:0  | >     |       |       | 0000          |  |  |  |  |  |  |  |

| RPINR4       | 06A8  | —      |             | T5CKR<6:0> |        |            |        |       |       | —       |             |            |           | T4CKR<6:0  | >     |       |       | 0000          |  |  |  |  |  |  |  |

| RPINR5       | 06AA  | —      |             | T7CKR<6:0> |        |            |        |       |       | —       | T6CKR<6:0>  |            |           |            |       | 0000  |       |               |  |  |  |  |  |  |  |

| RPINR6       | 06AC  | —      |             | T9CKR<6:0> |        |            |        |       |       | —       |             |            |           | T8CKR<6:0  | >     |       |       | 0000          |  |  |  |  |  |  |  |

| RPINR7       | 06AE  | —      |             | IC2R<6:0>  |        |            |        |       |       | —       |             |            |           | IC1R<6:0>  |       |       |       | 0000          |  |  |  |  |  |  |  |

| RPINR8       | 06B0  | —      |             |            |        | IC4R<6:0>  |        |       |       | —       |             |            |           | IC3R<6:0>  |       |       |       | 0000          |  |  |  |  |  |  |  |

| RPINR9       | 06B2  | —      |             |            |        | IC6R<6:0>  |        |       |       | —       |             |            |           | IC5R<6:0>  |       |       |       | 0000          |  |  |  |  |  |  |  |

| RPINR10      | 06B4  | —      | IC8R<6:0>   |            |        |            |        |       |       | —       |             |            |           | IC7R<6:0>  |       |       |       | 0000          |  |  |  |  |  |  |  |

| RPINR11      | 06B6  | —      | OCFBR<6:0>  |            |        |            |        |       |       | —       |             |            |           | OCFAR<6:0  | >     |       |       | 0000          |  |  |  |  |  |  |  |

| RPINR12      | 06B8  | —      | FLT2R<6:0>  |            |        |            |        | —     |       |         |             | FLT1R<6:0> | >         |            |       | 0000  |       |               |  |  |  |  |  |  |  |

| RPINR13      | 06BA  | _      | FLT4R<6:0>  |            |        |            |        |       |       | —       | FLT3R<6:0>  |            |           |            |       | 0000  |       |               |  |  |  |  |  |  |  |

| RPINR14      | 06BC  | _      | QEB1R<6:0>  |            |        |            |        |       | —     |         |             | (          | QEA1R<6:0 | >          |       |       | 0000  |               |  |  |  |  |  |  |  |

| RPINR15      | 06BE  | —      | HOME1R<6:0> |            |        |            |        |       |       | —       |             |            | I         | NDX1R<6:0  | >     |       |       | 0000          |  |  |  |  |  |  |  |

| RPINR16      | 06C0  | —      |             | QEB2R<6:0> |        |            |        |       |       | —       |             |            |           | QEA2R<6:0  | >     |       |       | 0000          |  |  |  |  |  |  |  |

| RPINR17      | 06C2  | —      |             |            | F      | IOME2R<6:  | 0>     |       |       | —       | INDX2R<6:0> |            |           |            | 0000  |       |       |               |  |  |  |  |  |  |  |

| RPINR18      | 06C4  | —      |             |            | ι      | J1CTSR<6:  | 0>     |       |       | —       | U1RXR<6:0>  |            |           |            |       | 0000  |       |               |  |  |  |  |  |  |  |

| RPINR19      | 06C6  | —      |             |            | ι      | J2CTSR<6:  | 0>     |       |       | —       | U2RXR<6:0>  |            |           |            |       |       | 0000  |               |  |  |  |  |  |  |  |

| RPINR20      | 06C8  | —      |             |            |        | SCK1R<6:0  | >      |       |       | —       | SDI1R<6:0>  |            |           |            |       |       | 0000  |               |  |  |  |  |  |  |  |

| RPINR21      | 06CA  | —      | —           | —          | —      |            | —      | _     | —     | —       |             |            |           | SS1R<6:0>  |       |       |       | 0000          |  |  |  |  |  |  |  |

| RPINR23      | 06CE  | —      | —           | —          | —      |            | —      | _     | —     | —       | SS2R<6:0>   |            |           |            |       |       | 0000  |               |  |  |  |  |  |  |  |

| RPINR24      | 06D0  | —      |             |            | 1      | CSCKR<6:0  | )>     |       | _     | —       |             |            |           | CSDIR<6:0  | >     |       |       | 0000          |  |  |  |  |  |  |  |

| RPINR25      | 06D2  | —      | —           | _          | _      |            | —      | —     | —     | —       |             |            | С         | OFSINR<6:  | 0>    |       |       | 0000          |  |  |  |  |  |  |  |

| RPINR26      | 06D4  | —      |             |            |        | C2RXR<6:0  | >      |       |       | —       |             |            |           | C1RXR<6:0  | >     |       |       | 0000          |  |  |  |  |  |  |  |

| RPINR27      | 06D6  | —      |             |            | ι      | J3CTSR<6:  | 0>     |       |       | —       |             |            |           | U3RXR<6:0  | >     |       |       | 0000          |  |  |  |  |  |  |  |

| RPINR28      | 06D8  | _      |             |            | ι      | J4CTSR<6:  | 0>     |       |       | —       | U4RXR<6:0>  |            |           |            |       | 0000  |       |               |  |  |  |  |  |  |  |

| RPINR29      | 06DA  | _      |             |            |        | SCK3R<6:0  | >      |       |       | —       | SDI3R<6:0>  |            |           |            |       | 0000  |       |               |  |  |  |  |  |  |  |

| RPINR30      | 06DC  | _      | _           | —          | —      | _          | —      | —     | —     | _       | SS3R<6:0>   |            |           |            |       |       | 0000  |               |  |  |  |  |  |  |  |

| RPINR31      | 06DE  | _      |             |            |        | SCK4R<6:0  | >      |       |       | _       | SDI4R<6:0>  |            |           |            |       |       | 0000  |               |  |  |  |  |  |  |  |

| RPINR32      | 06E0  | _      | _           | —          |        | _          | —      | —     | —     | _       | SS4R<6:0>   |            |           |            |       | 0000  |       |               |  |  |  |  |  |  |  |

| RPINR33      | 06E2  | _      |             |            |        | IC10R<6:03 | >      |       |       | _       | IC9R<6:0>   |            |           |            | 0000  |       |       |               |  |  |  |  |  |  |  |

| RPINR34      | 06E4  | _      |             |            |        | IC12R<6:0  | >      |       |       | _       |             |            |           | IC11R<6:0> | ·     |       |       | 0000          |  |  |  |  |  |  |  |

#### TABLE 4-41: PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR dsPIC33EPXXXMU810 DEVICES ONLY

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| REGISTER 5-2: | NVMADRU: NONVOLATILE MEMORY UPPER ADDRESS REGISTER |

|---------------|----------------------------------------------------|

|---------------|----------------------------------------------------|

| U-0             | U-0   | U-0              | U-0   | U-0                                     | U-0   | U-0   | U-0   |  |  |  |

|-----------------|-------|------------------|-------|-----------------------------------------|-------|-------|-------|--|--|--|

| —               | —     | —                | —     | —                                       | _     | —     | —     |  |  |  |

| bit 15          | •     |                  |       |                                         |       |       | bit 8 |  |  |  |

|                 |       |                  |       |                                         |       |       |       |  |  |  |

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x                                   | R/W-x | R/W-x | R/W-x |  |  |  |

|                 |       |                  | NVMAE | )RU<7:0>                                |       |       |       |  |  |  |

| bit 7           |       |                  |       |                                         |       |       | bit 0 |  |  |  |

|                 |       |                  |       |                                         |       |       |       |  |  |  |

| Legend:         |       |                  |       |                                         |       |       |       |  |  |  |

| R = Readable    | bit   | W = Writable I   | bit   | U = Unimplemented bit, read as '0'      |       |       |       |  |  |  |

| -n = Value at F | POR   | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |  |  |

| bit 15-8 | Unimplemented: Read as '0' |

|----------|----------------------------|

| 511 15-0 |                            |

bit 7-0 **NVMADRU<7:0>:** Nonvolatile Memory Upper Write Address bits Selects the upper 8 bits of the location to program or erase in program Flash memory. This register may be read or written by the user application.

#### REGISTER 5-3: NVMADR: NONVOLATILE MEMORY ADDRESS REGISTER

| R/W-x          | R/W-x | R/W-x            | R/W-x | R/W-x        | R/W-x            | R/W-x    | R/W-x |

|----------------|-------|------------------|-------|--------------|------------------|----------|-------|

|                |       |                  | NVMA  | DR<15:8>     |                  |          |       |

| bit 15         |       |                  |       |              |                  |          | bit 8 |

|                |       |                  |       |              |                  |          |       |

| R/W-x          | R/W-x | R/W-x            | R/W-x | R/W-x        | R/W-x            | R/W-x    | R/W-x |

|                |       |                  | NVMA  | DR<7:0>      |                  |          |       |

| bit 7          |       |                  |       |              |                  |          | bit 0 |

|                |       |                  |       |              |                  |          |       |

| Legend:        |       |                  |       |              |                  |          |       |

| R = Readable I | bit   | W = Writable bit | t     | U = Unimpler | mented bit, read | d as '0' |       |

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 NVMADR<15:0>: Nonvolatile Memory Write Address bits

Selects the lower 16 bits of the location to program or erase in program Flash memory. This register may be read or written by the user application.

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

| W-0         | W-0         | W-0 | W-0 | W-0 | W-0 | W-0 | W-0 |  |  |

|-------------|-------------|-----|-----|-----|-----|-----|-----|--|--|

| NVMKEY<7:0> |             |     |     |     |     |     |     |  |  |

| bit 7       | bit 7 bit 0 |     |     |     |     |     |     |  |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **NVMKEY<7:0>:** Key Register (write-only) bits

| REGISTER 9-6: | ACLKDIV3: AUXILIARY CLOCK DIVISOR REGISTER 3 <sup>(1,2)</sup> |

|---------------|---------------------------------------------------------------|

|---------------|---------------------------------------------------------------|

| U-0                                | U-0 | U-0 | U-0                                     | U-0                                | U-0          | U-0   | U-0   |

|------------------------------------|-----|-----|-----------------------------------------|------------------------------------|--------------|-------|-------|

| —                                  | —   | —   | _                                       | —                                  | —            | —     | —     |

| bit 15                             |     |     |                                         |                                    |              |       | bit 8 |

|                                    |     |     |                                         |                                    |              |       |       |

| U-0                                | U-0 | U-0 | U-0                                     | U-0                                | R/W-0        | R/W-0 | R/W-0 |

|                                    | —   | —   | _                                       | _                                  | APLLDIV<2:0> |       |       |

| bit 7                              | •   |     |                                         |                                    |              |       | bit 0 |

|                                    |     |     |                                         |                                    |              |       |       |

| Legend:                            |     |     |                                         |                                    |              |       |       |

| R = Readable bit W = Writable bit  |     |     | bit                                     | U = Unimplemented bit, read as '0' |              |       |       |

| -n = Value at POR '1' = Bit is set |     |     | '0' = Bit is cleared x = Bit is unknown |                                    |              | nown  |       |

bit 15-3 Unimplemented: Read as '0'

| bit 2-0 | APLLDIV<2:0>: PLL Feedback Divisor bits (PLL Multiplier Ratio) |

|---------|----------------------------------------------------------------|

|         | 111 <b>= 24</b>                                                |

|         | 110 <b>= 21</b>                                                |

|         | 101 <b>= 20</b>                                                |

|         | 100 = 19                                                       |

|         | 011 <b>= 18</b>                                                |

|         | 010 = 17                                                       |

|         | 001 = 16                                                       |

|         | 000 = 15 (default)                                             |

Note 1: This register resets only on a Power-on Reset (POR).

2: This register is only available on dsPIC33EPXXXMU8XX and PIC24EPXXXGU8XX devices.

| U-0               | R/W-0        | R/W-0                                            | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |

|-------------------|--------------|--------------------------------------------------|----------------|------------------|------------------|-----------------|-------|--|--|--|--|

| —                 |              |                                                  |                | CSCKR<6:0>       | >                |                 |       |  |  |  |  |

| bit 15            |              |                                                  |                |                  |                  |                 | bit 8 |  |  |  |  |

|                   |              |                                                  |                |                  |                  |                 |       |  |  |  |  |

| U-0               | R/W-0        | R/W-0                                            | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |

|                   |              |                                                  |                | CSDIR<6:0>       |                  |                 |       |  |  |  |  |

| bit 7             |              |                                                  |                |                  |                  |                 | bit C |  |  |  |  |

|                   |              |                                                  |                |                  |                  |                 |       |  |  |  |  |

| Legend:           |              |                                                  |                |                  |                  |                 |       |  |  |  |  |

| R = Readable bit  |              | W = Writable                                     | bit            | U = Unimpler     | nented bit, read | d as '0'        |       |  |  |  |  |

| -n = Value at POR |              | '1' = Bit is set                                 |                | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |  |  |  |  |

|                   |              |                                                  |                |                  |                  |                 |       |  |  |  |  |

| bit 15            | Unimpleme    | nted: Read as '                                  | 0'             |                  |                  |                 |       |  |  |  |  |

| bit 14-8          | CSCKR<6:0    | )>: Assign DCI (                                 | Clock Input (C | SCK) to the Co   | rresponding RI   | Pn/RPIn Pin bit | s     |  |  |  |  |

|                   | (see Table 1 | 1-2 for input pin                                | selection num  | nbers)           |                  |                 |       |  |  |  |  |

|                   | 1111111 =    | Input tied to RP                                 | 127            |                  |                  |                 |       |  |  |  |  |

|                   | •            |                                                  |                |                  |                  |                 |       |  |  |  |  |

|                   | •            |                                                  |                |                  |                  |                 |       |  |  |  |  |

|                   | •            | Input tied to CM                                 | D1             |                  |                  |                 |       |  |  |  |  |

|                   |              | Input tied to Vss                                |                |                  |                  |                 |       |  |  |  |  |

| bit 7             |              | nted: Read as '                                  |                |                  |                  |                 |       |  |  |  |  |

| bit 6-0           | •            | Assign DCI D                                     |                | )I) to the Corre | sponding RPn/    | RPIn Pin hits   |       |  |  |  |  |

|                   |              |                                                  |                |                  | sponding rain    |                 |       |  |  |  |  |

|                   | -            | (see Table 11-2 for input pin selection numbers) |                |                  |                  |                 |       |  |  |  |  |

|                   |              |                                                  |                |                  |                  |                 |       |  |  |  |  |

|                   |              |                                                  |                |                  |                  |                 |       |  |  |  |  |

|                   |              |                                                  |                |                  |                  |                 |       |  |  |  |  |

|                   |              | Input tied to CM                                 |                |                  |                  |                 |       |  |  |  |  |

### REGISTER 11-24: RPINR24: PERIPHERAL PIN SELECT INPUT REGISTER 24

0000000 = Input tied to Vss

#### 12.1 Timer Resources

Many useful resources related to Timers are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en554310              |

#### 12.1.1 KEY RESOURCES

- Section 11. "Timers" (DS70362) in the "dsPIC33E/PIC24E Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All related *"dsPIC33E/PIC24E Family Reference Manual"* Sections

- Development Tools

| HSC-0                  | HSC-0                            | HSC-0                                                                          | R/W-0                 | R/W-0            | R/W-0                             | R/W-0                         | R/W-0               |

|------------------------|----------------------------------|--------------------------------------------------------------------------------|-----------------------|------------------|-----------------------------------|-------------------------------|---------------------|

| FLTSTAT <sup>(1)</sup> | CLSTAT <sup>(1)</sup>            | TRGSTAT                                                                        | FLTIEN                | CLIEN            | TRGIEN                            | ITB <sup>(2)</sup>            | MDCS <sup>(2)</sup> |

| bit 15                 |                                  |                                                                                |                       |                  |                                   |                               | bit 8               |

|                        |                                  |                                                                                |                       | DAMO             |                                   |                               |                     |

| R/W-0                  | R/W-0                            | R/W-0<br>DTCP <sup>(3)</sup>                                                   | U-0                   | R/W-0            | R/W-0<br>CAM <sup>(2,4)</sup>     | R/W-0<br>XPRES <sup>(5)</sup> | R/W-0               |

|                        | <1:0>                            | DICPO                                                                          | —                     | MTBS             | CAM-,-,-/                         | XPRES <sup>(0)</sup>          | -                   |

| bit 7                  |                                  |                                                                                |                       |                  |                                   |                               | bit                 |

| Legend:                |                                  | HSC = Set or                                                                   | Cleared in Ha         | ardware          |                                   |                               |                     |

| R = Readable           | bit                              | W = Writable                                                                   | bit                   | U = Unimplei     | mented bit, rea                   | d as '0'                      |                     |

| -n = Value at F        | POR                              | '1' = Bit is set                                                               |                       | '0' = Bit is cle | eared                             | x = Bit is unkr               | nown                |

| bit 15                 | 1 = Fault inte<br>0 = No Fault i | ult Interrupt Sta<br>rrupt is pending<br>interrupt is pen-<br>ared by setting  | )<br>ding             |                  |                                   |                               |                     |

| bit 14                 | 1 = Current-li<br>0 = No currer  | rent-Limit Intern<br>mit interrupt is<br>nt-limit interrupt<br>ared by setting | pending<br>is pending | (1)              |                                   |                               |                     |

| bit 13                 | 1 = Trigger in<br>0 = No trigger | igger Interrupt<br>terrupt is pendi<br>r interrupt is pe<br>ared by setting    | ng<br>nding           |                  |                                   |                               |                     |

| bit 12                 | 1 = Fault inte                   | t Interrupt Enal<br>rrupt is enablec<br>rrupt is disablec                      | 1                     | T bit is cleared | d                                 |                               |                     |

| bit 11                 | 1 = Current-li                   | ent-Limit Interru<br>mit interrupt is                                          | enabled               |                  |                                   |                               |                     |

|                        |                                  | mit interrupt is                                                               |                       | CLSTAT bit is    | cleared                           |                               |                     |

| bit 10                 |                                  | ger Interrupt E                                                                |                       |                  |                                   |                               |                     |

|                        | 0 = Trigger ev                   | event generate<br>vent interrupts a                                            | are disabled a        |                  | bit is cleared                    |                               |                     |

| bit 9                  | 1 = PHASEx/                      | dent Time Base<br>SPHASEx regise<br>egister provides                           | sters provide t       |                  | od for this PWN<br>ator           | 1 generator                   |                     |

| bit 8                  |                                  | er Duty Cycle F                                                                |                       |                  |                                   |                               |                     |

|                        |                                  |                                                                                |                       |                  | PWM generate<br>ation for this PV |                               |                     |

| <b>2:</b> The          | ese bits should                  | ar the interrupt<br>not be changeo<br>r DTCP to be e                           | d after the PW        | M is enabled (   | (PTEN = 1).                       | it in the interrup            | t controller.       |

|                        |                                  |                                                                                |                       |                  | -                                 | Alianed mode.                 | If ITB = $0.$ th    |

#### REGISTER 16-11: PWMCONx: PWMx CONTROL REGISTER

- 4: The Independent Time Base (ITB = 1) mode must be enabled to use Center-Aligned mode. If ITB = 0, the CAM bit is ignored.

- **5:** To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

| <b>REGISTER 16-14:</b> PHASEX: PWMX PRIMARY PHASE SHIFT REGISTER <sup>(1,2)</sup> |

|-----------------------------------------------------------------------------------|

|-----------------------------------------------------------------------------------|

| R/W-0 R/W                         | /-0 R/W-0 | R/W-0  | R/W-0        | D M M A          |        |       |

|-----------------------------------|-----------|--------|--------------|------------------|--------|-------|

|                                   |           | 1011 0 | K/W-U        | R/W-0            | R/W-0  | R/W-0 |

|                                   |           | PHASE  | Ex<15:8>     |                  |        |       |

| bit 15                            |           |        |              |                  |        | bit 8 |

|                                   |           |        |              |                  |        |       |

| R/W-0 R/W                         | /-0 R/W-0 | R/W-0  | R/W-0        | R/W-0            | R/W-0  | R/W-0 |

|                                   |           | PHAS   | Ex<7:0>      |                  |        |       |

| bit 7                             |           |        |              |                  |        | bit 0 |

|                                   |           |        |              |                  |        |       |

| Legend:                           |           |        |              |                  |        |       |

| R = Readable bit W = Writable bit |           |        | U = Unimplei | mented bit, read | as '0' |       |

bit 15-0 **PHASEx<15:0>:** PWM Phase Shift Value or Independent Time Base Period for the PWM Generator bits

**Note 1:** If ITB (PWMCONx<9>) = 0, the following applies based on the mode of operation:

'1' = Bit is set

• Complementary, Redundant and Push-Pull Output mode (PMOD<1:0> (IOCON<11:10>) = 00, 01 or 10), PHASEx<15:0> = Phase shift value for PWMxH and PWMxL outputs.

'0' = Bit is cleared

- True Independent Output mode (PMOD<1:0> (IOCONx<11:10>) = 11), PHASEx<15:0> = Phase shift value for PWMxH only.

- **2:** If ITB (PWMCONx<9>) = 1, the following applies based on the mode of operation:

- Complementary, Redundant and Push-Pull Output mode (PMOD<1:0> (IOCONx<11:10>) = 00, 01 or 10), PHASEx<15:0> = Independent time base period value for PWMxH and PWMxL.

- True Independent Output mode (PMOD<1:0> (IOCONx<11:10>) = 11), PHASEx<15:0> = Independent time base period value for PWMxH only.

-n = Value at POR

x = Bit is unknown

#### 24.2 DCI Resources

Many useful resources related to DCI are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| In the event you are not able to access the |

|---------------------------------------------|

| product page using the link above, enter    |

| this URL in your browser:                   |

| http://www.microchip.com/wwwproducts/       |

| Devices.aspx?dDocName=en554310              |

|                                             |

#### 24.2.1 KEY RESOURCES

- Section 20. "Data Converter Interface (DCI)" (DS70356) in the "dsPIC33E/PIC24E Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All related *"dsPIC33E/PIC24E Family Reference Manual"* Sections

- Development Tools

## **REGISTER 26-4: RTCVAL (WHEN RTCPTR<1:0> = 11): YEAR VALUE REGISTER<sup>(1)</sup>**

| U-0          | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 |  |

|--------------|-----|-----|-----|-----|-----|-----|-----|--|

| —            | —   | —   | _   | _   | —   | —   | —   |  |

| bit 15 bit 8 |     |     |     |     |     |     |     |  |

| R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |        |       |

|-------|-------|-------|-------|-------|-------|--------|-------|

|       | YRTEN | <3:0> |       |       | YRONI | E<3:0> |       |

| bit 7 |       |       |       |       |       |        | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-8 | Unimplemented: Read as '0'                                       |

|----------|------------------------------------------------------------------|

| bit 7-4  | YRTEN<3:0>: Binary Coded Decimal Value of Year's Tens Digit bits |

|          | Contains a value from 0 to 9.                                    |

| bit 3-0  | YRONE<3:0>: Binary Coded Decimal Value of Year's Ones Digit bits |

|          | Contains a value from 0 to 9.                                    |

**Note 1:** A write to the YEAR register is only allowed when RTCWREN = 1.

## REGISTER 26-5: RTCVAL (WHEN RTCPTR<1:0> = 10): MONTH AND DAY VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | R-x     | R-x | R-x   | R-x     | R-x   |

|--------|-----|-----|---------|-----|-------|---------|-------|

| _      | —   | —   | MTHTEN0 |     | MTHON | IE<3:0> |       |

| bit 15 |     |     |         |     |       |         | bit 8 |

| U-0   | U-0 | R/W-x | R/W-x  | R/W-x | R/W-x | R/W-x   | R/W-x |

|-------|-----|-------|--------|-------|-------|---------|-------|

| —     | —   | DAYTE | N<1:0> |       | DAYON | IE<3:0> |       |

| bit 7 |     |       |        |       |       |         | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                         |

|-----------|--------------------------------------------------------------------|

| bit 12    | MTHTEN0: Binary Coded Decimal Value of Month's Tens Digit bit      |

|           | Contains a value of 0 or 1.                                        |

| bit 11-8  | MTHONE<3:0>: Binary Coded Decimal Value of Month's Ones Digit bits |

|           | Contains a value from 0 to 9.                                      |

| bit 7-6   | Unimplemented: Read as '0'                                         |

| bit 5-4   | DAYTEN<1:0>: Binary Coded Decimal Value of Day's Tens Digit bits   |

|           | Contains a value from 0 to 3.                                      |

| hit 3-0   | DAYONE<3:0> Binary Coded Decimal Value of Day's Ones Digit hits    |

bit 3-0 **DAYONE<3:0>:** Binary Coded Decimal Value of Day's Ones Digit bits Contains a value from 0 to 9.

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

# REGISTER 26-8: ALRMVAL (WHEN ALRMPTR<1:0> = 10): ALARM MONTH AND DAY VALUE REGISTER<sup>(1)</sup>

| U-0          | U-0        | U-0                               | R/W-x         | R/W-x             | R/W-x           | R/W-x           | R/W-x |

|--------------|------------|-----------------------------------|---------------|-------------------|-----------------|-----------------|-------|

| _            | —          | —                                 | MTHTEN0       |                   | MTHO            | NE<3:0>         |       |

| bit 15       |            |                                   |               |                   |                 |                 | bit 8 |

| U-0          | U-0        | R/W-x                             | R/W-x         | R/W-x             | R/W-x           | R/W-x           | R/W-x |

| _            | _          | DAYTE                             | EN<1:0>       |                   | DAYO            | NE<3:0>         |       |

| bit 7        |            |                                   |               |                   |                 |                 | bit 0 |

|              |            |                                   |               |                   |                 |                 |       |

| Legend:      |            |                                   |               |                   |                 |                 |       |

| R = Readab   | le bit     | W = Writable                      | bit           | U = Unimplen      | nented bit, rea | d as '0'        |       |

| -n = Value a | t POR      | '1' = Bit is se                   | t             | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|              |            |                                   |               |                   |                 |                 |       |

| bit 15-13    | Unimplemer | nted: Read as                     | '0'           |                   |                 |                 |       |

| bit 12       |            | Binary Coded E<br>alue of 0 or 1. | Decimal Value | of Month's Tens   | s Digit bit     |                 |       |

- bit 11-8MTHONE<3:0>: Binary Coded Decimal Value of Month's Ones Digit bits<br/>Contains a value from 0 to 9.bit 7-6Unimplemented: Read as '0'

- bit 5-4 **DAYTEN<1:0>:** Binary Coded Decimal Value of Day's Tens Digit bits Contains a value from 0 to 3.

- bit 3-0 **DAYONE<3:0>:** Binary Coded Decimal Value of Day's Ones Digit bits Contains a value from 0 to 9.

- **Note 1:** A write to this register is only allowed when RTCWREN = 1.

| Base<br>Instr<br># | nstr Mnemonic |                        | Assembly Syntax         | Description                              | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |

|--------------------|---------------|------------------------|-------------------------|------------------------------------------|---------------|-------------------------------|--------------------------|

| 1                  | ADD           | ADD Acc <sup>(1)</sup> |                         | Add Accumulators                         | 1             | 1                             | OA,OB,SA,SB              |

|                    |               | ADD                    | f                       | f = f + WREG                             | 1             | 1                             | C,DC,N,OV,Z              |

|                    |               | ADD                    | f,WREG                  | WREG = f + WREG                          | 1             | 1                             | C,DC,N,OV,Z              |

|                    |               | ADD                    | #lit10,Wn               | Wd = lit10 + Wd                          | 1             | 1                             | C,DC,N,OV,Z              |

|                    |               | ADD                    | Wb,Ws,Wd                | Wd = Wb + Ws                             | 1             | 1                             | C,DC,N,OV,Z              |

|                    |               | ADD                    | Wb,#lit5,Wd             | Wd = Wb + lit5                           | 1             | 1                             | C,DC,N,OV,Z              |

|                    |               | ADD                    | Wso,#Slit4,Acc          | 16-bit Signed Add to Accumulator         | 1             | 1                             | OA,OB,SA,SB              |

| 2                  | ADDC          | ADDC                   | f                       | f = f + WREG + (C)                       | 1             | 1                             | C,DC,N,OV,Z              |

|                    |               | ADDC                   | f,WREG                  | WREG = f + WREG + (C)                    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |               | ADDC                   | #lit10,Wn               | Wd = lit10 + Wd + (C)                    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |               | ADDC                   | Wb,Ws,Wd                | Wd = Wb + Ws + (C)                       | 1             | 1                             | C,DC,N,OV,Z              |

|                    |               | ADDC                   | Wb,#lit5,Wd             | Wd = Wb + lit5 + (C)                     | 1             | 1                             | C,DC,N,OV,Z              |

| 3                  | AND           | AND                    | f                       | f = f .AND. WREG                         | 1             | 1                             | N,Z                      |

|                    |               | AND                    | f,WREG                  | WREG = f .AND. WREG                      | 1             | 1                             | N,Z                      |

|                    |               | AND                    | #lit10,Wn               | Wd = lit10 .AND. Wd                      | 1             | 1                             | N,Z                      |

|                    |               | AND                    | Wb,Ws,Wd                | Wd = Wb .AND. Ws                         | 1             | 1                             | N,Z                      |

|                    |               | AND                    | Wb,#lit5,Wd             | Wd = Wb .AND. lit5                       | 1             | 1                             | N,Z                      |

| 1                  | ASR           | ASR                    | f                       | f = Arithmetic Right Shift f             | 1             | 1                             | C,N,OV,Z                 |

|                    |               | ASR                    | f,WREG                  | WREG = Arithmetic Right Shift f          | 1             | 1                             | C,N,OV,Z                 |

|                    |               | ASR                    | Ws,Wd                   | Wd = Arithmetic Right Shift Ws           | 1             | 1                             | C,N,OV,Z                 |

|                    |               | ASR                    | Wb,Wns,Wnd              | Wnd = Arithmetic Right Shift Wb by Wns   | 1             | 1                             | N,Z                      |

|                    |               | ASR                    | Wb,#lit5,Wnd            | Wnd = Arithmetic Right Shift Wb by lit5  | 1             | 1                             | N,Z                      |

| 5                  | BCLR          | BCLR                   | f,#bit4                 | Bit Clear f                              | 1             | 1                             | None                     |

|                    |               | BCLR                   | Ws,#bit4                | Bit Clear Ws                             | 1             | 1                             | None                     |

| 6                  | BRA           | BRA                    | C,Expr                  | Branch if Carry                          | 1             | 1 (4)                         | None                     |

|                    |               | BRA                    | GE,Expr                 | Branch if greater than or equal          | 1             | 1 (4)                         | None                     |

|                    |               | BRA                    | GEU, Expr               | Branch if unsigned greater than or equal | 1             | 1 (4)                         | None                     |

|                    |               | BRA                    | GT,Expr                 | Branch if greater than                   | 1             | 1 (4)                         | None                     |

|                    |               | BRA                    | GTU, Expr               | Branch if unsigned greater than          | 1             | 1 (4)                         | None                     |

|                    |               | BRA                    | LE,Expr                 | Branch if less than or equal             | 1             | 1 (4)                         | None                     |

|                    |               | BRA                    | LEU, Expr               | Branch if unsigned less than or equal    | 1             | 1 (4)                         | None                     |

|                    |               | BRA                    | LT,Expr                 | Branch if less than                      | 1             | 1 (4)                         | None                     |

|                    |               | BRA                    | LTU, Expr               | Branch if unsigned less than             | 1             | 1 (4)                         | None                     |

|                    |               | BRA                    | N,Expr                  | Branch if Negative                       | 1             | 1 (4)                         | None                     |

|                    |               | BRA                    | NC,Expr                 | Branch if Not Carry                      | 1             | 1 (4)                         | None                     |

|                    |               | BRA                    | NN, Expr                | Branch if Not Negative                   | 1             | 1 (4)                         | None                     |

|                    |               | BRA                    | NOV, Expr               | Branch if Not Overflow                   | 1             | 1 (4)                         | None                     |

|                    |               | BRA                    | NZ,Expr                 | Branch if Not Zero                       | 1             | 1 (4)                         | None                     |

|                    |               | BRA                    | OA, Expr(1)             | Branch if Accumulator A overflow         | 1             | 1 (4)                         | None                     |

|                    |               | BRA                    | OB, Expr(1)             | Branch if Accumulator B overflow         | 1             | 1 (4)                         | None                     |

|                    |               | BRA                    | OV, Expr(1)             | Branch if Overflow                       | 1             | 1 (4)                         | None                     |

|                    |               | BRA                    | SA, Expr(1)             | Branch if Accumulator A saturated        | 1             | 1 (4)                         | None                     |

|                    |               | BRA                    | SB, Expr <sup>(1)</sup> | Branch if Accumulator B saturated        | 1             | 1 (4)                         | None                     |

|                    |               | BRA                    | Expr                    | Branch Unconditionally                   | 1             | 4                             | None                     |

|                    |               | BRA                    | Z,Expr                  | Branch if Zero                           | 1             | 4<br>1 (4)                    | None                     |

|                    |               | BRA                    | Z,Expr<br>Wn            | Computed Branch                          | 1             | 4                             | None                     |

| 7                  | BSET          | BSET                   | f,#bit4                 | Bit Set f                                | 1             | 4                             | None                     |

|                    |               |                        |                         |                                          |               |                               |                          |

#### TABLE 30-2 INSTRUCTION SET OVERVIEW

Note 1:

This instruction is available in dsPIC33EPXXX(GP/MC/MU)806/810/814 devices only. Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle. 2:

| Base<br>Instr<br># | Assembly<br>Mnemonic | Assembly Syntax |                                           | Description                                                | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |

|--------------------|----------------------|-----------------|-------------------------------------------|------------------------------------------------------------|---------------|-------------------------------|--------------------------|

| 8                  | BSW                  |                 |                                           | Write C bit to Ws <wb></wb>                                | 1             | 1                             | None                     |

|                    |                      | BSW.Z           | Ws,Wb                                     | Write Z bit to Ws <wb></wb>                                | 1             | 1                             | None                     |

| 9                  | BTG                  | BTG             | f,#bit4                                   | Bit Toggle f                                               | 1             | 1                             | None                     |

|                    |                      | BTG             | Ws,#bit4                                  | Bit Toggle Ws                                              | 1             | 1                             | None                     |

| 10                 | BTSC                 | BTSC            | f,#bit4                                   | Bit Test f, Skip if Clear                                  |               | 1<br>(2 or 3)                 | None                     |

|                    |                      | BTSC            | Ws,#bit4                                  | Bit Test Ws, Skip if Clear                                 | 1             | 1<br>(2 or 3)                 | None                     |

| 11                 | BTSS                 | BTSS            | f,#bit4                                   | Bit Test f, Skip if Set                                    | 1             | 1<br>(2 or 3)                 | None                     |

|                    |                      | BTSS            | Ws,#bit4                                  | Bit Test Ws, Skip if Set                                   | 1             | 1<br>(2 or 3)                 | None                     |

| 12                 | BTST                 | BTST            | f,#bit4                                   | Bit Test f                                                 | 1             | 1                             | Z                        |

|                    |                      | BTST.C          | Ws,#bit4                                  | Bit Test Ws to C                                           | 1             | 1                             | С                        |

|                    |                      | BTST.Z          | Ws,#bit4                                  | Bit Test Ws to Z                                           | 1             | 1                             | Z                        |

|                    |                      | BTST.C          | Ws,Wb                                     | Bit Test Ws <wb> to C</wb>                                 | 1             | 1                             | С                        |

|                    |                      | BTST.Z          | Ws,Wb                                     | Bit Test Ws <wb> to Z</wb>                                 | 1             | 1                             | Z                        |

| 13                 | BTSTS                | BTSTS           | f,#bit4                                   | Bit Test then Set f                                        | 1             | 1                             | Z                        |

|                    |                      | BTSTS.C         | Ws,#bit4                                  | Bit Test Ws to C, then Set                                 | 1             | 1                             | С                        |

|                    |                      | BTSTS.Z         | Ws,#bit4                                  | Bit Test Ws to Z, then Set                                 | 1             | 1                             | Z                        |

| 14                 | CALL                 | CALL            | lit23                                     | Call subroutine                                            | 2             | 4                             | SFA                      |

|                    |                      | CALL            | Wn                                        | Call indirect subroutine                                   | 1             | 4                             | SFA                      |

|                    |                      | CALL.L          | Wn                                        | Call indirect subroutine (long address)                    | 1             | 4                             | SFA                      |

| 15                 | CLR                  | CLR             | f                                         | f = 0x0000                                                 | 1             | 1                             | None                     |

|                    |                      | CLR             | WREG                                      | WREG = 0x0000                                              | 1             | 1                             | None                     |

|                    |                      | CLR             | Ws                                        | Ws = 0x0000                                                | 1             | 1                             | None                     |

|                    |                      | CLR             | Acc, Wx, Wxd, Wy, Wyd, AWB <sup>(1)</sup> | Clear Accumulator                                          | 1             | 1                             | OA,OB,SA,SE              |