Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 60 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART, USB OTG             |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                     |

| Number of I/O              | 51                                                                                |

| Program Memory Size        | 256КВ (85.5К х 24)                                                                |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 12K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x10/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256mu806t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS AND MICROCONTROLLERS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "dsPIC33E/PIC24E Family Reference Manual", which is available from the Microchip web site (www.microchip.com)

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

# 2.1 Basic Connection Requirements

Getting started with the 16-bit DSCs and microcontrollers requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins (regardless if ADC module is not used) (see Section 2.2 "Decoupling Capacitors")

- VCAP (see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins**")

- OSC1 and OSC2 pins when external oscillator source is used (see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

- VUSB3V3 pin is used when utilizing the USB module. If the USB module is not used, VUSB3V3 must be connected to VDD.

- VREF+/VREF- pin is used when external voltage reference for ADC module is implemented

| Note: | The AVDD and AVSS pins must be         |  |  |  |  |  |  |  |  |  |

|-------|----------------------------------------|--|--|--|--|--|--|--|--|--|

|       | connected independent of the ADC       |  |  |  |  |  |  |  |  |  |

|       | voltage reference source. The voltage  |  |  |  |  |  |  |  |  |  |

|       | difference between AVDD and VDD cannot |  |  |  |  |  |  |  |  |  |

|       | exceed 300 mV at any time during       |  |  |  |  |  |  |  |  |  |

|       | operation or start-up.                 |  |  |  |  |  |  |  |  |  |

# 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, VUSB3V3, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended to use ceramic capacitors.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, above tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

# 2.9 Application Examples

- Induction heating

- Uninterruptable Power Supplies (UPS)

- DC/AC inverters

- Compressor motor control

- Washing machine 3-phase motor control

- BLDC motor control

- Automotive HVAC, cooling fans, fuel pumps

- · Stepper motor control

- Audio and fluid sensor monitoring

- · Camera lens focus and stability control

- Speech (playback, hands-free kits, answering machines, VoIP)

- Consumer audio

- Industrial and building control (security systems and access control)

- Barcode reading

- · Networking: LAN switches, gateways

- · Data storage device management

- · Smart cards and smart card readers

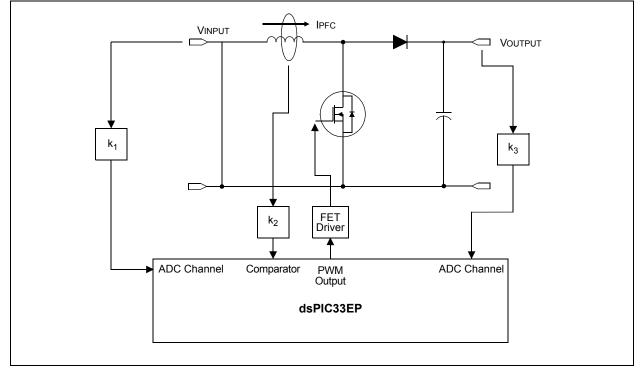

Examples of typical application connections are shown in Figure 2-4 through Figure 2-8.

# FIGURE 2-4: BOOST CONVERTER IMPLEMENTATION

#### PWM GENERATOR 4 REGISTER MAP FOR dsPIC33EPXXX(MC/MU)806/810/814 DEVICES ONLY **TABLE 4-16**: All File Name Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Addr. Resets 0C80 FLTSTAT CLSTAT TRGSTAT FLTIEN CLIEN TRGIEN ITB MDCS DTC<1:0> DTCP MTBS CAM XPRES IUE PWMCON4 0000 \_ IOCON4 0C82 PENH PENL POLH POLL PMOD<1:0> **OVRENH** OVRENL OVRDAT<1:0> FLTDAT<1:0> CLDAT<1:0> SWAP OSYNC 0000 FCLCON4 0C84 IFLTMOD CLSRC<4:0> CLPOL CLMOD FLTSRC<4:0> FLTPOL FLTMOD<1:0> 0000 PDC4 0C86 PDC4<15:0> 0000 0C88 PHASE4 PHASE4<15:0> 0000 DTR4 0C8A DTR4<13:0> 0000 ALTDTR4 0C8C ALTDTR4<13:0> \_ \_\_\_\_ 0000 SDC4 0C8E SDC4<15:0> 0000 0C90 SPHASE4 SPHASE4<15:0> 0000 0C92 TRIG4 TRGCMP<15:0> 0000 0C94 TRGDIV<3:0> TRGCON4 \_ \_ \_ TRGSTRT<5:0> 0000 PWMCAP4 0C98 PWMCAP4<15:0> 0000 LEBCON4 0C9A PHR PHF PLR PLF FLTLEBEN CLLEBEN \_ \_ \_ \_ BCH BCL BPHH BPHL BPLH BPLL 0000 LEBDLY4 0C9C LEB<11:0> \_ 0000 \_ \_ \_ AUXCON4 0C9E BLANKSEL<3:0> CHOPSEL<3:0> CHOPHEN CHOPLEN \_ \_ \_ \_ \_ 0000 \_

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-17: PWM GENERATOR 5 REGISTER MAP FOR dsPIC33EPXXX(MC/MU)810/814 DEVICES ONLY

| WMCON5<br>CON5<br>CLCON5<br>DC5                                         |                                                              | Bit 15<br>FLTSTAT<br>PENH | Bit 14<br>CLSTAT | Bit 13  | Bit 12    | Bit 11   | Bit 10  | Bit 9                  | Bit 8                                            | Bit 7         | Bit 6                     | Bit 5   | Bit 4                                                                                                        | Bit 3   | Bit 2     | Bit 1   | Bit 0   | All    |

|-------------------------------------------------------------------------|--------------------------------------------------------------|---------------------------|------------------|---------|-----------|----------|---------|------------------------|--------------------------------------------------|---------------|---------------------------|---------|--------------------------------------------------------------------------------------------------------------|---------|-----------|---------|---------|--------|

| DCON5<br>CLCON5                                                         | 0CA2                                                         |                           |                  | TRGSTAT |           |          |         |                        |                                                  |               |                           |         | BRA                                                                                                          | Ditto   | DRI       |         |         | Resets |

| CLCON5                                                                  |                                                              | PENH                      |                  | -       | FLTIEN    | CLIEN    | TRGIEN  | ITB                    | MDCS                                             | DTC<          | 1:0>                      | DTCP    | _                                                                                                            | MTBS    | CAM       | XPRES   | IUE     | 0000   |

|                                                                         | 0CA4                                                         |                           | PENL             | POLH    | POLL      | PMOD     | <1:0>   | OVRENH                 | OVRENL                                           | OVRDA         | T<1:0>                    | FLTDA   | T<1:0>                                                                                                       | CLDA    | AT<1:0>   | SWAP    | OSYNC   | 0000   |

| DC5                                                                     |                                                              | IFLTMOD                   |                  | C       | CLSRC<4:0 | >        |         | CLPOL                  | CLMOD                                            |               | FLT                       | SRC<4:0 | P — MTBS CAM XPRES IUE<br>DAT<1:0> CLDAT<1:0> SWAP OSYNC<br>4:0> FLTPOL FLTMOD<1:0><br>TRGSTRT<5:0>          |         |           | 0000    |         |        |

|                                                                         | 0CA6                                                         |                           |                  |         |           |          |         |                        | PDC5<15:0>                                       |               |                           |         |                                                                                                              |         |           |         |         | 0000   |

| HASE5                                                                   | 0CA8                                                         |                           |                  |         |           |          |         | F                      | PHASE5<15:0                                      | )>            |                           |         |                                                                                                              |         |           |         |         | 0000   |

| TR5                                                                     | 0CAA                                                         | _                         | _                |         |           |          |         |                        | [                                                | DTR5<13:0     | >                         |         |                                                                                                              |         |           |         |         | 0000   |

| LTDTR5                                                                  | 0CAC                                                         | _                         | _                |         |           |          |         |                        | AL                                               | TDTR5<13:     | :0>                       |         | DTCP — MTBS CAM XPRES IUE<br>FLTDAT<1:0> CLDAT<1:0> SWAP OSYNC<br>RC<4:0> FLTPOL FLTMOD<1:0><br>TRGSTRT<5:0> |         |           | 0000    |         |        |

| DC5                                                                     | 0CAE                                                         |                           |                  |         |           |          |         |                        | SDC5<15:0>                                       |               |                           |         |                                                                                                              |         |           |         |         | 0000   |

| PHASE5                                                                  | 0CB0                                                         |                           |                  |         |           |          |         | S                      | PHASE5<15:                                       | 0>            |                           |         |                                                                                                              |         |           |         |         | 0000   |

| RIG5                                                                    | 0CB2                                                         |                           |                  |         |           |          |         | Т                      | RGCMP<15:                                        | 0>            |                           |         |                                                                                                              |         |           |         |         | 0000   |

| RGCON5                                                                  | 0CB4                                                         |                           | TRGDI            | V<3:0>  |           | _        | _       | _                      | _                                                | _             | _                         |         |                                                                                                              | TRO     | GSTRT<5:0 | >       |         | 0000   |

| WMCAP5                                                                  | 0CB8                                                         |                           |                  |         |           |          |         | PW                     | M Capture<1                                      | 5:0>          |                           |         |                                                                                                              |         |           |         |         | 0000   |

| EBCON5                                                                  | 0CBA                                                         | PHR                       | PHF              | PLR     | PLF       | FLTLEBEN | CLLEBEN |                        | _                                                | _             |                           | BCH     | BCL                                                                                                          | BPHH    | BPHL      | BPLH    | BPLL    | 0000   |

| EBDLY5                                                                  | 0CBC                                                         | _                         | _                | _       | —         |          |         |                        |                                                  |               | LEB<11:0                  | )>      |                                                                                                              |         |           |         |         | 0000   |

| UXCON5                                                                  | 0CBE                                                         | —                         | _                | _       | —         |          | BLANKS  | SEL<3:0>               |                                                  | _             | _                         |         | CHOPS                                                                                                        | EL<3:0> |           | CHOPHEN | CHOPLEN | 0000   |

| LTDTR5<br>DC5<br>PHASE5<br>RIG5<br>RGCON5<br>WMCAP5<br>EBCON5<br>EBCLY5 | 0CAC<br>0CAE<br>0CB0<br>0CB2<br>0CB4<br>0CB8<br>0CBA<br>0CBC | PHR<br>–                  | TRGDI<br>PHF<br> | PLR     |           |          | CLLEBEN | S<br>T<br>—<br>PW<br>— | AL<br>SDC5<15:0><br>PHASE5<15:<br>RGCMP<15:<br>— | TDTR5<13:<br> | :0><br>—<br>—<br>LEB<11:0 |         | -                                                                                                            | BPHH    | BPHL      | BPI     |         | I      |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12      | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6       | Bit 5       | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|-------------|--------|--------|-------|-------|-------|-------------|-------------|-------|-------|--------|-------|-------|---------------|

| RPOR0        | 0680  | _      | _      |        |             | RP65F  | २<5:0> |       |       | _     | _           | RP64R<5:0>  |       |       |        |       |       | 0000          |

| RPOR1        | 0682  | -      |        |        | RP67R<5:0>  |        |        |       |       |       |             |             |       | RP66  | R<5:0> |       |       | 0000          |

| RPOR2        | 0684  | _      | _      |        | RP69R<5:0>  |        |        |       |       | —     | _           |             |       | RP68  | R<5:0> |       |       | 0000          |

| RPOR3        | 0686  | _      | _      |        | RP71R<5:0>  |        |        |       |       |       | _           |             |       | RP70  | R<5:0> |       |       | 0000          |

| RPOR4        | 0688  | _      | _      |        | RP80R<5:0>  |        |        |       |       | —     | _           |             |       | RP79  | R<5:0> |       |       | 0000          |

| RPOR5        | 068A  | _      | _      |        | RP84R<5:0>  |        |        |       |       | —     | _           | RP82R<5:0>  |       |       |        |       | 0000  |               |

| RPOR6        | 068C  | _      | _      |        | RP87R<5:0>  |        |        |       |       | —     | _           |             |       | RP85  | R<5:0> |       |       | 0000          |

| RPOR7        | 068E  | _      | _      |        | RP97R<5:0>  |        |        |       |       | —     | _           |             |       | RP96  | R<5:0> |       |       | 0000          |

| RPOR8        | 0690  | -      | _      |        |             | RP99F  | R<5:0> |       |       |       | —           |             |       | RP98  | R<5:0> |       |       | 0000          |

| RPOR9        | 0692  | -      | _      |        |             | RP101  | R<5:0> |       |       |       | —           | RP100R<5:0> |       |       |        |       |       | 0000          |

| RPOR11       | 0696  | -      | _      |        |             | RP108  | R<5:0> |       |       |       | —           |             |       | RP104 | R<5:0> |       |       | 0000          |

| RPOR12       | 0698  | -      | _      |        | RP112R<5:0> |        |        |       |       |       | —           |             |       | RP109 | R<5:0> |       |       | 0000          |

| RPOR13       | 069A  | _      | _      |        | RP118R<5:0> |        |        |       | —     | —     | RP113R<5:0> |             |       |       |        |       | 0000  |               |

| RPOR14       | 069C  | _      | _      |        |             | RP125  | R<5:0> |       |       | —     | —           |             |       | RP120 | R<5:0> |       |       | 0000          |

| RPOR15       | 069E  | _      | _      |        |             | RP127  | R<5:0> |       |       | _     | _           |             |       | RP126 | R<5:0> |       |       | 0000          |

# TABLE 4-37:PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXMU810/814 AND PIC24EPXXXGU810/814DEVICES ONLY

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| Addressing Mode                                           | Description                                                                                            |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                              |

| Register Direct                                           | The contents of a register are accessed directly.                                                      |

| Register Indirect                                         | The contents of Wn forms the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn forms the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.             |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                     |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                              |

TABLE 4-75: FUNDAMENTAL ADDRESSING MODES SUPPORTED

#### 4.5.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions (dsPIC33EPXXXMU806/810/814 and PIC24EPXXXGU810/814) and the DSP accumulator class of instructions (dsPIC33EPXXXMU806/810/ 814 only) provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note: For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (Register Offset) field is shared by both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

**Note:** Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

## 4.5.4 MAC INSTRUCTIONS (dsPIC33EPXXXMU806/810/814 DEVICES ONLY)

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The two-source operand prefetch registers must be members of the set {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must, therefore, be valid addresses within X data space for W8 and W9 and Y data space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- Register Indirect

- Register Indirect Post-Modified by 2

- Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

# 4.5.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as NOP, do not have any operands.

#### 4.6.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. Address boundaries check for addresses equal to:

- The upper boundary addresses for incrementing buffers

- The lower boundary addresses for decrementing buffers

It is important to realize that the address boundaries check for addresses less than or greater than the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes can, therefore, jump beyond boundaries and still be adjusted correctly.

Note: The modulo corrected Effective Address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the Effective Address. When an address offset (such as [W7 + W2]) is used, Modulo Addressing correction is performed but the contents of the register remain unchanged.

# 4.7 Bit-Reversed Addressing (dsPIC33EPXXXMU806/810/814 Devices Only)

Bit-Reversed Addressing mode is intended to simplify data reordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which can be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

# 4.7.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled in any of these situations:

- BWMx bits (W register selection) in the MODCON register are any value other than '1111' (the stack cannot be accessed using Bit-Reversed Addressing)

- The BREN bit is set in the XBREV register

- The addressing mode used is Register Indirect with Pre-Increment or Post-Increment

If the length of a bit-reversed buffer is  $M = 2^N$  bytes, the last 'N' bits of the data buffer start address must be zeros.

XB<14:0> is the Bit-Reversed Address modifier, or 'pivot point,' which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

Note: All bit-reversed EA calculations assume word-sized data (LSb of every EA is always clear). The XB value is scaled accordingly to generate compatible (byte) addresses.

When enabled, Bit-Reversed Addressing is executed only for Register Indirect with Pre-Increment or Post-Increment Addressing and word-sized data writes. It does not function for any other addressing mode or for byte-sized data and normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XB) and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

Note: Modulo Addressing and Bit-Reversed Addressing can be enabled simultaneously using the same W register, but Bit-Reversed Addressing operation will always take precedence for data writes when enabled.

If Bit-Reversed Addressing has already been enabled by setting the BREN (XBREV<15>) bit, a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the Bit-Reversed Pointer.

# dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

#### **REGISTER 8-3:** DMAXSTAH: DMA CHANNEL X START ADDRESS REGISTER A (HIGH)

| U-0    | U-0   | U-0   | U-0   | U-0    | U-0   | U-0   | U-0   |

|--------|-------|-------|-------|--------|-------|-------|-------|

| _      | _     |       |       |        | _     |       | _     |

| bit 15 |       |       |       |        |       |       | bit 8 |

|        |       |       |       |        |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|        |       |       | STA<  | 23:16> |       |       |       |

| bit 7  |       |       |       |        |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 STA<23:16>: Primary Start Address bits (source or destination)

#### REGISTER 8-4: DMAXSTAL: DMA CHANNEL x START ADDRESS REGISTER A (LOW)

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | STA   | <15:8>           |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | STA   | <7:0>            |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimpler     | mented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-0 STA<15:0>: Primary Start Address bits (source or destination)

|                 |             |                                     |               |                  |                  |                 | <b>D</b> • |

|-----------------|-------------|-------------------------------------|---------------|------------------|------------------|-----------------|------------|

| U-0             | R-0         | R-0                                 | R-0           | R-0              | R-0              | R-0             | R-0        |

|                 | PPST14      | PPST13                              | PPST12        | PPST11           | PPST10           | PPST9           | PPST8      |

| bit 15          |             |                                     |               |                  |                  |                 | bit        |

| R-0             | R-0         | R-0                                 | R-0           | R-0              | R-0              | R-0             | R-0        |

| PPST7           | PPST6       | PPST5                               | PPST4         | PPST3            | PPST2            | PPST1           | PPST0      |

| bit 7           | 11010       | 11010                               | 11011         | 11010            | 11012            |                 | bit        |

|                 |             |                                     |               |                  |                  |                 |            |

| Legend:         |             |                                     |               |                  |                  |                 |            |

| R = Readable    | bit         | W = Writable                        | bit           | U = Unimplen     | nented bit, read | as '0'          |            |

| -n = Value at F | POR         | '1' = Bit is set                    |               | '0' = Bit is cle | ared             | x = Bit is unkr | iown       |

|                 |             |                                     | e.1           |                  |                  |                 |            |

| bit 15          | -           | ted: Read as '                      |               |                  |                  |                 |            |

| bit 14          |             | annel 14 Ping-I                     | -             | atus Flag bit    |                  |                 |            |

|                 |             | 314 register se<br>14 register sel  |               |                  |                  |                 |            |

| bit 13          |             | annel 13 Ping-F                     |               | atus Elao bit    |                  |                 |            |

|                 |             | B13 register se                     | -             |                  |                  |                 |            |

|                 |             | 13 register sel                     |               |                  |                  |                 |            |

| bit 12          | PPST12: Cha | annel 12 Ping-I                     | ong Mode Sta  | atus Flag bit    |                  |                 |            |

|                 |             | 312 register se                     |               |                  |                  |                 |            |

|                 | 0 = DMASTA  | 12 register sel                     | ected         |                  |                  |                 |            |

| bit 11          |             | annel 11 Ping-F                     | -             | atus Flag bit    |                  |                 |            |

|                 |             | 311 register se<br>11 register sel  |               |                  |                  |                 |            |

| bit 10          |             | annel 10 Ping-F                     |               | atus Elag hit    |                  |                 |            |

|                 |             | 310 register se                     | -             | atus i lag bit   |                  |                 |            |

|                 |             | 10 register sel                     |               |                  |                  |                 |            |

| bit 9           | PPST9: Char | nnel 9 Ping-Po                      | ng Mode Statu | s Flag bit       |                  |                 |            |

|                 |             | 39 register sele                    | -             | 0                |                  |                 |            |

|                 | 0 = DMASTA  | .9 register sele                    | cted          |                  |                  |                 |            |

| bit 8           |             | nnel 8 Ping-Po                      | -             | s Flag bit       |                  |                 |            |

|                 |             | 38 register sele                    |               |                  |                  |                 |            |

| bit 7           |             | N8 register sele<br>Nnel 7 Ping-Pol |               | e Elog bit       |                  |                 |            |

|                 |             | B7 register sele                    | -             | S Flag bit       |                  |                 |            |

|                 |             | A7 register sele                    |               |                  |                  |                 |            |

| bit 6           |             | nnel 6 Ping-Po                      |               | s Flag bit       |                  |                 |            |

|                 |             | 36 register sele                    |               | 0                |                  |                 |            |

|                 | 0 = DMASTA  | 6 register sele                     | cted          |                  |                  |                 |            |

| bit 5           | PPST5: Char | nnel 5 Ping-Po                      | ng Mode Statu | s Flag bit       |                  |                 |            |

|                 |             | 35 register sele                    |               |                  |                  |                 |            |

|                 |             | 5 register sele                     |               |                  |                  |                 |            |

| bit 4           |             | nnel 4 Ping-Pol                     | -             | s ⊢lag bit       |                  |                 |            |

|                 |             | 34 register sele 4 register sele    |               |                  |                  |                 |            |

| bit 3           |             | nel 3 Ping-Po                       |               | s Elan hit       |                  |                 |            |

|                 |             | -                                   | -             | s i lay bit      |                  |                 |            |

|                 | 1 = DMASTE  | 33 register sele                    | ected         |                  |                  |                 |            |

#### - ------

| R/W-0         | U-0                          | R/W-0                                 | R/W-0         | R/W-0             | R/W-0                               | R/W-0           | U-0       |

|---------------|------------------------------|---------------------------------------|---------------|-------------------|-------------------------------------|-----------------|-----------|

| ENAPLL        | —                            | SELACLK                               | AOSC          | MD<1:0>           | ASRCSEL                             | FRCSEL          |           |

| bit 15        |                              |                                       |               |                   |                                     |                 | bit       |

| R/W-0         | R/W-0                        | R/W-0                                 | U-0           | U-0               | R/W-0                               | R/W-0           | R/W-0     |

|               | APLLPOST<2:                  | 0>                                    |               |                   | Α                                   | PLLPRE<2:0>     |           |

| bit 7         |                              |                                       |               | •                 |                                     |                 | bit       |

| Legend:       |                              |                                       |               |                   |                                     |                 |           |

| R = Readabl   | e bit                        | W = Writable                          | oit           | U = Unimple       | emented bit, read                   | as '0'          |           |

| -n = Value at | POR                          | '1' = Bit is set                      |               | '0' = Bit is cl   | eared                               | x = Bit is unkn | own       |

| bit 15        |                              | -                                     |               |                   | L as USB Clock                      | Source bit      |           |

|               |                              | enabled, the US disabled, the US      |               |                   | . output<br>clock to the APL        | L               |           |

| bit 14        | Unimpleme                    | nted: Read as '                       | )'            |                   |                                     |                 |           |

| bit 13        | SELACLK:                     | Select Auxiliary                      | Clock Source  | e for Auxiliary ( | Clock Divider bit                   |                 |           |

|               |                              | PLL or oscillato                      |               |                   | for auxiliary cloc<br>clock divider | k divider       |           |

| bit 12-11     | AOSCMD<1                     | :0>: Auxiliary O                      | scillator Mod | e bits            |                                     |                 |           |

|               |                              | ternal Clock) Os                      |               | e select          |                                     |                 |           |

|               | · · ·                        | ystal) Oscillator i                   |               |                   |                                     |                 |           |

|               |                              | gh-Speed) Oscill<br>y Oscillator disa |               |                   |                                     |                 |           |

| bit 10        |                              | Select Referenc                       |               |                   | ÷                                   |                 |           |

|               |                              | Oscillator is the                     |               |                   | it.                                 |                 |           |

|               |                              | Oscillator is the                     |               |                   |                                     |                 |           |

| bit 9         |                              | elect FRC as Re                       |               |                   | PLL bit                             |                 |           |

|               |                              | he clock source<br>Oscillator or Prir |               | or is the clock s | source for APLL (                   | determined by A | ASRCSEL b |

| bit 8         | Unimpleme                    | nted: Read as '                       | )'            |                   |                                     |                 |           |

| bit 7-5       | APLLPOST                     | <2:0>: Select Pl                      | L VCO Outp    | out Divider bits  |                                     |                 |           |

|               | 111 <b>= Divide</b>          |                                       |               |                   |                                     |                 |           |

|               | 110 <b>= Divide</b>          |                                       |               |                   |                                     |                 |           |

|               | 101 = Divide                 |                                       |               |                   |                                     |                 |           |

|               | 100 = Divide<br>011 = Divide |                                       |               |                   |                                     |                 |           |

|               | 010 = Divide                 | •                                     |               |                   |                                     |                 |           |

|               | 001 <b>= Divide</b>          |                                       |               |                   |                                     |                 |           |

|               | 000 <b>= Divide</b>          | ed by 256 (defau                      | lt)           |                   |                                     |                 |           |

| bit 4-3       | Unimpleme                    | nted: Read as '                       | )'            |                   |                                     |                 |           |

| bit 2-0       | APLLPRE<                     | 2:0>: PLL Phase                       | Detector In   | put Divider bits  | 5                                   |                 |           |

|               | 111 <b>= Divide</b>          | -                                     |               |                   |                                     |                 |           |

|               | 110 <b>= Divide</b>          | •                                     |               |                   |                                     |                 |           |

|               | 101 = Divide                 | •                                     |               |                   |                                     |                 |           |

|               | 100 = Divide<br>011 = Divide |                                       |               |                   |                                     |                 |           |

|               | 010 = Divide                 |                                       |               |                   |                                     |                 |           |

|               | 001 = Divide                 |                                       |               |                   |                                     |                 |           |

|               | 000 <b>= Divide</b>          |                                       |               |                   |                                     |                 |           |

#### $\alpha$ ~ . ~ - -\_ . . . *.* . . . .

Note 1: This register resets only on a Power-on Reset (POR).

2: This register is only available on dsPIC33EPXXXMU8XX and PIC24EPXXXGU8XX devices.

#### REGISTER 11-18: RPINR17: PERIPHERAL PIN SELECT INPUT REGISTER 17 (dsPIC33EPXXXMU806/810/814 DEVICES ONLY)

| U-0             | R/W-0                        | R/W-0                                | R/W-0 | R/W-0            | R/W-0        | R/W-0            | R/W-0 |

|-----------------|------------------------------|--------------------------------------|-------|------------------|--------------|------------------|-------|

| —               |                              |                                      | I     | HOME2R<6:0>      | .(1)         |                  |       |

| bit 15          |                              |                                      |       |                  |              |                  | bit 8 |

| U-0             | R/W-0                        | R/W-0                                | R/W-0 | R/W-0            | R/W-0        | R/W-0            | R/W-0 |

| _               |                              |                                      |       | INDX2R<6:0>      | [1]          |                  |       |

| bit 7           |                              |                                      |       |                  |              |                  | bit 0 |

|                 |                              |                                      |       |                  |              |                  |       |

| Legend:         |                              |                                      |       |                  |              |                  |       |

| R = Readable    |                              | W = Writable I                       | oit   | U = Unimplen     |              |                  |       |

| -n = Value at F | POR                          | '1' = Bit is set                     |       | '0' = Bit is cle | ared         | x = Bit is unkr  | nown  |

|                 |                              | -2 for input pin<br>nput tied to RP1 |       | ,                |              |                  |       |

|                 | •                            |                                      |       |                  |              |                  |       |

|                 |                              | nput tied to CMI                     |       |                  |              |                  |       |

| h:+ 7           |                              | nput tied to Vss                     |       |                  |              |                  |       |

| bit 7           | -                            | ted: Read as '                       |       |                  | i' D         |                  | (1)   |

| bit 6-0         |                              | -2 for input pin                     |       |                  | responding R | Pn/RPIn Pin bits | (')   |

|                 | 1111111 = Ir                 | nput tied to RP1                     | 27    |                  |              |                  |       |

|                 | ·                            |                                      |       |                  |              |                  |       |

|                 |                              |                                      |       |                  |              |                  |       |

|                 | 0000001 = lr<br>0000000 = lr | nput tied to CMI                     |       |                  |              |                  |       |

Note 1: These bits are available on dsPIC33EPXXX(MC/MU)806/810/814 devices only.

# REGISTER 11-45: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | _   |       |       | RP67  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|---------|-------|-------|

| —     | —   |       |       | RP66  | 6R<5:0> |       |       |

| bit 7 |     |       |       |       |         |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP67R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP67 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP66R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP66 Output Pin bits (see Table 11-3 for peripheral function numbers) |

#### REGISTER 11-46: RPOR2: PERIPHERAL PIN SELECT OUTPUT REGISTER 2

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP69  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| —     | —   |       |       | RP68  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP69R<5:0>:** Peripheral Output Function is Assigned to RP69 Output Pin bits (see Table 11-3 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP68R<5:0>:** Peripheral Output Function is Assigned to RP68 Output Pin bits (see Table 11-3 for peripheral function numbers)

# dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

### REGISTER 16-6: STCON2: PWM SECONDARY CLOCK DIVIDER SELECT REGISTER 2

| U-0                               | U-0 | U-0              | U-0          | U-0                                     | U-0    | U-0                       | U-0   |

|-----------------------------------|-----|------------------|--------------|-----------------------------------------|--------|---------------------------|-------|

| —                                 | -   | —                | —            | —                                       |        | —                         | —     |

| bit 15                            |     |                  |              |                                         |        |                           | bit 8 |

|                                   |     |                  |              |                                         |        |                           |       |

| U-0                               | U-0 | U-0              | U-0          | U-0                                     | R/W-0  | R/W-0                     | R/W-0 |

| _                                 | —   | —                | _            | —                                       | P      | CLKDIV<2:0> <sup>(*</sup> | 1)    |

| bit 7                             |     |                  |              |                                         |        |                           | bit 0 |

|                                   |     |                  |              |                                         |        |                           |       |

| Legend:                           |     |                  |              |                                         |        |                           |       |

| R = Readable bit W = Writable bit |     | oit              | U = Unimpler | nented bit, read                        | as '0' |                           |       |

| -n = Value at P                   | OR  | '1' = Bit is set |              | '0' = Bit is cleared x = Bit is unknown |        |                           | nown  |

bit 15-3 Unimplemented: Read as '0'

bit 2-0 PCLKDIV<2:0>: PWM Input Clock Prescaler (Divider) Select bits<sup>(1)</sup>

- 111 = Reserved 110 = Divide-by-64

- 101 = Divide-by-32

- 100 = Divide-by-32

- 011 = Divide-by-8

- 010 = Divide-by-4

- 001 = Divide-by-2

- 000 = Divide-by-1, maximum PWM timing resolution (power-on default)

- **Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

# **REGISTER 16-7:** STPER: SECONDARY MASTER TIME BASE PERIOD REGISTER<sup>(1)</sup>

| R/W-1                              | R/W-1 | R/W-1          | R/W-1                                | R/W-1           | R/W-1          | R/W-1  | R/W-1 |

|------------------------------------|-------|----------------|--------------------------------------|-----------------|----------------|--------|-------|

|                                    |       |                | STPE                                 | R<15:8>         |                |        |       |

| bit 15                             |       |                |                                      |                 |                |        | bit 8 |

| David                              |       | <b>D</b> 444 4 |                                      | <b>D</b> 444 4  | <b>D</b> 444 A | 5444.0 | DAVA  |

| R/W-1                              | R/W-1 | R/W-1          | R/W-1                                | R/W-1           | R/W-0          | R/W-0  | R/W-0 |

|                                    |       |                | STPE                                 | R<7:0>          |                |        |       |

| bit 7                              |       |                |                                      |                 |                |        | bit 0 |

|                                    |       |                |                                      |                 |                |        |       |

| Legend:                            |       |                |                                      |                 |                |        |       |

| R = Readable bit W = Writable bit  |       | bit            | U = Unimpler                         | mented bit, rea | d as '0'       |        |       |

| -n = Value at POR '1' = Bit is set |       |                | '0' = Bit is cleared x = Bit is unkr |                 | nown           |        |       |

bit 15-0 STPER<15:0>: Secondary Master Time Base (PMTMR) Period Value bits

# 23.2 ADC Helpful Tips

- 1. The SMPIx control bits in the ADxCON2 registers:

- a) Determine when the ADC interrupt flag is set and an interrupt is generated, if enabled.

- b) When the CSCNA bit in the ADxCON2 register is set to '1', this determines when the ADC analog scan channel list, defined in the AD1CSSL/AD1CSSH registers, starts over from the beginning.

- c) When the DMA peripheral is not used (ADDMAEN = 0), this determines when the ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0.

- d) When the DMA peripheral is used (ADDMAEN = 1), this determines when the DMA Address Pointer is incremented after a sample/conversion operation. ADC1BUF0 is the only ADC buffer used in this mode. The ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0. The DMA address is incremented after completion of every 32nd sample/conversion operation. Conversion results are stored in the ADC1BUF0 register for transfer to RAM using DMA.

- 2. When the DMA module is disabled (ADDMAEN = 0), the ADC has 16 result buffers. ADC conversion results are stored sequentially in ADC1BUF0-ADC1BUFF, regardless of which analog inputs are being used subject to the SMPIx bits and the condition described in 1c) above. There is no relationship between the ANx input being measured and which ADC buffer (ADC1BUF0-ADC1BUFF) that the conversion results will be placed in.

- 3. When the DMA module is disabled (ADDMAEN = 1), the ADC module has only 1 ADC result buffer (i.e., ADC1BUF0) per ADC peripheral and the ADC conversion result must be read, either by the CPU or DMA controller, before the next ADC conversion is complete to avoid overwriting the previous value.

- 4. The DONE bit (ADxCON1<0>) is only cleared at the start of each conversion and is set at the completion of the conversion, but remains set indefinitely, even through the next sample phase until the next conversion begins. If application code is monitoring the DONE bit in any kind of software loop, the user must consider this behavior because the CPU code execution is faster than the ADC. As a result, in Manual Sample mode, particularly where the user's code is setting the SAMP bit (ADxCON1<1>), the DONE bit should also be cleared by the user application just before setting the SAMP bit.

# 23.3 ADC Resources

Many useful resources related to Analog-to-Digital conversion are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en554310                                        |

#### 23.3.1 KEY RESOURCES

- Section 16. "Analog-to-Digital Converter (ADC)" (DS70621) in the "dsPIC33E/PIC24E Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All related *"dsPIC33E/PIC24E Family Reference Manual"* Sections

- Development Tools

## REGISTER 23-2: AD1CON2: ADC1 CONTROL REGISTER 2 (CONTINUED)

- bit 1 BUFM: Buffer Fill Mode Select bit

- 1 = Starts filling the first half of the buffer on the first interrupt and the second half of the buffer on the next interrupt

- 0 = Always starts filling the buffer from the Start address.

#### bit 0 ALTS: Alternate Input Sample Mode Select bit

- 1 = Uses channel input selects for Sample A on the first sample and Sample B on the next sample

- 0 = Always uses channel input selects for Sample A

| U-0            | U-0                                                                                                         | U-0                                                                                            | U-0                                                                                  | R-0                         | R-0              | R-0             | R-0          |

|----------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------|------------------|-----------------|--------------|

| r              | r                                                                                                           | r                                                                                              | r                                                                                    | SLOT<3:0>                   |                  |                 |              |

| bit 15         |                                                                                                             |                                                                                                |                                                                                      |                             |                  |                 | bit          |

|                |                                                                                                             |                                                                                                |                                                                                      | <b>.</b>                    | <b>D</b> 0       | <b>D</b> 0      |              |

| U-0<br>r       | U-0                                                                                                         | U-0                                                                                            | U-0<br>r                                                                             | R-0<br>ROV                  | R-0<br>RFUL      | R-0<br>TUNF     | R-0<br>TMPTY |

| bit 7          |                                                                                                             | I                                                                                              | I                                                                                    | ROV                         | RFUL             | TONE            | bit          |

|                |                                                                                                             |                                                                                                |                                                                                      |                             |                  |                 |              |

| Legend:        |                                                                                                             | r = Reserved                                                                                   | bit                                                                                  |                             |                  |                 |              |

| R = Readab     | le bit                                                                                                      | W = Writable I                                                                                 | oit                                                                                  | U = Unimplen                | nented bit, read | l as '0'        |              |

| -n = Value a   | t POR                                                                                                       | '1' = Bit is set                                                                               |                                                                                      | '0' = Bit is cle            | ared             | x = Bit is unki | nown         |

|                |                                                                                                             |                                                                                                |                                                                                      |                             |                  |                 |              |

| bit 15-12      | Reserved: Re                                                                                                |                                                                                                |                                                                                      |                             |                  |                 |              |

| bit 11-8       |                                                                                                             | DCI Slot Status                                                                                |                                                                                      |                             |                  |                 |              |

|                |                                                                                                             | 5 is currently a                                                                               | ctive                                                                                |                             |                  |                 |              |

|                | •                                                                                                           |                                                                                                |                                                                                      |                             |                  |                 |              |

|                | •                                                                                                           |                                                                                                |                                                                                      |                             |                  |                 |              |

|                | 0010 <b>= Slot 2</b>                                                                                        | is currently ac                                                                                | tive                                                                                 |                             |                  |                 |              |

|                | 0001 <b>= Slot 1</b>                                                                                        | is currently ac                                                                                | tive                                                                                 |                             |                  |                 |              |

|                |                                                                                                             | is currently ac                                                                                | tive                                                                                 |                             |                  |                 |              |

| bit 7-4        | Reserved: Re                                                                                                |                                                                                                |                                                                                      |                             |                  |                 |              |

| bit 3          |                                                                                                             | e Overflow Stat                                                                                |                                                                                      |                             |                  |                 |              |

|                |                                                                                                             | overflow has o                                                                                 |                                                                                      | t least one Rec             | eive register    |                 |              |

|                |                                                                                                             |                                                                                                |                                                                                      |                             |                  |                 |              |

| bit 2          | <b>RFUL:</b> Receive Buffer Full Status bit<br>1 = New data is available in the Receive registers           |                                                                                                |                                                                                      |                             |                  |                 |              |

| bit 2          |                                                                                                             |                                                                                                | the Receive r                                                                        | egisters                    |                  |                 |              |

| bit 2          | 1 = New data                                                                                                |                                                                                                |                                                                                      | egisters                    |                  |                 |              |

|                | 1 = New data<br>0 = The Rece<br><b>TUNF:</b> Transi                                                         | is available in t<br>ive registers ha<br>nit Buffer Unde                                       | ave old data<br>rflow Status I                                                       | oit                         |                  |                 |              |

|                | 1 = New data<br>0 = The Rece<br><b>TUNF:</b> Transr<br>1 = A transmi                                        | is available in t<br>ive registers ha<br>nit Buffer Unde<br>t underflow has                    | ave old data<br>rflow Status I<br>s occurred for                                     | oit<br>∘at least one Tr     | ansmit register  |                 |              |