Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART, USB OTG            |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 83                                                                               |

| Program Memory Size        | 256KB (85.5K x 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 12K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 32x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256mu810-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.2.5 X AND Y DATA SPACES

The dsPIC33EPXXX(GP/MC/MU)806/810/814 core has two data spaces, X and Y. These data spaces can be considered either separate (for some DSP instructions), or as one unified linear address range (for MCU instructions). The data spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms such as Finite Impulse Response (FIR) filtering and Fast Fourier Transform (FFT).

The PIC24EPXXX(GP/GU)806/810/814 devices do not have a Y data space and a Y AGU. For these devices, the entire data space is treated as X data space.

The X data space is used by all instructions and supports all addressing modes. X data space has separate read and write data buses. The X read data bus is the read data path for all instructions that view data space as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class).

The Y data space is used in concert with the X data space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths.

Both the X and Y data spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to X data space. Modulo Addressing and Bit-Reversed Addressing are not present in PIC24EPXXX(GP/ GU)806/810/814 devices.

All data memory writes, including in DSP instructions, view data space as combined X and Y address space. The boundary between the X and Y data spaces is device-dependent and is not user-programmable.

#### 4.2.6 DMA RAM

Each dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814 device contains 4 Kbytes of dual ported DMA RAM located at the end of Y data RAM and is part of Y data space. Memory locations in the DMA RAM space are accessible simultaneously by the CPU and the DMA Controller module. DMA RAM is utilized by the DMA controller to store data to be transferred to various peripherals using DMA, as well as data transferred from various peripherals using DMA. The DMA RAM can be accessed by the DMA controller without having to steal cycles from the CPU. When the CPU and the DMA controller attempt to concurrently write to the same DMA RAM location, the hardware ensures that the CPU is given precedence in accessing the DMA RAM location. Therefore, the DMA RAM provides a reliable means of transferring DMA data without ever having to stall the CPU.

| Note 1: | DMA    | RAM     | can     | be   | used     | for  | general  |

|---------|--------|---------|---------|------|----------|------|----------|

|         | purpo  | se data | a stor  | age  | if the D | DMA  | function |

|         | is not | require | ed in a | an a | pplicat  | ion. |          |

2: On PIC24EPXXX(GP/GU)806/810/814 devices, DMA RAM is located at the end of X data RAM and is part of X data space.

# 4.3 Program Memory Resources

Many useful resources related to the Program Memory are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en554310                                        |

#### 4.3.1 KEY RESOURCES

- Section 4. "Program Memory" (DS70612) in the "dsPIC33E/PIC24E Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related *"dsPIC33E/PIC24E Family Reference Manual"* Sections

- Development Tools

# 4.4 Special Function Register Maps

Table 4-1 through Table 4-72 provide mapping tables for all Special Function Registers (SFRs).

| IABLE        | 4-5.  |        |        |            | NULLER  | V KEGIS |        |                 | USFIC | 3357777  |         | DEVICE      | S UNL I |            | NUED)  |             |          |               |

|--------------|-------|--------|--------|------------|---------|---------|--------|-----------------|-------|----------|---------|-------------|---------|------------|--------|-------------|----------|---------------|

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12  | Bit 11  | Bit 10 | Bit 9           | Bit 8 | Bit 7    | Bit 6   | Bit 5       | Bit 4   | Bit 3      | Bit 2  | Bit 1       | Bit 0    | All<br>Resets |

| IPC16        | 0860  | _      |        | CRCIP<2:0  | >       | _       |        | U2EIP<2:0>      |       | _        |         | U1EIP<2:0>  |         | —          | —      | —           | _        | 4440          |

| IPC17        | 0862  | _      |        | C2TXIP<2:0 | )>      | _       |        | C1TXIP<2:0      | >     | _        |         | DMA7IP<2:0  | >       | _          | [      | DMA6IP<2:0> | <b>`</b> | 4444          |

| IPC18        | 0864  | _      |        | QEI2IP<2:0 | >       | _       | _      | _               | _     | _        | I       | PSESMIP<2:0 | )>      | -          | _      | _           | _        | 4040          |

| IPC20        | 0868  | _      |        | U3TXIP<2:0 | )>      | _       |        | U3RXIP<2:0      | >     | —        |         | U3EIP<2:0>  |         | —          | _      | _           | _        | 4440          |

| IPC21        | 086A  | _      |        | U4EIP<2:0  | >       | _       |        | USB1IP<2:0      | >     | —        | _       | —           | _       | —          | _      | _           | _        | 4400          |

| IPC22        | 086C  | _      |        | SPI3IP<2:0 | >       | _       | :      | SPI3EIP<2:0     | >     | —        |         | U4TXIP<2:0> | >       | —          | l      | J4RXIP<2:0> | •        | 4444          |

| IPC23        | 086E  | _      | I      | PWM2IP<2:( | 0>      | _       | F      | PWM1IP<2:0      | >     | —        |         | IC9IP<2:0>  |         | —          |        | OC9IP<2:0>  |          | 4444          |

| IPC24        | 0870  | _      | _      | _          | _       | _       | _      | _               | _     | —        |         | PWM4IP<2:0  | >       | —          | F      | WM3IP<2:0>  | >        | 0044          |

| IPC29        | 087A  | _      |        | DMA9IP<2:0 | )>      | _       |        | DMA8IP<2:0      | >     | _        | _       | _           | —       | _          | _      | _           |          | 4400          |

| IPC30        | 087C  | _      |        | SPI4IP<2:0 | >       | _       | :      | SPI4EIP<2:0     | >     | _        |         | DMA11IP<2:0 | >       | _          | D      | MA10IP<2:0  | >        | 4444          |

| IPC31        | 087E  | _      |        | IC11IP<2:0 | >       | _       |        | OC11IP<2:0      | >     | _        |         | IC10IP<2:0> |         | _          | (      | OC10IP<2:0> |          | 4444          |

| IPC32        | 0880  | _      | [      | DMA13IP<2: | 0>      | _       | [      | )<br>MA12IP<2:( | )>    | _        |         | IC12IP<2:0> |         | _          | (      | OC12IP<2:0> |          | 4444          |

| IPC33        | 0882  | _      |        | IC13IP<2:0 | >       | _       |        | OC13IP<2:0      | >     | _        | _       | _           | —       | _          | D      | MA14IP<2:0  | >        | 4404          |

| IPC34        | 0884  | _      |        | IC15IP<2:0 | >       | _       |        | OC15IP<2:0      | >     | _        |         | IC14IP<2:0> |         | —          | (      | OC14IP<2:0> |          | 4444          |

| IPC35        | 0886  | _      | _      | _          | —       | _       |        | ICDIP<2:0>      |       | _        |         | IC16IP<2:0> |         | —          | (      | OC16IP<2:0> |          | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     | COVAERR | COVBERR | OVATE  | OVBTE           | COVTE | SFTACERR | DIV0ERR | DMACERR     | MATHERR | ADDRERR    | STKERR | OSCFAIL     |          | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     |         | _       | _      |                 | -     | _        |         | _           | INT4EP  | INT3EP     | INT2EP | INT1EP      | INT0EP   | 8000          |

| INTCON3      | 08C4  | _      | _      | _          |         | _       | _      |                 | -     | _        | UAE     | DAE         | DOOVR   | —          | —      | —           | _        | 0000          |

| INTCON4      | 08C6  | _      | _      | _          | _       | _       | _      | _               | _     | _        | —       | _           | —       | _          | _      | _           | SGHT     | 0000          |

| INTTREG      | 08C8  | _      | _      | _          | _       | _       |        | ILR             | <3:0> |          |         |             | VE      | ECNUM<7:0> |        |             |          | 0000          |

|              |       |        |        |            |         |         |        |                 |       |          |         |             |         |            |        |             |          |               |

# TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXMU806 DEVICES ONLY (CONTINUED)

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10  | Bit 9          | Bit 8   | Bit 7  | Bit 6  | Bit 5       | Bit 4   | Bit 3         | Bit 2         | Bit 1        | Bit 0         | All<br>Resets |

|--------------|-------|--------|--------|------------|--------|--------|---------|----------------|---------|--------|--------|-------------|---------|---------------|---------------|--------------|---------------|---------------|

| IFS0         | 0800  | NVMIF  | DMA1IF | AD1IF      | U1TXIF | U1RXIF | SPI1IF  | SPI1EIF        | T3IF    | T2IF   | OC2IF  | IC2IF       | DMA0IF  | T1IF          | OC1IF         | IC1IF        | <b>INT0IF</b> | 0000          |

| IFS1         | 0802  | U2TXIF | U2RXIF | INT2IF     | T5IF   | T4IF   | OC4IF   | OC3IF          | DMA2IF  | IC8IF  | IC7IF  | AD2IF       | INT1IF  | CNIF          | CMIF          | MI2C1IF      | SI2C1IF       | 0000          |

| IFS2         | 0804  | T6IF   | DMA4IF | PMPIF      | OC8IF  | OC7IF  | OC6IF   | OC5IF          | IC6IF   | IC5IF  | IC4IF  | IC3IF       | DMA3IF  | C1IF          | C1RXIF        | SPI2IF       | SPI2EIF       | 0000          |

| IFS3         | 0806  | _      | RTCIF  | DMA5IF     | DCIIF  | DCIEIF | _       |                | C2IF    | C2RXIF | INT4IF | INT3IF      | T9IF    | T8IF          | MI2C2IF       | SI2C2IF      | T7IF          | 0000          |

| IFS4         | 0808  | _      |        | —          | _      |        | _       |                | _       | C2TXIF | C1TXIF | DMA7IF      | DMA6IF  | CRCIF         | U2EIF         | U1EIF        | —             | 0000          |

| IFS5         | 080A  | —      | _      | IC9IF      | OC9IF  | SPI3IF | SPI3EIF | U4TXIF         | U4RXIF  | U4EIF  | USB1IF | —           | —       | <b>U3TXIF</b> | <b>U3RXIF</b> | <b>U3EIF</b> | —             | 0000          |

| IFS7         | 080E  | IC11IF | OC11IF | IC10IF     | OC10IF | SPI4IF | SPI4EIF | DMA11IF        | DMA10IF | DMA9IF | DMA8IF | —           |         | —             | —             |              | —             | 0000          |

| IFS8         | 0810  | _      | ICDIF  | IC16IF     | OC16IF | IC15IF | OC15IF  | IC14IF         | OC14IF  | IC13IF | OC13IF | —           | DMA14IF | DMA13IF       | DMA12IF       | IC12IF       | OC12IF        | 0000          |

| IEC0         | 0820  | NVMIE  | DMA1IE | AD1IE      | U1TXIE | U1RXIE | SPI1IE  | SPI1EIE        | T3IE    | T2IE   | OC2IE  | IC2IE       | DMA0IE  | T1IE          | OC1IE         | IC1IE        | INT0IE        | 0000          |

| IEC1         | 0822  | U2TXIE | U2RXIE | INT2IE     | T5IE   | T4IE   | OC4IE   | OC3IE          | DMA2IE  | IC8IE  | IC7IE  | AD2IE       | INT1IE  | CNIE          | CMIE          | MI2C1IE      | SI2C1IE       | 0000          |

| IEC2         | 0824  | T6IE   | DMA4IE | PMPIE      | OC8IE  | OC7IE  | OC6IE   | OC5IE          | IC6IE   | IC5IE  | IC4IE  | IC3IE       | DMA3IE  | C1IE          | C1RXIE        | SPI2IE       | SPI2EIE       | 0000          |

| IEC3         | 0826  | _      | RTCIE  | DMA5IE     | DCIIE  | DCIEIE | _       |                | C2IE    | C2RXIE | INT4IE | INT3IE      | T9IE    | T8IE          | MI2C2IE       | SI2C2IE      | T7IE          | 0000          |

| IEC4         | 0828  | _      |        | —          | —      |        | _       |                | _       | C2TXIE | C1TXIE | DMA7IE      | DMA6IE  | CRCIE         | U2EIE         | U1EIE        | —             | 0000          |

| IEC5         | 082A  |        |        | IC9IE      | OC9IE  | SPI3IE | SPI3EIE | U4TXIE         | U4RXIE  | U4EIE  | USB1IE | —           | -       | <b>U3TXIE</b> | <b>U3RXIE</b> | U3EIE        | _             | 0000          |

| IEC7         | 082E  | IC11IE | OC11IE | IC10IE     | OC10IE | SPI4IE | SPI4EIE | DMA11IE        | DMA10IE | DMA9IE | DMA8IE | _           | _       | _             | _             | _            | _             | 0000          |

| IEC8         | 0830  | -      | ICDIE  | IC16IE     | OC16IE | IC15IE | OC15IE  | IC14IE         | OC14IE  | IC13IE | OC13IE | _           | DMA14IE | DMA13IE       | DMA12IE       | IC12IE       | OC12IE        | 0000          |

| IPC0         | 0840  | -      |        | T1IP<2:0>  | •      | _      |         | OC1IP<2:0      | >       | _      |        | IC1IP<2:0>  |         | _             |               | NT0IP<2:0>   |               | 4444          |

| IPC1         | 0842  | _      |        | T2IP<2:0>  | •      |        |         | OC2IP<2:0      | >       | —      |        | IC2IP<2:0>  |         | —             | C             | 0MA0IP<2:0   | >             | 4444          |

| IPC2         | 0844  | -      | l      | U1RXIP<2:  | )>     | _      |         | SPI1IP<2:0     | >       | _      |        | SPI1EIP<2:0 | >       | _             |               | T3IP<2:0>    |               | 4444          |

| IPC3         | 0846  | -      |        | NVMIP<2:0  | >      | _      | [       | DMA1IP<2:0     | )>      | _      |        | AD1IP<2:0>  | >       | _             | ι             | J1TXIP<2:0   | >             | 4444          |

| IPC4         | 0848  | -      |        | CNIP<2:0   | >      | _      |         | CMIP<2:0>      | •       | _      |        | MI2C1IP<2:0 | )>      | _             | 5             | SI2C1IP<2:0  | >             | 4444          |

| IPC5         | 084A  | -      |        | IC8IP<2:0  | >      | _      |         | IC7IP<2:0>     | •       | _      |        | AD2IP<2:0>  | >       | _             |               | NT1IP<2:0>   |               | 4444          |

| IPC6         | 084C  | -      |        | T4IP<2:0>  | •      | _      |         | OC4IP<2:0      | >       | _      |        | OC3IP<2:0>  | >       | _             | C             | 0MA2IP<2:0   | >             | 4444          |

| IPC7         | 084E  | _      | -      | U2TXIP<2:( | )>     |        | ι       | J2RXIP<2:(     | )>      | —      |        | INT2IP<2:0  | >       | —             |               | T5IP<2:0>    |               | 4444          |

| IPC8         | 0850  | -      |        | C1IP<2:0>  | •      | _      | (       | C1RXIP<2:0     | )>      | _      |        | SPI2IP<2:0  | >       | _             | S             | PI2EIP<2:0   | >             | 4444          |

| IPC9         | 0852  | -      |        | IC5IP<2:03 | >      | _      |         | IC4IP<2:0>     | •       | _      |        | IC3IP<2:0>  |         | _             | C             | 0MA3IP<2:0   | >             | 4444          |

| IPC10        | 0854  | _      |        | OC7IP<2:0  | >      |        |         | OC6IP<2:0      | >       | —      |        | OC5IP<2:0>  | >       | —             |               | IC6IP<2:0>   |               | 4444          |

| IPC11        | 0856  |        |        | T6IP<2:0>  |        |        | 0       | )<br>MA4IP<2:( | )>      | —      |        | PMPIP<2:0   | >       | —             |               | OC8IP<2:0>   |               | 4444          |

| IPC12        | 0858  | -      |        | T8IP<2:0>  | •      | _      | Ν       | /II2C2IP<2:0   | )>      | _      |        | SI2C2IP<2:0 | >       | _             |               | T7IP<2:0>    |               | 4444          |

| IPC13        | 085A  |        | (      | C2RXIP<2:  | )>     | _      |         | INT4IP<2:0     | >       | _      |        | INT3IP<2:0  | >       | —             |               | T9IP<2:0>    |               | 4444          |

| IPC14        | 085C  |        |        | DCIEIP<2:( | )>     |        | —       | —              | _       | _      | _      | _           | _       | —             |               | C2IP<2:0>    |               | 4004          |

| IPC15        | 085E  | _      | _      | —          | _      | _      |         | RTCIP<2:0      | >       | _      |        | DMA5IP<2:0  | >       | _             |               | DCIIP<2:0>   |               | 0444          |

| IPC16        | 0860  | —      |        | CRCIP<2:0  | >      | _      |         | U2EIP<2:0      | >       | _      |        | U1EIP<2:0>  | >       | _             | _             | —            |               | 4440          |

| IPC17        | 0862  | _      | (      | C2TXIP<2:0 | )>     | _      | (       | C1TXIP<2:0     | >       | _      |        | DMA7IP<2:0  | >       | _             | 0             | )MA6IP<2:0   | >             | 4444          |

dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-25: ADC1 and ADC2 REGISTER MAP (CONTINUED)

| File Name | Addr. | Bit 15 | Bit 14                                                                                                       | Bit 13 | Bit 12  | Bit 11 | Bit 10   | Bit 9   | Bit 8       | Bit 7    | Bit 6     | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1    | Bit 0   | All<br>Resets |

|-----------|-------|--------|--------------------------------------------------------------------------------------------------------------|--------|---------|--------|----------|---------|-------------|----------|-----------|-------|-------|--------|--------|----------|---------|---------------|

| ADC2BUF9  | 0352  |        |                                                                                                              |        |         |        |          |         | ADCx Data E | Buffer 9 |           |       |       |        |        |          |         | XXXX          |

| ADC2BUFA  | 0354  |        |                                                                                                              |        |         |        |          |         | ADCx Data B | uffer 10 |           |       |       |        |        |          |         | XXXX          |

| ADC2BUFB  | 0356  |        |                                                                                                              |        |         |        |          |         | ADCx Data B | uffer 11 |           |       |       |        |        |          |         | XXXX          |

| ADC2BUFC  | 0358  |        |                                                                                                              |        |         |        |          |         | ADCx Data B | uffer 12 |           |       |       |        |        |          |         | XXXX          |

| ADC2BUFD  | 035A  |        |                                                                                                              |        |         |        |          |         | ADCx Data B | uffer 13 |           |       |       |        |        |          |         | XXXX          |

| ADC2BUFE  | 035C  |        |                                                                                                              |        |         |        |          |         | ADCx Data B | uffer 14 |           |       |       |        |        |          |         | XXXX          |

| ADC2BUFF  | 035E  |        |                                                                                                              |        |         |        |          |         | ADCx Data B | uffer 15 |           |       |       |        |        |          |         | XXXX          |

| AD2CON1   | 0360  | ADON   | _                                                                                                            | ADSIDL | ADDMABM | —      |          | FOR     | M<1:0>      | 5        | SSRC<2:0> | •     | SSRCG | SIMSAM | ASAM   | SAMP     | DONE    | 0000          |

| AD2CON2   | 0362  | Ň      | VCFG<2:0                                                                                                     | >      | —       | —      | CSCNA    | CHP     | S<1:0>      | BUFS     |           |       | SMP   | l<3:0> |        | BUFM     | ALTS    | 0000          |

| AD2CON3   | 0364  | ADRC   |                                                                                                              |        |         |        | SAMC<4:0 | >       |             |          |           |       | ADCS  | S<7:0> |        |          |         | 0000          |

| AD2CHS123 | 0366  | —      |                                                                                                              | _      | _       | _      | CH123N   | NB<1:0> | CH123SB     |          | _         | _     | _     | _      | CH123N | IA<1:0>  | CH123SA | 0000          |

| AD2CHS0   | 0368  | CH0NB  | DNB         -         -         CH0SB<4:0>         CH0NA         -         -         CH0SA<4:0>         0000 |        |         |        |          |         |             | 0000     |           |       |       |        |        |          |         |               |

| AD2CSSL   | 0270  | CSS15  | CSS14                                                                                                        | CSS13  | CSS12   | CSS11  | CSS10    | CSS9    | CSS8        | CSS7     | CSS6      | CSS5  | CSS4  | CSS3   | CSS2   | CSS1     | CSS0    | 0000          |

| AD2CON4   | 0272  | —      | _                                                                                                            |        | _       | —      |          | —       | ADDMAEN     | _        |           |       |       | —      | C      | MABL<2:0 | )>      | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These bits are not available on dsPIC33EP256MU806 devices.

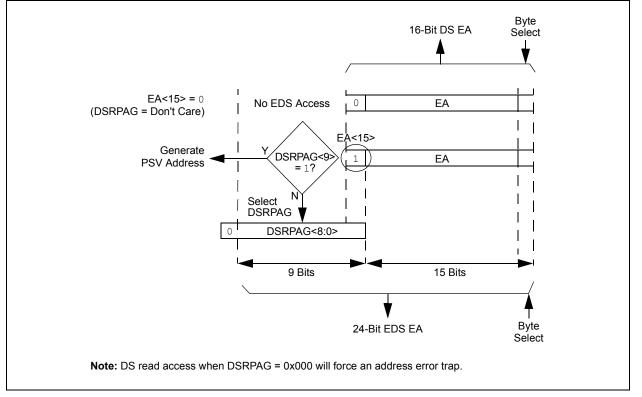

#### 4.4.1 PAGED MEMORY SCHEME

The dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814 architecture extends the available data space through a paging scheme, which allows the available data space to be accessed using MOV instructions in a linear fashion for pre- and post-modified Effective Addresses (EA). The upper half of Base Data Space address is used in conjunction with the Data Space Page registers, the 10-Bit Read Page register (DSRPAG) or the 9-Bit Write Page register (DSWPAG), to form an Extended Data Space (EDS) address or Program Space Visibility (PSV) address. The Data Space Page registers are located in the SFR space.

Construction of the EDS address is shown in Figure 4-1. When DSRPAG<9> = 0 and the base address bit, EA<15> = 1, DSRPAG<8:0> is concatenated onto EA<14:0> to form the 24-bit EDS read address. Similarly, when the base address bit, EA<15> = 1, DSWPAG<8:0> is concatenated onto EA<14:0> to form the 24-bit EDS write address.

#### EXAMPLE 4-1: EXTENDED DATA SPACE (EDS) READ ADDRESS GENERATION

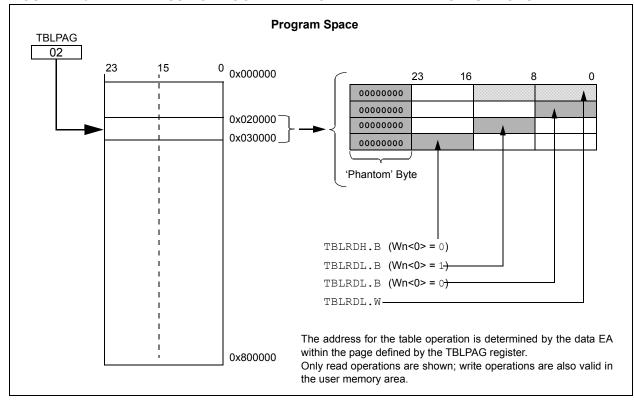

#### 4.8.1 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the Program Space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a Program Space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from Program Space. Both function as either byte or word operations.

- TBLRDL (Table Read Low):

- In Word mode, this instruction maps the lower word of the Program Space location (P<15:0>) to a data address (D<15:0>).

- In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.

- TBLRDH (Table Read High):

- In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. The 'phantom' byte (D<15:8>), is always '0'.

- In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address, in the TBLRDL instruction. The data is always '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a Program Space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user application and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

#### FIGURE 4-13: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

# REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

| bit 4 | MATHERR: Math Error Status bit               |

|-------|----------------------------------------------|

|       | 1 = Math error trap has occurred             |

|       | 0 = Math error trap has not occurred         |

|       |                                              |

| bit 3 | ADDRERR: Address Error Trap Status bit       |

|       | 1 = Address error trap has occurred          |

|       | 0 = Address error trap has not occurred      |

| bit 2 | STKERR: Stack Error Trap Status bit          |

|       | 1 = Stack error trap has occurred            |

|       | 0 = Stack error trap has not occurred        |

| bit 1 | OSCFAIL: Oscillator Failure Trap Status bit  |

|       | 1 = Oscillator failure trap has occurred     |

|       | 0 = Oscillator failure trap has not occurred |

| bit 0 | Unimplemented: Read as '0'                   |

Note 1: This bit is available on dsPIC33EPXXX(GP/MC/MU)806/810/814 devices only.

| R/W-0<br>CHEN<br>bit 15 | R/W-0<br>SIZE                                                                                                         | R/W-0<br>DIR                      | R/W-0           | R/W-0             | U-0              | U-0              | U-0          |  |  |  |  |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------|-------------------|------------------|------------------|--------------|--|--|--|--|

| -                       | SIZE                                                                                                                  |                                   |                 |                   |                  |                  |              |  |  |  |  |

| bit 15                  |                                                                                                                       | DIR                               | HALF            | NULLW             |                  |                  | _            |  |  |  |  |

|                         |                                                                                                                       |                                   |                 |                   |                  |                  | bit 8        |  |  |  |  |

| U-0                     | U-0                                                                                                                   | R/W-0                             | R/W-0           | U-0               | U-0              | R/W-0            | R/W-0        |  |  |  |  |

| _                       | _                                                                                                                     | AMODE                             | E<1:0>          | —                 | _                | MODE             | <1:0>        |  |  |  |  |

| bit 7                   |                                                                                                                       |                                   |                 |                   |                  |                  | bit C        |  |  |  |  |

|                         |                                                                                                                       |                                   |                 |                   |                  |                  |              |  |  |  |  |

| Legend:                 | .:.                                                                                                                   |                                   | L :4            |                   | <b></b>          |                  |              |  |  |  |  |

| R = Readable I          |                                                                                                                       | W = Writable                      | DIT             | -                 | nented bit, read |                  |              |  |  |  |  |

| -n = Value at P         | OR                                                                                                                    | '1' = Bit is set                  |                 | '0' = Bit is clea | ared             | x = Bit is unkn  | own          |  |  |  |  |

| bit 15                  | CHEN: Chanr                                                                                                           | nel Enable bit                    |                 |                   |                  |                  |              |  |  |  |  |

|                         | 1 = Channel                                                                                                           | is enabled                        |                 |                   |                  |                  |              |  |  |  |  |

|                         | 0 = Channel                                                                                                           | is disabled                       |                 |                   |                  |                  |              |  |  |  |  |

| bit 14                  | SIZE: Data Tr                                                                                                         | ansfer Size bit                   |                 |                   |                  |                  |              |  |  |  |  |

|                         | 1 = Byte                                                                                                              |                                   |                 |                   |                  |                  |              |  |  |  |  |

|                         | 0 = Word                                                                                                              |                                   |                 |                   |                  |                  |              |  |  |  |  |

| bit 13                  | DIR: Transfer                                                                                                         | Direction bit (s                  | ource/destina   | ation bus select  | )                |                  |              |  |  |  |  |

|                         | 1 = Reads fro                                                                                                         | om DPSRAM (o                      | or RAM) addr    | ess, writes to p  | eripheral addre  | SS               |              |  |  |  |  |

|                         | 0 = Reads fro                                                                                                         | om peripheral a                   | ddress, write   | s to DPSRAM (     | or RAM) addre    | SS               |              |  |  |  |  |

| bit 12                  | HALF: Block                                                                                                           | Transfer Interru                  | upt Select bit  |                   |                  |                  |              |  |  |  |  |

|                         | 1 = Initiates in                                                                                                      | nterrupt when h                   | half of the dat | a has been mo     | ved              |                  |              |  |  |  |  |

|                         | 0 = Initiates in                                                                                                      | nterrupt when a                   | all of the data | has been move     | ed               |                  |              |  |  |  |  |

| bit 11                  |                                                                                                                       | Data Periphera                    |                 |                   |                  |                  |              |  |  |  |  |

|                         |                                                                                                                       |                                   | eral in additio | on to DPSRAM (    | (or RAM) write   | (DIR bit must al | so be clear) |  |  |  |  |

|                         | 0 = Normal o                                                                                                          | -                                 |                 |                   |                  |                  |              |  |  |  |  |

| bit 10-6                | •                                                                                                                     | ted: Read as '                    |                 |                   |                  |                  |              |  |  |  |  |

| bit 5-4                 | AMODE<1:0>                                                                                                            | : DMA Channe                      | el Addressing   | Mode Select b     | its              |                  |              |  |  |  |  |

|                         | 11 = Reserve                                                                                                          |                                   |                 |                   |                  |                  |              |  |  |  |  |

|                         |                                                                                                                       | al Indirect Add                   | 0               |                   |                  |                  |              |  |  |  |  |

|                         | •                                                                                                                     | Indirect without                  |                 |                   |                  |                  |              |  |  |  |  |

| bit 3-2                 | -                                                                                                                     | Indirect with P<br>ted: Read as ' |                 | it mode           |                  |                  |              |  |  |  |  |

| bit 1-0                 | -                                                                                                                     |                                   |                 | odo Soloot hito   |                  |                  |              |  |  |  |  |

| DIL 1-0                 |                                                                                                                       |                                   |                 | ode Select bits   |                  | the each DNAA h  | (ffor)       |  |  |  |  |

|                         |                                                                                                                       |                                   |                 |                   | k transfer from  | /to each DMA b   | uner)        |  |  |  |  |

|                         | <ul> <li>10 = Continuous, Ping-Pong modes are enabled</li> <li>01 = One-Shot, Ping-Pong modes are disabled</li> </ul> |                                   |                 |                   |                  |                  |              |  |  |  |  |

|                         | 00 = Continuous, Ping-Pong modes are disabled                                                                         |                                   |                 |                   |                  |                  |              |  |  |  |  |

# REGISTER 8-1: DMAXCON: DMA CHANNEL X CONTROL REGISTER

#### REGISTER 8-9: DSADRH: MOST RECENT DMA DATA SPACE HIGH ADDRESS REGISTER

| U-0             | U-0 | U-0              | U-0   | U-0              | U-0              | U-0             | U-0   |

|-----------------|-----|------------------|-------|------------------|------------------|-----------------|-------|

| —               | _   | -                | _     | —                | —                | —               | —     |

| bit 15          |     |                  |       |                  |                  |                 | bit 8 |

|                 |     |                  |       |                  |                  |                 |       |

| R-0             | R-0 | R-0              | R-0   | R-0              | R-0              | R-0             | R-0   |

|                 |     |                  | DSADF | R<23:16>         |                  |                 |       |

| bit 7           |     |                  |       |                  |                  |                 | bit 0 |

|                 |     |                  |       |                  |                  |                 |       |

| Legend:         |     |                  |       |                  |                  |                 |       |

| R = Readable    | bit | W = Writable I   | oit   | U = Unimplei     | mented bit, read | d as '0'        |       |

| -n = Value at P | POR | '1' = Bit is set |       | '0' = Bit is cle | eared            | x = Bit is unkr | nown  |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 DSADR<23:16>: Most Recent DMA Address Accessed by DMA bits

#### REGISTER 8-10: DSADRL: MOST RECENT DMA DATA SPACE LOW ADDRESS REGISTER

| R-0             | R-0 | R-0              | R-0  | R-0                 | R-0            | R-0             | R-0   |

|-----------------|-----|------------------|------|---------------------|----------------|-----------------|-------|

|                 |     |                  | DSAE | )R<15:8>            |                |                 |       |

| bit 15          |     |                  |      |                     |                |                 | bit 8 |

|                 |     |                  |      |                     |                |                 |       |

| R-0             | R-0 | R-0              | R-0  | R-0                 | R-0            | R-0             | R-0   |

|                 |     |                  | DSA  | DR<7:0>             |                |                 |       |

| bit 7           |     |                  |      |                     |                |                 | bit 0 |

|                 |     |                  |      |                     |                |                 |       |

| Legend:         |     |                  |      |                     |                |                 |       |

| R = Readable b  | oit | W = Writable b   | it   | U = Unimpleme       | nted bit, read | d as '0'        |       |

| -n = Value at P | OR  | '1' = Bit is set |      | '0' = Bit is cleare | ed             | x = Bit is unkn | iown  |

| 1               |     |                  |      |                     |                |                 |       |

bit 15-0 DSADR<15:0>: Most Recent DMA Address Accessed by DMA bits

# REGISTER 10-2: PMD2: PERIPHERAL MODULE DISABLE CONTROL REGISTER 2 (CONTINUED)

| bit 3 | <b>OC4MD:</b> Output Compare 4 Module Disable bit |

|-------|---------------------------------------------------|

|       | 1 = Output Compare 4 module is disabled           |

|       | 0 = Output Compare 4 module is enabled            |

| bit 2 | <b>OC3MD:</b> Output Compare 3 Module Disable bit |

|       | 1 = Output Compare 3 module is disabled           |

|       | 0 = Output Compare 3 module is enabled            |

| bit 1 | <b>OC2MD:</b> Output Compare 2 Module Disable bit |

|       | 1 = Output Compare 2 module is disabled           |

|       | 0 = Output Compare 2 module is enabled            |

| bit 0 | <b>OC1MD:</b> Output Compare 1 Module Disable bit |

|       | 1 = Output Compare 1 module is disabled           |

|       |                                                   |

| REGISTER      |              | 5: PERIPHER       |          |                   |                 |                 |        |

|---------------|--------------|-------------------|----------|-------------------|-----------------|-----------------|--------|

| R/W-0         | R/W-0        | R/W-0             | R/W-0    | R/W-0             | R/W-0           | R/W-0           | R/W-0  |

| IC16MD        | IC15MD       | IC14MD            | IC13MD   | IC12MD            | IC11MD          | IC10MD          | IC9MD  |

| bit 15        |              |                   |          |                   |                 |                 | bit    |

| R/W-0         | R/W-0        | D/M/ 0            | R/W-0    | D/M/ 0            |                 | D/M/ O          | D/M/ 0 |

| -             | -            | R/W-0             | -        | R/W-0             | R/W-0           | R/W-0           | R/W-0  |

| OC16MD        | OC15MD       | OC14MD            | OC13MD   | OC12MD            | OC11MD          | OC10MD          | OC9MD  |

| bit 7         |              |                   |          |                   |                 |                 | bit    |

| Legend:       |              |                   |          |                   |                 |                 |        |

| R = Readabl   | e hit        | W = Writable I    | oit      | U = Unimplen      | nented bit, rea | d as '0'        |        |

| -n = Value at |              | '1' = Bit is set  |          | '0' = Bit is clea |                 | x = Bit is unkn | 0.4/D  |

|               | TOR          |                   |          |                   | areu            |                 | OWIT   |

| bit 15        | IC16MD: IC1  | 6 Module Disab    | le bit   |                   |                 |                 |        |

|               | 1 = IC16 mod | dule is disabled  |          |                   |                 |                 |        |

|               | 0 = IC16 mod | ule is enabled    |          |                   |                 |                 |        |

| bit 14        | IC15MD: IC1  | 5 Module Disab    | le bit   |                   |                 |                 |        |

|               | 1 = IC15 mod | dule is disabled  |          |                   |                 |                 |        |

|               | 0 = IC15 mod | dule is enabled   |          |                   |                 |                 |        |

| bit 13        | IC14MD: IC1  | 4 Module Disab    | le bit   |                   |                 |                 |        |

|               |              | ule is disabled   |          |                   |                 |                 |        |

|               | 0 = IC14 mod | dule is enabled   |          |                   |                 |                 |        |

| bit 12        |              | 3 Module Disab    | le bit   |                   |                 |                 |        |

|               |              | dule is disabled  |          |                   |                 |                 |        |

| 1.11.44       |              | dule is enabled   | 1        |                   |                 |                 |        |

| bit 11        | -            | 2 Module Disab    | le bit   |                   |                 |                 |        |

|               |              | dule is disabled  |          |                   |                 |                 |        |

| bit 10        |              | 1 Module Disab    | le hit   |                   |                 |                 |        |

|               | _            | lule is disabled  |          |                   |                 |                 |        |

|               |              | lule is enabled   |          |                   |                 |                 |        |

| bit 9         | IC10MD: IC1  | 0 Module Disab    | le bit   |                   |                 |                 |        |

|               |              | ule is disabled   |          |                   |                 |                 |        |

|               |              | dule is enabled   |          |                   |                 |                 |        |

| bit 8         | IC9MD: IC9 N | Module Disable    | bit      |                   |                 |                 |        |

|               | 1 = IC9 modu | le is disabled    |          |                   |                 |                 |        |

|               | 0 = IC9 modu | ule is enabled    |          |                   |                 |                 |        |

| bit 7         | OC16MD: OC   | C16 Module Dis    | able bit |                   |                 |                 |        |

|               |              | odule is disabled | 1        |                   |                 |                 |        |

| bit 6         | OC15MD: 00   | C15 Module Dis    | able bit |                   |                 |                 |        |

|               | 1 = OC15 mo  | dule is disabled  | 1        |                   |                 |                 |        |

|               | 0 = OC15 mo  | dule is enabled   |          |                   |                 |                 |        |

| bit 5         | OC14MD: 00   | C14 Module Dis    | able bit |                   |                 |                 |        |

|               | 1 = OC14 mo  | dule is disabled  | ł        |                   |                 |                 |        |

|               | 0 = OC14 mo  | odule is enabled  |          |                   |                 |                 |        |

| bit 4         | OC13MD: OC   | C13 Module Dis    | able bit |                   |                 |                 |        |

|               |              | dule is disabled  | 1        |                   |                 |                 |        |

|               | 0 = OC13 mo  | odule is enabled  |          |                   |                 |                 |        |

|               |              |                   |          |                   |                 |                 |        |

| REGISTER 11-16: | <b>RPINR15: PERIPHERAL PIN SELECT INPUT REGISTER 15</b> |

|-----------------|---------------------------------------------------------|

|                 | (dsPIC33EPXXXMU806/810/814 DEVICES ONLY)                |

| U-0                   | R/W-0        | R/W-0                                                     | R/W-0         | R/W-0             | R/W-0         | R/W-0            | R/W-0 |

|-----------------------|--------------|-----------------------------------------------------------|---------------|-------------------|---------------|------------------|-------|

|                       |              |                                                           | I             | HOME1R<6:0>       | .(1)          |                  |       |

| bit 15                |              |                                                           |               |                   |               |                  | bit 8 |

|                       |              |                                                           |               |                   |               |                  |       |

| U-0                   | R/W-0        | R/W-0                                                     | R/W-0         | R/W-0             | R/W-0         | R/W-0            | R/W-0 |

|                       |              |                                                           |               | INDX1R<6:0>       | 1)            |                  |       |

| bit 7                 |              |                                                           |               |                   |               |                  | bit 0 |

| <del></del>           |              |                                                           |               |                   |               |                  |       |

| Legend:<br>R = Readab | lo bit       | W = Writable I                                            | oit           | U = Unimplen      | contod bit ro | ad as '0'        |       |

|                       |              | '1' = Bit is set                                          | JIL           | '0' = Bit is clea |               | x = Bit is unkr  |       |

| -n = Value a          | ILPUR        | I = BILIS SEL                                             |               | 0 = Bit is clear  | areo          | x = Bit is unkr  | IOWI  |

|                       | •            |                                                           |               |                   |               |                  |       |

|                       |              | Input tied to CMI<br>Input tied to Vss                    |               |                   |               |                  |       |

| bit 7                 | Unimpleme    | nted: Read as 'd                                          | )'            |                   |               |                  |       |

| bit 6-0               | (see Table 1 | D>: Assign QEI1<br>1-2 for input pin<br>Input tied to RP1 | selection num |                   | responding R  | Pn/RPIn Pin bits | (1)   |

|                       |              | Input tied to CMI<br>Input tied to Vss                    |               |                   |               |                  |       |

Note 1: These bits are available on dsPIC33EPXXX(MC/MU)806/810/814 devices only.

# 16.1 PWM Resources

Many useful resources related to the high-speed PWM are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en554310              |

#### 16.1.1 KEY RESOURCES

- Section 11. "High-Speed PWM" (DS70645) in the "dsPIC33E/PIC24E Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All related *"dsPIC33E/PIC24E Family Reference Manual"* Sections

- Development Tools

# REGISTER 16-19: IOCONX: PWMx I/O CONTROL REGISTER (CONTINUED)

| bit 3-2 | CLDAT<1:0>: Data for PWMxH and PWMxL Pins if CLMOD is Enabled bits                                                                                                                                              |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | IFLTMOD (FCLCONx<15>) = 0: Normal Fault mode:                                                                                                                                                                   |

|         | If current limit is active, PWMxH is driven to the state specified by CLDAT<1>.                                                                                                                                 |

|         | If current limit is active, PWMxL is driven to the state specified by CLDAT<0>.                                                                                                                                 |

|         | IFLTMOD (FCLCONx<15>) = 1: Independent Fault mode:                                                                                                                                                              |

|         | The CLDAT<1:0> bits are ignored.                                                                                                                                                                                |

| bit 1   | SWAP: Swap PWMxH and PWMxL Pins bit                                                                                                                                                                             |

|         | 1 = PWMxH output signal is connected to PWMxL pins; PWMxL output signal is connected to<br>PWMxH pins                                                                                                           |

|         | 0 = PWMxH and PWMxL pins are mapped to their respective pins                                                                                                                                                    |

| bit 0   | OSYNC: Output Override Synchronization bit                                                                                                                                                                      |

|         | <ul> <li>1 = Output overrides via the OVRDAT&lt;1:0&gt; bits are synchronized to the PWM time base</li> <li>0 = Output overrides via the OVDDAT&lt;1:0&gt; bits occur on the next CPU clock boundary</li> </ul> |

|         |                                                                                                                                                                                                                 |

Note 1: These bits should not be changed after the PWM module is enabled (PTEN = 1).

# 22.3 USB OTG Resources

Many useful resources related to USB OTG are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en554310

#### 22.3.1 KEY RESOURCES

- Section 11. "USB On-The-Go (OTG)" (DS70571) in the "dsPIC33E/PIC24E Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related *"dsPIC33E/PIC24E Family Reference Manual"* Sections

- Development Tools

| Base<br>Instr<br># | Assembly<br>Mnemonic | Assembly Syntax |                                             | Description                                 | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |

|--------------------|----------------------|-----------------|---------------------------------------------|---------------------------------------------|---------------|-------------------------------|--------------------------|

| 25                 | DAW                  |                 |                                             | Wn = decimal adjust Wn                      | 1             | 1                             | С                        |

| 26                 | DEC                  | DEC             | f                                           | f = f - 1                                   | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | DEC             | f,WREG                                      | WREG = f – 1                                | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | DEC             | Ws,Wd                                       | Wd = Ws - 1                                 | 1             | 1                             | C,DC,N,OV,Z              |

| 27                 | DEC2                 | DEC2            | f                                           | f = f - 2                                   | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | DEC2            | f,WREG                                      | WREG = f – 2                                | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | DEC2            | Ws,Wd                                       | Wd = Ws - 2                                 | 1             | 1                             | C,DC,N,OV,Z              |

| 28                 | DISI                 | DISI            | #lit14                                      | Disable Interrupts for k instruction cycles | 1             | 1                             | None                     |

| 29                 | DIV                  | DIV.S           | Wm,Wn                                       | Signed 16/16-bit Integer Divide             | 1             | 18                            | N,Z,C,OV                 |

|                    |                      | DIV.SD          | Wm,Wn                                       | Signed 32/16-bit Integer Divide             | 1             | 18                            | N,Z,C,OV                 |

|                    |                      | DIV.U           | Wm,Wn                                       | Unsigned 16/16-bit Integer Divide           | 1             | 18                            | N,Z,C,OV                 |

|                    |                      | DIV.UD          | Wm,Wn                                       | Unsigned 32/16-bit Integer Divide           | 1             | 18                            | N,Z,C,OV                 |

| 30                 | DIVF                 | DIVF            | <sub>Wm</sub> , <sub>Wn</sub> (1)           | Signed 16/16-bit Fractional Divide          | 1             | 18                            | N,Z,C,OV                 |

| 31                 | DO                   | DO              | <pre>#lit15,Expr(1)</pre>                   | Do code to PC + Expr, lit15 + 1 times       | 2             | 2                             | None                     |

|                    |                      | DO              | Wn, Expr(1)                                 | Do code to PC + Expr, (Wn) + 1 times        | 2             | 2                             | None                     |

| 32                 | ED                   | ED              | Wm*Wm,Acc,Wx,Wy,Wxd <sup>(1)</sup>          | Euclidean Distance (no accumulate)          | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

| 33                 | EDAC                 | EDAC            | Wm*Wm, Acc, Wx, Wy, Wxd <sup>(1)</sup>      | Euclidean Distance                          | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

| 34                 | EXCH                 | EXCH            | Wns,Wnd                                     | Swap Wns with Wnd                           | 1             | 1                             | None                     |

| 35                 | FBCL                 | FBCL            | Ws,Wnd                                      | Find Bit Change from Left (MSb) Side        | 1             | 1                             | С                        |

| 36                 | FF1L                 | FF1L            | Ws,Wnd                                      | Find First One from Left (MSb) Side         | 1             | 1                             | С                        |

| 37                 | FF1R                 | FF1R            | Ws,Wnd                                      | Find First One from Right (LSb) Side        | 1             | 1                             | С                        |

| 38                 | GOTO                 | GOTO            | Expr                                        | Go to address                               | 2             | 4                             | None                     |

|                    |                      | GOTO            | Wn                                          | Go to indirect                              | 1             | 4                             | None                     |

|                    |                      | GOTO.L          | Wn                                          | Go to indirect (long address)               | 1             | 4                             | None                     |

| 39                 | INC                  | INC             | f                                           | f = f + 1                                   | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | INC             | f,WREG                                      | WREG = f + 1                                | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | INC             | Ws,Wd                                       | Wd = Ws + 1                                 | 1             | 1                             | C,DC,N,OV,Z              |

| 40                 | INC2                 | INC2            | f                                           | f = f + 2                                   | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | INC2            | f,WREG                                      | WREG = f + 2                                | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | INC2            | Ws,Wd                                       | Wd = Ws + 2                                 | 1             | 1                             | C,DC,N,OV,Z              |

| 41                 | IOR                  | IOR             | f                                           | f = f .IOR. WREG                            | 1             | 1                             | N,Z                      |

|                    |                      | IOR             | f,WREG                                      | WREG = f .IOR. WREG                         | 1             | 1                             | N,Z                      |

|                    |                      | IOR             | #lit10,Wn                                   | Wd = lit10 .IOR. Wd                         | 1             | 1                             | N,Z                      |

|                    |                      | IOR             | Wb,Ws,Wd                                    | Wd = Wb .IOR. Ws                            | 1             | 1                             | N,Z                      |

|                    |                      | IOR             | Wb,#lit5,Wd                                 | Wd = Wb .IOR. lit5                          | 1             | 1                             | N,Z                      |

| 42                 | LAC                  | LAC             | Wso,#Slit4,Acc                              | Load Accumulator                            | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

| 43                 | LNK                  | LNK             | #lit14                                      | Link Frame Pointer                          | 1             | 1                             | SFA                      |

| 44                 | LSR                  | LSR             | f                                           | f = Logical Right Shift f                   | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | LSR             | f,WREG                                      | WREG = Logical Right Shift f                | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | LSR             | Ws,Wd                                       | Wd = Logical Right Shift Ws                 | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | LSR             | Wb,Wns,Wnd                                  | Wnd = Logical Right Shift Wb by Wns         | 1             | 1                             | N,Z                      |

|                    |                      | LSR             | Wb,#lit5,Wnd                                | Wnd = Logical Right Shift Wb by lit5        | 1             | 1                             | N,Z                      |

| 45                 | MAC                  | MAC             | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd,AWB <sup>(1)</sup>  | Multiply and Accumulate                     | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | MAC             | Wm*Wm, Acc, Wx, Wxd, Wy, Wyd <sup>(1)</sup> | Square and Accumulate                       | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

#### TABLE 30-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note 1:

This instruction is available in dsPIC33EPXXX(GP/MC/MU)806/810/814 devices only. Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle. 2:

| Base<br>Instr<br># | Assembly<br>Mnemonic |        | Assembly Syntax    | Description                        | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |

|--------------------|----------------------|--------|--------------------|------------------------------------|---------------|-------------------------------|--------------------------|

| 72                 | SL                   | SL     | f                  | f = Left Shift f                   | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | SL     | f,WREG             | WREG = Left Shift f                | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | SL     | Ws,Wd              | Wd = Left Shift Ws                 | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | SL     | Wb,Wns,Wnd         | Wnd = Left Shift Wb by Wns         | 1             | 1                             | N,Z                      |

|                    |                      | SL     | Wb,#lit5,Wnd       | Wnd = Left Shift Wb by lit5        | 1             | 1                             | N,Z                      |

| 73                 | SUB                  | SUB    | <sub>Acc</sub> (1) | Subtract Accumulators              | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | SUB    | f                  | f = f – WREG                       | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUB    | f,WREG             | WREG = f – WREG                    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUB    | #lit10,Wn          | Wn = Wn - lit10                    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUB    | Wb,Ws,Wd           | Wd = Wb – Ws                       | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUB    | Wb,#lit5,Wd        | Wd = Wb - lit5                     | 1             | 1                             | C,DC,N,OV,Z              |

| 74                 | SUBB                 | SUBB   | f                  | $f = f - WREG - (\overline{C})$    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBB   | f,WREG             | WREG = $f - WREG - (\overline{C})$ | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBB   | #lit10,Wn          | Wn = Wn – lit10 – $(\overline{C})$ | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBB   | Wb,Ws,Wd           | $Wd = Wb - Ws - (\overline{C})$    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBB   | Wb,#lit5,Wd        | $Wd = Wb - lit5 - (\overline{C})$  | 1             | 1                             | C,DC,N,OV,Z              |

| 75                 | SUBR                 | SUBR   | f                  | f = WREG – f                       | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBR   | f,WREG             | WREG = WREG – f                    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBR   | Wb,Ws,Wd           | Wd = Ws – Wb                       | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBR   | Wb,#lit5,Wd        | Wd = lit5 – Wb                     | 1             | 1                             | C,DC,N,OV,Z              |

| 76                 | SUBBR                | SUBBR  | f                  | $f = WREG - f - (\overline{C})$    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBBR  | f,WREG             | WREG = WREG – f – $(\overline{C})$ | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBBR  | Wb,Ws,Wd           | $Wd = Ws - Wb - (\overline{C})$    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBBR  | Wb,#lit5,Wd        | Wd = lit5 – Wb – $(\overline{C})$  | 1             | 1                             | C,DC,N,OV,Z              |

| 77                 | SWAP                 | SWAP.b | Wn                 | Wn = nibble swap Wn                | 1             | 1                             | None                     |

|                    |                      | SWAP   | Wn                 | Wn = byte swap Wn                  | 1             | 1                             | None                     |

| 78                 | TBLRDH               | TBLRDH | Ws,Wd              | Read Prog<23:16> to Wd<7:0>        | 1             | 5                             | None                     |

| 79                 | TBLRDL               | TBLRDL | Ws,Wd              | Read Prog<15:0> to Wd              | 1             | 5                             | None                     |

| 80                 | TBLWTH               | TBLWTH | Ws,Wd              | Write Ws<7:0> to Prog<23:16>       | 1             | 2                             | None                     |

| 81                 | TBLWTL               | TBLWTL | Ws,Wd              | Write Ws to Prog<15:0>             | 1             | 2                             | None                     |

| 82                 | ULNK                 | ULNK   |                    | Unlink Frame Pointer               | 1             | 1                             | SFA                      |

| 83                 | XOR                  | XOR    | f                  | f = f .XOR. WREG                   | 1             | 1                             | N,Z                      |