Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| 2000                       |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 60 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART, USB OTG             |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                     |

| Number of I/O              | 83                                                                                |

| Program Memory Size        | 256КВ (85.5К х 24)                                                                |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 12K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 32x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256mu810t-e-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                          | Pin<br>Type | Buffer<br>Type | PPS | Description                                                    |

|-----------------------------------|-------------|----------------|-----|----------------------------------------------------------------|

| SCL1 <sup>(5)</sup>               | I/O         | ST             | No  | Synchronous serial clock input/output for I2C1.                |

| SDA1 <sup>(5)</sup>               | I/O         | ST             | No  | Synchronous serial data input/output for I2C1.                 |

| ASCL1 <sup>(5)</sup>              | I/O         | ST             | No  | Alternate synchronous serial clock input/output for I2C1.      |

| ASDA1 <sup>(5)</sup>              | I/O         | ST             | No  | Alternate synchronous serial data input/output for I2C1.       |

| SCL2 <sup>(5)</sup>               | I/O         | ST             | No  | Synchronous serial clock input/output for I2C2.                |

| SDA2 <sup>(5)</sup>               | I/O         | ST             | No  | Synchronous serial data input/output for I2C2.                 |

| ASCL2 <sup>(5)</sup>              | I/O         | ST             | No  | Alternate synchronous serial clock input/output for I2C2.      |

| ASDA2 <sup>(5)</sup>              | I/O         | ST             | No  | Alternate synchronous serial data input/output for I2C2.       |

| TMS                               | Ι           | ST             | No  | JTAG Test mode select pin.                                     |

| ТСК                               | I           | ST             | No  | JTAG test clock input pin.                                     |

| TDI                               | I.          | ST             | No  | JTAG test data input pin.                                      |

| TDO                               | 0           | —              | No  | JTAG test data output pin.                                     |

| INDX1 <sup>(1)</sup>              | I           | ST             | Yes | Quadrature Encoder Index1 pulse input.                         |

| HOME1 <sup>(1)</sup>              | 1           | ST             | Yes | Quadrature Encoder Home1 pulse input.                          |

| QEA1 <sup>(1)</sup>               | I           | ST             | Yes | Quadrature Encoder Phase A input in QEI1 mode. Auxiliary timer |

|                                   |             |                |     | external clock input in Timer mode.                            |

| QEB1 <sup>(1)</sup>               | I           | ST             | Yes | Quadrature Encoder Phase A input in QEI1 mode. Auxiliary timer |

| (4)                               |             |                |     | external gate input in Timer mode.                             |

| CNTCMP1 <sup>(1)</sup>            | 0           |                | Yes | Quadrature Encoder Compare Output 1.                           |

| INDX2 <sup>(1)</sup>              | I           | ST             | Yes | Quadrature Encoder Index2 pulse input.                         |

| HOME2 <sup>(1)</sup>              | I           | ST             | Yes | Quadrature Encoder Home2 pulse input.                          |

| QEA2 <sup>(1)</sup>               | I           | ST             | Yes | Quadrature Encoder Phase A input in QEI2 mode. Auxiliary timer |

| (1)                               |             |                |     | external clock input in Timer mode.                            |

| QEB2 <sup>(1)</sup>               | I           | ST             | Yes | Quadrature Encoder Phase B input in QEI2 mode. Auxiliary timer |

|                                   | 0           |                | M   | external gate input in Timer mode.                             |

| CNTCMP2 <sup>(1)</sup>            | 0           | —              | Yes | Quadrature Encoder Compare Output 2.                           |

| COFS                              | I/O         | ST             | Yes | Data Converter Interface frame synchronization pin.            |

| CSCK                              | I/O         | ST             | Yes | Data Converter Interface serial clock input/output pin.        |

| CSDI                              |             | ST             | Yes | Data Converter Interface serial data input pin.                |

| CSDO                              | 0           |                | Yes | Data Converter Interface serial data output pin.               |

| C1RX                              | I           | ST             | Yes | ECAN1 bus receive pin.                                         |

| C1TX                              | 0           | —              | Yes | ECAN1 bus transmit pin.                                        |

| C2RX                              | Ι           | ST             | Yes | ECAN2 bus receive pin.                                         |

| C2TX                              | 0           | —              | Yes | ECAN2 bus transmit pin.                                        |

| RTCC                              | 0           |                | No  | Real-Time Clock alarm output.                                  |

| CVREF                             | 0           | Analog         | No  | Comparator voltage reference output.                           |

| C1IN1+, C1IN2-,<br>C1IN1-, C1IN3- | I           | Analog         | No  | Comparator 1 inputs                                            |

| C1OUT                             | 0           |                | Yes | Comparator 1 output.                                           |

#### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend:

CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels PPS = Peripheral Pin Select

Analog = Analog input O = Output TTL = TTL input buffer

P = Powe I = Input

Note 1: This pin is available on dsPIC33EPXXX(MC/MU)806/810/814 devices only.

- **2:** AVDD must be connected at all times.

- 3: These pins are input only on dsPIC33EPXXXMU8XX and PIC24EPXXXGU8XX devices.

- 4: These pins are only available on dsPIC33EPXXXMU8XX and PIC24EPXXXGU8XX devices.

- 5: The availability of I<sup>2</sup>C<sup>™</sup> interfaces varies by device. Refer to the "**Pin Diagrams**" section for availability. Selection (SDAx/SCLx or ASDAx/ASCLx) is made using the device Configuration bits, ALTI2C1 and ALTI2C2 (FPOR<5:4>). See Section 29.0 "Special Features" for more information.

- 6: Analog functionality is activated by enabling the USB module and is not controlled by the ANSEL register.

#### **CPU Control Registers** 3.7

| R/W-0                  | R/W-0                  | R/W-0                                  | R/W-0                       | R/C-0              | R/C-0              | R -0              | R/W-0           |

|------------------------|------------------------|----------------------------------------|-----------------------------|--------------------|--------------------|-------------------|-----------------|

| 0A <sup>(1)</sup>      | OB <sup>(1)</sup>      | SA <sup>(1,4)</sup>                    | SB <sup>(1,4)</sup>         | OAB <sup>(1)</sup> | SAB <sup>(1)</sup> | DA <sup>(1)</sup> | DC              |

| bit 15                 |                        |                                        | I                           |                    | I                  | 1                 | bit 8           |

| R/W-0 <sup>(2,3)</sup> | R/W-0 <sup>(2,3)</sup> | R/W-0 <sup>(2,3)</sup>                 |                             | DAVA               | DAMA               | DAMO              | DANA            |

| R/W-0(-,-,)            |                        | R/W-0(-,-,-)                           | R-0                         | R/W-0              | R/W-0              | R/W-0             | R/W-0           |

|                        | IPL<2:0>               |                                        | RA                          | N                  | OV                 | Z                 | С               |

| bit 7                  |                        |                                        |                             |                    |                    |                   | bit (           |

| Legend:                |                        | U = Unimplen                           | nented bit, rea             | ad as '0'          |                    |                   |                 |

| R = Readable           | bit                    | W = Writable                           | bit                         | C = Clearable      | e bit              |                   |                 |

| -n = Value at I        | POR                    | '1'= Bit is set                        |                             | '0' = Bit is cle   | ared               | x = Bit is unkr   | nown            |

|                        |                        |                                        |                             |                    |                    |                   |                 |

| bit 15                 | OA: Accumu             | lator A Overflov                       | v Status bit <sup>(1)</sup> |                    |                    |                   |                 |

|                        |                        | ator A has over                        |                             |                    |                    |                   |                 |

|                        |                        | ator A has not o                       |                             |                    |                    |                   |                 |

| bit 14                 |                        | lator B Overflov                       |                             |                    |                    |                   |                 |

|                        |                        | ator B has over                        |                             |                    |                    |                   |                 |

|                        |                        | ator B has not o                       |                             | (1 4)              |                    |                   |                 |

| bit 13                 |                        | lator A Saturatio                      |                             |                    |                    |                   |                 |

|                        |                        | ator A is saturat<br>ator A is not sat |                             | en saturated at    | some time          |                   |                 |

| bit 12                 |                        | lator B Saturatio                      |                             | tue hit(1,4)       |                    |                   |                 |

| DIT 12                 |                        | ator B is saturat                      |                             |                    | some time          |                   |                 |

|                        |                        | ator B is not sat                      |                             |                    | Some time          |                   |                 |

| bit 11                 | <b>0AB:</b> 0A    0    | OB Combined A                          | ccumulator O                | verflow Status     | bit <sup>(1)</sup> |                   |                 |

|                        |                        | ators A or B hav                       |                             |                    |                    |                   |                 |

|                        | 0 = Neither A          | Accumulators A                         | or B have ove               | erflowed           |                    |                   |                 |

| bit 10                 | <b>SAB:</b> SA    S    | B Combined Ad                          | cumulator 'Si               | ticky' Status bit  | (1)                |                   |                 |

|                        |                        | ators A or B are<br>Accumulator A o    |                             |                    | urated at some     | time              |                 |

| bit 9                  | DA: DO Loop            |                                        |                             |                    |                    |                   |                 |

| bit 9                  | 1 = DO loop i          |                                        |                             |                    |                    |                   |                 |

|                        |                        | not in progress                        |                             |                    |                    |                   |                 |

| bit 8                  |                        | U Half Carry/Bo                        | prrow bit                   |                    |                    |                   |                 |

|                        | 1 = A carry-           | out from the 4th                       |                             | for byte-sized o   | data) or 8th low   | order bit (for wo | rd-sized data   |

|                        |                        | -out from the 4                        | th low order b              | oit (for byte-siz  | ed data) or 8th    | low order bit (f  | or word-size    |

|                        |                        | the result occur                       |                             |                    |                    |                   |                 |

| Note 1: Thi            | s bit is availab       | le on dsPIC33E                         | PXXX(GP/MC                  | C/MU)806/810/      | 814 devices on     | lv.               |                 |

|                        |                        | are concatenat                         | -                           | -                  |                    | -                 | errupt Priority |

|                        |                        | n parentheses i                        |                             |                    |                    |                   |                 |

| • T                    |                        |                                        |                             |                    | 4 .4 5. )          |                   |                 |

#### **REGISTER 3-1: SR: CPU STATUS REGISTER**

- 3: The IPL<2:0> bits are read-only when NSTDIS = 1 (INTCON1<15>).

- 4: A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

#### TABLE 4-58: PORTC REGISTER MAP FOR dsPIC33EPXXX(GP/MC/MU)806 AND PIC24EPXXXGP806 DEVICES ONLY

| File<br>Name | Addr, | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISC        | 0E20  | TRISC15 | TRISC14 | TRISC13 | TRISC12 | _      |        |       |       | _     |       | —     | _     | —     | _     | _     |       | F000          |

| PORTC        | 0E22  | RC15    | RC14    | RC13    | RC12    | _      |        |       |       | _     | _     | _     | _     | _     | _     | _     |       | XXXX          |

| LATC         | 0E24  | LATC15  | LATC14  | LATC13  | LATC12  | _      |        |       |       | _     | _     | _     | _     | _     | _     | _     |       | XXXX          |

| ODCC         | 0E26  | _       | -       | _       | _       |        | _      | _     | _     | _     | _     | _     |       | _     |       | _     | _     | 0000          |

| CNENC        | 0E28  | CNIEC15 | CNIEC14 | CNIEC13 | CNIEC12 |        | _      | _     | _     | _     | _     | _     |       | _     |       | _     | _     | 0000          |

| CNPUC        | 0E2A  | CNPUC15 | CNPUC14 | CNPUC13 | CNPUC12 |        | _      | _     | _     | _     | _     | _     |       | _     |       | _     | _     | 0000          |

| CNPDC        | 0E2C  | CNPDC15 | CNPDC14 | CNPDC13 | CNPDC12 | _      |        |       |       | _     | _     | _     | _     | _     | _     | _     |       | 0000          |

| ANSELC       | 0E2E  | —       | ANSC14  | ANSC13  | —       | _      | _      | _     |       | —     | -     | _     | _     | _     | _     | _     |       | 6000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal

#### TABLE 4-59: PORTD REGISTER MAP FOR dsPIC33EPXXXMU810/814 AND PIC24EPXXXGU810/814 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISD        | 0E30  | TRISD15 | TRISD14 | TRISD13 | TRISD12 | TRISD11 | TRISD10 | TRISD9 | TRISD8 | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 | FFFF          |

| PORTD        | 0E32  | RD15    | RD14    | RD13    | RD12    | RD11    | RD10    | RD9    | RD8    | RD7    | RD6    | RD5    | RD4    | RD3    | RD2    | RD1    | RD0    | XXXX          |

| LATD         | 0E34  | LATD15  | LATD14  | LATD13  | LATD12  | LATD11  | LATD10  | LATD9  | LATD8  | LATD7  | LATD6  | LATD5  | LATD4  | LATD3  | LATD2  | LATD1  | LATD0  | XXXX          |

| ODCD         | 0E36  | ODCD15  | ODCD14  | ODCD13  | ODCD12  | ODCD11  | ODCD10  | ODCD9  | ODCD8  |        | _      | ODCD5  | ODCD4  | ODCD3  | ODCD2  | ODCD1  | ODCD0  | 0000          |

| CNEND        | 0E38  | CNIED15 | CNIED14 | CNIED13 | CNIED12 | CNIED11 | CNIED10 | CNIED9 | CNIED8 | CNIED7 | CNIED6 | CNIED5 | CNIED4 | CNIED3 | CNIED2 | CNIED1 | CNIED0 | 0000          |

| CNPUD        | 0E3A  | CNPUD15 | CNPUD14 | CNPUD13 | CNPUD12 | CNPUD11 | CNPUD10 | CNPUD9 | CNPUD8 | CNPUD7 | CNPUD6 | CNPUD5 | CNPUD4 | CNPUD3 | CNPUD2 | CNPUD1 | CNPUD0 | 0000          |

| CNPDD        | 0E3C  | CNPDD15 | CNPDD14 | CNPDD13 | CNPDD12 | CNPDD11 | CNPDD10 | CNPDD9 | CNPDD8 | CNPDD7 | CNPDD6 | CNPDD5 | CNPDD4 | CNPDD3 | CNPDD2 | CNPDD1 | CNPDD0 | 0000          |

| ANSELD       | 0E3E  | _       | _       | _       | _       | _       | _       | _      | _      | ANSD7  | ANSD6  | _      | _      | _      | _      | _      | _      | 00C0          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-60: PORTD REGISTER MAP FOR dsPIC33EPXXX(GP/MC/MU)806 AND PIC24EPXXXGP806 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISD        | 0E30  | _      | _      | _      |        | TRISD11 | TRISD10 | TRISD9 | TRISD8 | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 | OFFF          |

| PORTD        | 0E32  | _      | _      | _      | _      | RD11    | RD10    | RD9    | RD8    | RD7    | RD6    | RD5    | RD4    | RD3    | RD2    | RD1    | RD0    | XXXX          |

| LATD         | 0E34  | _      | —      | —      |        | LATD11  | LATD10  | LATD9  | LATD8  | LATD7  | LATD6  | LATD5  | LATD4  | LATD3  | LATD2  | LATD1  | LATD0  | XXXX          |

| ODCD         | 0E36  | _      | —      | —      |        | ODCD11  | ODCD10  | ODCD9  | ODCD8  |        | —      | ODCD5  | ODCD4  | ODCD3  | ODCD2  | ODCD1  | ODCD0  | 0000          |

| CNEND        | 0E38  | _      | —      | —      |        | CNIED11 | CNIED10 | CNIED9 | CNIED8 | CNIED7 | CNIED6 | CNIED5 | CNIED4 | CNIED3 | CNIED2 | CNIED1 | CNIED0 | 0000          |

| CNPUD        | 0E3A  | _      | —      | —      |        | CNPUD11 | CNPUD10 | CNPUD9 | CNPUD8 | CNPUD7 | CNPUD6 | CNPUD5 | CNPUD4 | CNPUD3 | CNPUD2 | CNPUD1 | CNPUD0 | 0000          |

| CNPDD        | 0E3C  | _      | —      | —      |        | CNPDD11 | CNPDD10 | CNPDD9 | CNPDD8 | CNPDD7 | CNPDD6 | CNPDD5 | CNPDD4 | CNPDD3 | CNPDD2 | CNPDD1 | CNPDD0 | 0000          |

| ANSELD       | 0E3E  | _      | —      | _      |        | _       | —       | —      |        | ANSD7  | ANSD6  | _      |        | -      | _      | _      | _      | 00C0          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

© 2009-2012 Microchip Technology Inc.

NOTES:

#### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

| bit 4 | MATHERR: Math Error Status bit               |

|-------|----------------------------------------------|

|       | 1 = Math error trap has occurred             |

|       | 0 = Math error trap has not occurred         |

|       |                                              |

| bit 3 | ADDRERR: Address Error Trap Status bit       |

|       | 1 = Address error trap has occurred          |

|       | 0 = Address error trap has not occurred      |

| bit 2 | STKERR: Stack Error Trap Status bit          |

|       | 1 = Stack error trap has occurred            |

|       | 0 = Stack error trap has not occurred        |

| bit 1 | OSCFAIL: Oscillator Failure Trap Status bit  |

|       | 1 = Oscillator failure trap has occurred     |

|       | 0 = Oscillator failure trap has not occurred |

| bit 0 | Unimplemented: Read as '0'                   |

Note 1: This bit is available on dsPIC33EPXXX(GP/MC/MU)806/810/814 devices only.

#### 11.5 I/O Helpful Tips

- In some cases, certain pins, as defined in 1. Table 32-9 in Section 32.0 "Electrical Characteristics" under "Injection Current", have internal protection diodes to VDD and VSS; the term "Injection Current" is also referred to as "Clamp Current". On designated pins, with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings with respect to the VSS and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device that is clamped internally by the VDD and VSS power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin, (i.e., ANx, see Table 1-1 in Section 1.0 "Device Overview"), are always analog pins by default after any Reset. Consequently, configuring a pin as an analog input pin, automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared analog pin (see Table 1-1 in Section 1.0 "Device Overview"), the user application needs to configure the Analog Pin Configuration registers in the I/O ports module (i.e., ANSELx) by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in the data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left to right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1; this indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin. Dedicated peripheral functions are always higher priority than remappable functions. I/O pins are always the lowest priority.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD-0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

- 5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of the data sheet. For example:

VOH = 2.4v @ IOH = -8 mA and VDD = 3.3V

The maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in **Section 32.0 "Electrical Characteristics"** for additional information.

- 6. The Peripheral Pin Select (PPS) pin mapping rules are as follows:

- a) Only one "output" function can be active on a given pin at any time regardless if it is a dedicated or remappable function (one pin, one output).

- b) It is possible to assign a "remappable output" function to multiple pins and externally short or tie them together for increased current drive.

- c) If any "dedicated output" function is enabled on a pin, it will take precedence over any remappable "output" function.

- d) If any "dedicated digital" (input or output) function is enabled on a pin, any number of "input" remappable functions can be mapped to the same pin.

- e) If any "dedicated analog" function(s) are enabled on a given pin, "digital input(s)" of any kind will all be disabled, although a single "digital output", at the user's cautionary discretion, can be enabled and active as long as there is no signal contention with an external analog input signal. For example, it is possible for the ADC to convert the digital output logic level, or to toggle a digital output on a comparator or ADC input, provided there is no external analog input, such as for a built-in self test.

- f) Any number of "input" remappable functions can be mapped to the same pin(s) at the same time, including any pin with a single output from either a dedicated or remappable "output".

#### REGISTER 11-18: RPINR17: PERIPHERAL PIN SELECT INPUT REGISTER 17 (dsPIC33EPXXXMU806/810/814 DEVICES ONLY)

| U-0             | R/W-0                        | R/W-0                                | R/W-0 | R/W-0            | R/W-0        | R/W-0            | R/W-0 |

|-----------------|------------------------------|--------------------------------------|-------|------------------|--------------|------------------|-------|

| —               |                              |                                      | I     | HOME2R<6:0>      | .(1)         |                  |       |

| bit 15          |                              |                                      |       |                  |              |                  | bit 8 |

| U-0             | R/W-0                        | R/W-0                                | R/W-0 | R/W-0            | R/W-0        | R/W-0            | R/W-0 |

| _               |                              |                                      |       | INDX2R<6:0>      | [1]          |                  |       |

| bit 7           |                              |                                      |       |                  |              |                  | bit 0 |

|                 |                              |                                      |       |                  |              |                  |       |

| Legend:         |                              |                                      |       |                  |              |                  |       |

| R = Readable    |                              | W = Writable I                       | oit   | U = Unimplen     |              |                  |       |

| -n = Value at F | POR                          | '1' = Bit is set                     |       | '0' = Bit is cle | ared         | x = Bit is unkr  | nown  |

|                 |                              | -2 for input pin<br>nput tied to RP1 |       | ,                |              |                  |       |

|                 | •                            |                                      |       |                  |              |                  |       |

|                 |                              | nput tied to CMI                     |       |                  |              |                  |       |

| h:+ 7           |                              | nput tied to Vss                     |       |                  |              |                  |       |

| bit 7           | -                            | ted: Read as '                       |       |                  | l' D         |                  | (1)   |

| bit 6-0         |                              | -2 for input pin                     |       |                  | responding R | Pn/RPIn Pin bits | (')   |

|                 | 1111111 = Ir                 | nput tied to RP1                     | 27    |                  |              |                  |       |

|                 | ·                            |                                      |       |                  |              |                  |       |

|                 |                              |                                      |       |                  |              |                  |       |

|                 | 0000001 = lr<br>0000000 = lr | nput tied to CMI                     |       |                  |              |                  |       |

Note 1: These bits are available on dsPIC33EPXXX(MC/MU)806/810/814 devices only.

| U-0          | R/W-0        | R/W-0                                                                 | R/W-0         | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

|--------------|--------------|-----------------------------------------------------------------------|---------------|------------------|------------------|-----------------|-------|

| _            |              |                                                                       |               | U2CTSR<6:0       | >                |                 |       |

| oit 15       |              |                                                                       |               |                  |                  |                 | bit   |

|              |              |                                                                       |               |                  |                  |                 |       |

| U-0          | R/W-0        | R/W-0                                                                 | R/W-0         | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

| _            |              |                                                                       |               | U2RXR<6:0>       | •                |                 |       |

| bit 7        |              |                                                                       |               |                  |                  |                 | bit   |

|              |              |                                                                       |               |                  |                  |                 |       |

| Legend:      |              |                                                                       |               |                  |                  |                 |       |

| R = Readat   | ole bit      | W = Writable                                                          | bit           | U = Unimplen     | nented bit, read | d as '0'        |       |

| -n = Value a | at POR       | '1' = Bit is set                                                      |               | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|              | -            | 1-2 for input pin<br>Input tied to RP                                 |               | ,                |                  |                 |       |

|              |              |                                                                       |               |                  |                  |                 |       |

|              |              | Input tied to CM<br>Input tied to Vss                                 |               |                  |                  |                 |       |

| bit 7        | Unimpleme    | nted: Read as '                                                       | 0'            |                  |                  |                 |       |

| bit 6-0      | (see Table 1 | I>: Assign UART<br>1-2 for input pin<br>Input tied to RP <sup>2</sup> | selection num |                  | rresponding RI   | Pn/RPIn Pin bit | 3     |

|              |              |                                                                       |               |                  |                  |                 |       |

|              | •            |                                                                       |               |                  |                  |                 |       |

|              |              | Input tied to CM                                                      | P1            |                  |                  |                 |       |

#### REGISTER 11-20: RPINR19: PERIPHERAL PIN SELECT INPUT REGISTER 19

0000001 =Input tied to UMP 0000000 =Input tied to Vss

#### REGISTER 17-2: QEIxIOC: QEIx I/O CONTROL REGISTER (CONTINUED)

- bit 2 INDEX: Status of INDXx Input Pin After Polarity Control bit

- 1 = Pin is at logic '1'

- 0 = Pin is at logic '0'

#### bit 1 QEB: Status of QEBx Input Pin After Polarity Control And SWPAB Pin Swapping bit

- 1 = Pin is at logic '1'

- 0 = Pin is at logic '0'

#### bit 0 QEA: Status of QEAx Input Pin After Polarity Control And SWPAB Pin Swapping bit

- 1 = Pin is at logic '1'

- 0 = Pin is at logic '0'

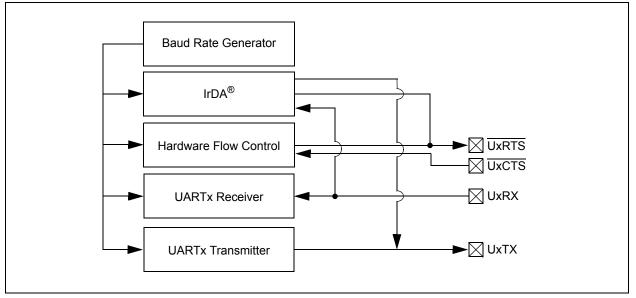

### 20.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXX(GP/MC/MU)806/ 810/814 and PIC24EPXXX(GP/GU)810/ 814 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 17. "UART" (DS70582) of the "dsPIC33E/PIC24E Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814 family of devices contains four UART modules.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814 device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

The primary features of the UARTx module are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- · One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 4.375 Mbps to 67 bps at 16x mode at 70 MIPS

- Baud Rates Ranging from 17.5 Mbps to 267 bps at 4x mode at 70 MIPS

- 4-Deep First-In First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-bit mode with Address Detect (9th bit = 1)

- · Transmit and Receive Interrupts

- A Separate Interrupt for All UARTx Error Conditions

- · Loopback mode for Diagnostic Support

- · Support for Sync and Break Characters

- · Support for Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UARTx module is shown in Figure 20-1. The UARTx module consists of these key hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

#### FIGURE 20-1: UARTX SIMPLIFIED BLOCK DIAGRAM

# dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

|                 | —            |                                       |                  |                  |                    |                 |       |

|-----------------|--------------|---------------------------------------|------------------|------------------|--------------------|-----------------|-------|

| R/C-0           |              | TXBO                                  | TXBP             | RXBP             | TXWAR              | RXWAR           | EWARN |

|                 |              |                                       |                  |                  |                    |                 | bit   |

|                 | R/C-0        | R/C-0                                 | U-0              | R/C-0            | R/C-0              | R/C-0           | R/C-0 |

| IVRIF           | WAKIF        | ERRIF                                 | _                | FIFOIF           | RBOVIF             | RBIF            | TBIF  |

| bit 7           |              |                                       |                  |                  |                    |                 | bit   |

| Legend:         |              | C = Writable                          | bit. but only '0 | ' can be writte  | n to clear the bit | -               |       |

| R = Readable    | e bit        | W = Writable                          |                  |                  | mented bit, read   |                 |       |

| -n = Value at I | POR          | '1' = Bit is set                      |                  | '0' = Bit is cle |                    | x = Bit is unkr | nown  |

|                 |              |                                       |                  |                  |                    |                 |       |

| bit 15-14       | -            | ted: Read as '                        |                  |                  |                    |                 |       |

| bit 13          |              | mitter in Error                       |                  | bit              |                    |                 |       |

|                 |              | er is in Bus Off                      |                  |                  |                    |                 |       |

| bit 12          |              | er is not in Bus<br>mitter in Error S |                  | sivo hit         |                    |                 |       |

| JILIZ           |              | er is in Bus Pa                       |                  |                  |                    |                 |       |

|                 |              | er is not in Bus                      |                  | <del>)</del>     |                    |                 |       |

| bit 11          | RXBP: Recei  | iver in Error Sta                     | ate Bus Passiv   | ve bit           |                    |                 |       |

|                 | 1 = Receiver | is in Bus Pass                        | ve state         |                  |                    |                 |       |

|                 | 0 = Receiver | is not in Bus P                       | assive state     |                  |                    |                 |       |

| bit 10          |              | nsmitter in Erro                      |                  | ng bit           |                    |                 |       |

|                 |              | er is in Error W                      | •                | 4 -              |                    |                 |       |

| bit 9           |              | er is not in Error                    | •                |                  |                    |                 |       |

| JIL9            |              | ceiver in Error<br>is in Error War    | -                | DIL              |                    |                 |       |

|                 |              | is not in Error                       |                  |                  |                    |                 |       |

| bit 8           |              | nsmitter or Red                       | •                | State Warning    | ı bit              |                 |       |

|                 |              | er or Receiver                        |                  | Ų                |                    |                 |       |

|                 |              | er or Receiver                        |                  | State Warning    | g state            |                 |       |

| bit 7           |              | d Message Inte                        |                  |                  |                    |                 |       |

|                 |              | Request has o<br>Request has n        |                  |                  |                    |                 |       |

| bit 6           |              | Wake-up Activ                         |                  | ag hit           |                    |                 |       |

| 510             |              | Request has o                         |                  |                  |                    |                 |       |

|                 |              | Request has n                         |                  |                  |                    |                 |       |

| bit 5           | ERRIF: Error | Interrupt Flag                        | bit (multiple so | ources in CxIN   | ITF<13:8> regis    | ter)            |       |

|                 |              | Request has o                         |                  |                  |                    |                 |       |

|                 | •            | Request has n                         |                  |                  |                    |                 |       |

| bit 4           | -            | ted: Read as '                        |                  |                  |                    |                 |       |

| bit 3           |              | ) Almost Full In                      |                  | t                |                    |                 |       |

|                 |              | Request has o<br>Request has n        |                  |                  |                    |                 |       |

| bit 2           | •            | Buffer Overflor                       |                  | a bit            |                    |                 |       |

|                 |              | Request has o                         | -                | 9 510            |                    |                 |       |

|                 |              | Request has n                         |                  |                  |                    |                 |       |

| bit 1           | RBIF: RX Bu  | ffer Interrupt Fl                     | ag bit           |                  |                    |                 |       |

|                 |              | Request has o                         |                  |                  |                    |                 |       |

|                 | -            | Request has n                         |                  |                  |                    |                 |       |

| bit 0           |              | fer Interrupt Fla                     | -                |                  |                    |                 |       |

|                 |              | Request has o<br>Request has n        |                  |                  |                    |                 |       |

### 25.2 Comparator Control Registers

| R/W-0         | U-0                                  | U-0                              | U-0            | U-0              | R-0               | R-0             | R-0   |

|---------------|--------------------------------------|----------------------------------|----------------|------------------|-------------------|-----------------|-------|

| CMSIDL        |                                      |                                  | _              | _                | C3EVT             | C2EVT           | C1EVT |

| bit 15        |                                      | l .                              |                |                  | I                 | 1               | bit 8 |

|               |                                      |                                  |                |                  |                   |                 |       |

| U-0           | U-0                                  | U-0                              | U-0            | U-0              | R-0               | R-0             | R-0   |

| _             | _                                    | _                                | _              | _                | C3OUT             | C2OUT           | C10UT |

| bit 7         |                                      |                                  |                |                  | 1                 |                 | bit ( |

|               |                                      |                                  |                |                  |                   |                 |       |

| Legend:       |                                      |                                  |                |                  |                   |                 |       |

| R = Readable  | e bit                                | W = Writable                     | bit            | U = Unimpler     | mented bit, read  | d as '0'        |       |

| -n = Value at | POR                                  | '1' = Bit is set                 |                | '0' = Bit is cle | ared              | x = Bit is unkr | nown  |

|               |                                      |                                  |                |                  |                   |                 |       |

| bit 15        | CMSIDL: Cor                          | nparator Stop                    | in Idle Mode b | pit              |                   |                 |       |

|               |                                      |                                  |                |                  | ice enters Idle n | node            |       |

|               |                                      | -                                | -              | s in Idle mode   |                   |                 |       |

| bit 14-11     | Unimplemen                           | ted: Read as '                   | 0'             |                  |                   |                 |       |

| bit 10        | -                                    | parator 3 Even                   |                |                  |                   |                 |       |

|               |                                      | or event occur                   |                |                  |                   |                 |       |

| L:1 0         | -                                    | or event did no                  |                |                  |                   |                 |       |

| bit 9         | -                                    | parator 2 Even<br>or event occur |                |                  |                   |                 |       |

|               |                                      | or event did no                  |                |                  |                   |                 |       |

| bit 8         | -                                    | parator 1 Even                   |                |                  |                   |                 |       |

|               |                                      | or event occur                   |                |                  |                   |                 |       |

|               |                                      | or event did no                  |                |                  |                   |                 |       |

| bit 7-3       | Unimplemen                           | ted: Read as '                   | 0'             |                  |                   |                 |       |

| bit 2         | C3OUT: Com                           | parator 3 Outp                   | ut Status bit  |                  |                   |                 |       |

|               | When CPOL :                          |                                  |                |                  |                   |                 |       |

|               | 1 = VIN+ > VIN<br>0 = VIN+ < VIN     |                                  |                |                  |                   |                 |       |

|               | When CPOL :                          |                                  |                |                  |                   |                 |       |

|               | 1 = VIN + < VIN                      |                                  |                |                  |                   |                 |       |

|               | 0 = VIN+ > VIN                       | ۷-                               |                |                  |                   |                 |       |

| bit 1         | C2OUT: Com                           | parator 2 Outp                   | ut Status bit  |                  |                   |                 |       |

|               | When CPOL :                          |                                  |                |                  |                   |                 |       |

|               | 1 = VIN+ > VIN<br>0 = VIN+ < VIN     |                                  |                |                  |                   |                 |       |

|               | When CPOL :                          |                                  |                |                  |                   |                 |       |

|               | 1 = VIN + < VIN                      |                                  |                |                  |                   |                 |       |

|               | 0 = VIN + > VIN                      | N-                               |                |                  |                   |                 |       |

| bit 0         | C1OUT: Com                           | parator 1 Outp                   | ut Status bit  |                  |                   |                 |       |

|               | When CPOL:                           |                                  |                |                  |                   |                 |       |

|               | 1 = VIN+ > VIN<br>0 = VIN+ < VIN     |                                  |                |                  |                   |                 |       |

|               |                                      | •                                |                |                  |                   |                 |       |

|               | When CPOL :                          | = 1:                             |                |                  |                   |                 |       |

|               | <u>When CPOL</u> :<br>1 = VIN+ < VIN |                                  |                |                  |                   |                 |       |

#### REGISTER 25-1: CMSTAT: COMPARATOR STATUS REGISTER

## dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

## **REGISTER 26-9:** ALRMVAL (WHEN ALRMPTR<1:0> = 01): ALARM WEEKDAY AND HOURS VALUE REGISTER<sup>(1)</sup>

| <b></b> |     |     |     |     |       |       |       |

|---------|-----|-----|-----|-----|-------|-------|-------|

| bit 15  |     |     |     |     |       |       | bit 8 |

| _       | _   | —   | —   |     | WDAY2 | WDAY1 | WDAY0 |

| U-0     | U-0 | U-0 | U-0 | U-0 | R/W-x | R/W-x | R/W-x |

| U-0   | U-0 | R/W-x | R/W-x  | R/W-x | R/W-x | R/W-x  | R/W-x |

|-------|-----|-------|--------|-------|-------|--------|-------|

| —     | —   | HRTEN | N<1:0> |       | HRON  | E<3:0> |       |

| bit 7 |     |       |        |       |       |        | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-11 | Unimplemented: Read as '0'                                       |

|-----------|------------------------------------------------------------------|

| bit 10-8  | WDAY<2:0>: Binary Coded Decimal Value of Weekday Digit bits      |

|           | Contains a value from 0 to 6.                                    |

| bit 7-6   | Unimplemented: Read as '0'                                       |

| bit 5-4   | HRTEN<1:0>: Binary Coded Decimal Value of Hour's Tens Digit bits |

|           | Contains a value from 0 to 2.                                    |

| bit 3-0   | HRONE<3:0>: Binary Coded Decimal Value of Hour's Ones Digit bits |

|           | Contains a value from 0 to 9.                                    |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

NOTES:

| TABLE 29-2: | CONFIGURATION BITS DESCRIPTION |                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|-------------|--------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit Field   | Register                       | RTSP Effect                                                                                                | Description                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| GSSK<1:0>   | FGS                            | Immediate                                                                                                  | General Segment Key bits<br>These bits must be set to '00' if GWRP = 1 and GSS = 1. These bits must<br>be set to '11' for any other value of the GWRP and GSS bits.<br>Any mismatch between either the GWRP or GSS bits, and the GSSK bits<br>(as described above), will result in code protection becoming enabled for<br>the General Segment. A Flash bulk erase will be required to unlock the<br>device. |  |  |  |

| GSS         | FGS                            | Immediate                                                                                                  | General Segment Code-Protect bit<br>1 = User program memory is not code-protected<br>0 = User program memory is code-protected                                                                                                                                                                                                                                                                               |  |  |  |

| GWRP        | FGS                            | Immediate                                                                                                  | General Segment Write-Protect bit<br>1 = User program memory is not write-protected<br>0 = User program memory is write-protected                                                                                                                                                                                                                                                                            |  |  |  |

| IESO        | FOSCSEL                        | Immediate                                                                                                  | <ul> <li>Two-Speed Oscillator Start-up Enable bit</li> <li>1 = Start-up device with FRC, then automatically switch to the user-selected oscillator source when ready</li> <li>0 = Start-up device with user-selected oscillator source</li> </ul>                                                                                                                                                            |  |  |  |

| FNOSC<2:0>  | FOSCSEL                        | If clock switch<br>is enabled, the<br>RTSP effect is<br>on any device<br>Reset;<br>otherwise,<br>immediate | Initial Oscillator Source Selection bits<br>111 = Internal Fast RC (FRC) Oscillator with Postscaler<br>110 = Internal Fast RC (FRC) Oscillator with Divide-by-16<br>101 = LPRC Oscillator<br>100 = Secondary (LP) Oscillator<br>011 = Primary (XT, HS, EC) Oscillator with PLL<br>010 = Primary (XT, HS, EC) Oscillator<br>001 = Internal Fast RC (FRC) Oscillator with PLL<br>000 = FRC Oscillator          |  |  |  |

| FCKSM<1:0>  | FOSC                           | Immediate                                                                                                  | Clock Switching Mode bits<br>1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled<br>01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled<br>00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled                                                                                                                                                            |  |  |  |

| IOL1WAY     | FOSC                           | Immediate                                                                                                  | Peripheral Pin Select Configuration bit<br>1 = Allows only one reconfiguration<br>0 = Allows multiple reconfigurations                                                                                                                                                                                                                                                                                       |  |  |  |

| OSCIOFNC    | FOSC                           | Immediate                                                                                                  | OSC2 Pin Function bit (except in XT and HS modes)<br>1 = OSC2 is the clock output<br>0 = OSC2 is the general purpose digital I/O pin                                                                                                                                                                                                                                                                         |  |  |  |

| POSCMD<1:0> | FOSC                           | Immediate                                                                                                  | Primary Oscillator Mode Select bits<br>11 = Primary Oscillator is disabled<br>10 = HS Crystal Oscillator mode<br>01 = XT Crystal Oscillator mode<br>00 = EC (External Clock) mode                                                                                                                                                                                                                            |  |  |  |

| FWDTEN      | FWDT                           | Immediate                                                                                                  | <ul> <li>Watchdog Timer Enable bit</li> <li>1 = Watchdog Timer is always enabled (LPRC Oscillator cannot be disabled.<br/>Clearing the SWDTEN bit in the RCON register has no effect.)</li> <li>0 = Watchdog Timer is enabled/disabled by user software (LPRC can be disabled by clearing the SWDTEN bit in the RCON register.)</li> </ul>                                                                   |  |  |  |

#### TABLE 29-2: CONFIGURATION BITS DESCRIPTION

**Note 1:** BOR should always be enabled for proper operation (BOREN = 1).

**2:** This register can only be modified when code protection and write protection are disabled for both the General and Auxiliary Segments (APL = 1, AWRP = 1, APLK = 0, GSS = 1, GWRP = 1 and GSSK = 0).

#### 32.1 DC Characteristics

#### TABLE 32-1: OPERATING MIPS VS. VOLTAGE

|                | Voo Bongo                 | Tomp Bongo            | Maximum MIPS                                                       |  |  |

|----------------|---------------------------|-----------------------|--------------------------------------------------------------------|--|--|

| Characteristic | VDD Range<br>(in Volts)   | Temp Range<br>(in °C) | dsPIC33EPXXX(GP/MC/MU)806/810/<br>814 and PIC24EPXXX(GP/GU)810/814 |  |  |

| _              | 2.95V-3.6V <sup>(1)</sup> | -40°C to +85°C        | 70                                                                 |  |  |

| —              | 2.95V-3.6V <sup>(1)</sup> | -40°C to +125°C       | 60                                                                 |  |  |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules: ADC, Comparator and DAC will have degraded performance. Device functionality is tested but not characterized. Refer to Parameter BO10 in Table 32-11 for the minimum and maximum BOR values.

#### TABLE 32-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                           | Symbol | Min. | Тур.        | Max. | Unit |

|--------------------------------------------------------------------------------------------------|--------|------|-------------|------|------|

| Industrial Temperature Devices                                                                   |        |      |             |      |      |

| Operating Junction Temperature Range                                                             | TJ     | -40  | —           | +125 | °C   |

| Operating Ambient Temperature Range                                                              | TA     | -40  | —           | +85  | °C   |

| Extended Temperature Devices                                                                     |        |      |             |      |      |

| Operating Junction Temperature Range                                                             | TJ     | -40  | _           | +140 | °C   |

| Operating Ambient Temperature Range                                                              | TA     | -40  | —           | +125 | °C   |

| Power Dissipation:<br>Internal chip power dissipation:<br>$PINT = VDD \times (IDD - \Sigma IOH)$ | PD     |      | Pint + Pi/c | D    | W    |

| I/O Pin Power Dissipation:<br>$I/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$          |        |      |             |      |      |

| Maximum Allowed Power Dissipation                                                                | PDMAX  | (    | TJ — ΤΑ)/θ. | JA   | W    |

#### TABLE 32-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                                       | Symbol | Тур. | Max. | Unit | Notes |

|------------------------------------------------------|--------|------|------|------|-------|

| Package Thermal Resistance, 64-pin QFN (9x9 mm)      | θJA    | 28   |      | °C/W | 1     |

| Package Thermal Resistance, 64-pin TQFP (10x10 mm)   | θJA    | 47   | _    | °C/W | 1     |

| Package Thermal Resistance, 100-pin TQFP (12x12 mm)  | θJA    | 43   | —    | °C/W | 1     |

| Package Thermal Resistance, 100-pin TQFP (14x14 mm)  | θJA    | 43   | _    | °C/W | 1     |

| Package Thermal Resistance, 121-pin TFBGA (10x10 mm) | θJA    | 40   | _    | °C/W | 1     |

| Package Thermal Resistance, 144-pin LQFP (20x20 mm)  | θJA    | 33   | —    | °C/W | 1     |

| Package Thermal Resistance, 144-pin TQFP (16x16 mm)  | θJA    | 33   | _    | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

|        |        |                                   |           | otherwi   | se stated<br>rature | <b>i)</b><br>-40°C ≤ | TA $\leq$ +85°C for Industrial<br>TA $\leq$ +125°C for Extended |

|--------|--------|-----------------------------------|-----------|-----------|---------------------|----------------------|-----------------------------------------------------------------|

| Param. | Symbol | Characteristic                    | Min.      | Тур.      | Max.                | Units                | Conditions                                                      |

|        |        | ADC Accuracy (12-Bit Mod          | de) – Mea | sureme    | nts with            | Externa              | I VREF+/VREF-                                                   |

| AD20a  | Nr     | Resolution                        | 12        | 2 Data Bi | ts                  | bits                 |                                                                 |

| AD21a  | INL    | Integral Nonlinearity             | -2        |           | +2                  | LSb                  | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V                |

| AD22a  | DNL    | Differential Nonlinearity         | >-1       | -         | <1                  | LSb                  | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V                |

| AD23a  | Gerr   | Gain Error                        | 1.25      | 1.5       | 3                   | LSb                  | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V                |

| AD24a  | EOFF   | Offset Error                      | 1.25      | 1.52      | 2                   | LSb                  | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V                |

| AD25a  | —      | Monotonicity                      | _         | _         | _                   | _                    | Guaranteed <sup>(2)</sup>                                       |

|        |        | ADC Accuracy (12-Bit Mo           | de) – Mea | asureme   | ents with           | Interna              | I VREF+/VREF-                                                   |

| AD20a  | Nr     | Resolution                        | 1:        | 2 data bi | ts                  | bits                 |                                                                 |

| AD21a  | INL    | Integral Nonlinearity             | -2        | _         | +2                  | LSb                  | VINL = AVSS = 0V, AVDD = 3.6V                                   |

| AD22a  | DNL    | Differential Nonlinearity         | >-1       | _         | <1                  | LSb                  | VINL = AVSS = 0V, AVDD = 3.6V                                   |

| AD23a  | Gerr   | Gain Error                        | 2         | 3         | 7                   | LSb                  | VINL = AVSS = 0V, AVDD = 3.6V                                   |

| AD24a  | EOFF   | Offset Error                      | 2         | 3         | 5                   | LSb                  | VINL = AVSS = 0V, AVDD = 3.6V                                   |

| AD25a  | —      | Monotonicity                      | _         |           |                     | _                    | Guaranteed <sup>(2)</sup>                                       |

|        |        | Dynamie                           | c Perform | nance (1  | 2-Bit Mo            | de)                  |                                                                 |

| AD30a  | THD    | Total Harmonic Distortion         | —         | _         | -75                 | dB                   |                                                                 |

| AD31a  | SINAD  | Signal to Noise and<br>Distortion | 68.5      | 69.5      | _                   | dB                   |                                                                 |

| AD32a  | SFDR   | Spurious Free Dynamic<br>Range    | 80        | -         | _                   | dB                   |                                                                 |

| AD33a  | Fnyq   | Input Signal Bandwidth            | —         | _         | 250                 | kHz                  |                                                                 |

| AD34a  | ENOB   | Effective Number of Bits          | 11.09     | 11.3      | _                   | bits                 |                                                                 |

#### TABLE 32-55: ADC MODULE SPECIFICATIONS (12-BIT MODE)

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules: ADC, Comparator and DAC will have degraded performance. Device functionality is tested but not characterized. Refer to Parameter BO10 in Table 32-11 for the minimum and maximum BOR values.

2: The Analog-to-Digital conversion result never decreases with an increase in input voltage and has no missing codes.

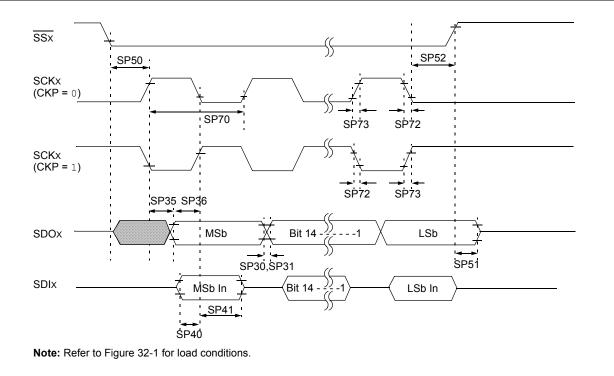

100-Lead Plastic Thin Quad Flatpack (PF) - 14x14x1 mm Body 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                           | N                | <b>ILLIMETER</b> | S        |      |

|---------------------------|------------------|------------------|----------|------|

| Dimension                 | Dimension Limits |                  |          | MAX  |

| Contact Pitch             | E                |                  | 0.50 BSC |      |

| Contact Pad Spacing       | C1               |                  | 15.40    |      |

| Contact Pad Spacing       | C2               |                  | 15.40    |      |

| Contact Pad Width (X100)  | X1               |                  |          | 0.30 |

| Contact Pad Length (X100) | Y1               |                  |          | 1.50 |

| Distance Between Pads     | G                | 0.20             |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2110B

### Revision C (May 2011)

This revision includes minor typographical and formatting changes throughout the data sheet text.

These global changes were implemented:

- All instances of VDDCORE have been removed.

- References to remappable pins have been updated to clarify output-only pins (RPn) versus input/output pins (RPIn).

- The minimum VDD value was changed from 2.7V to 3.0V to adhere to the current BOR specification.

The major changes are referenced by their respective section in Table A-2.

| Section Name                                                                                               | Update Description                                                                                                                                |

|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| High-Performance, 16-bit Digital<br>Signal Controllers and                                                 | Removed the shading for D+/RG2 and D-/RG3 pin designations in all pin diagrams, as these pins are not 5V tolerant.                                |