Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detalls                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART, USB OTG            |

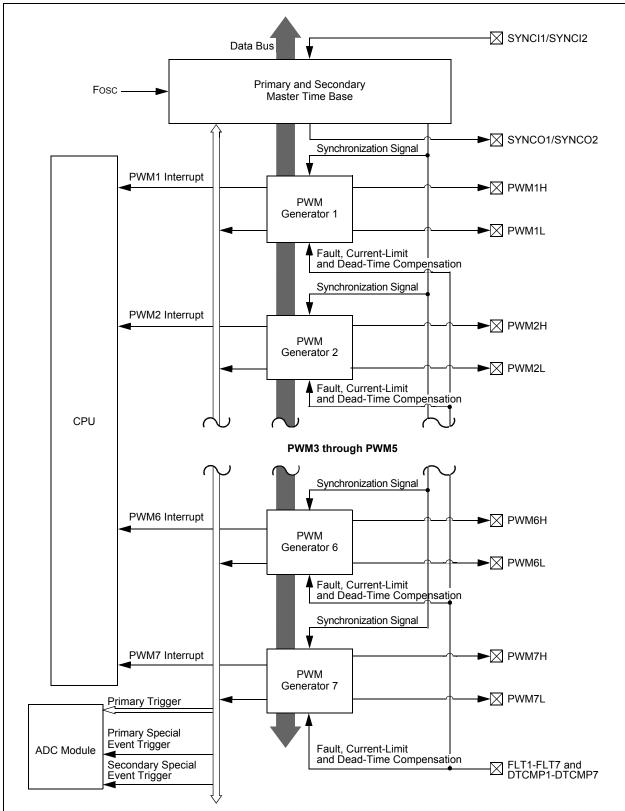

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 122                                                                              |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 12K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 32x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 144-LQFP                                                                         |

| Supplier Device Package    | 144-LQFP (20x20)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256mu814-e-pl |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

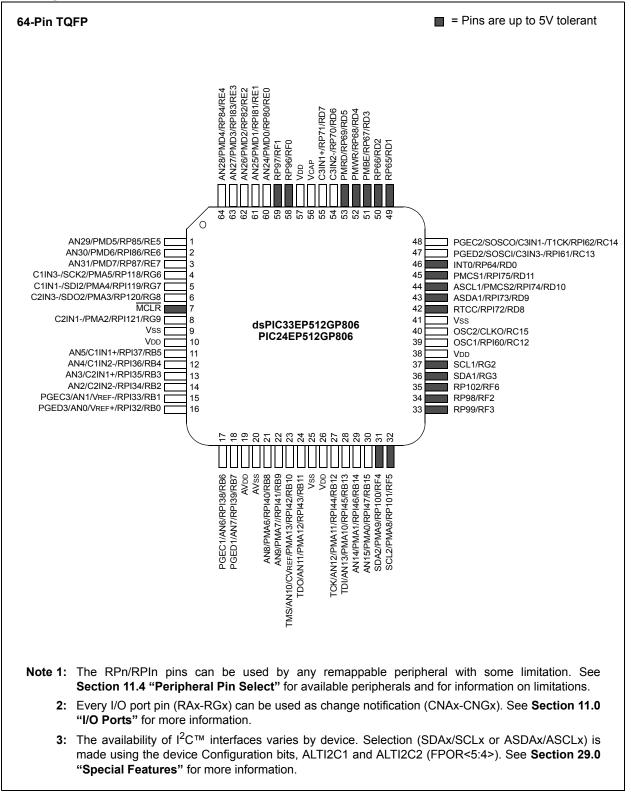

# Pin Diagrams (Continued)

| REGISTER            | 3-2: CURU                                                          | CON: CORE C                                                                                   |                                              | SISIEK                   |                           |                        |                   |

|---------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------|--------------------------|---------------------------|------------------------|-------------------|

| R/W-0               | U-0                                                                | R/W-0                                                                                         | R/W-0                                        | R/W-0                    | R-0                       | R-0                    | R-0               |

| VAR                 | —                                                                  | US<1                                                                                          | :0>(1)                                       | EDT <sup>(1,2)</sup>     |                           | DL<2:0> <sup>(1)</sup> |                   |

| bit 15              |                                                                    |                                                                                               |                                              |                          |                           |                        | bi                |

| R/W-0               | R/W-0                                                              | R/W-1                                                                                         | R/W-0                                        | R/C-0                    | R-0                       | R/W-0                  | R/W-0             |

| SATA <sup>(1)</sup> | SATB <sup>(1)</sup>                                                | SATDW <sup>(1)</sup>                                                                          | ACCSAT <sup>(1)</sup>                        | IPL3 <sup>(3)</sup>      | SFA                       | RND <sup>(1)</sup>     | IF <sup>(1)</sup> |

| bit 7               |                                                                    |                                                                                               |                                              |                          |                           |                        | bi                |

| Legend:             |                                                                    |                                                                                               |                                              |                          |                           |                        |                   |

| R = Readab          | le bit                                                             | W = Writable                                                                                  | bit                                          | U = Unimplem             | ented bit, rea            | id as '0'              |                   |

| -n = Value a        | t POR                                                              | '1' = Bit is set                                                                              |                                              | '0' = Bit is clea        | ared                      | x = Bit is unkne       | own               |

| oit 14              | 1 = Variable<br>0 = Fixed exe<br>Unimpleme                         | le Exception Pro<br>exception proces<br>ception process<br>nted: Read as '<br>SP Multiply Uns | essing is enabl<br>ing is enabled<br>0'      | ed                       |                           |                        |                   |

| bit 13-12           | 11 = Reserve<br>10 = DSP er<br>01 = DSP er<br>00 = DSP er          | ed<br>ngine multiplies<br>ngine multiplies<br>ngine multiplies                                | are mixed-sigr<br>are unsigned<br>are signed | 1                        |                           |                        |                   |

| bit 11              |                                                                    | O Loop Termination<br>es executing DO<br>t                                                    |                                              |                          | eration                   |                        |                   |

| bit 10-8            | DL<2:0>: DC                                                        | Loop Nesting I                                                                                | _evel Status bi                              | ts <sup>(1)</sup>        |                           |                        |                   |

|                     | 111 <b>= 7</b> do <b>i</b>                                         | oops are active                                                                               |                                              |                          |                           |                        |                   |

|                     | •                                                                  |                                                                                               |                                              |                          |                           |                        |                   |

|                     | •                                                                  |                                                                                               |                                              |                          |                           |                        |                   |

|                     | •                                                                  |                                                                                               |                                              |                          |                           |                        |                   |

|                     | $001 = 1$ DO $ _{000}$                                             | oop is active                                                                                 |                                              |                          |                           |                        |                   |

| bit 7               |                                                                    | A Saturation En                                                                               | able bit <sup>(1)</sup>                      |                          |                           |                        |                   |

|                     |                                                                    | ator A saturation                                                                             |                                              |                          |                           |                        |                   |

|                     |                                                                    | ator A saturatio                                                                              |                                              |                          |                           |                        |                   |

| bit 6               |                                                                    | 3 Saturation En                                                                               |                                              |                          |                           |                        |                   |

|                     |                                                                    | ator B saturatio<br>ator B saturatio                                                          |                                              |                          |                           |                        |                   |

| bit 5               | SATDW: Dat                                                         | ta Space Write f                                                                              | rom DSP Engi                                 | ne Saturation I          | Enable bit <sup>(1)</sup> |                        |                   |

|                     | •                                                                  | ice write saturat<br>ice write saturat                                                        |                                              |                          |                           |                        |                   |

| bit 4               | ACCSAT: Ac                                                         | cumulator Satu                                                                                | ration Mode S                                | elect bit <sup>(1)</sup> |                           |                        |                   |

|                     |                                                                    | uration (super sa<br>uration (normal s                                                        |                                              |                          |                           |                        |                   |

| bit 3               | IPL3: CPU Ir                                                       | nterrupt Priority                                                                             | Level Status b                               | it 3 <sup>(3)</sup>      |                           |                        |                   |

|                     |                                                                    | errupt Priority Le<br>errupt Priority Le                                                      |                                              |                          |                           |                        |                   |

|                     | <sup>-</sup> his bit is availabl<br><sup>-</sup> his bit is always |                                                                                               | PXXX(GP/MC                                   | /MU)806/810/8            | 14 devices or             | nly.                   |                   |

#### DECISTED 3-2 COPCON- COPE CONTROL PECISTER

3: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

### 4.6 Modulo Addressing (dsPIC33EPXXXMU806/810/814 Devices Only)

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either data or Program Space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into Program Space) and Y data spaces. Modulo Addressing can operate on any W Register Pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction as there are certain restrictions on the buffer start address (for incrementing buffers), or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

#### 4.6.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

| Note: | Y space Modulo Addressing EA calcula- |  |  |  |  |  |  |  |

|-------|---------------------------------------|--|--|--|--|--|--|--|

|       | tions assume word-sized data (LSb of  |  |  |  |  |  |  |  |

|       | every EA is always clear).            |  |  |  |  |  |  |  |

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

#### 4.6.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that operate with Modulo Addressing:

- If XWM = 1111, X RAGU and X WAGU Modulo Addressing is disabled.

- If YWM = 1111, Y AGU Modulo Addressing is disabled.

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X data space when XWM is set to any value other than '1111' and the XMODEN bit is set at MODCON<15>.

The Y Address Space Pointer W register (YWM) to which Modulo Addressing is to be applied is stored in MODCON<7:4>. Modulo Addressing is enabled for Y data space when YWM is set to any value other than '1111' and the YMODEN bit is set at MODCON<14>.

#### Byte MOV #0x1100, W0 Address MOV W0, XMODSRT ;set modulo start address #0x1163, W0 0x1100 MOV WO, MODEND MOV ;set modulo end address MOV #0x8001, W0 W0, MODCON ;enable W1, X AGU for modulo MOV MOV #0x0000, W0 ;WO holds buffer fill value MOV #0x1110, W1 ;point W1 to buffer 0x1163 ;fill the 50 buffer locations DO AGAIN, #0x31 MOV WO, [W1++] ;fill the next location AGAIN: INC WO, WO ; increment the fill value Start Addr = 0x1100 End Addr = 0x1163Length = 0x0032 words

#### FIGURE 4-10: MODULO ADDRESSING OPERATION EXAMPLE

# REGISTER 8-12: DMARQC: DMA REQUEST COLLISION STATUS REGISTER (CONTINUED)

| bit 2 | RQCOL2: Channel 2 Transfer Request Collision Flag bit                                                                     |

|-------|---------------------------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = User FORCE and interrupt-based request collision detected</li><li>0 = No request collision detected</li></ul> |

| bit 1 | RQCOL1: Channel 1 Transfer Request Collision Flag bit                                                                     |

|       | 1 = User FORCE and interrupt-based request collision detected                                                             |

|       | 0 = No request collision detected                                                                                         |

| bit 0 | RQCOL0: Channel 0 Transfer Request Collision Flag bit                                                                     |

|       | 1 = User FORCE and interrupt-based request collision detected                                                             |

|       | 0 = No request collision detected                                                                                         |

- bit 1 I2C2MD: I2C2 Module Disable bit

- 1 = I2C2 module is disabled

- 0 = I2C2 module is enabled

- bit 0 AD2MD: ADC2 Module Disable bit

- 1 = ADC2 module is disabled

- 0 = ADC2 module is enabled

- Note 1: This bit is available in dsPIC33EPXXX(MC/MU)806/810/814 devices only.

| Function                | RPnR<5:0> | Output Name                                     |

|-------------------------|-----------|-------------------------------------------------|

| U4TX                    | 011101    | RPn tied to UART4 Transmit                      |

| U4RTS                   | 011110    | RPn tied to UART4 Ready-to-Send                 |

| SDO3                    | 011111    | RPn tied to SPI3 Data Output                    |

| SCK3                    | 100000    | RPn tied to SPI3 Clock Output                   |

| SS3                     | 100001    | RPn tied to SPI3 Slave Select                   |

| SDO4                    | 100010    | RPn tied to SPI4 Data Output                    |

| SCK4                    | 100011    | RPn tied to SPI4 Clock Output                   |

| SS4                     | 100100    | RPn tied to SPI4 Slave Select                   |

| OC9                     | 100101    | RPn tied to Output Compare 9 Output             |

| OC10                    | 100110    | RPn tied to Output Compare 10 Output            |

| OC11                    | 100111    | RPn tied to Output Compare 11 Output            |

| OC12                    | 101000    | RPn tied to Output Compare 12 Output            |

| OC13                    | 101001    | RPn tied to Output Compare 13 Output            |

| OC14                    | 101010    | RPn tied to Output Compare 14 Output            |

| OC15                    | 101011    | RPn tied to Output Compare 15 Output            |

| OC16                    | 101100    | RPn tied to Output Compare 16 Output            |

| SYNCO1 <sup>(1)</sup>   | 101101    | RPn tied to PWM Primary Time Base Sync Output   |

| SYNCO2 <sup>(1)</sup>   | 101110    | RPn tied to PWM Secondary Time Base Sync Output |

| QEI1CCMP <sup>(1)</sup> | 101111    | RPn tied to QEI 1 Counter Comparator Output     |

| QEI2CCMP <sup>(1)</sup> | 110000    | RPn tied to QEI 2 Counter Comparator Output     |

| REFCLK                  | 110001    | RPn tied to Reference Clock Output              |

# TABLE 11-3: OUTPUT SELECTION FOR REMAPPABLE PINS (RPn) (CONTINUED)

Note 1: This function is available in dsPIC33EPXXX(MC/MU)806/810/814 devices only.

#### REGISTER 11-12: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| U-0          | R/W-0                        | R/W-0                                                                        | R/W-0                      | R/W-0             | R/W-0           | R/W-0           | R/W-0       |

|--------------|------------------------------|------------------------------------------------------------------------------|----------------------------|-------------------|-----------------|-----------------|-------------|

| _            |                              |                                                                              |                            | OCFBR<6:0>        |                 |                 |             |

| bit 15       |                              |                                                                              |                            |                   |                 |                 | bit 8       |

| U-0          | R/W-0                        | R/W-0                                                                        | R/W-0                      | R/W-0             | R/W-0           | R/W-0           | R/W-0       |

|              |                              | 10110                                                                        |                            | OCFAR<6:0>        |                 | 10110           | 1010 0      |

| bit 7        |                              |                                                                              |                            |                   |                 |                 | bit 0       |

| Legend:      |                              |                                                                              |                            |                   |                 |                 |             |

| R = Readab   | le bit                       | W = Writable                                                                 | bit                        | U = Unimplem      | nented bit, rea | ad as '0'       |             |

| -n = Value a | t POR                        | '1' = Bit is set                                                             |                            | '0' = Bit is clea | ared            | x = Bit is unkr | nown        |

|              | (see Table 11-               | -2 for input pin                                                             |                            |                   | oo oonoop       | <u>g</u>        | In Pin bits |

|              | 1111111 = In<br>0000001 = In | -2 for input pin<br>aput tied to RP1<br>aput tied to CMI<br>aput tied to Vss | selection nun<br>I27<br>P1 |                   |                 |                 |             |

| bit 7        | 1111111 = In                 | put tied to RP1                                                              | selection nun<br>127<br>P1 |                   |                 |                 |             |

| U-0                               | R/W-0        | R/W-0                                                  | R/W-0   | R/W-0             | R/W-0           | R/W-0           | R/W-0   |

|-----------------------------------|--------------|--------------------------------------------------------|---------|-------------------|-----------------|-----------------|---------|

|                                   | 10,00-0      | 10,00-0                                                | 10.00-0 | IC16R<6:0>        | 10/00-0         | 1000-0          | 10.00-0 |

| bit 15                            |              |                                                        |         |                   |                 |                 | bit 8   |

|                                   |              |                                                        |         |                   |                 |                 |         |

| U-0                               | R/W-0        | R/W-0                                                  | R/W-0   | R/W-0             | R/W-0           | R/W-0           | R/W-0   |

|                                   |              |                                                        |         | IC15R<6:0>        |                 |                 |         |

| bit 7                             |              |                                                        |         |                   |                 |                 | bit C   |

| Legend:                           |              |                                                        |         |                   |                 |                 |         |

| R = Readable bit W = Writable bit |              |                                                        |         | U = Unimplem      | nented bit, rea | d as '0'        |         |

| -n = Value a                      | at POR       | '1' = Bit is set                                       |         | '0' = Bit is clea | ared            | x = Bit is unkr | nown    |

|                                   |              | nput tied to RP <sup>-</sup>                           | 127     |                   |                 |                 |         |

|                                   |              | nput tied to CM                                        |         |                   |                 |                 |         |

| bit 7                             | 0000000 = Ir | nput tied to CM<br>nput tied to Vss<br>nted: Read as ' | ;       |                   |                 |                 |         |

## REGISTER 11-36: RPINR36: PERIPHERAL PIN SELECT INPUT REGISTER 36

# REGISTER 16-23: LEBDLYx: LEADING-EDGE BLANKING DELAY REGISTER x

| U-0             | U-0   | U-0              | U-0   | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |

|-----------------|-------|------------------|-------|-----------------------------------------|-------|-------|-------|--|

| —               | —     | —                | _     | LEB<11:8>                               |       |       |       |  |

| bit 15          |       |                  |       |                                         |       |       | bit 8 |  |

|                 |       |                  |       |                                         |       |       |       |  |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |

|                 |       |                  | LEE   | <7:0>                                   |       |       |       |  |

| bit 7           |       |                  |       |                                         |       |       | bit 0 |  |

|                 |       |                  |       |                                         |       |       |       |  |

| Legend:         |       |                  |       |                                         |       |       |       |  |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimplemented bit, read as '0'      |       |       |       |  |

| -n = Value at F | POR   | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |

bit 15-12 Unimplemented: Read as '0'

bit 11-0 LEB<11:0>: Leading-Edge Blanking Delay for Current-Limit and Fault Inputs bits

NOTES:

## REGISTER 20-1: UxMODE: UARTx MODE REGISTER (CONTINUED)

| bit 4   | URXINV: Receive Polarity Inversion bit                                                                                                                                             |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = UxRX  Idle state is '0'                                                                                                                                                        |

|         | 0 = UxRX Idle state is '1'                                                                                                                                                         |

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                                                    |

|         | <ul> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul> |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                         |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul>                      |

| bit 0   | STSEL: Stop Bit Selection bit                                                                                                                                                      |

|         | 1 = Two Stop bits                                                                                                                                                                  |

|         | 0 = One Stop bit                                                                                                                                                                   |

- **Note 1:** Refer to **Section 17. "UART**" (DS70582) in the *"dsPIC33E/PIC24E Family Reference Manual"* for information on enabling the UARTx module for receive or transmit operation.

- 2: This feature is only available for the 16x BRG mode (BRGH = 0).

# 21.2 Modes of Operation

The ECANx module can operate in one of several operation modes selected by the user. These modes include:

- Initialization mode

- Disable mode

- Normal Operation mode

- · Listen Only mode

- Listen All Messages mode

- · Loopback mode

Modes are requested by setting the REQOP<2:0> bits (CxCTRL1<10:8>). Entry into a mode is Acknowledged by monitoring the OPMODE<2:0> bits (CxCTRL1<7:5>). The module does not change the mode and the OPMODE bits until a change in mode is acceptable, generally during bus Idle time, which is defined as at least 11 consecutive recessive bits.

# 21.3 ECAN Resources

Many useful resources related to ECAN are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en554310

### 21.3.1 KEY RESOURCES

- Section 21. "Enhanced Controller Area Network (ECAN™)" (DS70353) in the "dsPIC33E/PIC24E Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related *"dsPIC33E/PIC24E Family Reference Manual"* Sections

- Development Tools

# dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

| U-0           | U-0           | R-0                                   | R-0              | R-0              | R-0                | R-0             | R-0   |

|---------------|---------------|---------------------------------------|------------------|------------------|--------------------|-----------------|-------|

| —             |               | TXBO                                  | TXBP             | RXBP             | TXWAR              | RXWAR           | EWARN |

| bit 15        |               |                                       |                  |                  |                    |                 | bit   |

| R/C-0         | R/C-0         | R/C-0                                 | U-0              | R/C-0            | R/C-0              | R/C-0           | R/C-0 |

| IVRIF         | WAKIF         | ERRIF                                 | _                | FIFOIF           | RBOVIF             | RBIF            | TBIF  |

| bit 7         |               |                                       |                  |                  |                    |                 | bit ( |

| Legend:       |               | C = Writable                          | hit but only '0' | can be writte    | n to clear the bit | ŀ               |       |

| R = Readabl   | e bit         | W = Writable                          |                  |                  | mented bit, read   |                 |       |

| -n = Value at | POR           | '1' = Bit is set                      |                  | '0' = Bit is cle |                    | x = Bit is unkr | nown  |

|               |               |                                       | o.1              |                  |                    |                 |       |

| bit 15-14     | -             | nted: Read as '                       |                  | - :4             |                    |                 |       |

| bit 13        |               | smitter in Error<br>ter is in Bus Off |                  | JIL              |                    |                 |       |

|               |               | ter is not in Bus                     |                  |                  |                    |                 |       |

| bit 12        | TXBP: Trans   | smitter in Error                      | State Bus Pas    | sive bit         |                    |                 |       |

|               | 1 = Transmit  | ter is in Bus Pa                      | ssive state      |                  |                    |                 |       |

|               |               | ter is not in Bus                     |                  |                  |                    |                 |       |

| bit 11        |               | eiver in Error Sta                    |                  | e bit            |                    |                 |       |

|               |               | r is in Bus Pass<br>r is not in Bus P |                  |                  |                    |                 |       |

| bit 10        |               | Insmitter in Erro                     |                  | na hit           |                    |                 |       |

|               |               | ter is in Error W                     |                  | ig sit           |                    |                 |       |

|               |               | ter is not in Erro                    | •                | te               |                    |                 |       |

| bit 9         | RXWAR: Re     | ceiver in Error                       | State Warning    | bit              |                    |                 |       |

|               |               | is in Error War<br>is not in Error '  |                  |                  |                    |                 |       |

| bit 8         | EWARN: Tra    | ansmitter or Red                      | eiver in Error   | State Warning    | bit                |                 |       |

|               |               | ter or Receiver<br>ter or Receiver    |                  | Ų                |                    |                 |       |

| bit 7         |               | d Message Inte                        |                  |                  | ,                  |                 |       |

|               | 1 = Interrupt | Request has of<br>Request has no      | ccurred          |                  |                    |                 |       |

| bit 6         |               | Wake-up Activ                         |                  | aq bit           |                    |                 |       |

|               |               | Request has o                         |                  |                  |                    |                 |       |

|               | 0 = Interrupt | Request has n                         | ot occurred      |                  |                    |                 |       |

| bit 5         |               |                                       |                  | ources in CxIN   | TF<13:8> regis     | ter)            |       |

|               |               | Request has o                         |                  |                  |                    |                 |       |

| bit 4         | -             | Request has ne<br>nted: Read as '     |                  |                  |                    |                 |       |

| bit 3         | -             | D Almost Full In                      |                  | t                |                    |                 |       |

|               | 1 = Interrupt | Request has o                         | ccurred          |                  |                    |                 |       |

| <b>h</b> # 0  | •             | Request has no                        |                  | l- 14            |                    |                 |       |

| bit 2         |               | Buffer Overflor                       |                  | g dit            |                    |                 |       |

|               |               | Request has of<br>Request has no      |                  |                  |                    |                 |       |

| bit 1         | -             | uffer Interrupt Fl                    |                  |                  |                    |                 |       |

|               |               | Request has o                         | -                |                  |                    |                 |       |

|               | -             | Request has no                        |                  |                  |                    |                 |       |

| bit 0         |               | ffer Interrupt Fla                    | -                |                  |                    |                 |       |

|               |               | Request has o                         |                  |                  |                    |                 |       |

| REGISTER 22-12: | UxOTGIR: USB OTG INTERRUPT STATUS REGISTER (HOS | Γ MODE ONLY) |

|-----------------|-------------------------------------------------|--------------|

|-----------------|-------------------------------------------------|--------------|

| U-0    | U-0          | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 |  |

|--------|--------------|-----|-----|-----|-----|-----|-----|--|

| —      | —            | —   | —   | —   | —   | _   | —   |  |

| bit 15 | bit 15 bit 8 |     |     |     |     |     |     |  |

| R/K-0, HS | U-0 | R/K-0, HS |

|-----------|-----------|-----------|-----------|-----------|-----------|-----|-----------|

| IDIF      | T1MSECIF  | LSTATEIF  | ACTVIF    | SESVDIF   | SESENDIF  | —   | VBUSVDIF  |

| bit 7     |           |           |           |           |           |     | bit 0     |

| Legend:           | U = Unimplemented bit, read as '0' |                            |                    |  |  |

|-------------------|------------------------------------|----------------------------|--------------------|--|--|

| R = Readable bit  | K = Write '1' to clear bit         | HS = Hardware Settable bit |                    |  |  |

| -n = Value at POR | '1' = Bit is set                   | '0' = Bit is cleared       | x = Bit is unknown |  |  |

| bit 15-8 | Unimplemented: Read as '0'                                                                                                                                 |  |  |  |  |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| bit 7    | IDIF: ID State Change Indicator bit                                                                                                                        |  |  |  |  |  |

|          | 1 = Change in ID state is detected                                                                                                                         |  |  |  |  |  |

|          | 0 = No ID state change                                                                                                                                     |  |  |  |  |  |

| bit 6    | T1MSECIF: 1 Millisecond Timer bit                                                                                                                          |  |  |  |  |  |

|          | 1 = The 1 millisecond timer has expired                                                                                                                    |  |  |  |  |  |

|          | 0 = The 1 millisecond timer has not expired                                                                                                                |  |  |  |  |  |

| bit 5    | LSTATEIF: Line State Stable Indicator bit                                                                                                                  |  |  |  |  |  |

|          | 1 = USB line state (as defined by the SE0 and JSTATE bits) has been stable for 1 ms, but different from last time                                          |  |  |  |  |  |

|          | 0 = USB line state has not been stable for 1 ms                                                                                                            |  |  |  |  |  |

| bit 4    | ACTVIF: Bus Activity Indicator bit                                                                                                                         |  |  |  |  |  |

|          | 1 = Activity on the D+/D- lines or VBUS is detected                                                                                                        |  |  |  |  |  |

|          | 0 = No activity on the D+/D- lines or VBUS is detected                                                                                                     |  |  |  |  |  |

| bit 3    | SESVDIF: Session Valid Change Indicator bit                                                                                                                |  |  |  |  |  |

|          | <ul> <li>1 = VBUS has crossed VA_SESS_VLD (as defined in the USB OTG Specification)<sup>(1)</sup></li> <li>0 = VBUS has not crossed VA_SESS_VLD</li> </ul> |  |  |  |  |  |

| bit 2    | SESENDIF: B-Device VBUS Change Indicator bit                                                                                                               |  |  |  |  |  |

|          | 1 = VBUS change on B-device is detected; VBUS has crossed VB_SESS_END (as defined in the USB OTG Specification) <sup>(1)</sup>                             |  |  |  |  |  |

|          | 0 = VBUS has not crossed VA_SESS_END                                                                                                                       |  |  |  |  |  |

| bit 1    | Unimplemented: Read as '0'                                                                                                                                 |  |  |  |  |  |

| bit 0    | VBUSVDIF: A-Device VBUS Change Indicator bit                                                                                                               |  |  |  |  |  |

|          | 1 = VBUS change on A-device is detected; VBUS has crossed VA_VBUS_VLD (as defined in the USB OTG Specification) <sup>(1)</sup>                             |  |  |  |  |  |

|          | 0 = No VBUS change on A-device is detected                                                                                                                 |  |  |  |  |  |

|          |                                                                                                                                                            |  |  |  |  |  |

**Note 1:** VBUS threshold crossings may be either rising or falling.

# 25.2 Comparator Control Registers

| R/W-0         | U-0                                                                                           | U-0              | U-0           | U-0                                     | R-0              | R-0      | R-0   |  |

|---------------|-----------------------------------------------------------------------------------------------|------------------|---------------|-----------------------------------------|------------------|----------|-------|--|

| CMSIDL        |                                                                                               | _                |               |                                         | C3EVT            | C2EVT    | C1EVT |  |

| bit 15        | I                                                                                             | l .              |               | 1                                       | I                | 1        | bit 8 |  |

|               |                                                                                               |                  |               |                                         |                  |          |       |  |

| U-0           | U-0                                                                                           | U-0              | U-0           | U-0                                     | R-0              | R-0      | R-0   |  |

| _             | _                                                                                             | —                | _             |                                         | C3OUT            | C2OUT    | C10UT |  |

| bit 7         |                                                                                               |                  |               | 4                                       | I                | 1        | bit ( |  |

|               |                                                                                               |                  |               |                                         |                  |          |       |  |

| Legend:       |                                                                                               |                  |               |                                         |                  |          |       |  |

| R = Readable  | e bit                                                                                         | W = Writable     | bit           | U = Unimpler                            | mented bit, read | 1 as '0' |       |  |

| -n = Value at | POR                                                                                           | '1' = Bit is set |               | '0' = Bit is cleared x = Bit is unknown |                  |          | nown  |  |

|               |                                                                                               |                  |               |                                         |                  |          |       |  |

| bit 15        | CMSIDL: Cor                                                                                   | nparator Stop i  | n Idle Mode b | oit                                     |                  |          |       |  |

|               | 1 = Discontinues operation of all comparators when device enters Idle mode                    |                  |               |                                         |                  |          |       |  |

|               |                                                                                               | s operation of a | -             | s in Idle mode                          |                  |          |       |  |

| bit 14-11     | •                                                                                             | ted: Read as '   |               |                                         |                  |          |       |  |

| bit 10        | C3EVT: Comparator 3 Event Status bit                                                          |                  |               |                                         |                  |          |       |  |

|               | <ul> <li>1 = Comparator event occurred</li> <li>0 = Comparator event did not occur</li> </ul> |                  |               |                                         |                  |          |       |  |

| -             |                                                                                               |                  |               |                                         |                  |          |       |  |

| bit 5         | <b>C2EVT:</b> Comparator 2 Event Status bit<br>1 = Comparator event occurred                  |                  |               |                                         |                  |          |       |  |

|               | 0 = Comparator event did not occur                                                            |                  |               |                                         |                  |          |       |  |

| bit 8         | C1EVT: Comparator 1 Event Status bit                                                          |                  |               |                                         |                  |          |       |  |

|               | 1 = Comparator event occurred                                                                 |                  |               |                                         |                  |          |       |  |

|               | 0 = Comparator event did not occur                                                            |                  |               |                                         |                  |          |       |  |

| bit 7-3       | Unimplemented: Read as '0'                                                                    |                  |               |                                         |                  |          |       |  |

| bit 2         | C3OUT: Comparator 3 Output Status bit                                                         |                  |               |                                         |                  |          |       |  |

|               | $\frac{\text{When CPOL} = 0:}{1 = \text{VIN} + \text{VIN}}$                                   |                  |               |                                         |                  |          |       |  |

|               | 1 = VIN+ > VIN- $0 = VIN+ < VIN-$                                                             |                  |               |                                         |                  |          |       |  |

|               | When $CPOL = 1$ :                                                                             |                  |               |                                         |                  |          |       |  |

|               | 1 = VIN + < VIN                                                                               |                  |               |                                         |                  |          |       |  |

|               | 0 = VIN + > VIN                                                                               |                  |               |                                         |                  |          |       |  |

| bit 1         | C2OUT: Comparator 2 Output Status bit                                                         |                  |               |                                         |                  |          |       |  |

|               | $\frac{\text{When CPOL} = 0}{1 = \text{VIN} + \text{VIN}}$                                    |                  |               |                                         |                  |          |       |  |

|               | 0 = VIN + < VIN -                                                                             |                  |               |                                         |                  |          |       |  |

|               | When CPOL = 1:                                                                                |                  |               |                                         |                  |          |       |  |

|               | $1 = V_{IN+} < V_{IN-}$                                                                       |                  |               |                                         |                  |          |       |  |

| h: 1 0        | 0 = VIN + > VIN                                                                               |                  |               |                                         |                  |          |       |  |

| bit 0         |                                                                                               |                  |               |                                         |                  |          |       |  |

|               | <u>When CPOL</u> :<br>1 = VIN+ > VIN                                                          |                  |               |                                         |                  |          |       |  |

|               | 0 = VIN + < VIN -                                                                             |                  |               |                                         |                  |          |       |  |

|               | When CPOL = 1:                                                                                |                  |               |                                         |                  |          |       |  |

|               | 1 = VIN + < VIN                                                                               |                  |               |                                         |                  |          |       |  |

|               | 0 = VIN + > VIN                                                                               | N-               |               |                                         |                  |          |       |  |

#### REGISTER 25-1: CMSTAT: COMPARATOR STATUS REGISTER

#### REGISTER 25-3: CMxMSKSRC: COMPARATOR x MASK SOURCE SELECT CONTROL REGISTER (CONTINUED)

- bit 3-0 SELSRCA<3:0>: Mask A Input Select bits 1111 = FLT4 1110 = FLT2 1101 = PWM7H 1100 = PWM7L 1011 = PWM6H

- 1010 = PWM6L 1001 = PWM5H 1000 = PWM5L 0111 = PWM4H 0110 = PWM4L 0101 = PWM3H 0100 = PWM3L 0011 = PWM2H 0010 = PWM2L

0001 = PWM1H 0000 = PWM1L

DS70616G-page 444

# Revision C (May 2011)

This revision includes minor typographical and formatting changes throughout the data sheet text.

These global changes were implemented:

- All instances of VDDCORE have been removed.

- References to remappable pins have been updated to clarify output-only pins (RPn) versus input/output pins (RPIn).

- The minimum VDD value was changed from 2.7V to 3.0V to adhere to the current BOR specification.

The major changes are referenced by their respective section in Table A-2.

| Section Name                                                                                               | Update Description                                                                                                                                |

|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| High-Performance, 16-bit Digital<br>Signal Controllers and                                                 | Removed the shading for D+/RG2 and D-/RG3 pin designations in all pin diagrams, as these pins are not 5V tolerant.                                |

| Microcontrollers                                                                                           | References to remappable pins have been updated to clarify input/output pins (RPn) and input-only pins (RPIn).                                    |

| Section 2.0 "Guidelines for<br>Getting Started with 16-bit Digital                                         | Add information on the VUSB pin in Section 2.1 "Basic Connection Requirements".                                                                   |

| Signal Controllers and<br>Microcontrollers"                                                                | Updated the title of Section 2.3 to <b>Section 2.3 "CPU Logic Filter Capacitor</b><br><b>Connection (VCAP)"</b> and modified the first paragraph. |

| Section 3.0 "CPU"                                                                                          | Added Note 2 to the Programmer's Model Register Descriptions (see Table 3-1).                                                                     |

| Section 4.0 "Memory<br>Organization"                                                                       | Added the CANCKS bit (CxCTRL1<11>) to the ECAN1 and ECAN 2 Register Maps (see Table 4-26 and Table 4-29).                                         |

|                                                                                                            | Added the SBOREN bit (RCON<13>) to the System Control Register Map (see Table 4-43).                                                              |

|                                                                                                            | Added Note 1 to the PORTG Register maps (see Table 4-60 and Table 4-61).                                                                          |

|                                                                                                            | Updated the Page Description for DSRPAG = 0x1FF and DSRPAG = 0x200 in Table 4-66.                                                                 |

|                                                                                                            | Updated the second paragraph of <b>Section 4.2.9</b> "EDS Arbitration and Bus Master Priority".                                                   |

|                                                                                                            | Updated the last note box in Section 4.2.10 "Software Stack".                                                                                     |

| Section 5.0 "Flash Program                                                                                 | Updated the equation formatting in Section 5.3 "Programming Operations".                                                                          |

| Memory"                                                                                                    | Added the Non-Volatile Memory Upper Address (NVMADRU) and Non-Volatile Memory Address (NVMADR) registers (see Register 5-2 and Register 5-3).     |

| Section 6.0 "Resets"                                                                                       | Added Security Reset to the Reset System Block Diagram (see Figure 6-1).                                                                          |

|                                                                                                            | Added the SBOREN bit (RCON<13>) and Notes 3 and 4 to the Reset Control register (see Register 6-1).                                               |

| Section 11.0 "I/O Ports"                                                                                   | References to remappable pins have been updated to clarify input/output pins (RPn) and input-only pins (RPIn).                                    |

|                                                                                                            | Added the new column, Input/Output, to Input Pin Selection for Selectable Input Sources (see Table 11-2).                                         |

| Section 17.0 "Quadrature<br>Encoder Interface (QEI) Module<br>(dsPIC33EPXXXMU806/810/814<br>Devices Only)" | Updated the definition for the INTHLD<31:0> bits (see Register 17-19 and Register 17-20).                                                         |

#### TABLE A-2: MAJOR SECTION UPDATES

© 2009-2012 Microchip Technology Inc.