Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 24K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 24x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-VQFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512gp806-i-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

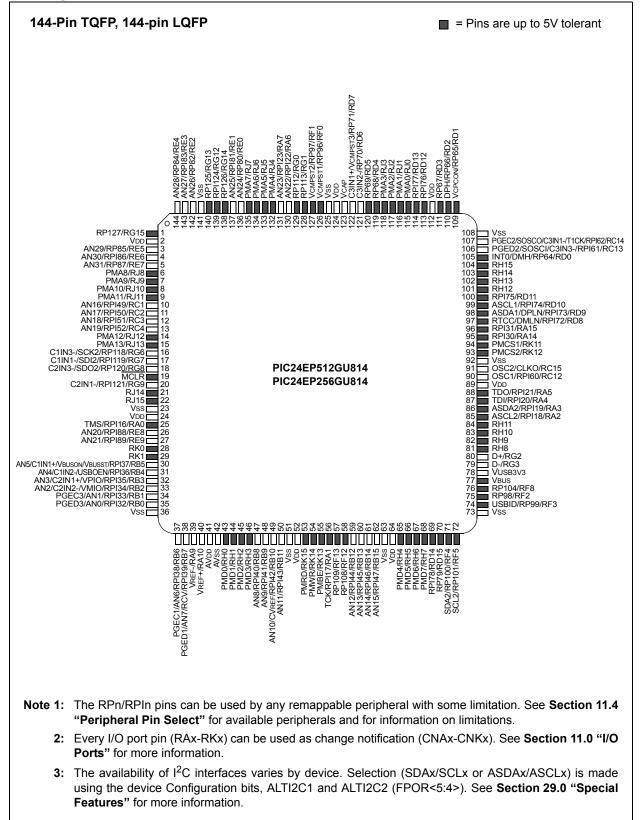

FIGURE 4-6: DATA MEMORY MAP FOR PIC24EP256GU810/814 DEVICES WITH 28-KBYTE RAM

#### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

| bit 4 | MATHERR: Math Error Status bit               |

|-------|----------------------------------------------|

|       | 1 = Math error trap has occurred             |

|       | 0 = Math error trap has not occurred         |

|       |                                              |

| bit 3 | ADDRERR: Address Error Trap Status bit       |

|       | 1 = Address error trap has occurred          |

|       | 0 = Address error trap has not occurred      |

| bit 2 | STKERR: Stack Error Trap Status bit          |

|       | 1 = Stack error trap has occurred            |

|       | 0 = Stack error trap has not occurred        |

| bit 1 | OSCFAIL: Oscillator Failure Trap Status bit  |

|       | 1 = Oscillator failure trap has occurred     |

|       | 0 = Oscillator failure trap has not occurred |

| bit 0 | Unimplemented: Read as '0'                   |

Note 1: This bit is available on dsPIC33EPXXX(GP/MC/MU)806/810/814 devices only.

## REGISTER 8-12: DMARQC: DMA REQUEST COLLISION STATUS REGISTER (CONTINUED)

| bit 2 | RQCOL2: Channel 2 Transfer Request Collision Flag bit                                                                     |

|-------|---------------------------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = User FORCE and interrupt-based request collision detected</li><li>0 = No request collision detected</li></ul> |

| bit 1 | RQCOL1: Channel 1 Transfer Request Collision Flag bit                                                                     |

|       | 1 = User FORCE and interrupt-based request collision detected                                                             |

|       | 0 = No request collision detected                                                                                         |

| bit 0 | RQCOL0: Channel 0 Transfer Request Collision Flag bit                                                                     |

|       | 1 = User FORCE and interrupt-based request collision detected                                                             |

|       | 0 = No request collision detected                                                                                         |

| U-0           | U-0        | U-0              | U-0             | U-0              | U-0              | U-0                | R/W-0     |

|---------------|------------|------------------|-----------------|------------------|------------------|--------------------|-----------|

| _             | —          | —                | _               | —                | —                | -                  | PLLDIV<8> |

| bit 15        |            |                  |                 |                  |                  |                    | bit 8     |

|               |            |                  |                 |                  |                  |                    |           |

| R/W-0         | R/W-0      | R/W-1            | R/W-1           | R/W-0            | R/W-0            | R/W-0              | R/W-0     |

|               |            |                  | PLLD            | IV<7:0>          |                  |                    |           |

| bit 7         |            |                  |                 |                  |                  |                    | bit 0     |

|               |            |                  |                 |                  |                  |                    |           |

| Legend:       |            |                  |                 |                  |                  |                    |           |

| R = Readab    | le bit     | W = Writable     | bit             | U = Unimpler     | mented bit, read | d as '0'           |           |

| -n = Value at | t POR      | '1' = Bit is set |                 | '0' = Bit is cle | ared             | x = Bit is unknown |           |

|               |            |                  |                 |                  |                  |                    |           |

| bit 15-9      | Unimpleme  | nted: Read as '  | 0'              |                  |                  |                    |           |

| bit 8-0       | PLLDIV<8:0 | >: PLL Feedbad   | ck Divisor bits | (also denoted    | as 'M', PLL mu   | ltiplier)          |           |

|               | 111111111  | = 513            |                 |                  |                  |                    |           |

|               | •          |                  |                 |                  |                  |                    |           |

|               | •          |                  |                 |                  |                  |                    |           |

|               | •          |                  |                 |                  |                  |                    |           |

|               | 000110000  | = 50 (default)   |                 |                  |                  |                    |           |

|               | •          |                  |                 |                  |                  |                    |           |

|               | •          |                  |                 |                  |                  |                    |           |

|               | 000000010  | = 3              |                 |                  |                  |                    |           |

|               | 000000000  | - 2              |                 |                  |                  |                    |           |

# REGISTER 9-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER<sup>(1)</sup>

Note 1: This register is reset only on a Power-on Reset (POR).

## REGISTER 10-5: PMD5: PERIPHERAL MODULE DISABLE CONTROL REGISTER 5 (CONTINUED)

| bit 3 | OC12MD: OC12 Module Disable bit |

|-------|---------------------------------|

|       | 1 = OC12 module is disabled     |

|       | 0 = OC12 module is enabled      |

| bit 2 | OC11MD: OC11 Module Disable bit |

|       | 1 = OC11 module is disabled     |

|       | 0 = OC11 module is enabled      |

| bit 1 | OC10MD: OC10 Module Disable bit |

|       | 1 = OC10 module is disabled     |

|       | 0 = OC10 module is enabled      |

| bit 0 | OC9MD: OC9 Module Disable bit   |

|       | 1 = OC9 module is disabled      |

|       | 0 = OC9 module is enabled       |

| U-0                | R/W-0                                    | R/W-0                                                                                                          | R/W-0                                        | R/W-0             | R/W-0           | R/W-0           | R/W-0    |

|--------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------|-------------------|-----------------|-----------------|----------|

| —                  |                                          |                                                                                                                |                                              | T3CKR<6:0>        |                 |                 |          |

| bit 15             |                                          |                                                                                                                |                                              |                   |                 |                 | bit      |

|                    |                                          |                                                                                                                |                                              |                   |                 |                 |          |

| U-0                | R/W-0                                    | R/W-0                                                                                                          | R/W-0                                        | R/W-0             | R/W-0           | R/W-0           | R/W-0    |

| —                  |                                          |                                                                                                                |                                              | T2CKR<6:0>        |                 |                 |          |

| bit 7              |                                          |                                                                                                                |                                              |                   |                 |                 | bit      |

|                    |                                          |                                                                                                                |                                              |                   |                 |                 |          |

| Legend:            |                                          |                                                                                                                |                                              |                   |                 |                 |          |

| R = Readab         | le bit                                   | W = Writable                                                                                                   | bit                                          | U = Unimplem      | nented bit, rea | id as '0'       |          |

| -n = Value a       | It POR                                   | '1' = Bit is set                                                                                               |                                              | '0' = Bit is clea | ared            | x = Bit is unkr | nown     |

|                    | T3CKR<6:0><br>(see Table 11              | <ul> <li>hted: Read as '</li> <li>Assign Timer</li> <li>I-2 for input pin</li> <li>nput tied to RP'</li> </ul> | 3 External Clo<br>selection num              | · /               | e Correspond    | ding RPn/RPIn F | 'in bits |

| bit 15<br>bit 14-8 | T3CKR<6:0><br>(see Table 11<br>1111111 = | Assign Timer<br>I-2 for input pin<br>nput tied to RP<br>nput tied to CM                                        | 3 External Clo<br>selection num<br>127<br>P1 | · /               | e Correspond    | ding RPn/RPIn F | 'in bits |

|                    | T3CKR<6:0><br>(see Table 11<br>1111111 = | Assign Timer<br>I-2 for input pin<br>nput tied to RP <sup>2</sup>                                              | 3 External Clo<br>selection num<br>127<br>P1 | · /               | e Correspond    | ding RPn/RPIn F | Pin bits |

#### REGISTER 11-4: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

#### REGISTER 11-30: RPINR30: PERIPHERAL PIN SELECT INPUT REGISTER 30

| U-0                               | U-0   | U-0              | U-0   | U-0                                     | U-0   | U-0   | U-0   |

|-----------------------------------|-------|------------------|-------|-----------------------------------------|-------|-------|-------|

| -                                 | —     | —                | _     | —                                       | —     | —     | —     |

| bit 15                            |       |                  |       |                                         |       |       | bit 8 |

|                                   |       |                  |       |                                         |       |       |       |

| U-0                               | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

| —                                 |       |                  |       | SS3R<6:0>                               |       |       |       |

| bit 7                             | •     |                  |       |                                         |       |       | bit 0 |

|                                   |       |                  |       |                                         |       |       |       |

| Legend:                           |       |                  |       |                                         |       |       |       |

| R = Readable bit W = Writable bit |       |                  | bit   | U = Unimplemented bit, read as '0'      |       |       |       |

| -n = Value at P                   | OR    | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |

| <b>•</b>                          |       |                  |       |                                         |       |       |       |

#### bit 15-7 Unimplemented: Read as '0'

bit 6-0

SS3R<6:0>: Assign SPI3 Slave Select Input (SS3) to the Corresponding RPn/RPIn Pin bits (see Table 11-2 for input pin selection numbers)

1111111 = Input tied to RP127

#### **REGISTER 17-7: VELXCNT: VELOCITY COUNTER x REGISTER**

| R/W-0                                                   | R/W-0 | R/W-0 | R/W-0           | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|---------------------------------------------------------|-------|-------|-----------------|------------------------------------|-------|-------|-------|

|                                                         |       |       | VELCI           | NT<15:8>                           |       |       |       |

| bit 15                                                  |       |       |                 |                                    |       |       | bit 8 |

|                                                         |       |       |                 |                                    |       |       |       |

| R/W-0                                                   | R/W-0 | R/W-0 | R/W-0           | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|                                                         |       |       | VELC            | NT<7:0>                            |       |       |       |

| bit 7                                                   |       |       |                 |                                    |       |       | bit 0 |

|                                                         |       |       |                 |                                    |       |       |       |

| Legend:                                                 |       |       |                 |                                    |       |       |       |

| R = Readable bit W = Writable bit                       |       |       | bit             | U = Unimplemented bit, read as '0' |       |       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared |       |       | x = Bit is unki | nown                               |       |       |       |

bit 15-0 VELCNT<15:0>: Velocity Counter bits

#### REGISTER 17-8: INDXxCNTH: INDEX COUNTER x HIGH WORD REGISTER

| R/W-0  | R/W-0          | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|--------|----------------|-------|-------|-------|-------|-------|-------|--|--|--|

|        | INDXCNT<31:24> |       |       |       |       |       |       |  |  |  |

| bit 15 |                |       |       |       |       |       | bit 8 |  |  |  |

| R/W-0          | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|----------------|-------|-------|-------|-------|-------|-------|-------|--|--|--|

| INDXCNT<23:16> |       |       |       |       |       |       |       |  |  |  |

| bit 7          |       |       |       |       |       |       |       |  |  |  |

| Legend:           |                  |                                             |                    |  |  |

|-------------------|------------------|---------------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | able bit U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                        | x = Bit is unknown |  |  |

bit 15-0 INDXCNT<31:16>: High Word Used to Form 32-Bit Index Counter Register (INDXxCNT) bits

#### REGISTER 17-9: INDXxCNTL: INDEX COUNTER x LOW WORD REGISTER

| R/W-0                                 | R/W-0                                                           | R/W-0 | R/W-0        | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|---------------------------------------|-----------------------------------------------------------------|-------|--------------|------------------------------------|-------|-------|-------|

|                                       |                                                                 |       | INDXC        | NT<15:8>                           |       |       |       |

| bit 15                                |                                                                 |       |              |                                    |       |       | bit 8 |

|                                       |                                                                 |       |              |                                    |       |       |       |

| R/W-0                                 | R/W-0                                                           | R/W-0 | R/W-0        | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|                                       |                                                                 |       | INDXC        | NT<7:0>                            |       |       |       |

| bit 7                                 |                                                                 |       |              |                                    |       |       | bit 0 |

|                                       |                                                                 |       |              |                                    |       |       |       |

| Legend:                               |                                                                 |       |              |                                    |       |       |       |

| R = Readable bit W = Writable bit U = |                                                                 |       | U = Unimplen | U = Unimplemented bit, read as '0' |       |       |       |

| -n = Value at P                       | at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |       |              | nown                               |       |       |       |

bit 15-0 INDXCNT<15:0>: Low Word Used to Form 32-Bit Index Counter Register (INDXxCNT) bits

#### REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1 (CONTINUED)

- bit 4-2 SPRE<2:0>: Secondary Prescale bits (Master mode)<sup>(3)</sup>

- 111 = Secondary prescale 1:1 110 = Secondary prescale 2:1

- •

- •

- .

- 000 = Secondary prescale 8:1

- bit 1-0 **PPRE<1:0>:** Primary Prescale bits (Master mode)<sup>(3)</sup>

- 11 = Primary prescale 1:1

- 10 = Primary prescale 4:1

- 01 = Primary prescale 16:1

- 00 = Primary prescale 64:1

- **Note 1:** The CKE bit is not used in the Framed SPIx modes. Program this bit to '0' for Framed SPIx modes (FRMEN = 1).

- 2: This bit must be cleared when FRMEN = 1.

- **3:** Do not set both primary and secondary prescalers to a value of 1:1.

- 4: The SMP bit must be set only after setting the MSTEN bit. The SMP bit remains cleared if MSTEN = 0.

| R/W-0           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W-0                                                                                                                                                                                                  | U-0                                                                    | R/W-0, HC                                                          | R/W-0                                    | R-0               | R-1          |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------|-------------------|--------------|

| UTXISEL1        | UTXINV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | UTXISEL0                                                                                                                                                                                               | —                                                                      | UTXBRK                                                             | UTXEN <sup>(1)</sup>                     | UTXBF             | TRMT         |

| bit 15          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                        |                                                                        |                                                                    |                                          |                   | bit 8        |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                        |                                                                        |                                                                    |                                          |                   |              |

| R/W-0           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W-0                                                                                                                                                                                                  | R-1                                                                    | R-0                                                                | R-0                                      | R/C-0             | R-0          |

| URXISE          | EL<1:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ADDEN                                                                                                                                                                                                  | RIDLE                                                                  | PERR                                                               | FERR                                     | OERR              | URXDA        |

| bit 7           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                        |                                                                        |                                                                    |                                          |                   | bit (        |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                        |                                                                        |                                                                    |                                          |                   |              |

| Legend:         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | HC = Hardware Clearable bit                                                                                                                                                                            |                                                                        | C = Clearabl                                                       |                                          |                   |              |

| R = Readable    | bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | W = Writable bit                                                                                                                                                                                       |                                                                        | •                                                                  | mented bit, rea                          | id as '0'         |              |

| -n = Value at F | POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | '1' = Bit is set                                                                                                                                                                                       |                                                                        | '0' = Bit is cle                                                   | eared                                    | x = Bit is unk    | nown         |

| bit 15,13       | <ul> <li>11 = Reservent</li> <li>10 = Interrupt</li> <li>11 = Interrupt</li> <li>11 = Interrupt</li> <li>11 = Interrupt</li> <li>12 = Interrupt</li> <li>13 = Interrupt</li> <li>14 = Interrupt</li> &lt;</ul> | <b>0&gt;:</b> UARTx Transed; do not use of when a charact to buffer becomes of when the last cons are complete of when a character oper character oper character oper oper oper oper oper oper oper op | er is transferre<br>empty<br>haracter is shit<br>d<br>ter is transferr | d to the Transn<br>fted out of the <sup>-</sup><br>ed to the Trans | nit Shift Registe<br>Transmit Shift F    | Register; all tra | ansmit       |

| bit 14          | $\frac{\text{If IREN = 0:}}{1 = \text{UxTX IdI}}$ $0 = \text{UxTX IdI}$ $\frac{\text{If IREN = 1:}}{1 = \text{IrDA end}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                        | state is '1'                                                           | bit                                                                |                                          |                   |              |

| bit 12          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | nted: Read as '0'                                                                                                                                                                                      |                                                                        |                                                                    |                                          |                   |              |

| bit 11          | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ARTx Transmit Br                                                                                                                                                                                       | eak bit                                                                |                                                                    |                                          |                   |              |

|                 | <ul> <li>1 = Sends Sync Break on next transmission – Start bit, followed by twelve '0' bits, followed by Stop bit; cleared by hardware upon completion</li> <li>0 = Sync Break transmission is disabled or completed</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                        |                                                                        |                                                                    |                                          |                   |              |

| bit 10          | <ul> <li>UTXEN: UARTx Transmit Enable bit<sup>(1)</sup></li> <li>1 = Transmit is enabled, UxTX pin is controlled by UARTx</li> <li>0 = Transmit is disabled, any pending transmission is aborted and the buffer is reset; UxTX pin controlled by port</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                        |                                                                        |                                                                    |                                          |                   |              |

| bit 9           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RTx Transmit Buff                                                                                                                                                                                      | er Full Status I                                                       | oit (read-only)                                                    |                                          |                   |              |

|                 | 1 = Transmit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                        |                                                                        |                                                                    | can be written                           |                   |              |

| bit 8           | 1 = Transmit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | mit Shift Register<br>Shift Register is e<br>Shift Register is                                                                                                                                         | empty and tran                                                         | smit buffer is e                                                   |                                          |                   | as completed |

| bit 7-6         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0>: UARTx Rece                                                                                                                                                                                         |                                                                        |                                                                    |                                          | •                 |              |

|                 | 11 = Interrup<br>10 = Interrup<br>0x = Interrup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ot is set on UxRSI<br>ot is set on UxRSI<br>ot is set when any<br>receive buffer has                                                                                                                   | R transfer mak<br>R transfer mak<br>y character is                     | ing the receive<br>ing the receive<br>received and t               | e buffer full (i.e.<br>e buffer 3/4 full | (i.e., has 3 dat  | a characters |

**Note 1:** Refer to **Section 17. "UART"** (DS70582) in the *"dsPIC33E/PIC24E Family Reference Manual"* for information on enabling the UARTx module for transmit operation.

#### REGISTER 22-14: UxIR: USB INTERRUPT STATUS REGISTER (DEVICE MODE ONLY)