Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 24K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 24x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512gp806-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin<br>Number | Full Pin Name                          | Pin<br>Number | Full Pin Name                        |

|---------------|----------------------------------------|---------------|--------------------------------------|

| A1            | AN28/PWM3L/PMD4/RP84/RE4               | E8            | RPI31/RA15                           |

| 12            | AN27/PWM2H/PMD3/RPI83/RE3              | E9            | RTCC/DMLN/RPI72/RD8                  |

| A3            | RP125/RG13                             | E10           | ASDA1 <sup>(3)</sup> /DPLN/RPI73/RD9 |

| A4            | AN24/PWM1L/PMD0/RP80/RE0               | E11           | RPI30/RA14                           |

| A5            | RP112/RG0                              | F1            | MCLR                                 |

| A6            | VCMPST2/RP97/RF1                       | F2            | C2IN3-/SDO2/PMA3/RP120/RG8           |

| A7            | VDD                                    | F3            | C2IN1-/PMA2/RPI121/RG9               |

| A8            | No Connect                             | F4            | C1IN1-/SDI2/PMA4/RPI119/RG7          |

| A9            | RPI76/RD12                             | F5            | Vss                                  |

| A10           | DPH/RP66/RD2                           | F6            | No Connect                           |

| A11           | VCPCON/RP65/RD1                        | F7            | No Connect                           |

| B1            | No Connect                             | F8            | VDD                                  |

| B2            | RP127/RG15                             | F9            | OSC1/RPI60/RC12                      |

| B3            | AN26/PWM2L/PMD2/RP82/RE2               | F10           | Vss                                  |

| B4            | AN25/PWM1H/PMD1/RPI81/RE1              | F11           | OSC2/CLKO/RC15                       |

| B5            | AN23/RPI23/RA7                         | G1            | AN20/RPI88/RE8                       |

| B6            | VCMPST1/RP96/RF0                       | G2            | AN21/RPI89/RE9                       |

| B7            | VCAP                                   | G3            | TMS/RPI16/RA0                        |

| B8            | PMRD/RP69/RD5                          | G4            | No Connect                           |

| B9            | PMBE/RP67/RD3                          | G5            | VDD                                  |

| 310           | Vss                                    | G6            | Vss                                  |

| 11            | PGEC2/SOSCO/C3IN1-/T1CK/RPI62/RC14     | G7            | Vss                                  |

| C1            | AN30/PWM4L/PMD6/RPI86/RE6              | G8            | No Connect                           |

| 2             | VDD                                    | G9            | TDO/RPI21/RA5                        |

| C3            | RPI124/RG12                            | G10           | ASDA2 <sup>(3)</sup> /RPI19/RA3      |

| C4            | RP126/RG14                             | G11           | TDI/RPI20/RA4                        |

| C5            | AN22/RPI22/RA6                         | H1            | AN5/C1IN1+/VBUSON/VBUSST/RPI37/RB5   |

| C6            | No Connect                             | H2            | AN4/C1IN2-/USBOEN/RPI36/RB4          |

| C7            | C3IN1+/VCMPST3/RP71/RD7                | H3            | No Connect                           |

| C8            | PMWR/RP68/RD4                          | H4            | No Connect                           |

| C9            | No Connect                             | H5            | No Connect                           |

| C10           | PGED2/SOSCI/C3IN3-/RPI61/RC13          | H6            | VDD                                  |

| C11           | PMCS1/RPI75/RD11                       | H7            | No Connect                           |

| D1            | AN16/PWM5L/RPI49/RC1                   | H8            | VBUS                                 |

| D2            | AN31/PWM4H/PMD7/RP87/RE7               | H9            | VUSB3V3                              |

| D3            | AN29/PWM3H/PMD5/RP85/RE5               | H10           | D+/RG2 <sup>(4)</sup>                |

| D4            | No Connect                             | H11           | ASCL2 <sup>(3)</sup> /RPI18/RA2      |

| D5            | No Connect                             | J1            | AN3/C2IN1+/VPIO/RPI35/RB3            |

| D6            | No Connect                             | J2            | AN2/C2IN2-/VMIO/RPI34/RB2            |

| D7            | C3IN2-/RP70/RD6                        | J3            | PGED1/AN7/RCV/RPI39/RB7              |

| D8            | RPI77/RD13                             | J4            | AVDD                                 |

| D9            | INT0/DMH/RP64/RD0                      | J5            | AN11/PMA12/RPI43/RB11                |

| 010           | No Connect                             | J6            | TCK/RPI17/RA1                        |

| 11            | ASCL1 <sup>(3)</sup> /PMCS2/RPI74/RD10 | J7            | AN12/PMA11/RPI44/RB12                |

#### TABLE 2: PIN NAMES: dsPIC33EP256MU810 AND dsPIC33EP512MU810 DEVICES<sup>(1,2)</sup>

Note 1: The RPn/RPIn pins can be used by any remappable peripheral with some limitation. See Section 11.4 "Peripheral Pin Select" for available peripherals and for information on limitations.

2: Every I/O port pin (RAx-RGx) can be used as change notification (CNAx-CNGx). See Section 11.0 "I/O Ports" for more information.

3: The availability of <sup>12</sup>C<sup>™</sup> interfaces varies by device. Selection (SDAx/SCLx or ASDAx/ASCLx) is made using the device Configuration bits, ALTI2C1 and ALTI2C2 (FPOR<5:4>). See Section 29.0 "Special Features" for more information.

The pin name is SCL1/RG2 for the dsPIC33EP512(GP/MC)806 and PIC24EP512GP806 devices.

5: The pin name is SDA1/RG3 for the dsPIC33EP512(GP/MC)806 and PIC24EP512GP806 devices.

| REGISTER 5-2: | NVMADRU: NONVOLATILE MEMORY UPPER ADDRESS REGISTER |

|---------------|----------------------------------------------------|

|---------------|----------------------------------------------------|

| U-0                                | U-0   | U-0   | U-0              | U-0             | U-0             | U-0   | U-0   |

|------------------------------------|-------|-------|------------------|-----------------|-----------------|-------|-------|

| —                                  | —     | —     | —                | —               | _               | —     | —     |

| bit 15                             | •     |       |                  |                 |                 |       | bit 8 |

|                                    |       |       |                  |                 |                 |       |       |

| R/W-x                              | R/W-x | R/W-x | R/W-x            | R/W-x           | R/W-x           | R/W-x | R/W-x |

|                                    |       |       | NVMAE            | )RU<7:0>        |                 |       |       |

| bit 7                              |       |       |                  |                 |                 |       | bit 0 |

|                                    |       |       |                  |                 |                 |       |       |

| Legend:                            |       |       |                  |                 |                 |       |       |

| R = Readable bit W = Writable bit  |       | bit   | U = Unimple      | mented bit, rea | d as '0'        |       |       |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cle | eared           | x = Bit is unkı | nown  |       |

| bit 15-8 | Unimplemented: Read as '0' |

|----------|----------------------------|

| 511 15-0 |                            |

bit 7-0 **NVMADRU<7:0>:** Nonvolatile Memory Upper Write Address bits Selects the upper 8 bits of the location to program or erase in program Flash memory. This register may be read or written by the user application.

## REGISTER 5-3: NVMADR: NONVOLATILE MEMORY ADDRESS REGISTER

| R/W-x          | R/W-x | R/W-x            | R/W-x | R/W-x        | R/W-x            | R/W-x    | R/W-x |

|----------------|-------|------------------|-------|--------------|------------------|----------|-------|

|                |       |                  | NVMA  | DR<15:8>     |                  |          |       |

| bit 15         |       |                  |       |              |                  |          | bit 8 |

|                |       |                  |       |              |                  |          |       |

| R/W-x          | R/W-x | R/W-x            | R/W-x | R/W-x        | R/W-x            | R/W-x    | R/W-x |

|                |       |                  | NVMA  | DR<7:0>      |                  |          |       |

| bit 7          |       |                  |       |              |                  |          | bit 0 |

|                |       |                  |       |              |                  |          |       |

| Legend:        |       |                  |       |              |                  |          |       |

| R = Readable I | bit   | W = Writable bit | t     | U = Unimpler | mented bit, read | d as '0' |       |

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 NVMADR<15:0>: Nonvolatile Memory Write Address bits

Selects the lower 16 bits of the location to program or erase in program Flash memory. This register may be read or written by the user application.

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

| W-0   | W-0 | W-0 | W-0   | W-0     | W-0 | W-0 | W-0   |

|-------|-----|-----|-------|---------|-----|-----|-------|

|       |     |     | NVMKE | EY<7:0> |     |     |       |

| bit 7 |     |     |       |         |     |     | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **NVMKEY<7:0>:** Key Register (write-only) bits

## dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

| U-0                | U-0                                            | U-0                                                                                                                     | U-0   | U-0                                | U-0 | U-0                | U-0   |

|--------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------|------------------------------------|-----|--------------------|-------|

| —                  | —                                              | —                                                                                                                       | —     | —                                  | —   | —                  | —     |

| bit 15             |                                                |                                                                                                                         |       |                                    |     |                    | bit 8 |

|                    |                                                |                                                                                                                         |       |                                    |     |                    |       |

| U-0                | R/W-0                                          | R/W-0                                                                                                                   | R/W-0 | U-0                                | U-0 | U-0                | U-0   |

| —                  | UAE                                            | DAE                                                                                                                     | DOOVR | —                                  | —   | —                  | —     |

| bit 7              |                                                |                                                                                                                         |       |                                    |     |                    | bit 0 |

|                    |                                                |                                                                                                                         |       |                                    |     |                    |       |

| Legend:            |                                                |                                                                                                                         |       |                                    |     |                    |       |

| R = Readable bit W |                                                | W = Writable bit                                                                                                        |       | U = Unimplemented bit, read as '0' |     |                    |       |

| -n = Value at F    | POR                                            | '1' = Bit is set                                                                                                        |       | '0' = Bit is cleared               |     | x = Bit is unknown |       |

|                    |                                                |                                                                                                                         |       |                                    |     |                    |       |

| bit 15-7           | Unimplemented: Read as '0'                     |                                                                                                                         |       |                                    |     |                    |       |

| bit 6              | UAE: USB Address Error Soft Trap Status bit    |                                                                                                                         |       |                                    |     |                    |       |

|                    | 1 = USB address error (soft) trap has occurred |                                                                                                                         |       |                                    |     |                    |       |

| bit E              |                                                | <ul> <li>USB address error (soft) trap has not occurred</li> <li>DAE: DMA Address Error Soft Trap Status bit</li> </ul> |       |                                    |     |                    |       |

| bit 5              |                                                | adress Error S                                                                                                          | -     |                                    |     |                    |       |

|                    |                                                |                                                                                                                         |       |                                    |     |                    |       |

## REGISTER 7-5: INTCON3: INTERRUPT CONTROL REGISTER 3

| bit 0    |                                                                                                                            |

|----------|----------------------------------------------------------------------------------------------------------------------------|

|          | <ul> <li>1 = DMA address error soft trap has occurred</li> <li>0 = DMA address error soft trap has not occurred</li> </ul> |

| bit 4    | DOOVR: Do Stack Overflow Soft Trap Status bit                                                                              |

|          | <ul> <li>1 = Do stack overflow soft trap has occurred</li> <li>0 = Do stack overflow soft trap has not occurred</li> </ul> |

| 1.11.0.0 |                                                                                                                            |

bit 3-0 Unimplemented: Read as '0'

## REGISTER 7-6: INTCON4: INTERRUPT CONTROL REGISTER 4

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|---------|-----|-----|-----|-----|-----|-----|-------|

| —       | —   | —   | —   | —   | —   | —   | —     |

| bit 15  |     |     |     |     |     |     | bit 8 |

|         |     |     |     |     |     |     |       |

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

| —       | —   | —   | —   | —   | —   | _   | SGHT  |

| bit 7   |     |     |     |     |     |     | bit 0 |

|         |     |     |     |     |     |     |       |

| Legend: |     |     |     |     |     |     |       |

| Logonan                           |                  |                        |                    |

|-----------------------------------|------------------|------------------------|--------------------|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

|                                   |                  |                        |                    |

bit 15-1 Unimplemented: Read as '0'

bit 0 SGHT: Software Generated Hard Trap Status bit

1 = Software generated hard trap has occurred

0 = Software generated hard trap has not occurred

# dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

## REGISTER 8-13: DMALCA: DMA LAST CHANNEL ACTIVE STATUS REGISTER

| U-0                                | U-0 | U-0          | U-0                                     | U-0                                | U-0  | U-0    | U-0   |

|------------------------------------|-----|--------------|-----------------------------------------|------------------------------------|------|--------|-------|

|                                    |     | —            | —                                       |                                    |      | —      | _     |

| bit 15                             |     |              |                                         |                                    |      |        | bit 8 |

|                                    |     |              |                                         |                                    |      |        |       |

| U-0                                | U-0 | U-0          | U-0                                     | R-1                                | R-1  | R-1    | R-1   |

| —                                  | —   | —            | —                                       |                                    | LSTC | H<3:0> |       |

| bit 7                              | •   |              |                                         |                                    |      |        | bit 0 |

|                                    |     |              |                                         |                                    |      |        |       |

| Legend:                            |     |              |                                         |                                    |      |        |       |

| R = Readable I                     | bit | W = Writable | bit                                     | U = Unimplemented bit, read as '0' |      |        |       |

| -n = Value at POR '1' = Bit is set |     |              | '0' = Bit is cleared x = Bit is unknown |                                    |      |        |       |

bit 15-4 Unimplemented: Read as '0'

| bit 3-0 | LSTCH<3:0>: Last DMAC Channel Active Status bits       |

|---------|--------------------------------------------------------|

|         | 1111 = No DMA transfer has occurred since system Reset |

|         | 1110 = Last data transfer was handled by Channel 14    |

|         | 1101 = Last data transfer was handled by Channel 13    |

|         | 1100 = Last data transfer was handled by Channel 12    |

|         | 1011 = Last data transfer was handled by Channel 11    |

|         | 1010 = Last data transfer was handled by Channel 10    |

|         | 1001 = Last data transfer was handled by Channel 9     |

|         | 1000 = Last data transfer was handled by Channel 8     |

|         | 0111 = Last data transfer was handled by Channel 7     |

|         | 0110 = Last data transfer was handled by Channel 6     |

|         | 0101 = Last data transfer was handled by Channel 5     |

|         | 0100 = Last data transfer was handled by Channel 4     |

|         | 0011 = Last data transfer was handled by Channel 3     |

|         | 0010 = Last data transfer was handled by Channel 2     |

|         | 0001 = Last data transfer was handled by Channel 1     |

|         | 0000 = Last data transfer was handled by Channel 0     |

## 10.5 Power-Saving Resources

Many useful resources related to Power-Saving features are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en554310                                        |

## 10.5.1 KEY RESOURCES

- Section 9. "Watchdog Timer and Power-Saving Modes" (DS70615) in the "dsPIC33E/PIC24E Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All related *"dsPIC33E/PIC24E Family Reference Manual"* Sections

- Development Tools

## 10.6 Special Function Registers

Seven registers, PMD1: Peripheral Module Disable Control Register 1 through PMD7: Peripheral Module Disable Control Register 7, are provided for peripheral module control.

**FIGURE 11-3:**

## 11.4.4.1 Output Mapping

In contrast to inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Like the RPINRx registers, each register contains sets of 6 bit fields, with each set associated with one RPn pin (see Register 11-44 through Register 11-51). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 11-3 and Figure 11-3).

A null output is associated with the Output Register Reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

#### **REMAPPABLE OUTPUT** FOR RPn RPnR<5:0> Default 0 U1TX Output 1 **U1RTS** Output 2 RPn Output Data . $\mathbb{N}$ . • **QEI2CCMP** Output 48 **REFCLK Output** 49

MULTIPLEXING OF

| Function     | RPnR<5:0> | Output Name                         |

|--------------|-----------|-------------------------------------|

| DEFAULT PORT | 000000    | RPn tied to Default Pin             |

| U1TX         | 000001    | RPn tied to UART1 Transmit          |

| U1RTS        | 000010    | RPn tied to UART1 Ready-to-Send     |

| U2TX         | 000011    | RPn tied to UART2 Transmit          |

| U2RTS        | 000100    | RPn tied to UART2 Ready-to-Send     |

| SDO1         | 000101    | RPn tied to SPI1 Data Output        |

| SCK1         | 000110    | RPn tied to SPI1 Clock Output       |

| SS1          | 000111    | RPn tied to SPI1 Slave Select       |

| SS2          | 001010    | RPn tied to SPI2 Slave Select       |

| CSDO         | 001011    | RPn tied to DCI Data Output         |

| CSCK         | 001100    | RPn tied to DCI Clock Output        |

| COFS         | 001101    | RPn tied to DCI FSYNC Output        |

| C1TX         | 001110    | RPn tied to CAN1 Transmit           |

| C2TX         | 001111    | RPn tied to CAN2 Transmit           |

| OC1          | 010000    | RPn tied to Output Compare 1 Output |

| OC2          | 010001    | RPn tied to Output Compare 2 Output |

| OC3          | 010010    | RPn tied to Output Compare 3 Output |

| OC4          | 010011    | RPn tied to Output Compare 4 Output |

| OC5          | 010100    | RPn tied to Output Compare 5 Output |

| OC6          | 010101    | RPn tied to Output Compare 6 Output |

| OC7          | 010110    | RPn tied to Output Compare 7 Output |

| OC8          | 010111    | RPn tied to Output Compare 8 Output |

| C1OUT        | 011000    | RPn tied to Comparator Output 1     |

| C2OUT        | 011001    | RPn tied to Comparator Output 2     |

| C3OUT        | 011010    | RPn tied to Comparator Output 3     |

| U3TX         | 011011    | RPn tied to UART3 Transmit          |

| U3RTS        | 011100    | RPn tied to UART3 Ready-to-Send     |

## TABLE 11-3: OUTPUT SELECTION FOR REMAPPABLE PINS (RPn)

**Note 1:** This function is available in dsPIC33EPXXX(MC/MU)806/810/814 devices only.

| U-0                | R/W-0                                    | R/W-0                                                                                                          | R/W-0                                        | R/W-0             | R/W-0           | R/W-0           | R/W-0    |

|--------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------|-------------------|-----------------|-----------------|----------|

| —                  |                                          |                                                                                                                |                                              | T3CKR<6:0>        |                 |                 |          |

| bit 15             |                                          |                                                                                                                |                                              |                   |                 |                 | bit      |

|                    |                                          |                                                                                                                |                                              |                   |                 |                 |          |

| U-0                | R/W-0                                    | R/W-0                                                                                                          | R/W-0                                        | R/W-0             | R/W-0           | R/W-0           | R/W-0    |

| —                  |                                          |                                                                                                                |                                              | T2CKR<6:0>        |                 |                 |          |

| bit 7              |                                          |                                                                                                                |                                              |                   |                 |                 | bit      |

|                    |                                          |                                                                                                                |                                              |                   |                 |                 |          |

| Legend:            |                                          |                                                                                                                |                                              |                   |                 |                 |          |

| R = Readab         | le bit                                   | W = Writable                                                                                                   | bit                                          | U = Unimplem      | nented bit, rea | id as '0'       |          |

| -n = Value a       | It POR                                   | '1' = Bit is set                                                                                               |                                              | '0' = Bit is clea | ared            | x = Bit is unkr | nown     |

|                    | T3CKR<6:0><br>(see Table 11              | <ul> <li>hted: Read as '</li> <li>Assign Timer</li> <li>I-2 for input pin</li> <li>nput tied to RP'</li> </ul> | 3 External Clo<br>selection num              | · /               | e Correspond    | ding RPn/RPIn F | 'in bits |

| bit 15<br>bit 14-8 | T3CKR<6:0><br>(see Table 11<br>1111111 = | Assign Timer<br>I-2 for input pin<br>nput tied to RP<br>nput tied to CM                                        | 3 External Clo<br>selection num<br>127<br>P1 | · /               | e Correspond    | ding RPn/RPIn F | 'in bits |

|                    | T3CKR<6:0><br>(see Table 11<br>1111111 = | Assign Timer<br>I-2 for input pin<br>nput tied to RP <sup>2</sup>                                              | 3 External Clo<br>selection num<br>127<br>P1 | · /               | e Correspond    | ding RPn/RPIn F | Pin bits |

## REGISTER 11-4: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

### REGISTER 11-25: RPINR25: PERIPHERAL PIN SELECT INPUT REGISTER 25

| U-0                                | U-0   | U-0                                | U-0              | U-0             | U-0          | U-0   | U-0   |  |

|------------------------------------|-------|------------------------------------|------------------|-----------------|--------------|-------|-------|--|

| _                                  |       | —                                  | _                | —               |              | —     | —     |  |

| bit 15                             |       |                                    |                  |                 |              |       | bit 8 |  |

| U-0                                | R/W-0 | R/W-0                              | R/W-0            | R/W-0           | R/W-0        | R/W-0 | R/W-0 |  |

| _                                  |       | 10110                              |                  | COFSR<6:0>      |              |       |       |  |

| bit 7                              |       |                                    |                  |                 |              |       | bit 0 |  |

| Legend:                            |       |                                    |                  |                 |              |       |       |  |

| R = Readable bit W = Writable bit  |       | U = Unimplemented bit, read as '0' |                  |                 |              |       |       |  |

| -n = Value at POR '1' = Bit is set |       |                                    | '0' = Bit is cle | x = Bit is unkr | t is unknown |       |       |  |

bit 15-7 Unimplemented: Read as '0'

bit 6-0 **COFSR<6:0>:** Assign DCI FSYNC Input (COFS) to the Corresponding RPn/RPIn Pin bits (see Table 11-2 for input pin selection numbers) 1111111 = Input tied to RP127

| U-0          | R/W-0        | R/W-0                                                  | R/W-0         | R/W-0             | R/W-0           | R/W-0           | R/W-0  |

|--------------|--------------|--------------------------------------------------------|---------------|-------------------|-----------------|-----------------|--------|

| 0-0          | K/ VV-U      | K/ VV-U                                                | K/VV-U        | IC12R<6:0>        | K/W-U           | K/VV-U          | K/VV-U |

| <br>bit 15   |              |                                                        |               | 10121(<0.02       |                 |                 | bit 8  |

|              |              |                                                        |               |                   |                 |                 | bit c  |

| U-0          | R/W-0        | R/W-0                                                  | R/W-0         | R/W-0             | R/W-0           | R/W-0           | R/W-0  |

| —            |              |                                                        |               | IC11R<6:0>        |                 |                 |        |

| bit 7        |              |                                                        |               |                   |                 |                 | bit 0  |

| Legend:      |              |                                                        |               |                   |                 |                 |        |

| R = Readab   | ole bit      | W = Writable                                           | bit           | U = Unimplen      | nented bit, rea | id as '0'       |        |

| -n = Value a | at POR       | '1' = Bit is set                                       |               | '0' = Bit is clea | ared            | x = Bit is unkr | nown   |

|              |              | nput tied to RP <sup>-</sup><br>nput tied to CM        |               |                   |                 |                 |        |

|              |              | nput tied to Vss                                       |               |                   |                 |                 |        |

| bit 7        | Unimpleme    | nted: Read as '                                        | 0'            |                   |                 |                 |        |

| bit 6-0      | (see Table 1 | Assign Input C<br>I-2 for input pin<br>nput tied to RP | selection nun | ,                 | esponding RPi   | n/RPIn Pin bits |        |

|              |              | nput tied to CM<br>nput tied to Vss                    |               |                   |                 |                 |        |

## REGISTER 11-34: RPINR34: PERIPHERAL PIN SELECT INPUT REGISTER 34

## 19.0 INTER-INTEGRATED CIRCUIT™ (I<sup>2</sup>C™)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXX(GP/MC/MU)806/ 810/814 and PIC24EPXXX(GP/GU)810/ 814 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 19. "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70330) of the "dsPIC33E/PIC24E Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814 family of devices contain two Inter-Integrated Circuit ( $I^2C$ ) modules: I2C1 and I2C2.

The  $I^2C$  module provides complete hardware support for both Slave and Multi-Master modes of the  $I^2C$  serial communication standard, with a 16-bit interface.

The  $I^2C$  module has a 2-pin interface:

- The SCLx pin is the clock.

- The SDAx pin is the data.

The I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both Master and Slave modes of operation.

- I<sup>2</sup>C Slave mode supports 7 and 10-bit addressing.

- I<sup>2</sup>C Master mode supports 7 and 10-bit addressing.

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves.

- Serial clock synchronization for I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control).

- I<sup>2</sup>C supports multi-master operation, detects bus collision and arbitrates accordingly.

- IPMI support

- · SMBus support

## 19.1 I<sup>2</sup>C Resources

Many useful resources related to  $I^2C$  are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en554310              |

### 19.1.1 KEY RESOURCES

- Section 19. "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70330) in the "dsPIC33E/PIC24E Family Reference Manual"

- Code Samples

- · Application Notes

- Software Libraries

- Webinars

- All related *"dsPIC33E/PIC24E Family Reference Manual"* Sections

- Development Tools

# dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

| U-0        | U-0            | U-0                                        | U-0                                     | U-0                   | U-0                  | U-0                    | U-0                    |

|------------|----------------|--------------------------------------------|-----------------------------------------|-----------------------|----------------------|------------------------|------------------------|

| —          | _              | _                                          | _                                       | —                     | _                    | _                      | —                      |

| bit 15     |                | ·                                          |                                         |                       |                      |                        | bit 8                  |

|            |                |                                            |                                         |                       |                      |                        |                        |

| R/W-0      | R/W-0          | R/W-0                                      | R/W-0                                   | R/W-0                 | R/W-0                | R/W-0                  | R/W-0                  |

| DPPULUF    | DMPULUP        | DPPULDWN <sup>(1)</sup>                    | DMPULDWN <sup>(1)</sup>                 | VBUSON <sup>(1)</sup> | OTGEN <sup>(1)</sup> | VBUSCHG <sup>(1)</sup> | VBUSDIS <sup>(1)</sup> |

| bit 7      |                |                                            |                                         |                       |                      |                        | bit (                  |

|            |                |                                            |                                         |                       |                      |                        |                        |

| Legend:    |                |                                            |                                         |                       |                      |                        |                        |

| R = Reada  |                | W = Writable bi                            | t                                       | U = Unimplen          |                      |                        |                        |

| -n = Value | at POR         | '1' = Bit is set                           |                                         | '0' = Bit is clea     | ared                 | x = Bit is unkn        | own                    |

|            |                |                                            | ,                                       |                       |                      |                        |                        |

| bit 15-8   | -              | nted: Read as '0                           |                                         |                       |                      |                        |                        |

| bit 7      |                | D+ Pull-Up Enab                            |                                         |                       |                      |                        |                        |

|            |                | line pull-up resist<br>line pull-up resist |                                         |                       |                      |                        |                        |

| oit 6      |                | D- Pull-Up Enab                            |                                         |                       |                      |                        |                        |

|            |                | line pull-up resis                         |                                         |                       |                      |                        |                        |

|            |                | line pull-up resis                         |                                         |                       |                      |                        |                        |

| bit 5      | DPPULDWN       | I: D+ Pull-Down                            | Enable bit <sup>(1)</sup>               |                       |                      |                        |                        |

|            |                |                                            | esistor is enabled                      |                       |                      |                        |                        |

|            |                | -                                          | esistor is disabled                     | 1                     |                      |                        |                        |

| bit 4      |                | N: D- Pull-Down                            |                                         |                       |                      |                        |                        |

|            |                | •                                          | sistor is enabled<br>sistor is disabled |                       |                      |                        |                        |

| bit 3      |                | BUS Power-on bi                            |                                         |                       |                      |                        |                        |

|            |                | e is powered                               | (* *                                    |                       |                      |                        |                        |

|            |                | e is not powered                           |                                         |                       |                      |                        |                        |

| bit 2      | OTGEN: OT      | G Features Enal                            | ole bit <sup>(1)</sup>                  |                       |                      |                        |                        |

|            | 1 = USB OT     | G is enabled; all                          | D+/D- pull-ups a                        | nd pull-downs         | are enabled          |                        |                        |

|            |                |                                            | +/D- pull-ups and                       |                       | re controlled i      | n hardware by          | the settings o         |

|            |                |                                            | N bits (UxCON<3                         | 3,0>)                 |                      |                        |                        |

| bit 1      |                | VBUS Charge Se                             |                                         |                       |                      |                        |                        |

|            |                | e is set to charge<br>e is set to charge   |                                         |                       |                      |                        |                        |

| bit 0      |                | /BUS Discharge E                           |                                         |                       |                      |                        |                        |

|            |                | 0                                          | hrough a resistor                       |                       |                      |                        |                        |

|            |                | e is not discharg                          |                                         |                       |                      |                        |                        |

|            |                |                                            |                                         |                       |                      |                        |                        |

| Note 1:    | These bits are | only used in Hos                           | st mode; do not u                       | se in Device m        | node.                |                        |                        |

## REGISTER 22-2: UxOTGCON: USB ON-THE-GO CONTROL REGISTER

## REGISTER 22-17: UxIE: USB INTERRUPT ENABLE REGISTER (HOST MODE)

| U-0          | U-0                                | U-0                | U-0             | U-0               | U-0             | U-0            | U-0      |

|--------------|------------------------------------|--------------------|-----------------|-------------------|-----------------|----------------|----------|

| _            | —                                  | —                  |                 | —                 | _               | _              | _        |

| bit 15       |                                    |                    |                 |                   |                 |                | bit 8    |

|              |                                    |                    |                 |                   |                 |                |          |

| R/W-0        | R/W-0                              | R/W-0              | R/W-0           | R/W-0             | R/W-0           | R/W-0          | R/W-0    |

| STALLIE      | ATTACHIE <sup>(1)</sup>            | RESUMEIE           | IDLEIE          | TRNIE             | SOFIE           | UERRIE         | DETACHIE |

| bit 7        |                                    |                    |                 |                   |                 |                | bit      |

| Legend:      |                                    |                    |                 |                   |                 |                |          |

| R = Readab   | le bit                             | W = Writable b     | it              | U = Unimplem      | ented bit, read | 1 as '0'       |          |

| -n = Value a |                                    | '1' = Bit is set   |                 | '0' = Bit is clea |                 | x = Bit is unk | nown     |

|              |                                    |                    |                 |                   |                 |                |          |

| bit 15-8     | Unimplement                        | ted: Read as '0'   |                 |                   |                 |                |          |

| oit 7        | STALLIE: ST                        | ALL Handshake      | Interrupt Ena   | able bit          |                 |                |          |

|              | 1 = Interrupt                      | is enabled         |                 |                   |                 |                |          |

|              | 0 = Interrupt                      | is disabled        |                 |                   |                 |                |          |

| pit 6        | ATTACHIE: P                        | eripheral Attach   | Interrupt bit(  | 1)                |                 |                |          |

|              | 1 = Interrupt i<br>0 = Interrupt i |                    |                 |                   |                 |                |          |

| bit 5        |                                    | Resume Interrup    | t hit           |                   |                 |                |          |

|              | 1 = Interrupt i                    |                    |                 |                   |                 |                |          |

|              | 0 = Interrupt                      |                    |                 |                   |                 |                |          |

| bit 4        | IDLEIE: Idle [                     | Detect Interrupt I | oit             |                   |                 |                |          |

|              | 1 = Interrupt                      |                    |                 |                   |                 |                |          |

|              | 0 = Interrupt                      |                    |                 |                   |                 |                |          |

| bit 3        |                                    | Processing Co      | mplete Interro  | upt bit           |                 |                |          |

|              | 1 = Interrupt                      |                    |                 |                   |                 |                |          |

| oit 2        | •                                  | of-Frame Token     | Intorrunt hit   |                   |                 |                |          |

|              | 1 = Interrupt i                    |                    | interrupt bit   |                   |                 |                |          |

|              | 0 = Interrupt                      |                    |                 |                   |                 |                |          |

| oit 1        |                                    | 3 Error Conditior  | n Interrupt bit |                   |                 |                |          |

|              | 1 = Interrupt                      |                    | •               |                   |                 |                |          |

|              | 0 = Interrupt                      | is disabled        |                 |                   |                 |                |          |

| bit 0        |                                    | JSB Detach Inte    | rrupt Enable    | bit               |                 |                |          |

|              | 1 = Interrupt                      | is enabled         |                 |                   |                 |                |          |

|              | 0 = Interrupt                      |                    |                 |                   |                 |                |          |

Note 1: Unimplemented in OTG mode, read as '0'.

# dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

## REGISTER 22-29: UxFRML: USB FRAME NUMBER LOW REGISTER

| U-0             | U-0                                                                  | U-0              | U-0 | U-0              | U-0   | U-0             | U-0   |

|-----------------|----------------------------------------------------------------------|------------------|-----|------------------|-------|-----------------|-------|

| —               | _                                                                    | —                | —   | —                | —     | —               |       |

| bit 15          |                                                                      |                  |     |                  |       |                 | bit 8 |

|                 |                                                                      |                  |     |                  |       |                 |       |

| R-0             | R-0                                                                  | R-0              | R-0 | R-0              | R-0   | R-0             | R-0   |

|                 |                                                                      |                  | FRM | <7:0>            |       |                 |       |

| bit 7           |                                                                      |                  |     |                  |       |                 | bit 0 |

|                 |                                                                      |                  |     |                  |       |                 |       |

| Legend:         |                                                                      |                  |     |                  |       |                 |       |

| R = Readable    | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |     |                  |       |                 |       |

| -n = Value at P | OR                                                                   | '1' = Bit is set |     | '0' = Bit is cle | eared | x = Bit is unki | nown  |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 FRM<7:0>: 11-Bit Frame Number Lower 8 bits

These register bits are updated with the current frame number whenever a SOF token is received.

## 26.3 RTCC Registers

# REGISTER 26-1: RCFGCAL: RTCC CALIBRATION AND CONFIGURATION REGISTER<sup>(1)</sup>

| R/W-0                | U-0 | R/W-0   | R-0     | R-0                    | R/W-0 | R/W-0 | R/W-0  |

|----------------------|-----|---------|---------|------------------------|-------|-------|--------|

| RTCEN <sup>(2)</sup> | —   | RTCWREN | RTCSYNC | HALFSEC <sup>(3)</sup> | RTCOE | RTCPT | R<1:0> |

| bit 15               |     |         |         |                        |       |       | bit 8  |

|                      |     |         |         |                        |       |       |        |

| R/W-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|----------|-------|-------|-------|-------|-------|-------|

|       | CAL<7:0> |       |       |       |       |       |       |

| bit 7 |          |       |       |       |       | bit 0 |       |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15  | RTCEN: RTCC Enable bit <sup>(2)</sup><br>1 = RTCC module is enabled<br>0 = RTCC module is disabled                                                                               |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14  | Unimplemented: Read as '0'                                                                                                                                                       |

| bit 13  | RTCWREN: RTCC Value Registers Write Enable bit                                                                                                                                   |

|         | <ul> <li>1 = RTCVAL register can be written to by the user application</li> <li>0 = RTCVAL register is locked out from being written to by the user application</li> </ul>       |

| bit 12  | RTCSYNC: RTCC Value Registers Read Synchronization bit                                                                                                                           |

|         | <ul> <li>1 = A rollover is about to occur in 32 clock edges (approximately 1 ms)</li> <li>0 = A rollover will not occur</li> </ul>                                               |

| bit 11  | HALFSEC: Half-Second Status bit <sup>(3)</sup>                                                                                                                                   |

|         | <ul> <li>1 = Second half period of a second</li> <li>0 = First half period of a second</li> </ul>                                                                                |

| bit 10  | RTCOE: RTCC Output Enable bit                                                                                                                                                    |

|         | <ul> <li>1 = RTCC output is enabled</li> <li>0 = RTCC output is disabled</li> </ul>                                                                                              |

| bit 9-8 | RTCPTR<1:0>: RTCC Value Register Pointer bits                                                                                                                                    |

|         | Points to the corresponding RTCC Value register when reading the RTCVAL register; the RTCPTR<1:0> value decrements on every access of the RTCVAL register until it reaches '00'. |

- **Note 1:** The RCFGCAL register is only affected by a POR.

- 2: A write to the RTCEN bit is only allowed when RTCWREN = 1.

- 3: This bit is read-only. It is cleared when the lower half of the MINSEC register is written.

## 31.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

## 31.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

## 31.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easyto-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

## 31.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express

The MPLAB PICkit 3 allows debugging and programming of PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB Integrated Development Environment (IDE). The MPLAB PICkit 3 is connected to the design engineer's PC using a full speed USB interface and can be connected to the target via an Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup>.

The PICkit 3 Debug Express include the PICkit 3, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

## 32.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814 electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814 family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

## Absolute Maximum Ratings

#### (See Note 1)

| Ambient temperature under bias                                                    | 40°C to +125°C          |

|-----------------------------------------------------------------------------------|-------------------------|

| Storage temperature                                                               | 65°C to +150°C          |

| Voltage on VDD with respect to Vss                                                | -0.3V to +4.0V          |

| Voltage on any pin that is not 5V tolerant, with respect to Vss <sup>(3)</sup>    | 0.3V to (VDD + 0.3V)    |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD \ge 3.0V^{(3)}$      | -0.3V to +5.5V          |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 3.0V <sup>(3)</sup> | 0.3V to 3.6V            |

| Voltage on D+ OR D- pin with respect to VUSB3V3                                   | 0.3V to (VUSB3V3 +0.3V) |

| Voltage on VBUS with respect to VSS                                               | 0.3V to +5.5V           |

| Maximum current out of Vss pin                                                    |                         |

| Maximum current into Vod pin <sup>(2)</sup>                                       |                         |

| Maximum current sourced/sunk by any 4x I/O pin <sup>(4)</sup>                     |                         |

| Maximum current sourced/sunk by any 8x I/O pin <sup>(4)</sup>                     | 25 mA                   |

| Maximum current sunk by all ports                                                 | 200 mA                  |

| Maximum current sourced by all ports <sup>(2)</sup>                               | 200 mA                  |

**Note 1:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 32-2).

- 3: See the "Pin Diagrams" section for the 5V tolerant pins.

- 4: Characterized but not tested.

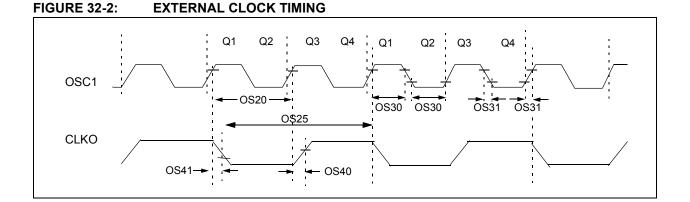

| TABLE 32-16: | EXTERNAL | <b>CLOCK TIMING REQUIREMENTS</b> | S |

|--------------|----------|----------------------------------|---|

|              |          |                                  |   |

|        |               |                                                                                                                                                                                              | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated) |                     |              |       |                               |  |

|--------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------|--------------|-------|-------------------------------|--|

|        |               | $\begin{array}{rl} \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                                                                          |                     |              |       |                               |  |

| Param. | Symbol        | Characteristic                                                                                                                                                                               | Min.                                                                     | Typ. <sup>(1)</sup> | Max.         | Units | Conditions                    |  |

| OS10   | FIN           | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes)                                                                                                           | DC                                                                       | _                   | 60           | MHz   | EC                            |  |

|        |               | Oscillator Crystal Frequency                                                                                                                                                                 | 3.5                                                                      |                     | 10           | MHz   | ХТ                            |  |

|        |               |                                                                                                                                                                                              | 10                                                                       |                     | 40           | MHz   | HS                            |  |

|        |               |                                                                                                                                                                                              | 32.4                                                                     | 32.768              | 33.1         | kHz   | SOSC                          |  |

| OS20   | Tosc          | Tosc = 1/Fosc                                                                                                                                                                                | 8.33                                                                     | _                   | DC           | ns    | +125°C                        |  |

|        |               |                                                                                                                                                                                              | 7.14                                                                     | —                   | DC           | ns    | +85°C                         |  |

| OS25   | TCY           | Instruction Cycle Time <sup>(2)</sup>                                                                                                                                                        | 16.67                                                                    | _                   | DC           | ns    | +125°C                        |  |

|        |               |                                                                                                                                                                                              | 14.28                                                                    |                     | DC           | ns    | +85°C                         |  |

| OS30   | TosL,<br>TosH | External Clock In (OSC1)<br>High or Low Time                                                                                                                                                 | 0.375 x Tosc                                                             | —                   | 0.625 x Tosc | ns    | EC                            |  |

| OS31   | TosR,<br>TosF | External Clock In (OSC1)<br>Rise or Fall Time                                                                                                                                                | —                                                                        | —                   | 20           | ns    | EC                            |  |

| OS40   | TckR          | CLKO Rise Time <sup>(3)</sup>                                                                                                                                                                | —                                                                        | 5.2                 | _            | ns    |                               |  |

| OS41   | TckF          | CLKO Fall Time <sup>(3)</sup>                                                                                                                                                                |                                                                          | 5.2                 | _            | ns    |                               |  |

| OS42   | Gм            | External Oscillator<br>Transconductance <sup>(4)</sup>                                                                                                                                       | -                                                                        | 12                  | —            | mA/V  | HS, VDD = 3.3V,<br>TA = +25°C |  |

|        |               |                                                                                                                                                                                              | —                                                                        | 6                   | —            | mA/V  | XT, VDD = 3.3V,<br>TA = +25°C |  |

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

2: Instruction cycle period (Tcr) equals two times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "Minimum" values with an external clock applied to the OSC1 pin. When an external clock input is used, the "Maximum" cycle time limit is "DC" (no clock) for all devices.

- 3: Measurements are taken in EC mode. The CLKO signal is measured on the OSC2 pin.

- 4: This parameter is characterized, but not tested in manufacturing.

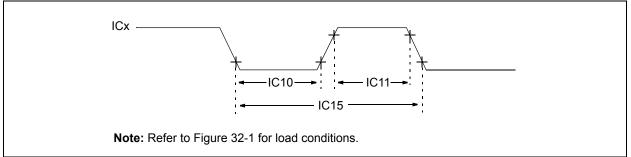

### TABLE 32-27: INPUT CAPTURE MODULE (ICx) TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                | <b>d)</b><br>-40°C ≤                     | TA ≤ +8 | <b>o 3.6V</b><br>5°C for Industrial<br>25°C for Extended | Ŀ                                |                                  |

|--------------------|--------|--------------------------------|------------------------------------------|---------|----------------------------------------------------------|----------------------------------|----------------------------------|

| Param.             | Symbol | Characteristics <sup>(1)</sup> | Min. Max. Units Conditions               |         |                                                          |                                  | tions                            |

| IC10               | TccL   | ICx Input Low Time             | [Greater of<br>(12.5 or 0.5 Tcy)/N] + 25 |         | ns                                                       | Must also meet<br>Parameter IC15 | N = prescale<br>value (1, 4, 16) |

| IC11               | TCCH   | ICx Input High Time            | [Greater of<br>(12.5 or 0.5 Tcy)/N] + 25 |         | ns                                                       | Must also meet<br>Parameter IC15 |                                  |